Efficient validation of coherency between processor cores and accelerators in computer systems

a computer system and accelerator technology, applied in the field of computer systems, can solve the problems of many protocols, long access penalties, and complicated protocols

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

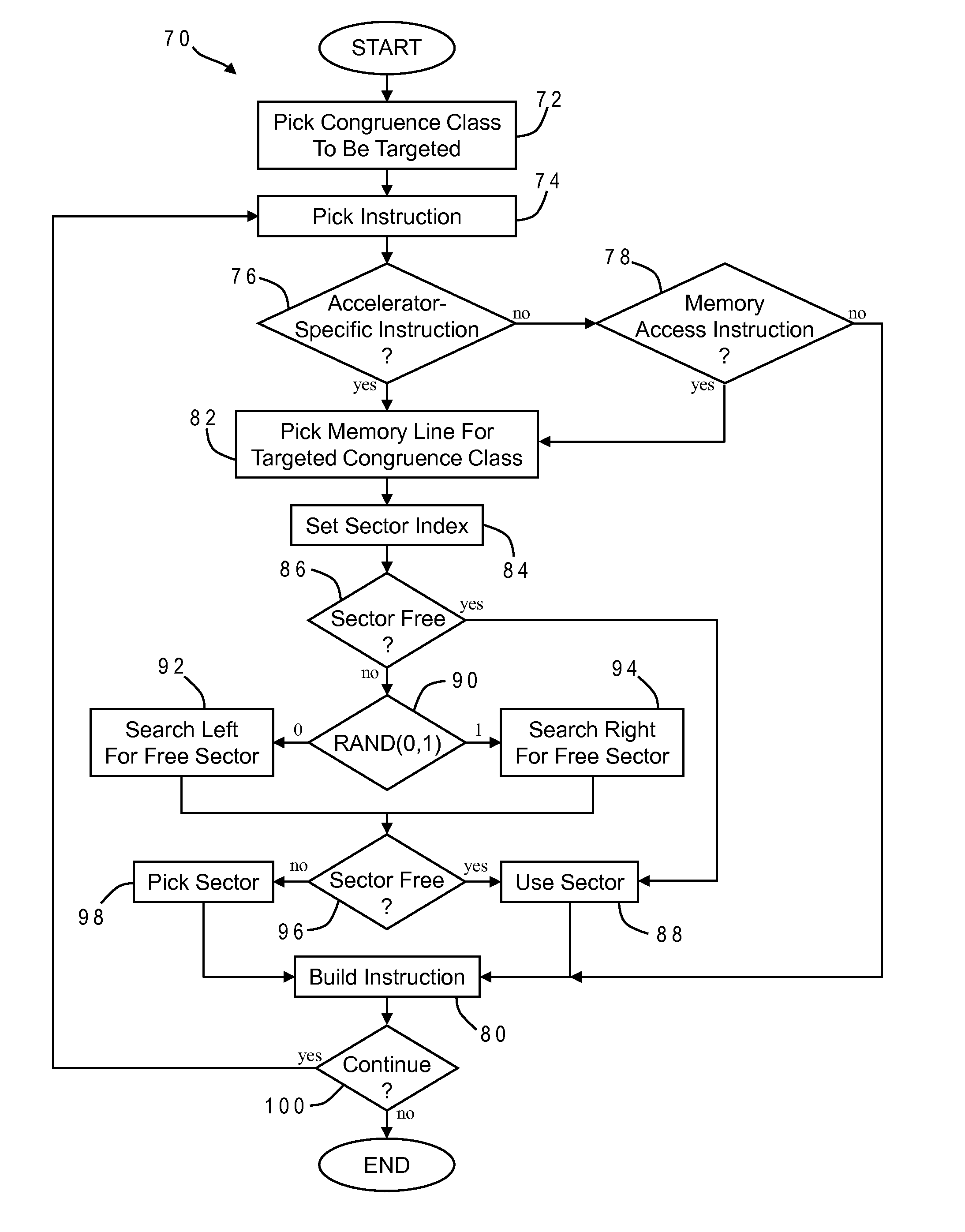

Method used

Image

Examples

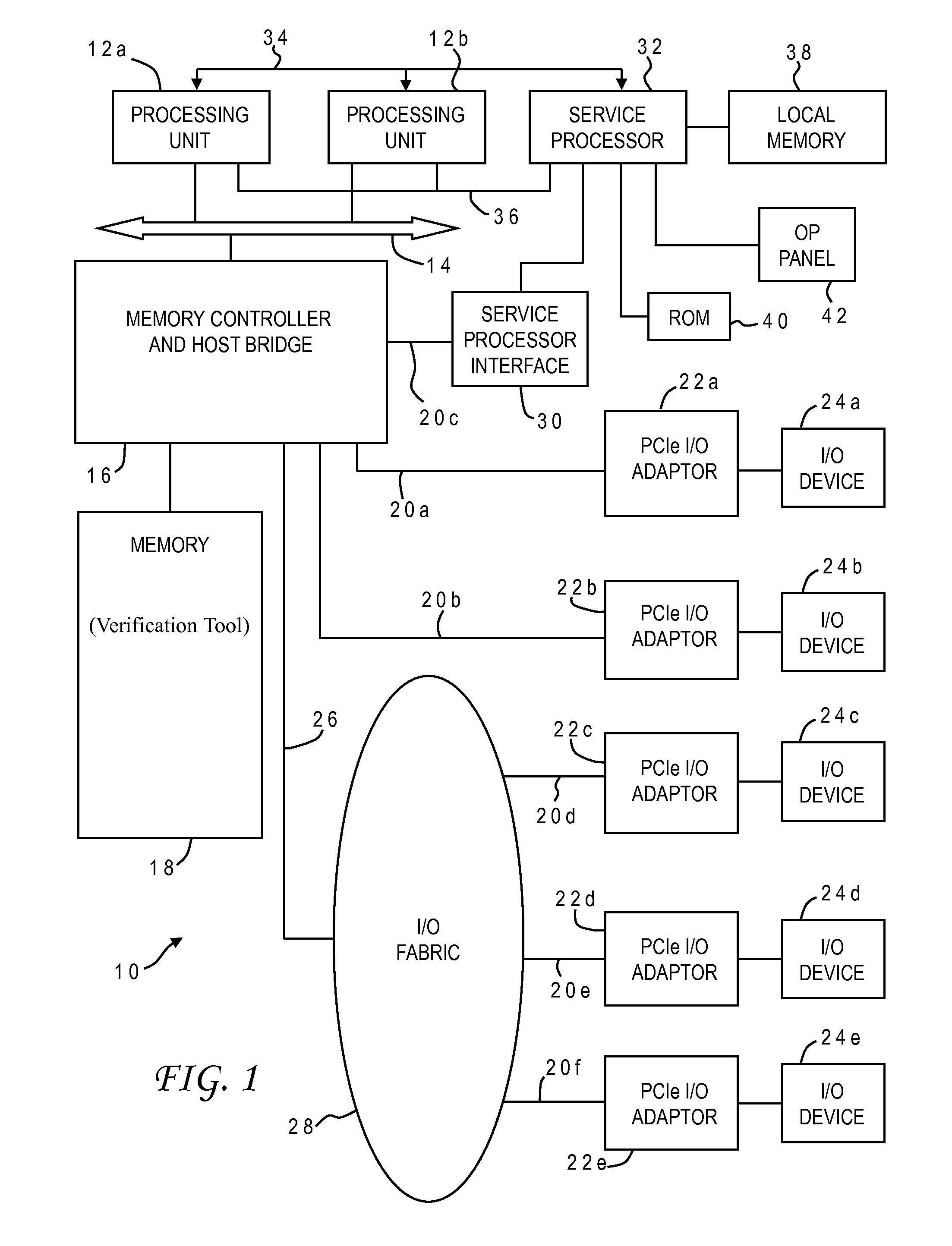

Embodiment Construction

)

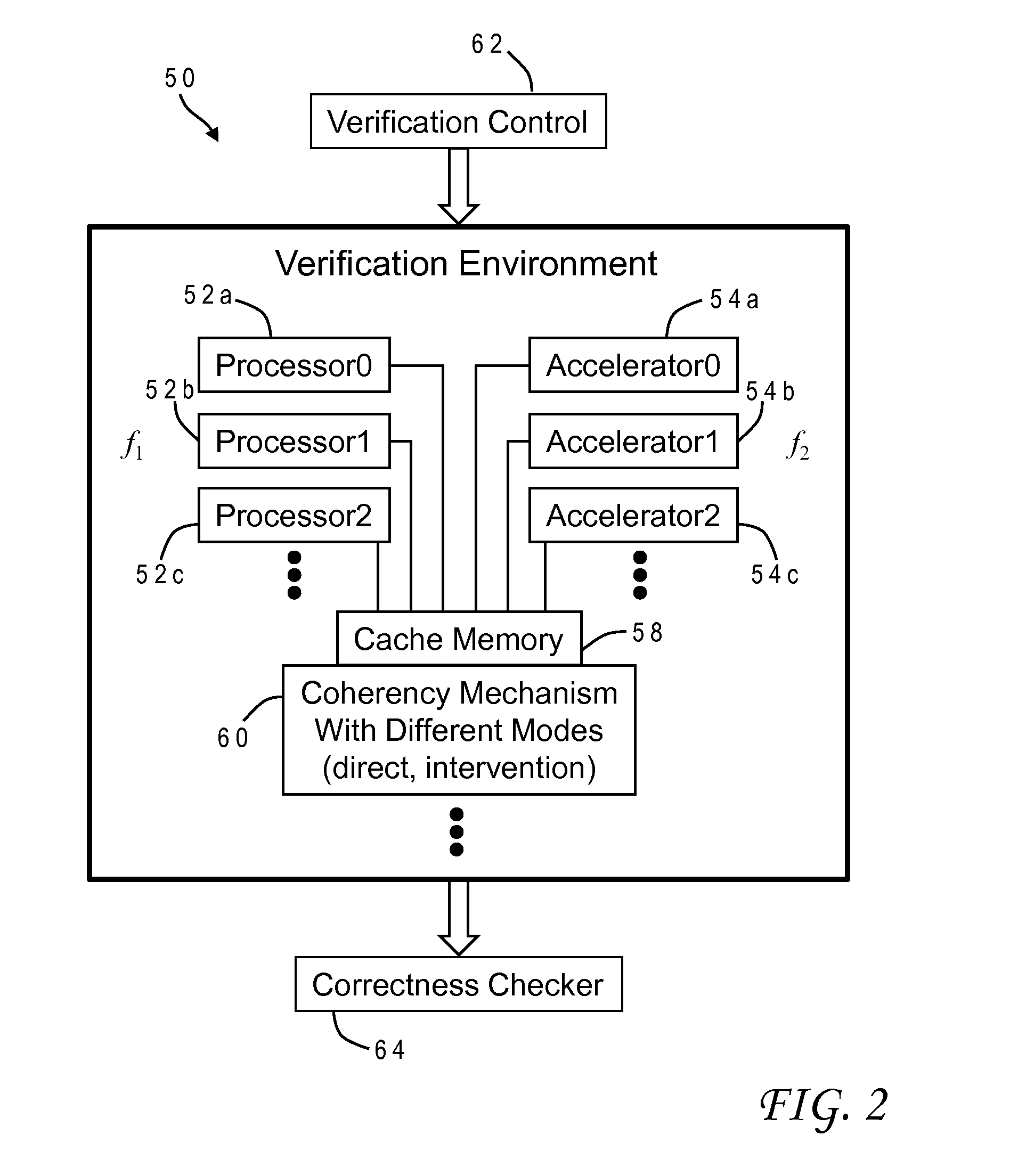

[0018]As growing demands for performance have increased reliance on hardware accelerators, it has become more important and more difficult to ensure that accelerator operations are coherent with respect to memory operations by processors. Coherency within SMP systems is easily validated according to known methods, but coherency across two different mechanisms possibly operating at different frequencies like processors and an off-chip field programmable gate array (FPGA) is a difficult challenge for the design and validation teams. Special alignment requirements and synchronization requirements make it difficult to extract all possible corner errors in regular random tests.

[0019]It would, therefore, be desirable to devise an improved method of validating coherency between processors and accelerators which can imitate real world scenarios. It would be further advantageous if the method could efficiently validate accelerators with different coherency modes available in the system to m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More