Circuit and method for generating column path control signals in semiconductor device

a technology of circuit and path control, applied in logic circuit coupling/interface arrangement, digital storage, instruments, etc., can solve problems such as erroneous read or write operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030]Preferred embodiments of the present disclosure will now be described in detail with reference to the accompanying drawings.

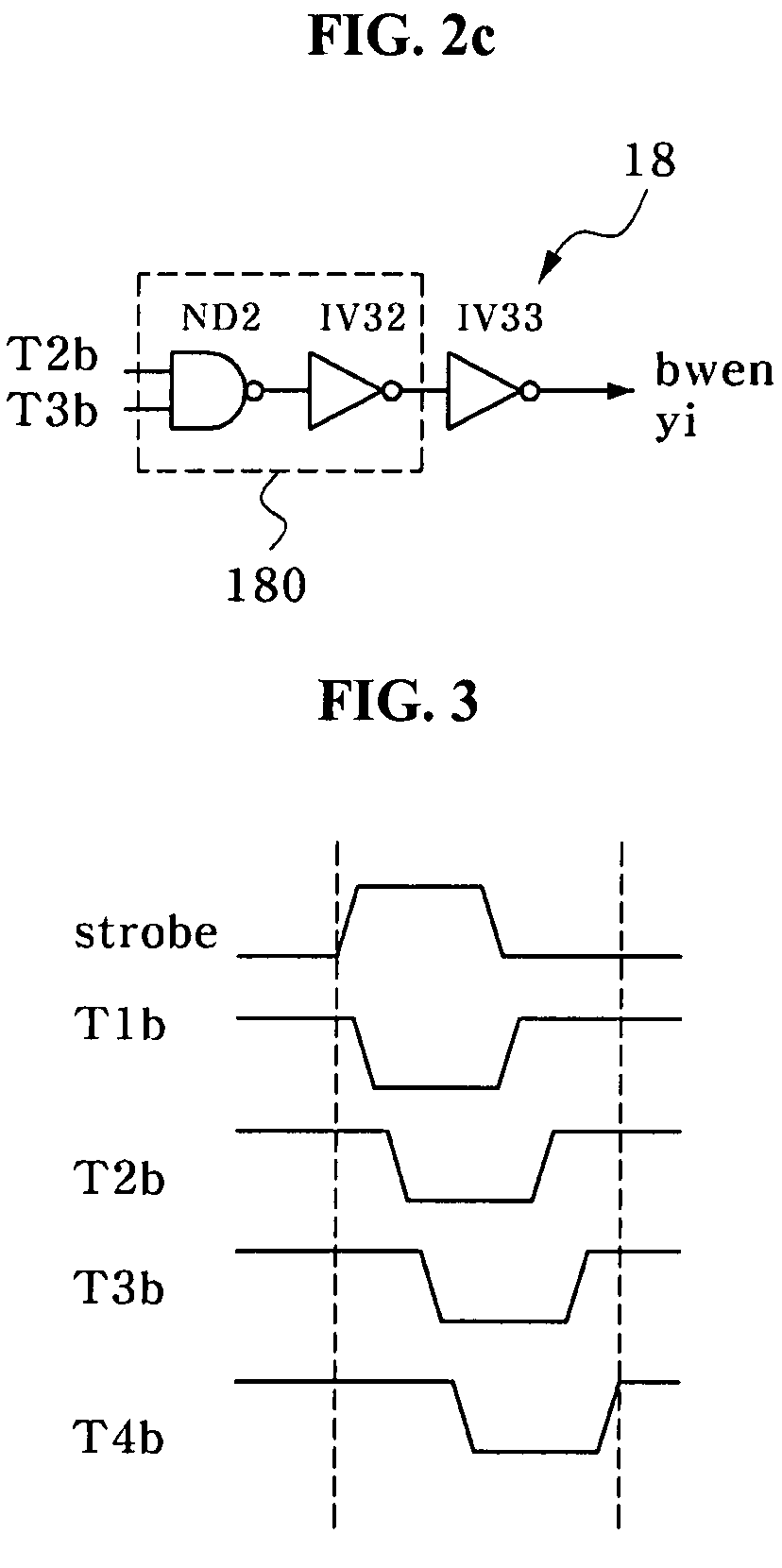

[0031]In a column path control signal generating circuit and method according to the present disclosure, generation of column path control signals required for a read / write operation in a semiconductor device is achieved, using delay of a strobe signal through the same delay unit. Accordingly, the column path control signals can be generated under the condition in which they have been influenced by the same process, voltage, and temperature (PVT) characteristic variation of CMOS transistors. As a result, the initially-designed timing margins among the column path control signals can be maintained.

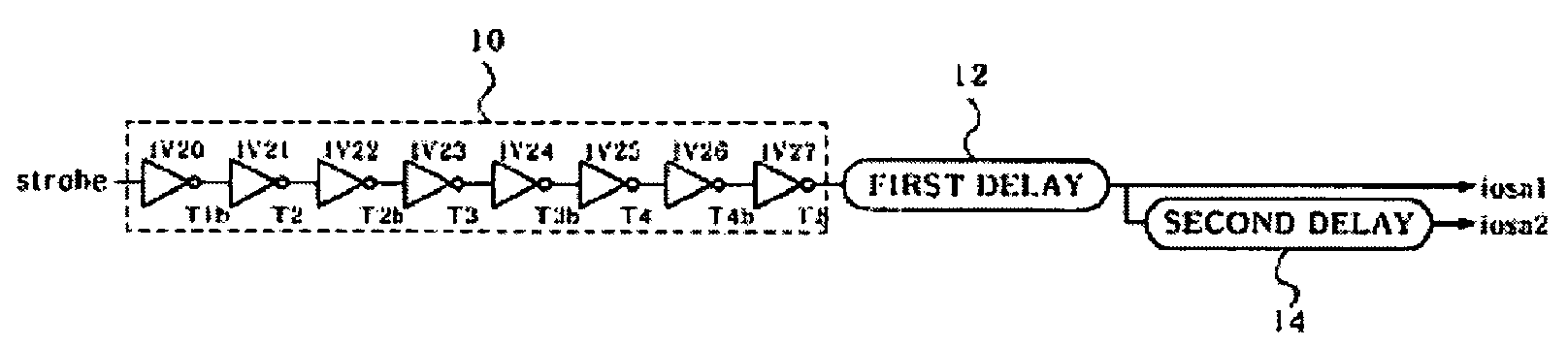

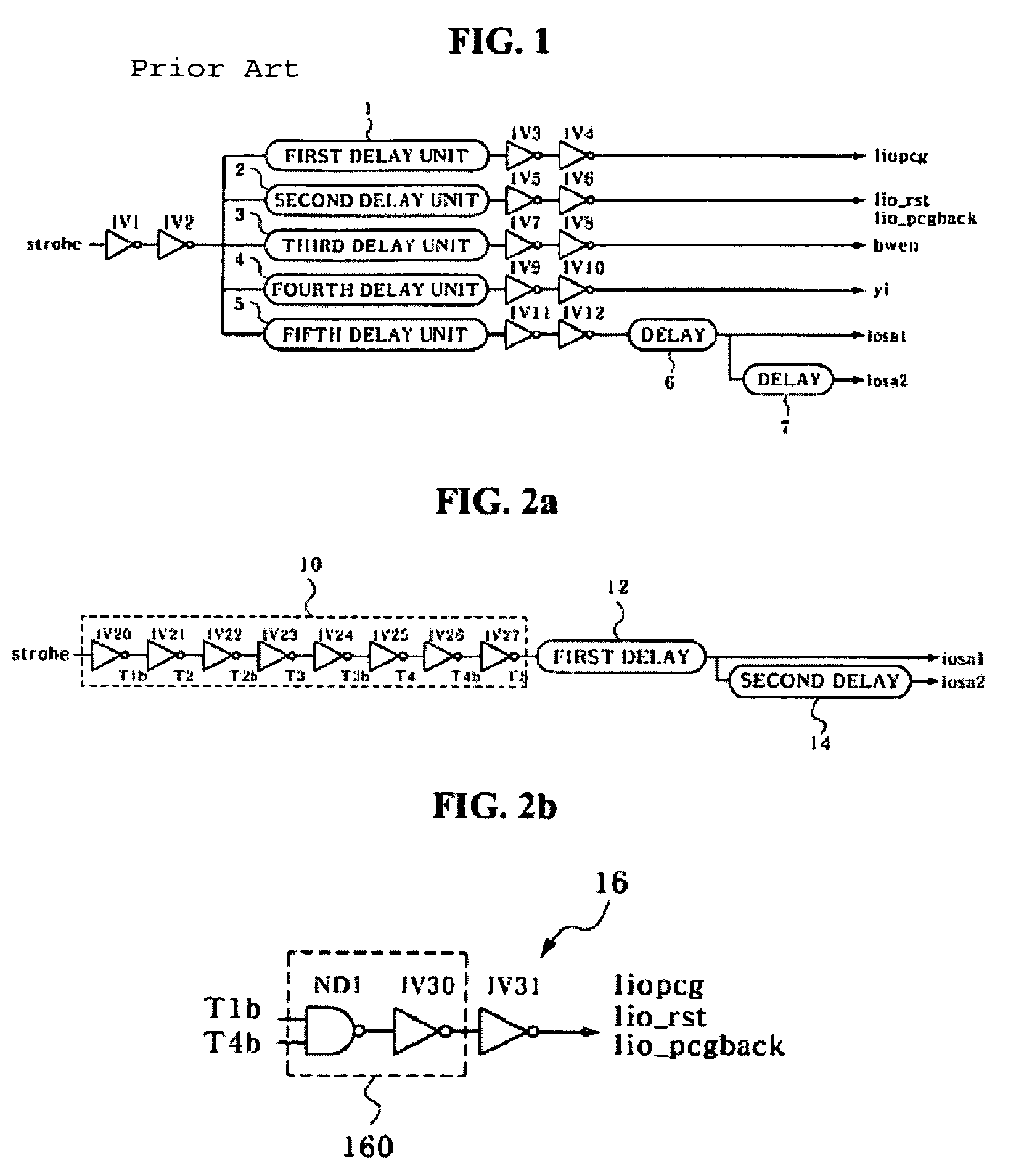

[0032]FIGS. 2A to 2C are circuit diagrams illustrating a column path control signal generating circuit according to an exemplary embodiment of the present disclosure.

[0033]As shown in FIG. 2A, the column path control signal generating circuit includes a strobe si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More