Method for making a design layout and mask

a technology of design layout and mask, applied in the direction of error detection/correction, program control, instruments, etc., can solve the problems of difficult to faithfully form the pattern, the configuration on the wafer is not formed, and the time and effort required to determine the design rules

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022]An embodiment of the present invention will be described below with reference to the drawing.

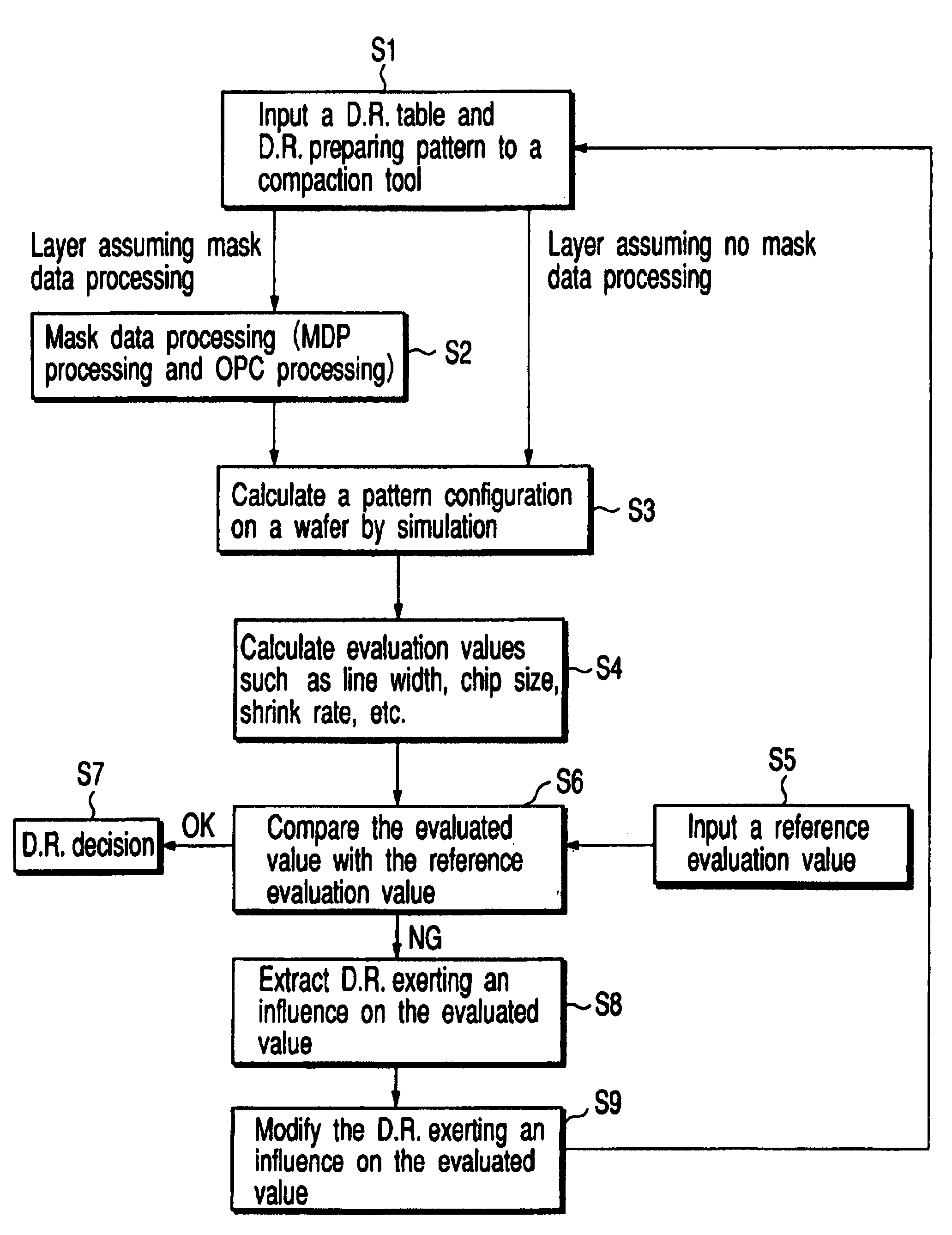

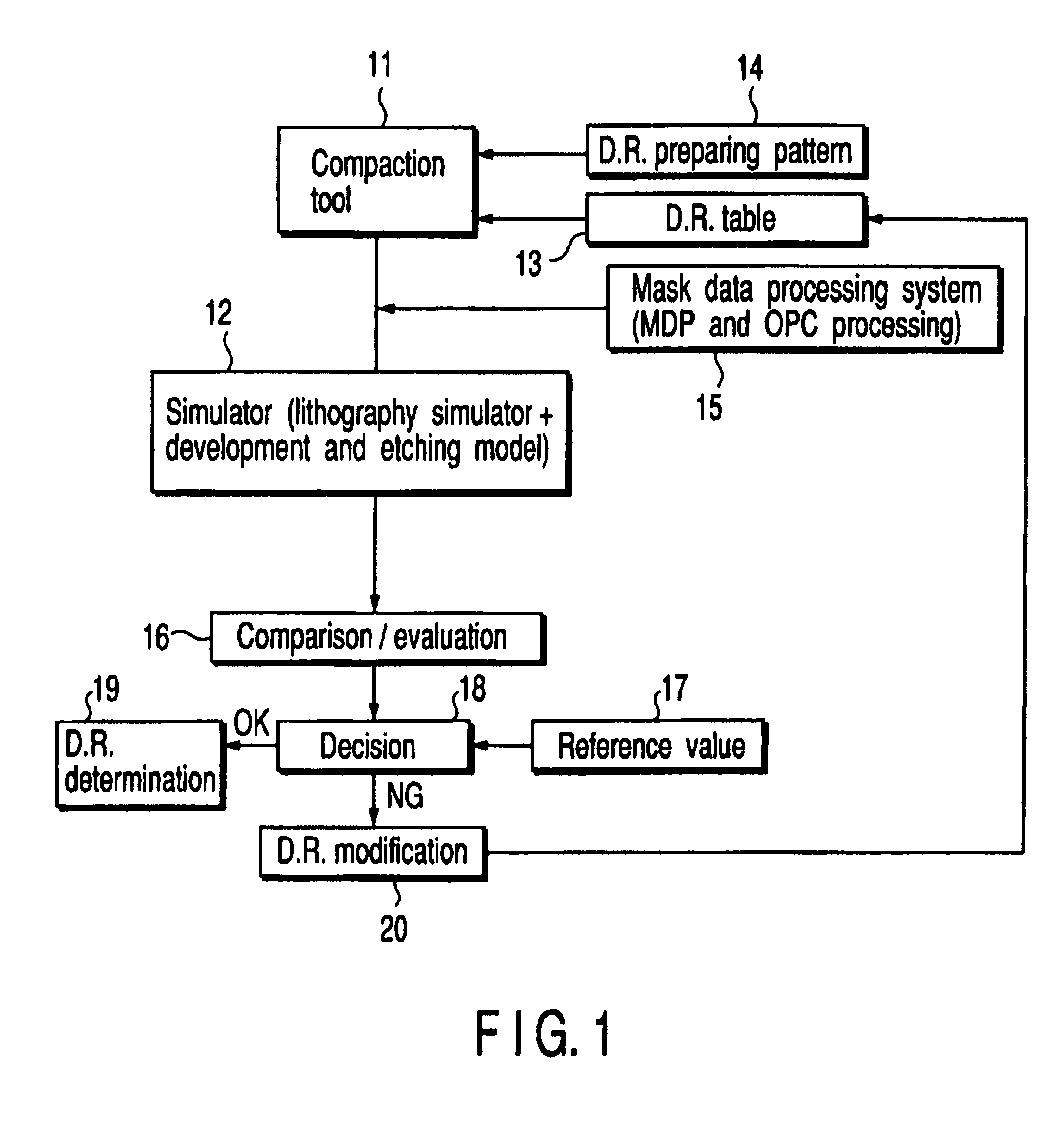

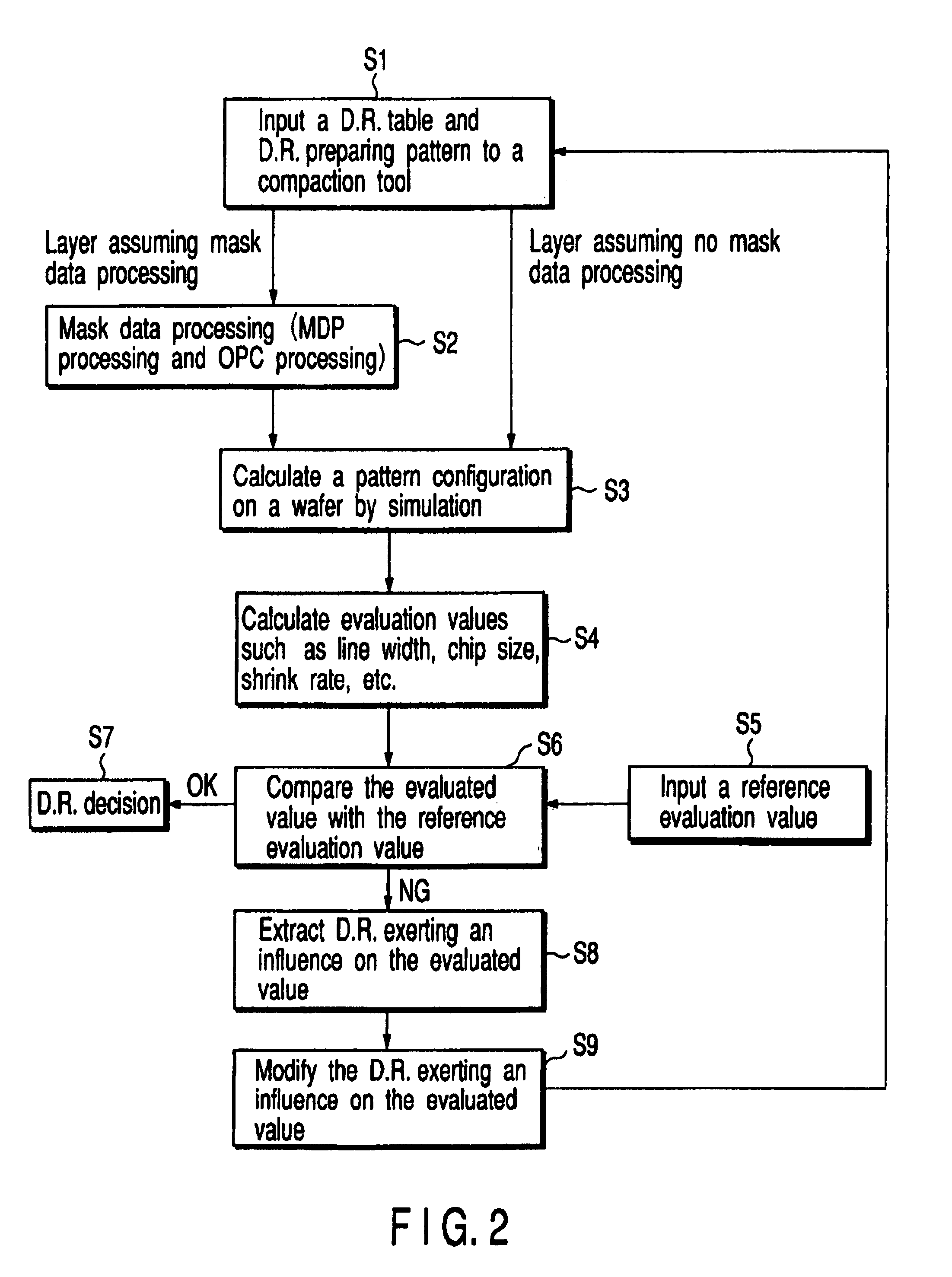

[0023]FIG. 1 is a functional block diagram showing a concept of a designing system according to an embodiment of the present invention.

[0024]In the present system, a compaction tool 11 and simulator 12 coexist. The compaction tool 11 compacts a design layout so as to make the design layout area as small as possible. The simulator 12 predicts a pattern configuration formed at a surface area of a semiconductor wafer on the basis of the design layout.

[0025]To the compaction tool 11, a design rule table 13 for defining a design rule of a given generation and a design rule preparing pattern 14 for use in a design rule calculation are inputted. In the compaction tool 11, the design rule preparing pattern 14 is compacted in accordance with the design rule defined by the design rule table 13 and a “compacted” pattern is outputted to the simulator 12.

[0026]The simulator 12 includes the followin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More