Testing method capable of configuring FPGA configurable logic block with five times

A technology for configuring logic and testing methods, which is applied in digital circuit testing, electronic circuit testing, etc., can solve the problems of complex test circuit structure, low efficiency, and multiple configuration times, so as to save test input and output ports and reduce the number of input and output ports , the effect of reducing the number of configurations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

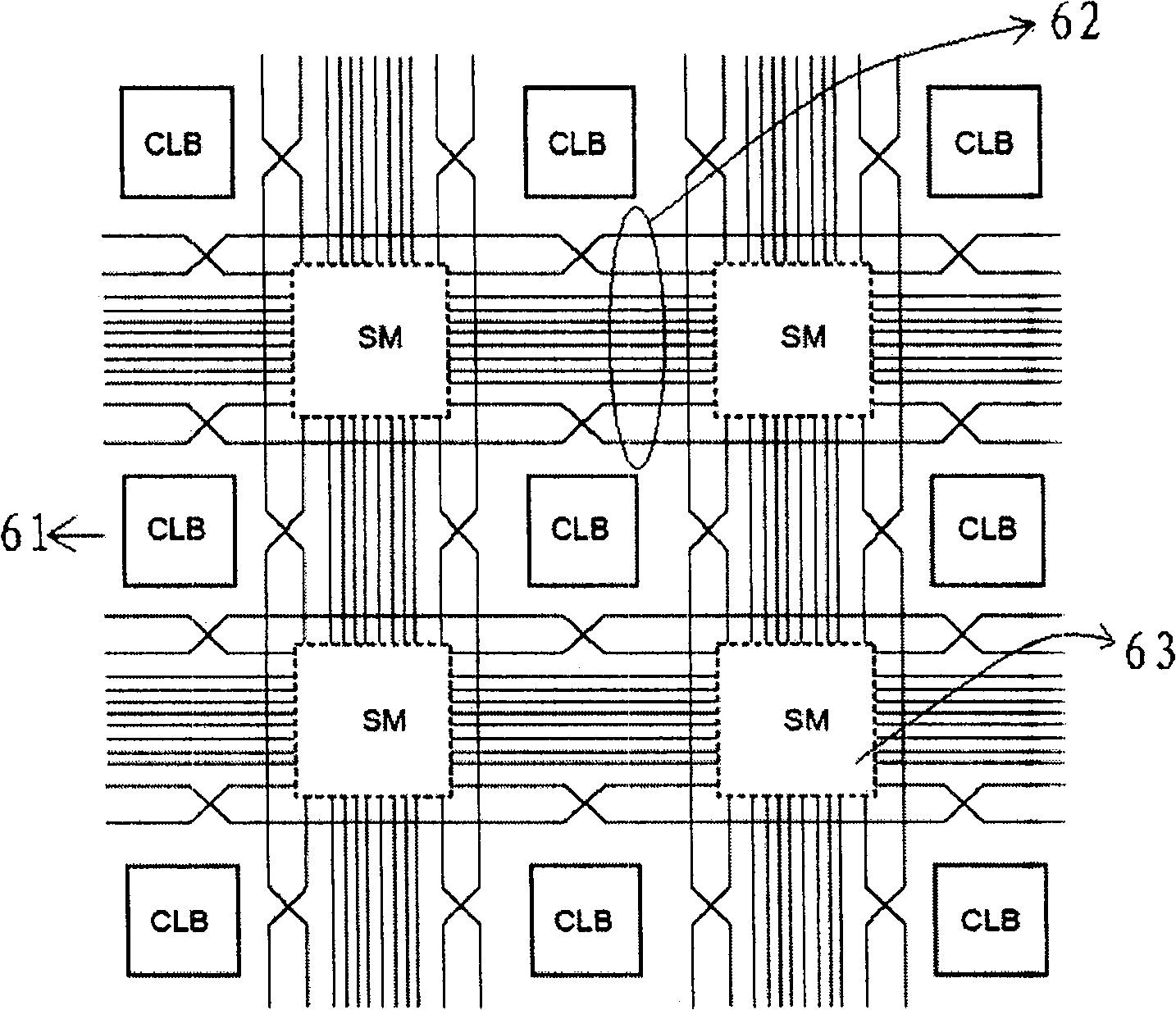

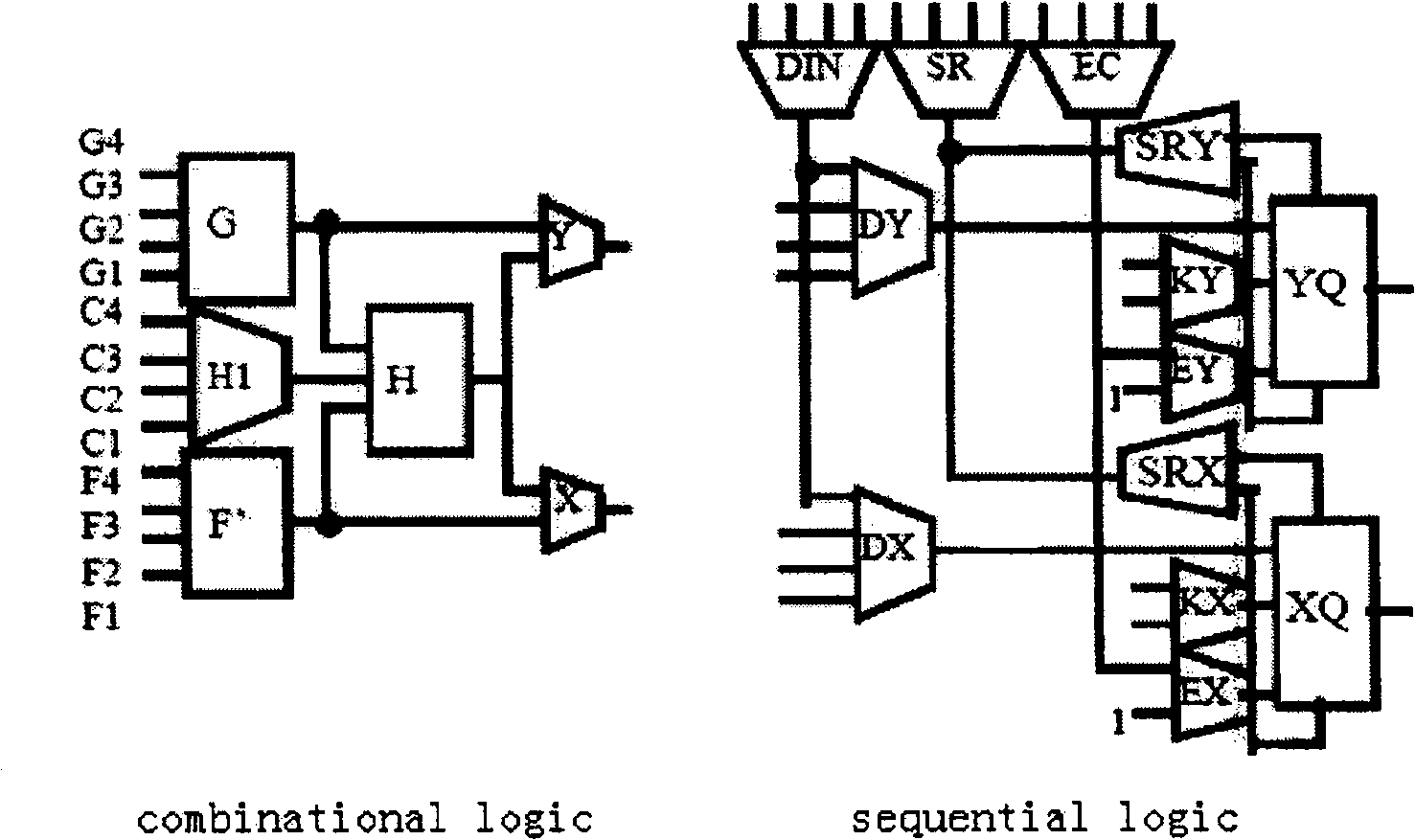

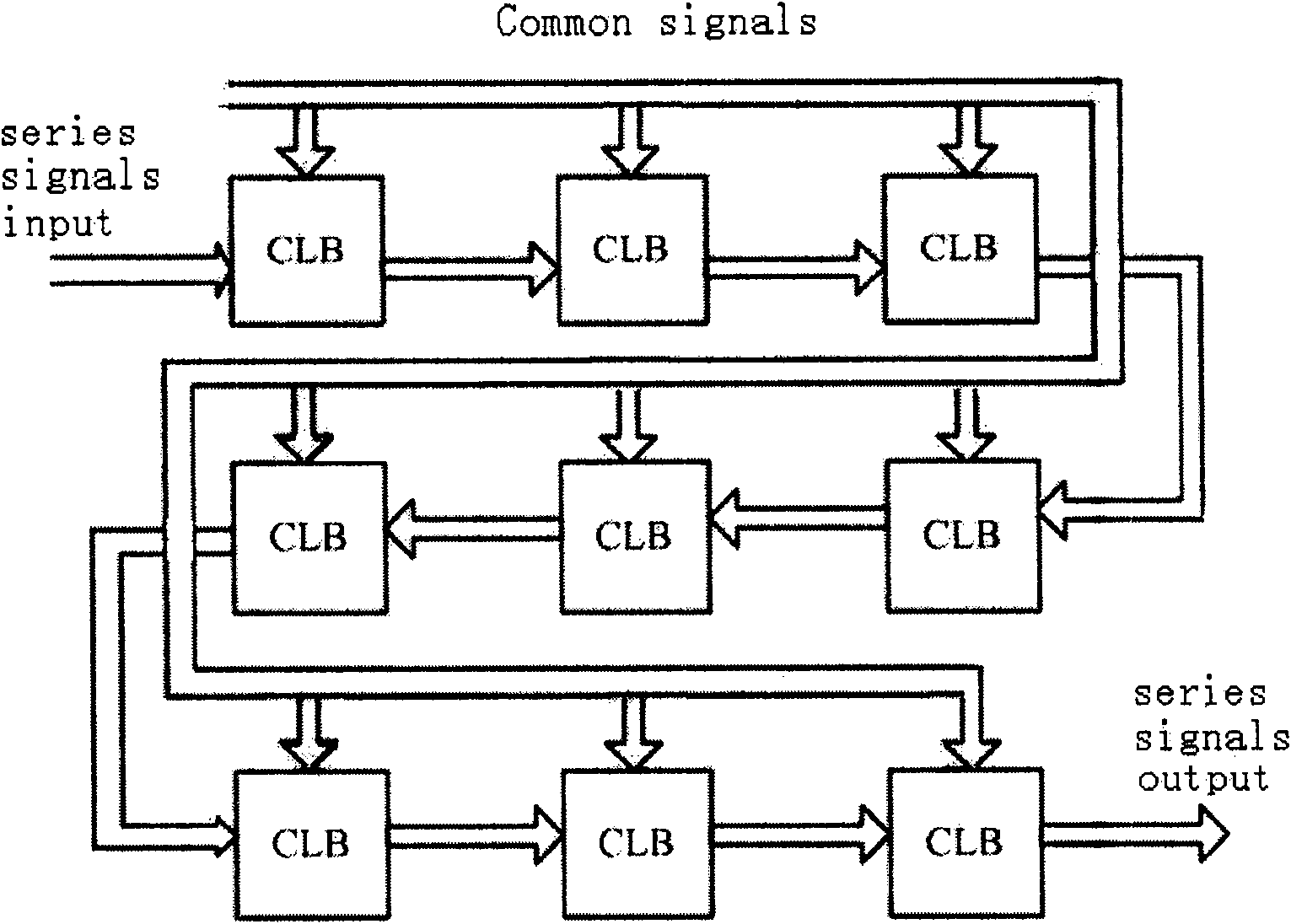

[0050] FPGA basic circuit structure such as figure 1 As shown, the configurable logic block CLB61 is distributed in an array, the interconnection segment 62 and the switch matrix SM63 surround the configurable logic block, and various functions can be flexibly realized through user configuration. Such as figure 2 As shown, the configurable logic block 61 can be divided into a combination logic part and a sequential logic part according to its function. The combination logic part includes a four-input (that is, four input terminals) lookup table G, a four-input lookup table F, a four-input lookup table F, and a four-input lookup table F. Input multiplexer H1, three-input lookup table H, two-input multiplexer X, two-input multiplexer Y; the sequential logic part mainly includes four-input multiplexer DIN, four-input multiplexer SR, four-input multiplexer EC, four-input multiplexer DX, four-input multiplexer DY, two-input multiplexer KY, two-input multiplexer EY, two-input mult...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More