Method for realizing bare nucleus software debugging in multicore processor

A technology for multi-core processors and debugging tasks, applied in the field of communications, can solve problems such as inability to debug multi-core processors, and achieve the effects of facilitating development and debugging, enhancing competitiveness, and improving satisfaction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

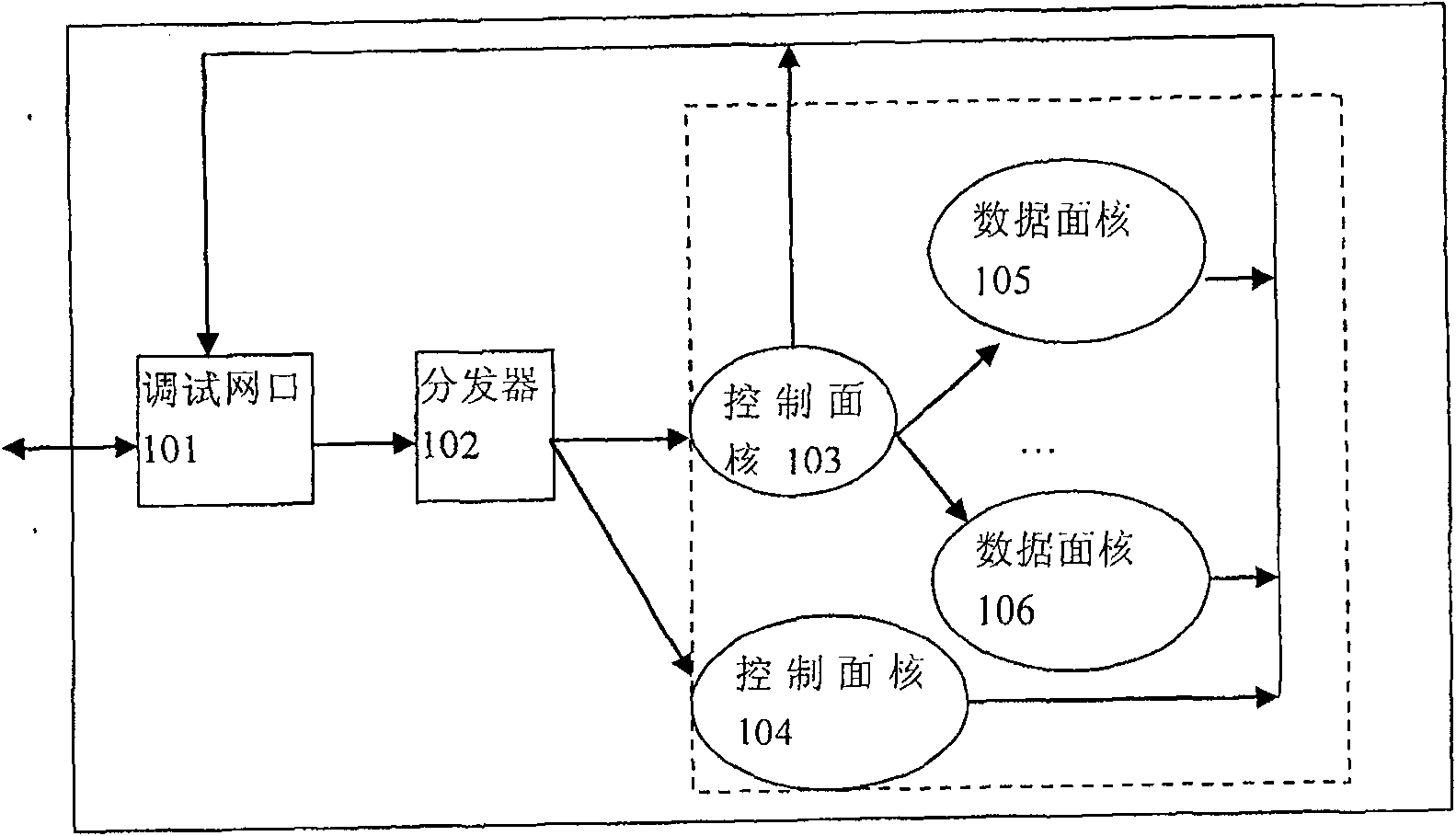

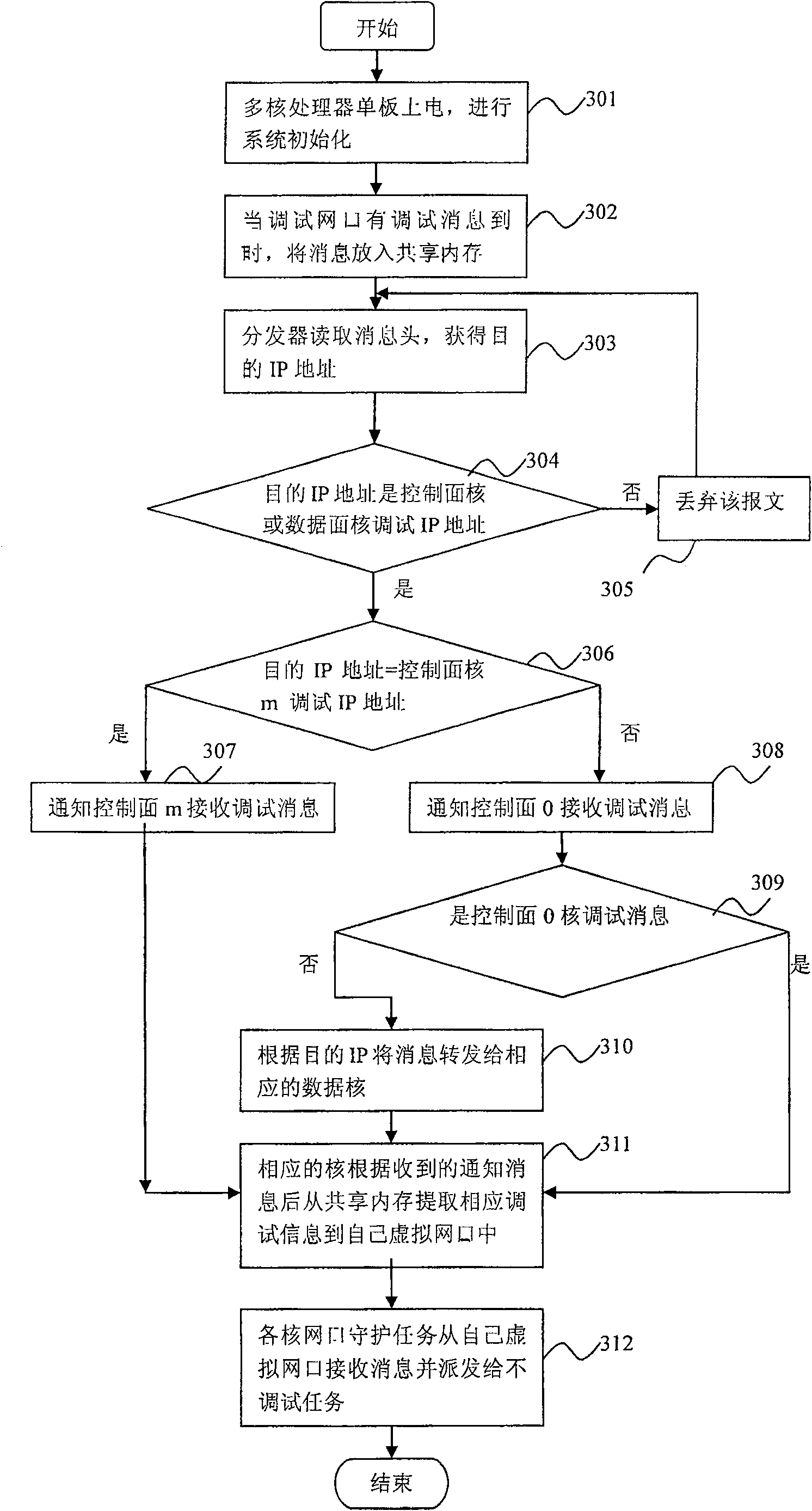

[0034] When the multi-core processor is limited by the allocation of IP addresses, the following methods can be used: image 3 As shown in the software debugging scheme, correspondingly, the debugging single board of the multi-core processor adopts the following figure 1 Structure setup shown. With this implementation method, the control plane core needs to be used as an agent to distribute the debugging request information to the data plane core for the second time, such as image 3 The control plane core 103 in the network acts as a proxy. When the distributor extracts the destination IP address and judges that the IP address is the same as the IP address of the data plane core (105, 106), the distributor will redistribute the debugging notification information to the data plane core through the proxy of the control plane core 103 (105, 106). If after the distributor extracts the destination IP address, it judges that the IP address is the same as the IP address of the co...

Embodiment 2

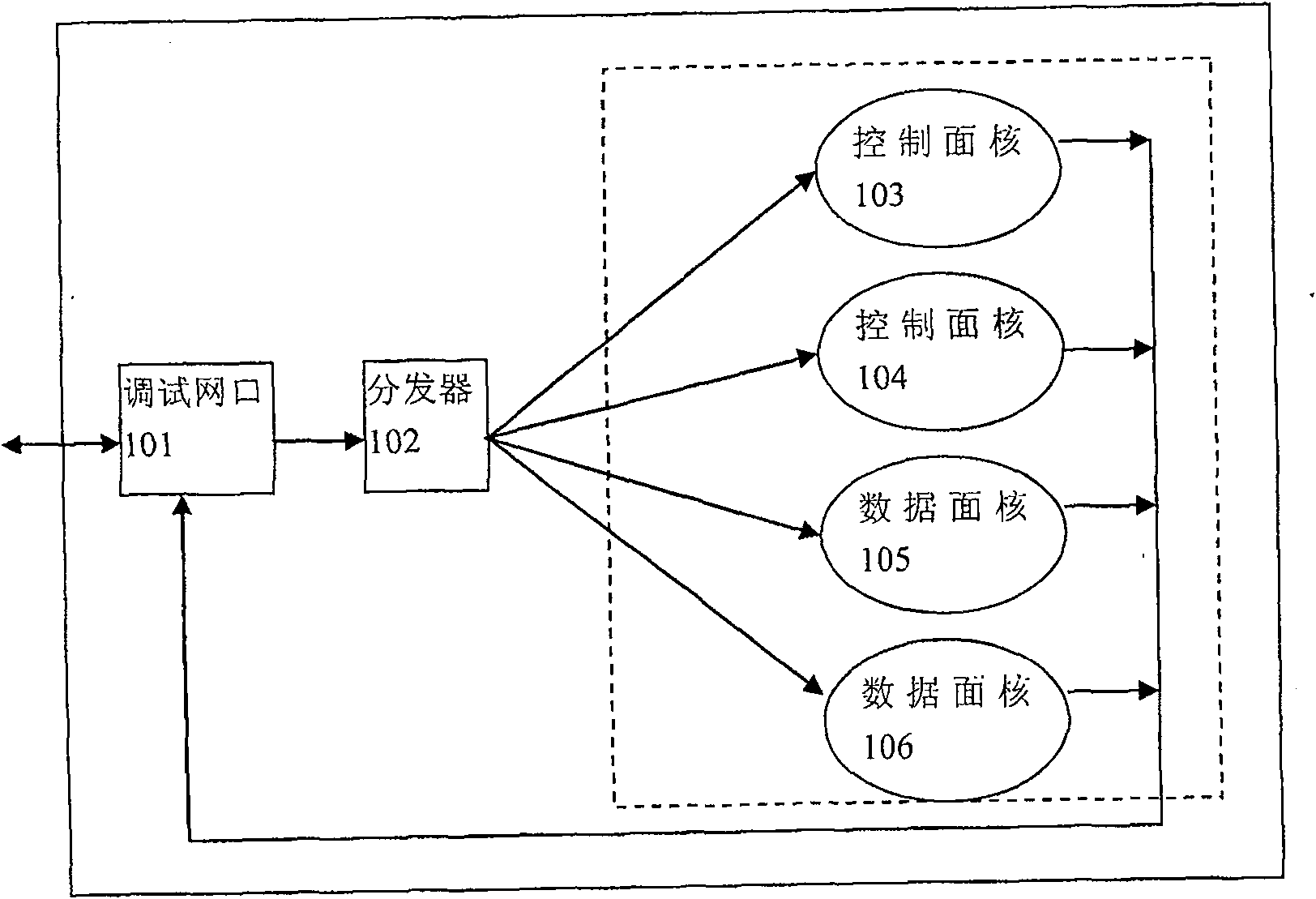

[0054] When the multi-core processor is not limited by the number of IP addresses, you can use the following Figure 4 As shown in the software debugging scheme, correspondingly, the debugging single board of the multi-core processor adopts the following figure 2 Structure setup shown. With this implementation method, the control plane core does not need to act as a proxy. After the distributor extracts the destination IP address, it determines that the IP address is related to one or more of the control plane cores (103, 104) or data plane cores (105, 106). When the IP addresses are the same, the distributor directly sends debugging notification information to the control plane cores (103, 104) or data plane cores (105, 106).

[0055] The second embodiment is described in detail below, the method for realizing bare-core software debugging in the multi-core processor of the present invention, please refer to the attached Figure 4 , and its implementation process includes t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More