Method for constructing time invariant LDPCC based on PEG algorithm, and encoder/decoder

A technology of LDPC code and construction method, applied in the field of construction method of LDPC code and its codec, to achieve the effects of excellent loop characteristics and code spacing characteristics, superior performance, and excellent performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0073] In view of the present situation of the construction method of the LDPCC code, in order to realize the construction of the time-invariant LDPCC code with controllable parameters, this embodiment describes a new method for constructing the time-invariant LDPCC code. This method is different from other construction methods of LDPCC codes at present. Its biggest feature is to construct regular and irregular time-invariant LDPCC codes by using the maximum loop optimization criterion. The method includes the following five main steps, and the main steps are as follows: Figure 6 Shown:

[0074] step 1:

[0075] The parameters of the LDPCC code are unchanged during initialization: it is determined as k input n output LDPCC code, and its parity check matrix H TThe constraint length is M; determine the dimension distribution function of the variable node of the LDPCC code, and the dimension distribution function satisfies the constraint condition: the number of different dim...

Embodiment 2

[0180] This embodiment implements simple convolutional code encoding of LDPCC codes. Figure 9 Shows the structure of an encoder with a code rate 1 / 3 LDPCC code including: input (u(D)), systematic sequence output (v 1 (D)), check sequence output (v 2 (D), v 3 (D)), delay line (D register), multiplexer (MULTIPLEXER), exclusive OR gate (XOR), the delay line of constant length realizes the delay of the input source and the feedback delay of the output bit; the source bit is delayed Lines form the system sequence output; the time-invariant multiplexer multiplexes the input bits and output feedback bits on the delay line, and then forms the check sequence output through exclusive OR gate modulo 2 addition. The length of the delay line, the connection relationship of the multiplexer and the connection relationship of the XOR gate of a typical LDPCC encoder are periodically changed, and the present invention uses the constant delay line length, the connection relationship of the mu...

Embodiment 3

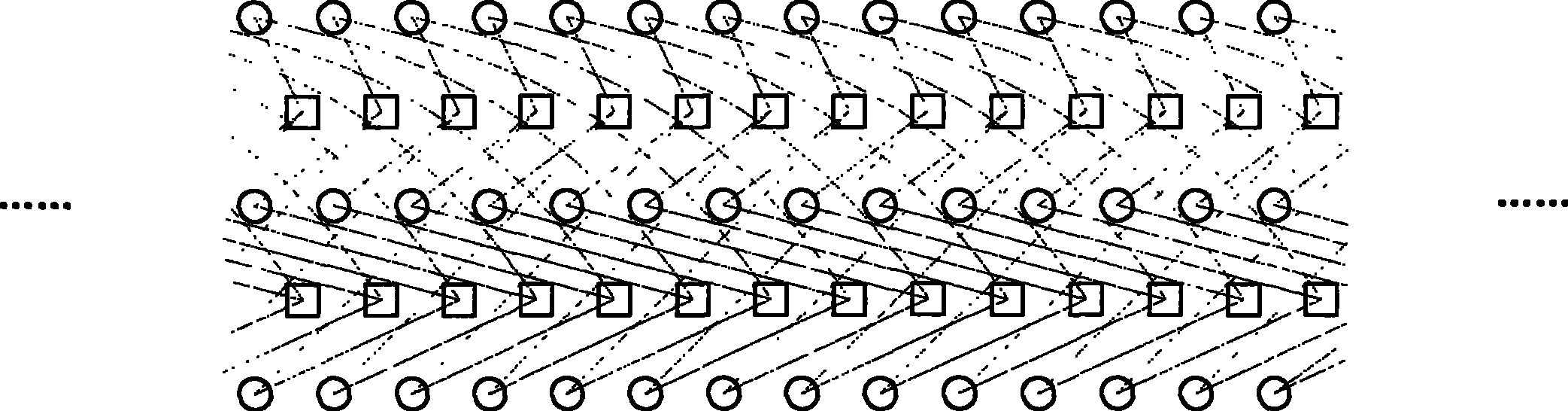

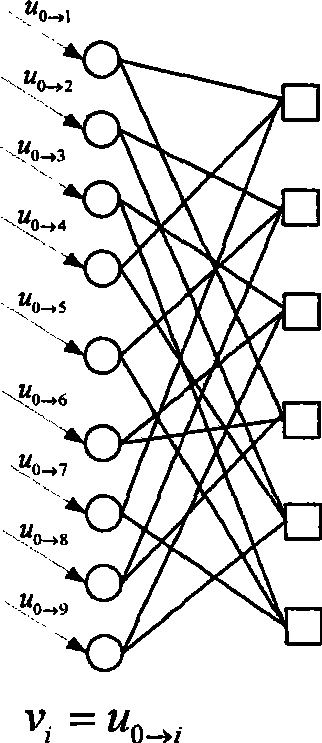

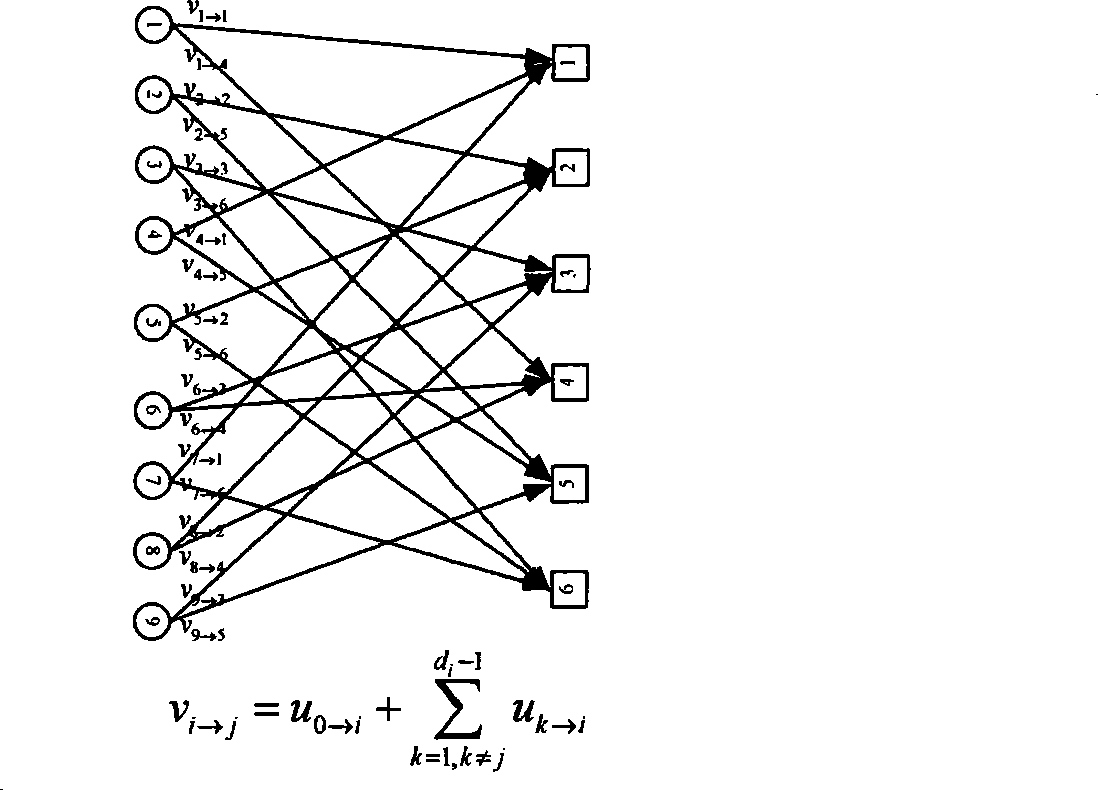

[0183] This embodiment implements pipeline decoding of LDPCC codes. The pipelined LDPCC code decoder adopts a structure similar to that of the check matrix HT, including VNU computing units, CNU computing units, channel information and decoding information stored in FIFO; it consists of a time-invariant VNU computing unit and a time-invariant The invariant CNU operation unit is constantly connected to the channel information and the decoding information is stored in the FIFO to form a sub-decoder; multiple sub-decoders are serially cascaded, and the number of sub-decoders is equal to the sum-product algorithm The number of iterations; the channel information and the decoding information pass through each sub-decoder in a pipelined manner to complete the decoding; the output of each sub-decoding unit is the input of the subsequent sub-decoding unit; except for the first sub-decoding unit The input of the coding unit is the likelihood ratio of the channel information, and the ou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More