Power supply wiring configuration in semiconductor integrated circuit

A power wiring and integrated circuit technology, applied in the direction of semiconductor devices, circuits, semiconductor/solid-state device components, etc., can solve problems such as the decline in drive power supply performance, achieve the effect of suppressing the increase of the circuit area and ensuring the connection area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

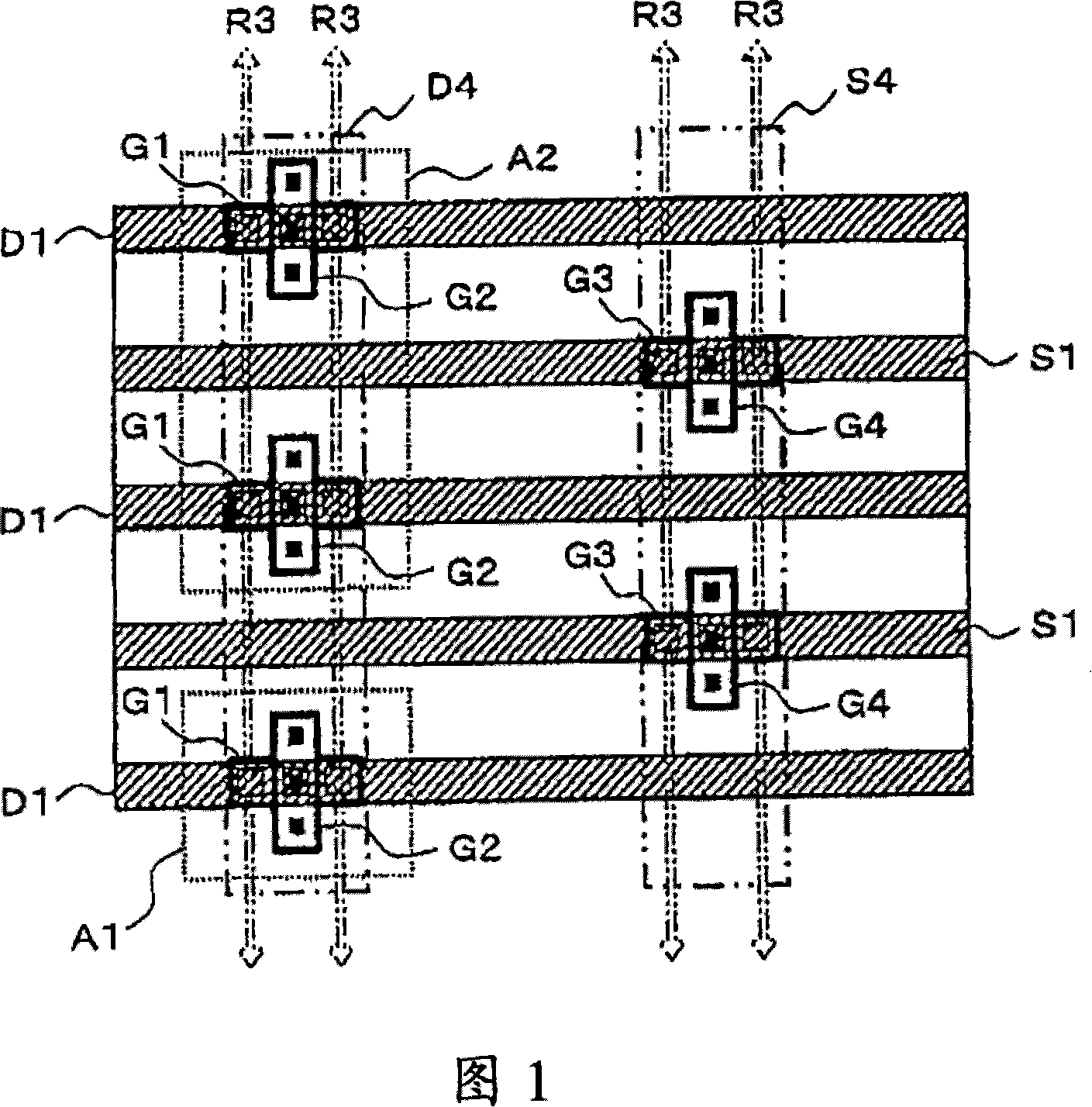

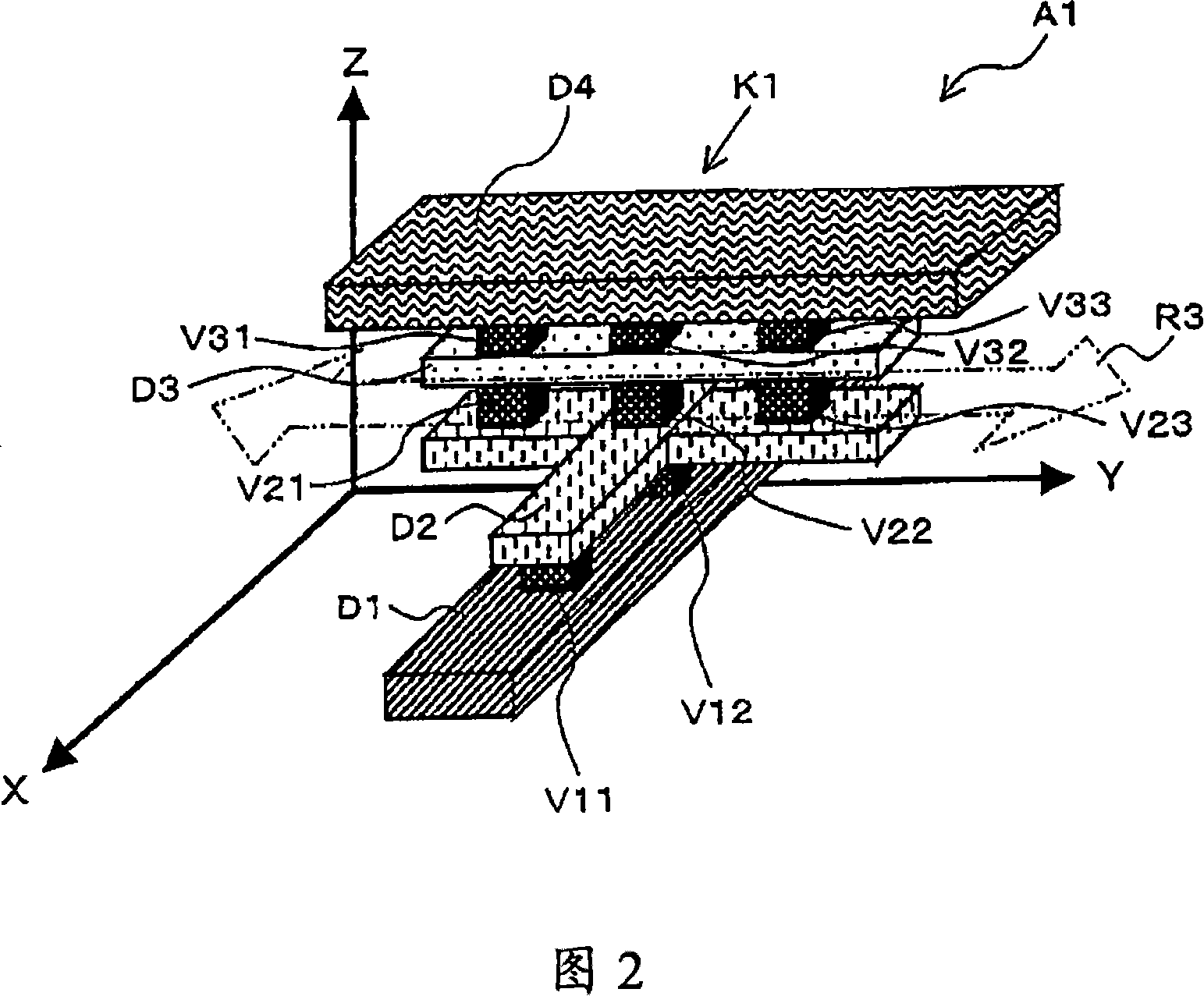

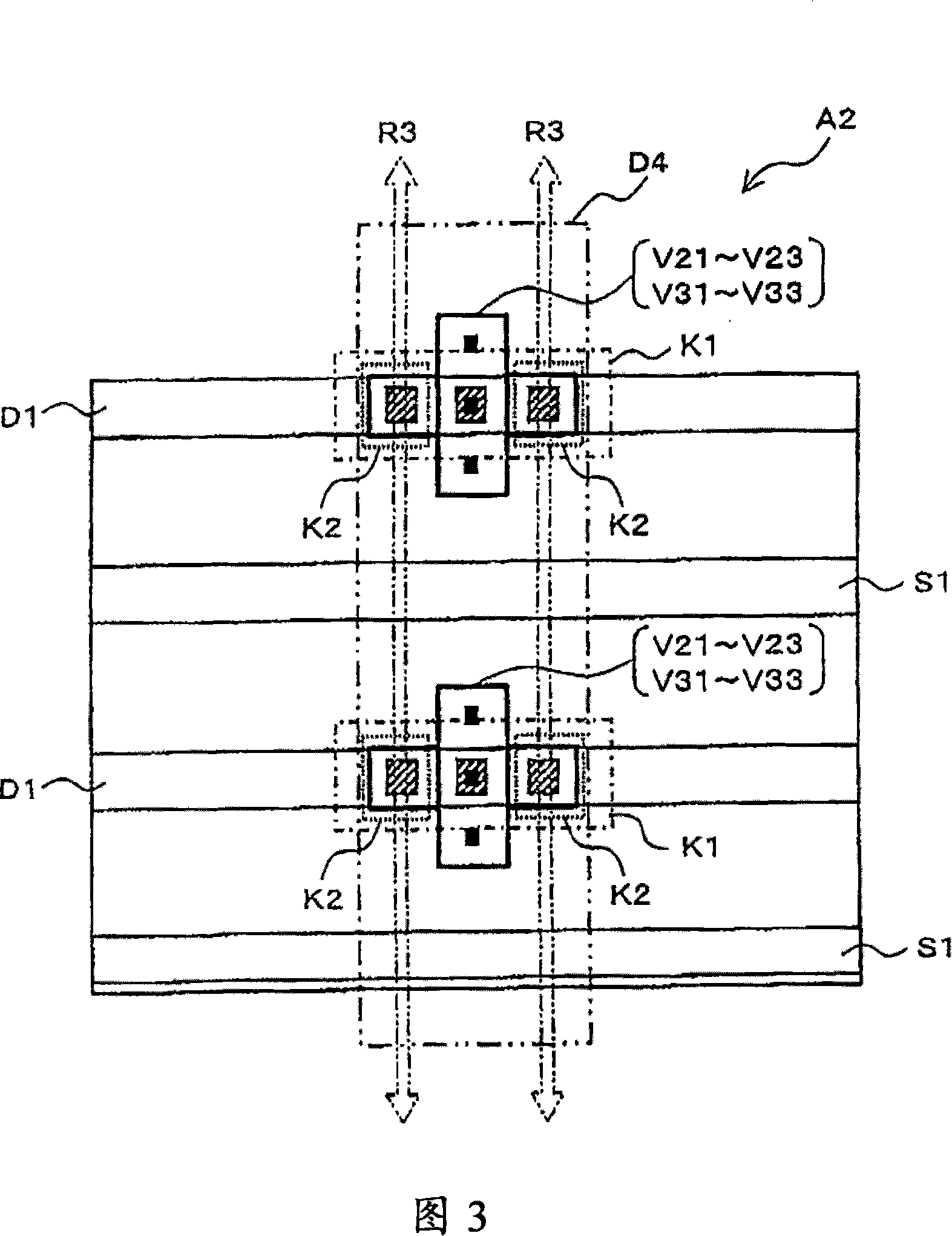

[0033] In FIG. 1 , D1 indicates the VDD power supply wiring (hereinafter, referred to as the lowest VDD power supply wiring) arranged in the lowest wiring layer, and S1 indicates the VSS power supply wiring (hereinafter, referred to as the lowest VSS supply wiring) arranged in the lowest wiring layer. power wiring). The lowest VDD power supply wiring D1 and the lowest VSS power supply wiring S1 extend along the first direction X, and both the power supply wirings D1, S1 are laid alternately along the second direction Y (perpendicular to the first direction) at the same interval. D4 denotes a VDD power supply wiring (hereinafter, referred to as the highest VDD power supply wiring) arranged in the highest wiring layer, and S4 denotes a VSS power supply wiring (hereinafter, referred to as the highest VSS power supply wiring) arranged in the highest wiring layer. The highest VDD power supply wiring D4 and the highest VSS power supply wiring S4 extend along the second direction Y, ...

no. 2 example

[0046] 5 is a power wiring diagram of a semiconductor integrated circuit according to a second embodiment of the present invention. Descriptions of regions having the same structure as those of the first embodiment will be omitted. In FIG. 5, C1 and C2 denote standard cells including transistors. The branch power supply wiring D11 and the branch power supply wiring D12 electrically connected in the same layer and connected to the source of the P-channel transistor at the same potential as the power supply wiring D1 of the lowest layer are laid in the cell C1 along the second direction Y, and Similarly, branch power supply wiring D13 electrically connected within the same layer and connected to the source of the P-channel transistor at the same potential as the lowest power supply wiring D1 is laid in the cell C2 along the second direction Y. The power supply wiring group g1 is a power supply wiring composed of a second intermediate wiring layer and a third intermediate wiring...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More