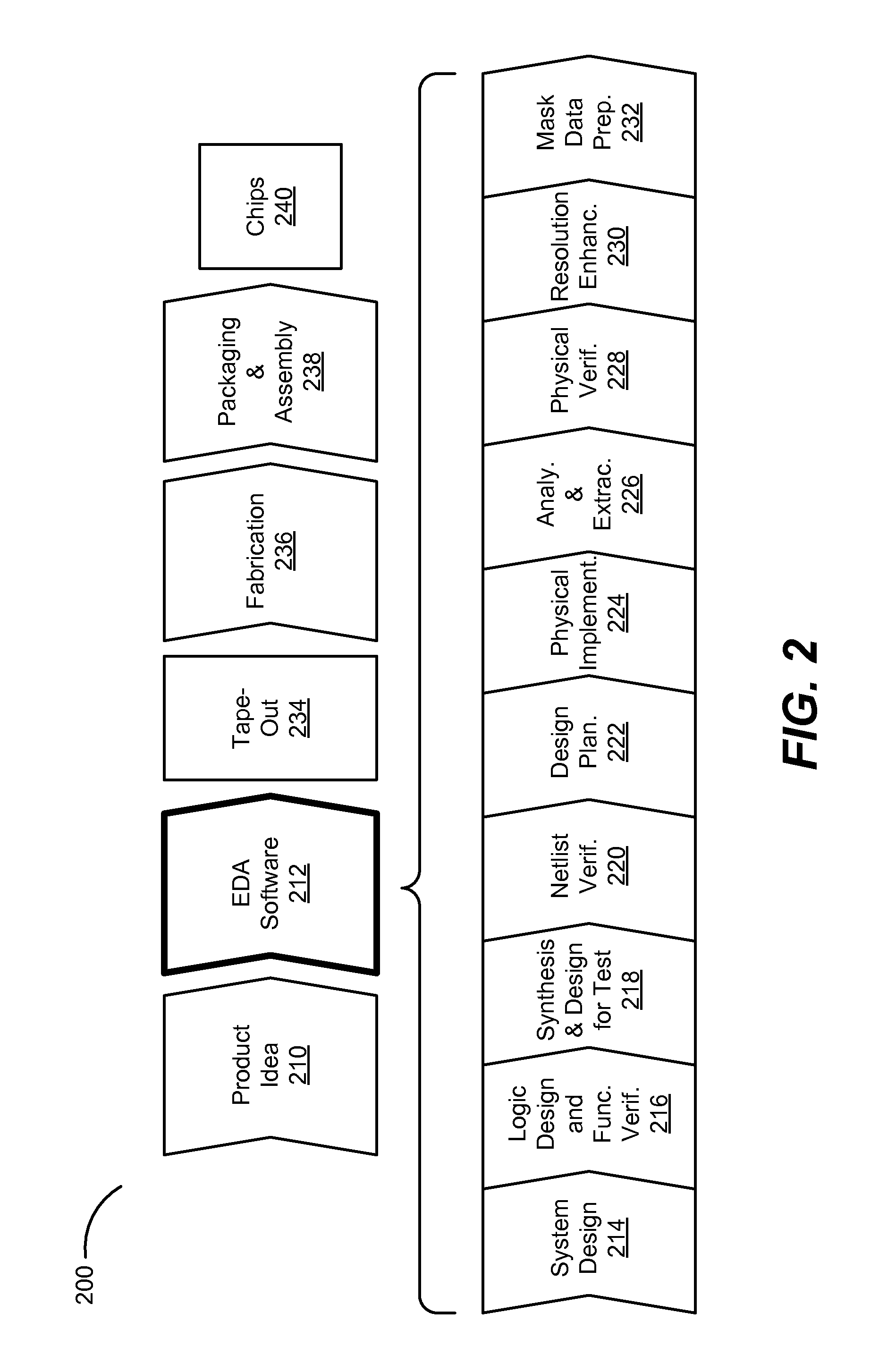

Patents

Literature

292 results about "Power routing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

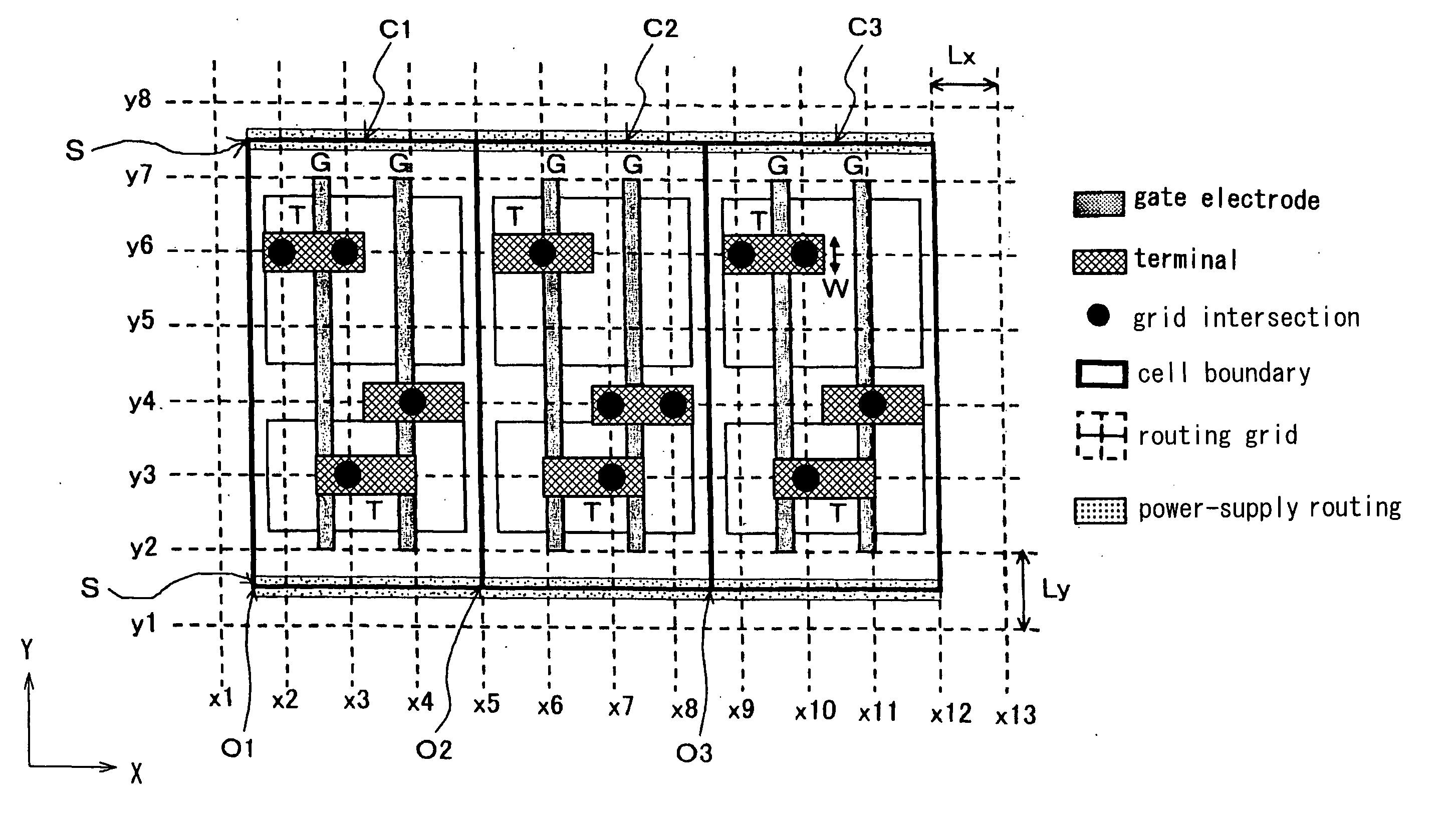

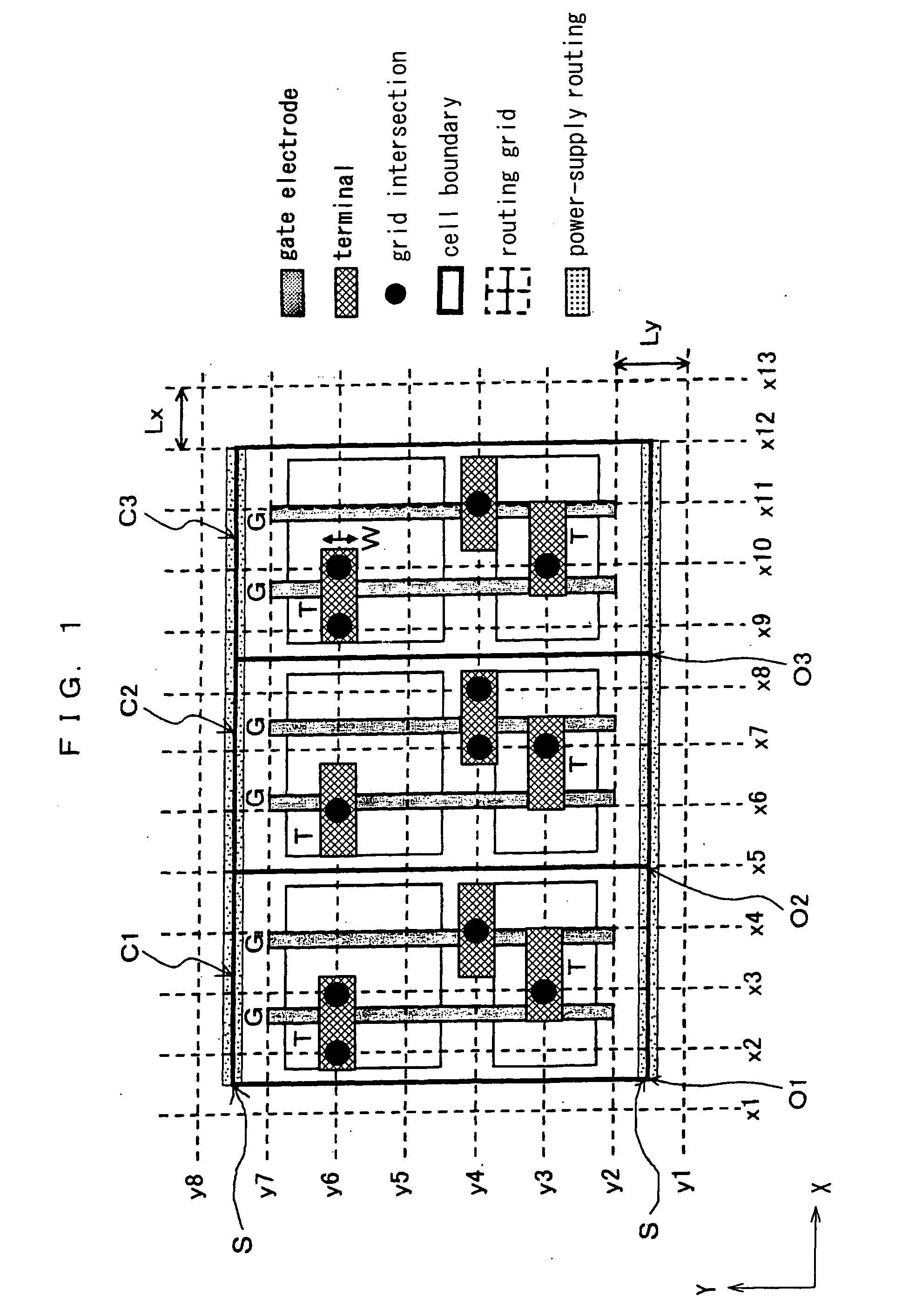

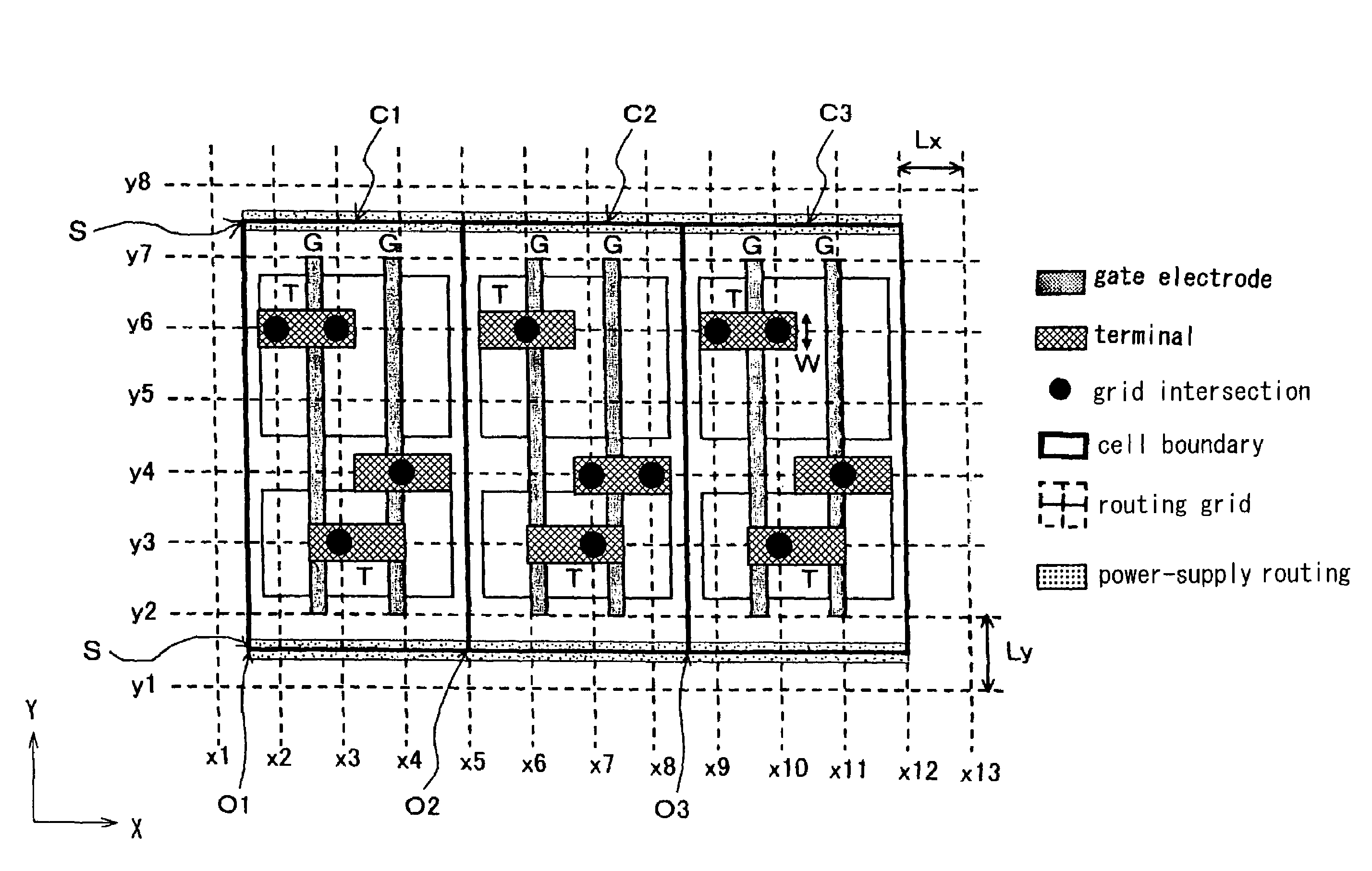

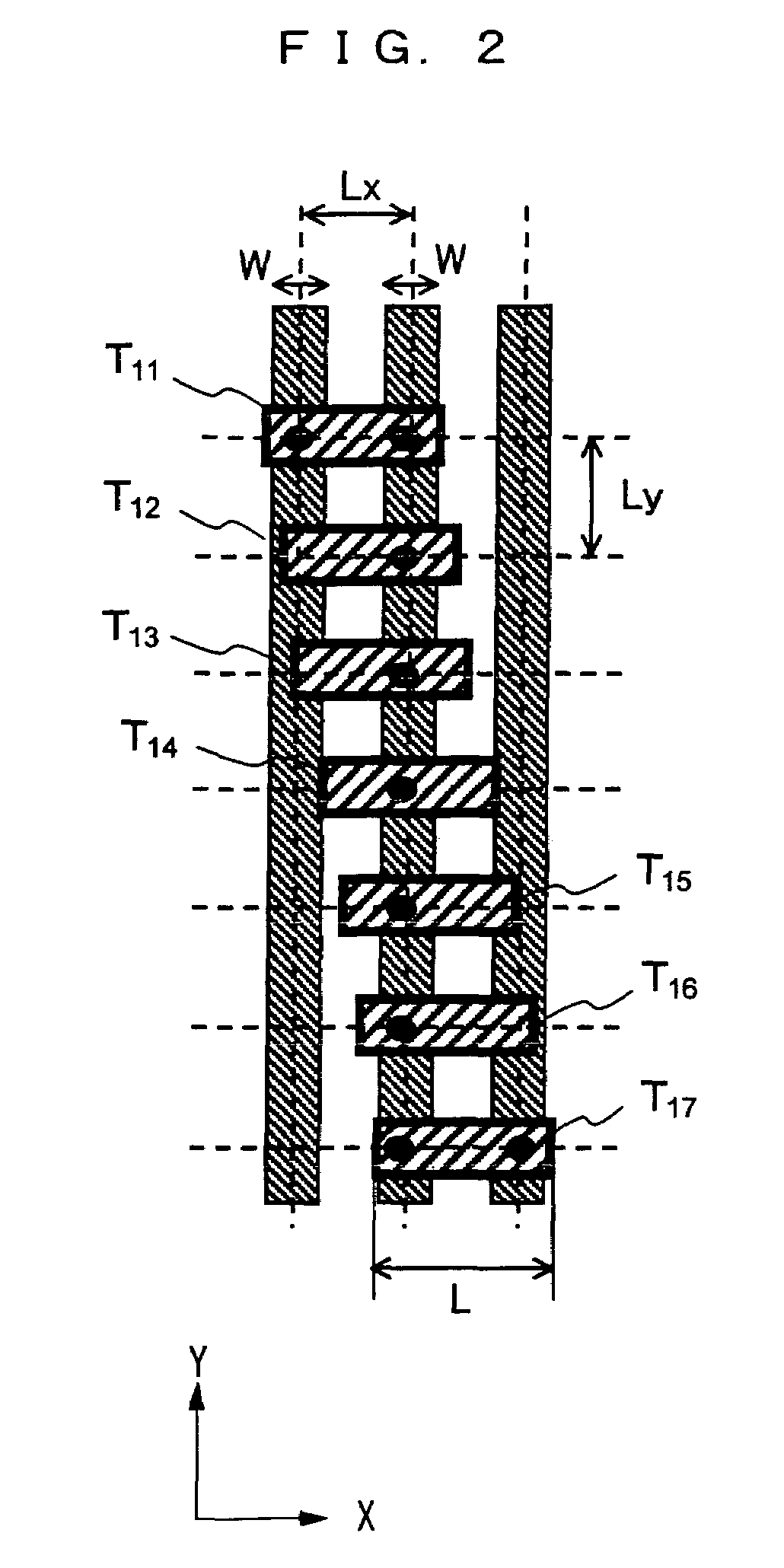

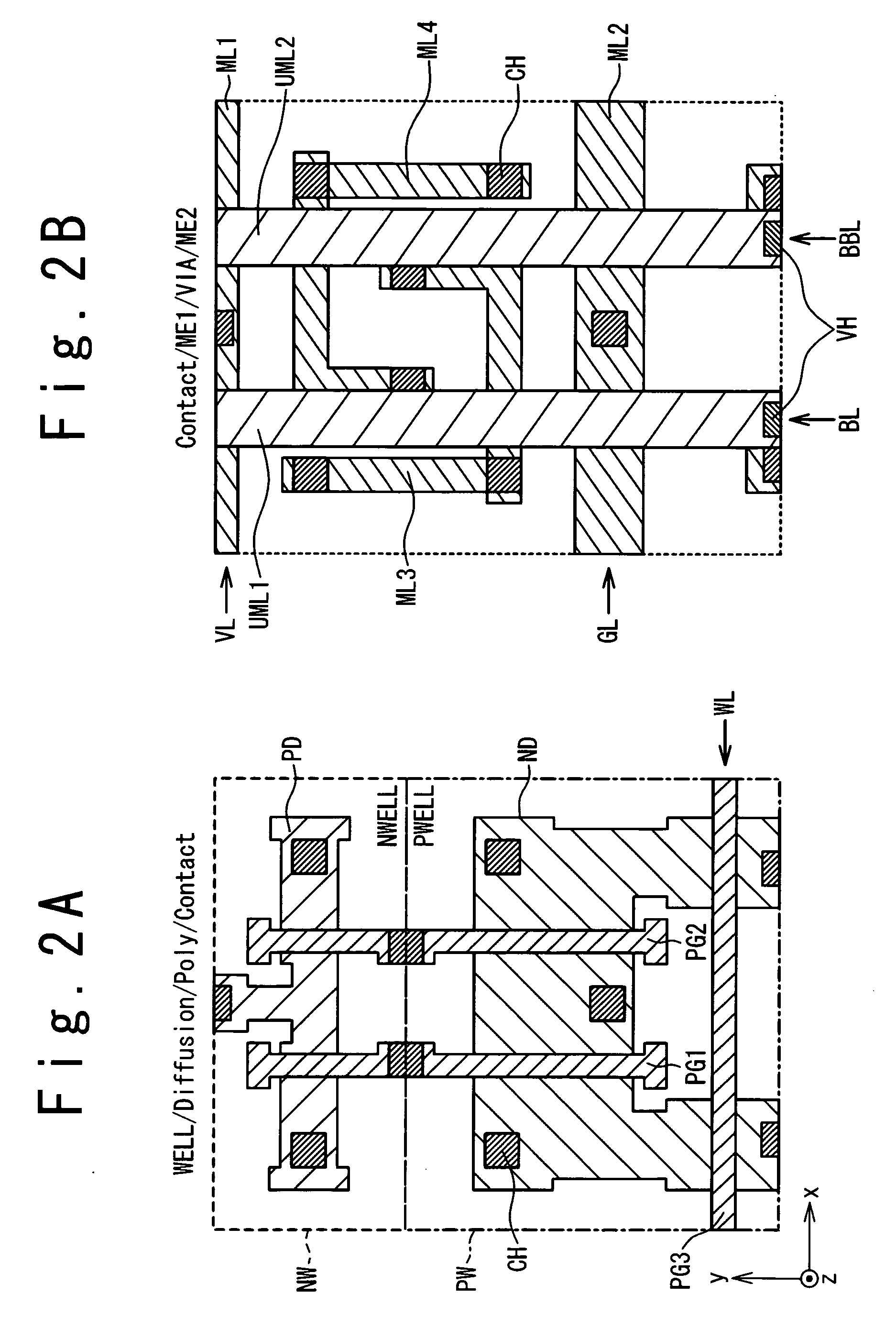

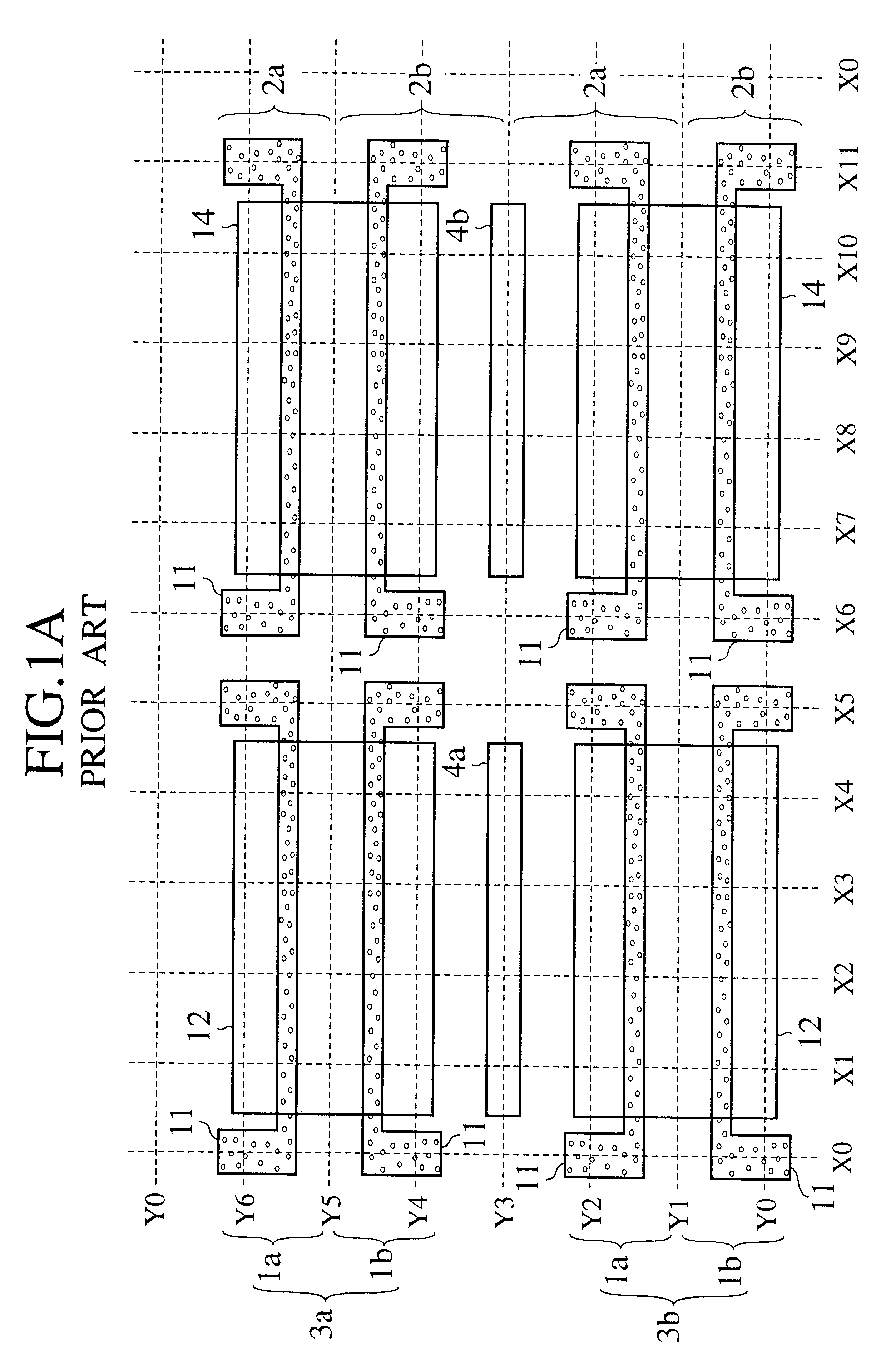

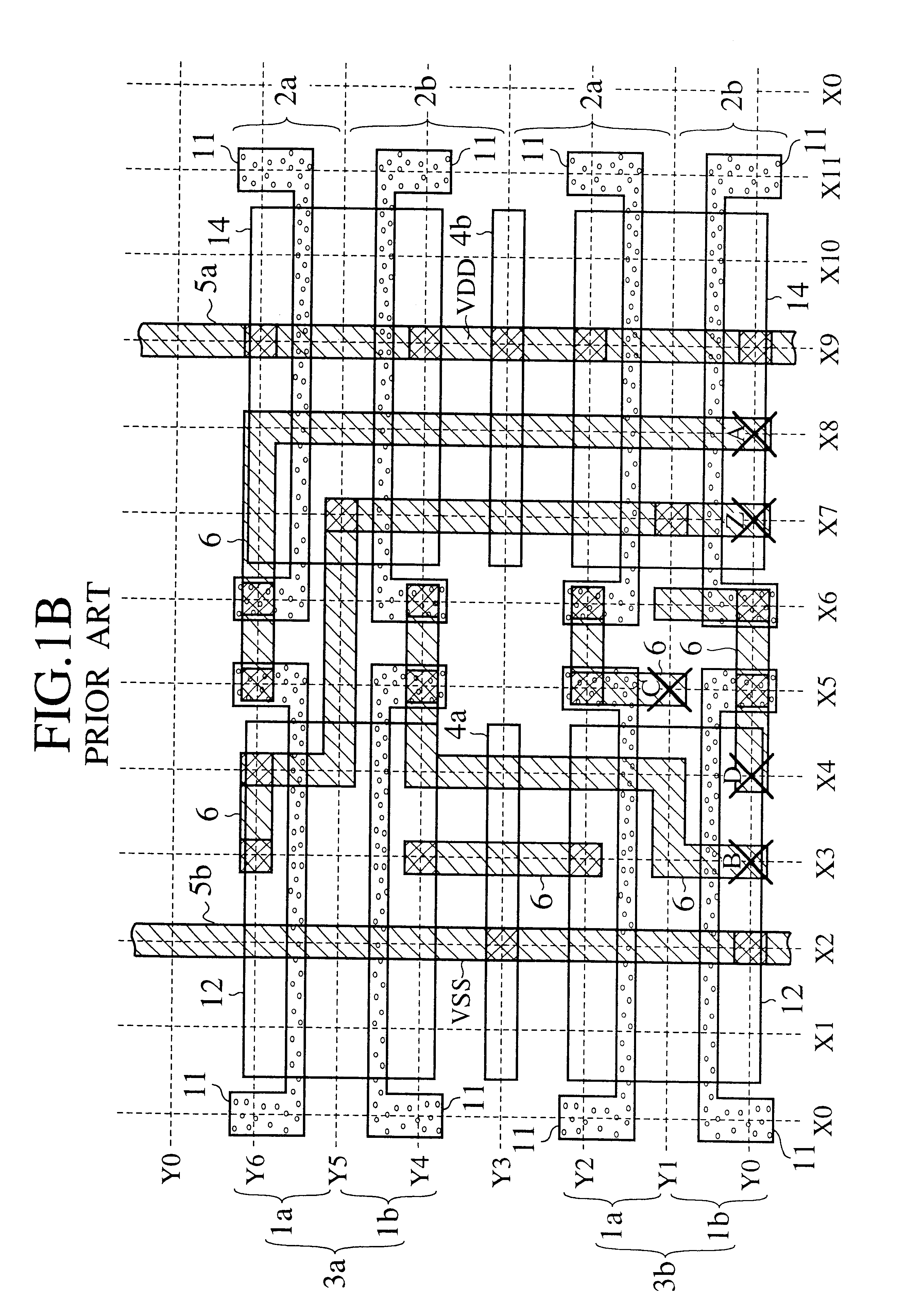

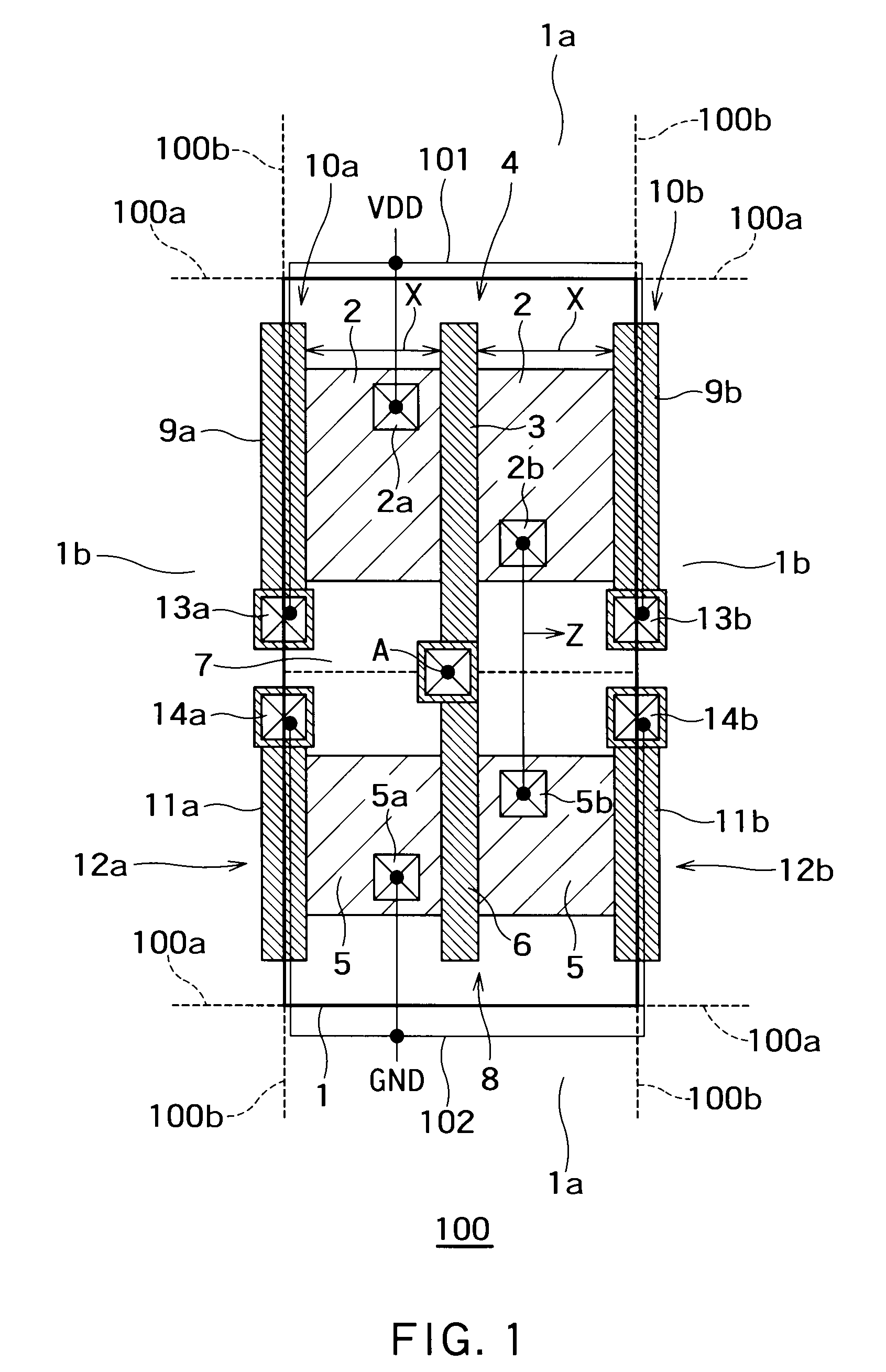

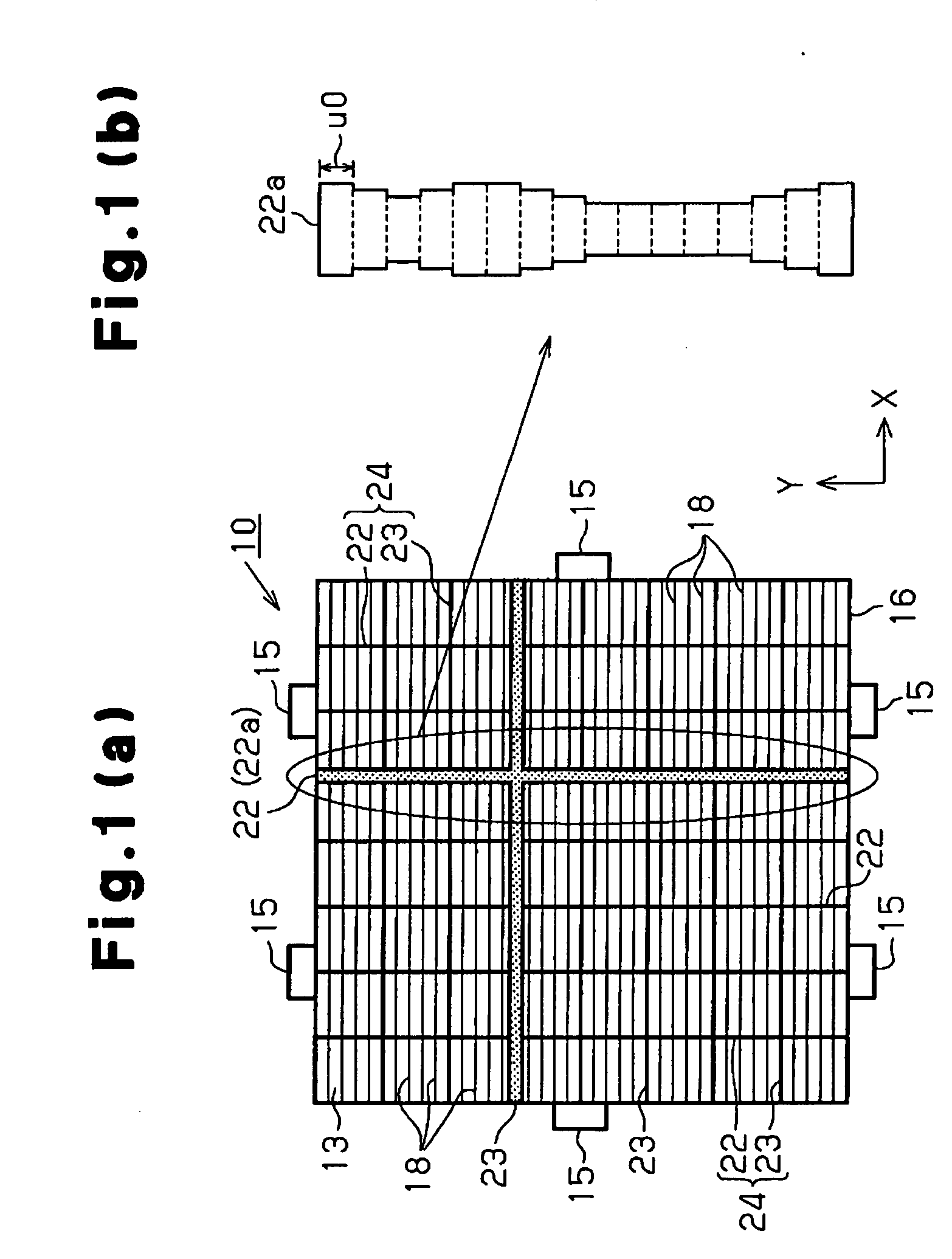

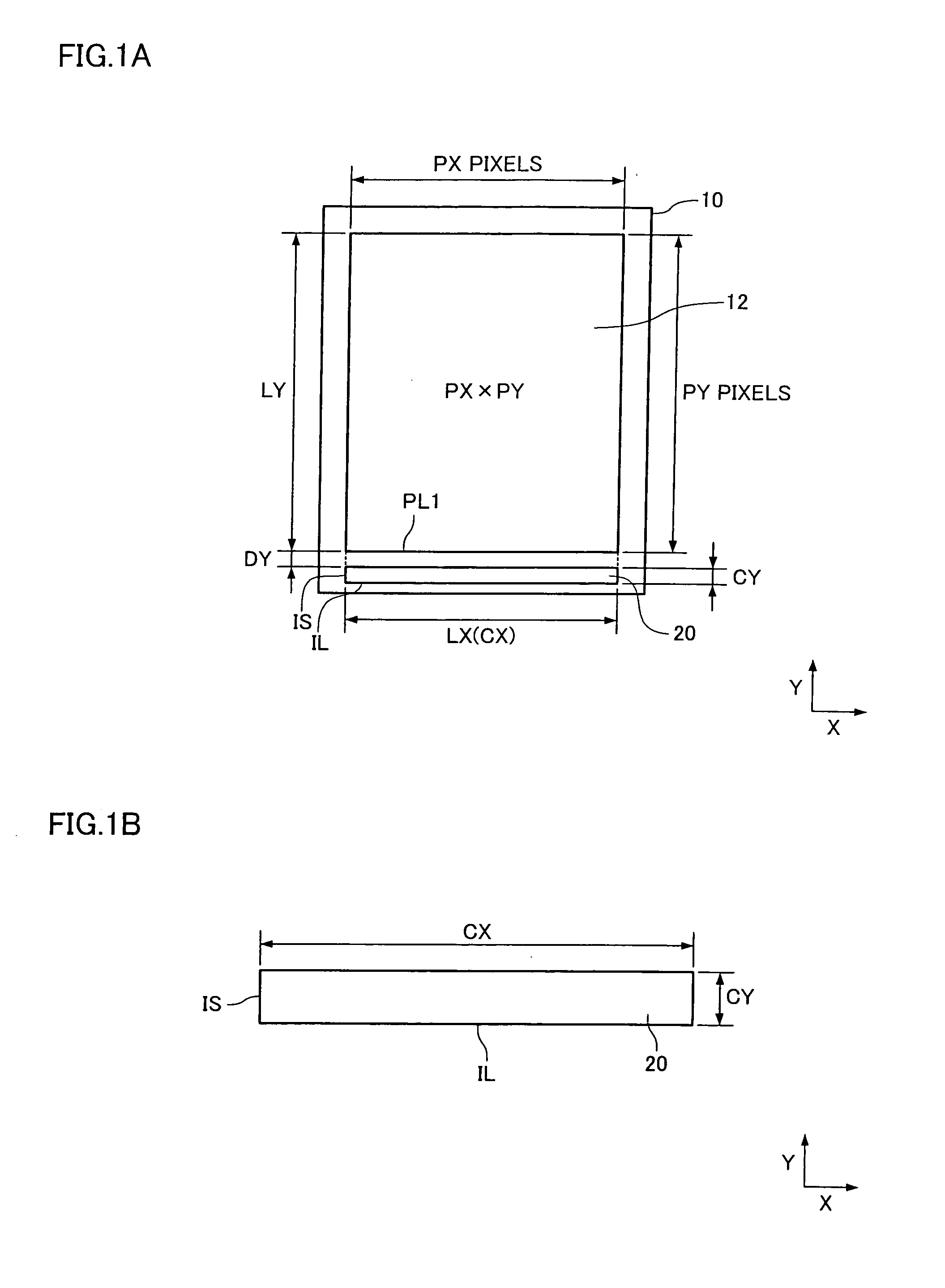

Cell, standard cell, standard cell library, a placement method using standard cell, and a semiconductor integrated circuit

ActiveUS20060136848A1Reducing cell area areaReduce chip areaSolid-state devicesProgram controlEngineeringSemiconductor

A cell according to the present invention comprises a plurality of terminals capable of transmitting an input signal or an output signal and serving as a minimum unit in designing a semiconductor integrated circuit, wherein the plurality of terminals is located on routing grids lined in a Y direction which is a direction vertical to a power-supply wiring of the cell used in automatic placement & routing and has a shape extended in an X direction which is a direction in parallel with the power-supply wiring, more specifically such a shape that, for example, a longer-side dimension of the terminal is equal to “a routing grid interval in the X direction+a wiring width. According to the constitution, a cell area is reduced, which advantageously leads to the reduction of a chip area.

Owner:SOCIONEXT INC

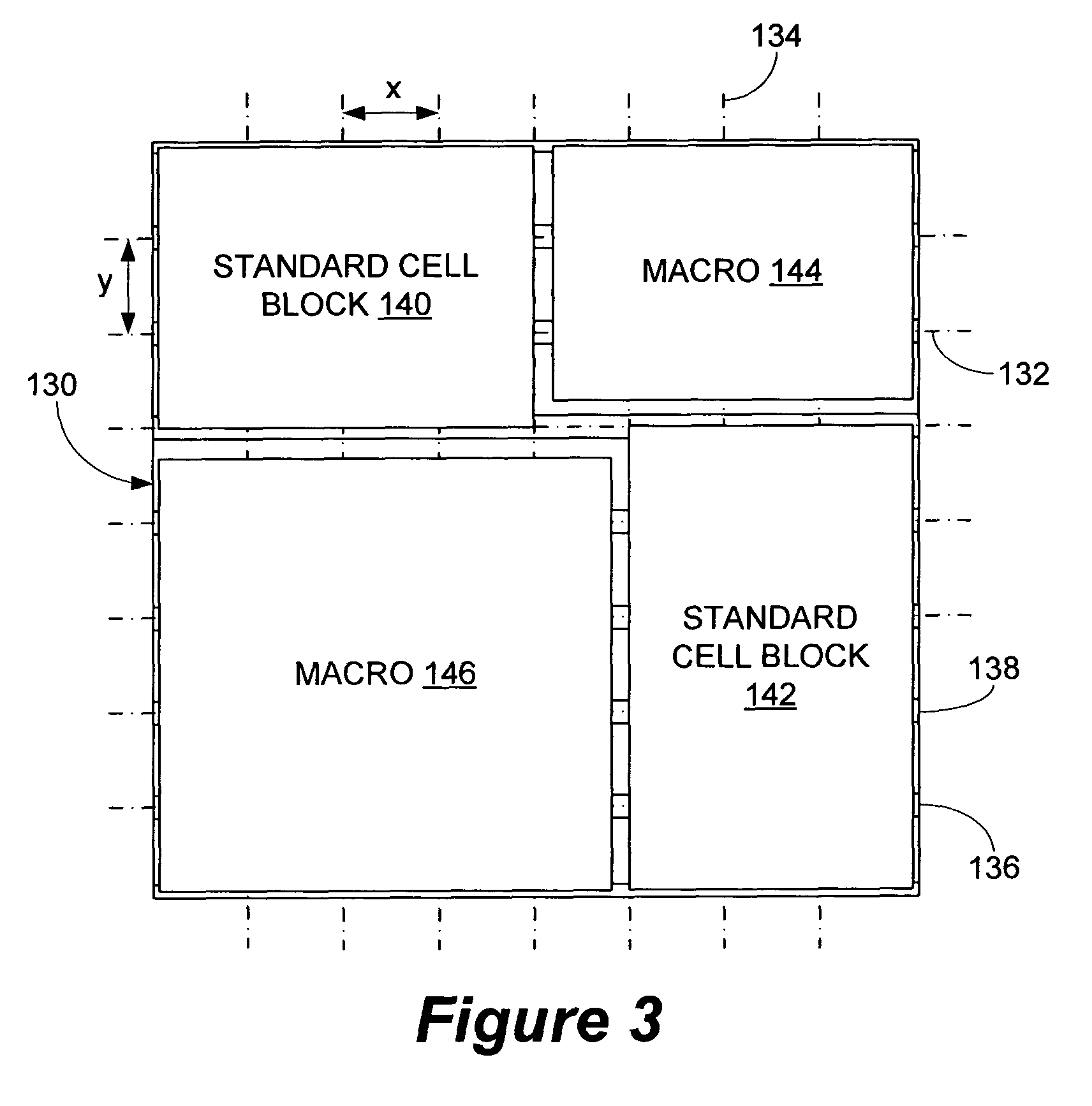

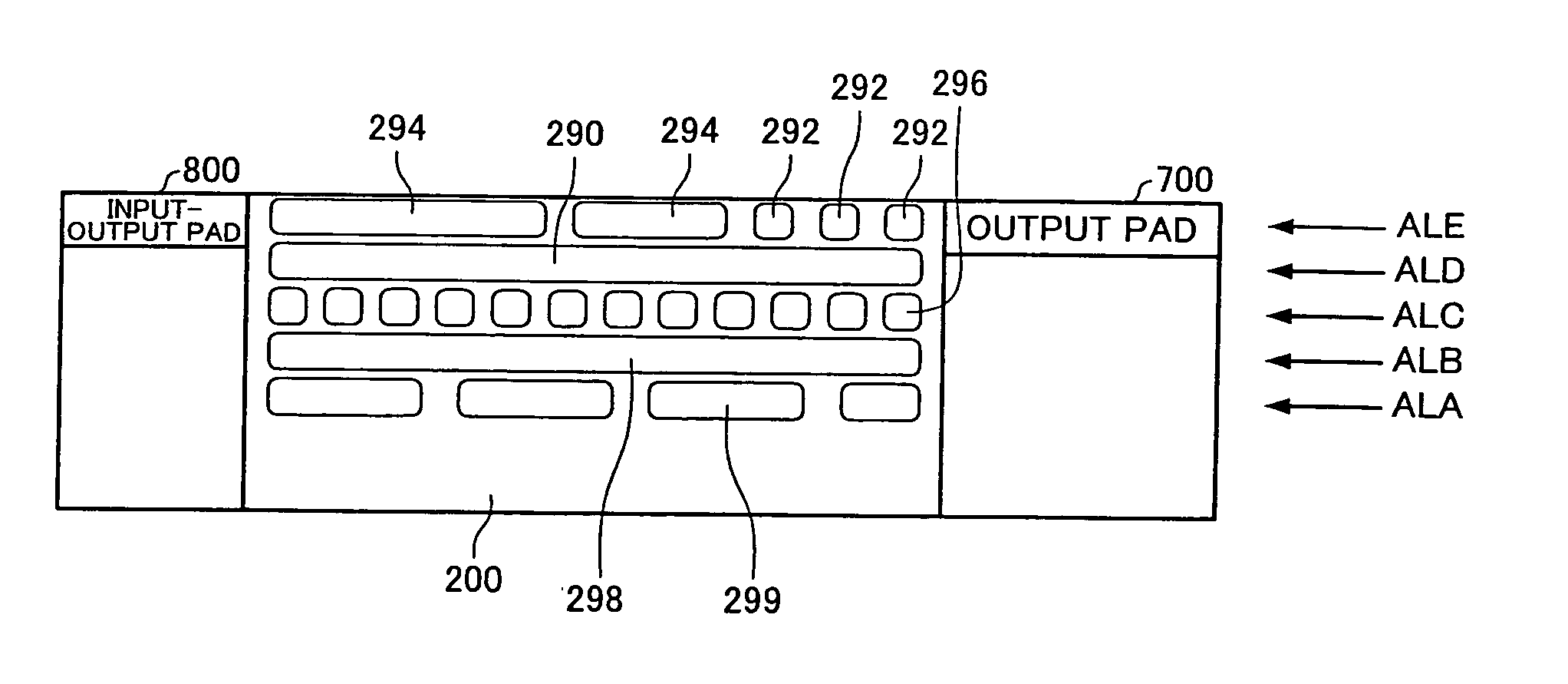

Method and apparatus for power routing in an integrated circuit

A system and method for routing power between circuit blocks in an integrated circuit, such as macros and standard cells. A macro is wrapped in a relatively narrow power interface ring and placed in the integrated circuit such that the lower metal layers of the power interface ring are aligned and in direct contact with the power rails of a standard cell block. A power grid is formed above the macro and the upper metal layers of the power interface ring are coupled to the power grid. The upper power grid is tied either to an outer power bus or directly to power pins in the surrounding I / O ring. Data signals may be routed in the I / O ring space.

Owner:SYNAPTICS INC

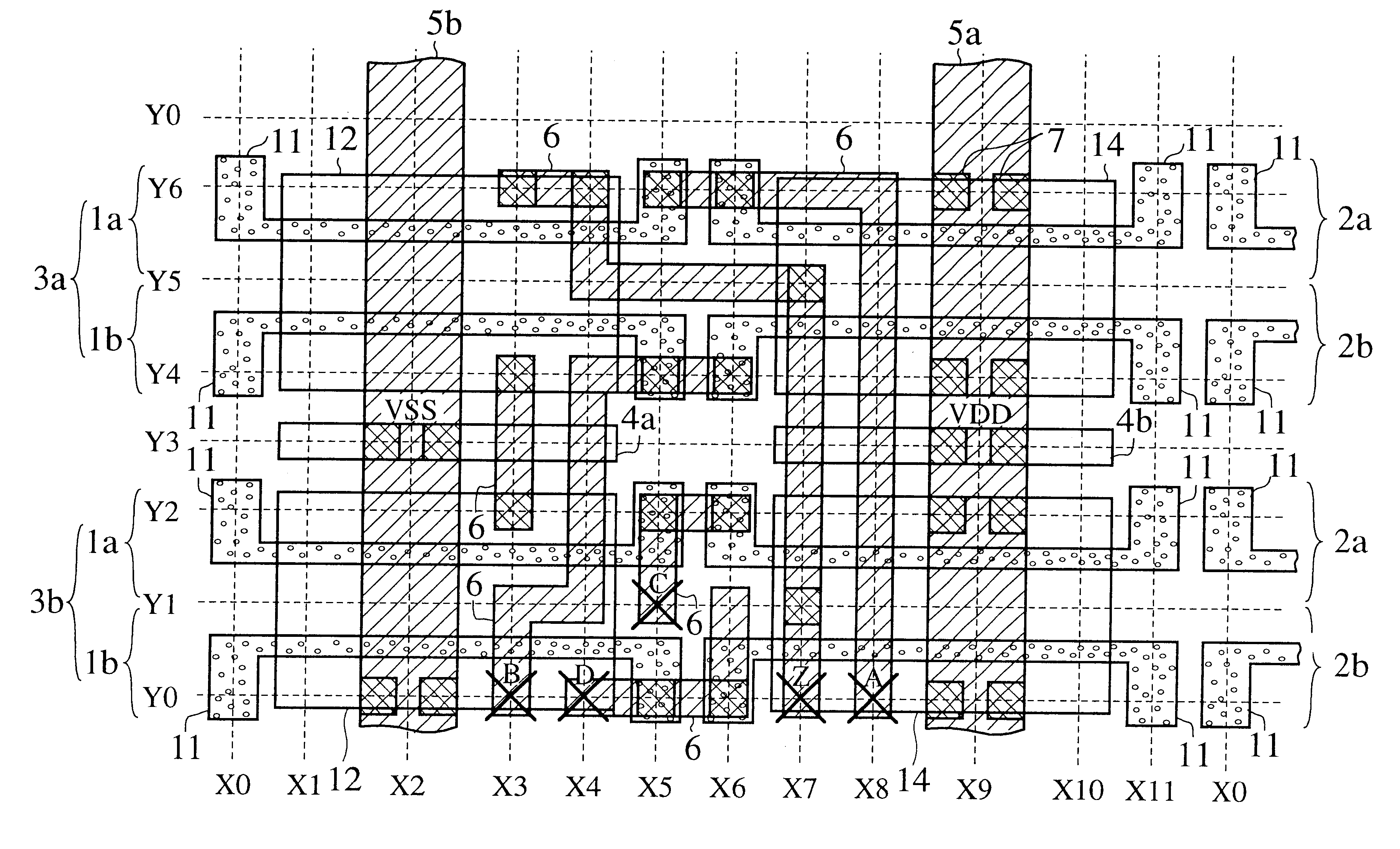

Cell, standard cell, standard cell library, a placement method using standard cell, and a semiconductor integrated circuit

ActiveUS7503026B2Reducing cell area and chip areaHigh precisionSolid-state devicesComputer aided designElectrical batteryEngineering

A cell according to the present invention comprises a plurality of terminals capable of transmitting an input signal or an output signal and serving as a minimum unit in designing a semiconductor integrated circuit, wherein the plurality of terminals is located on routing grids lined in a Y direction which is a direction vertical to a power-supply wiring of the cell used in automatic placement & routing and has a shape extended in an X direction which is a direction in parallel with the power-supply wiring, more specifically such a shape that, for example, a longer-side dimension of the terminal is equal to “a routing grid interval in the X direction+a wiring width. According to the constitution, a cell area is reduced, which advantageously leads to the reduction of a chip area.

Owner:SOCIONEXT INC

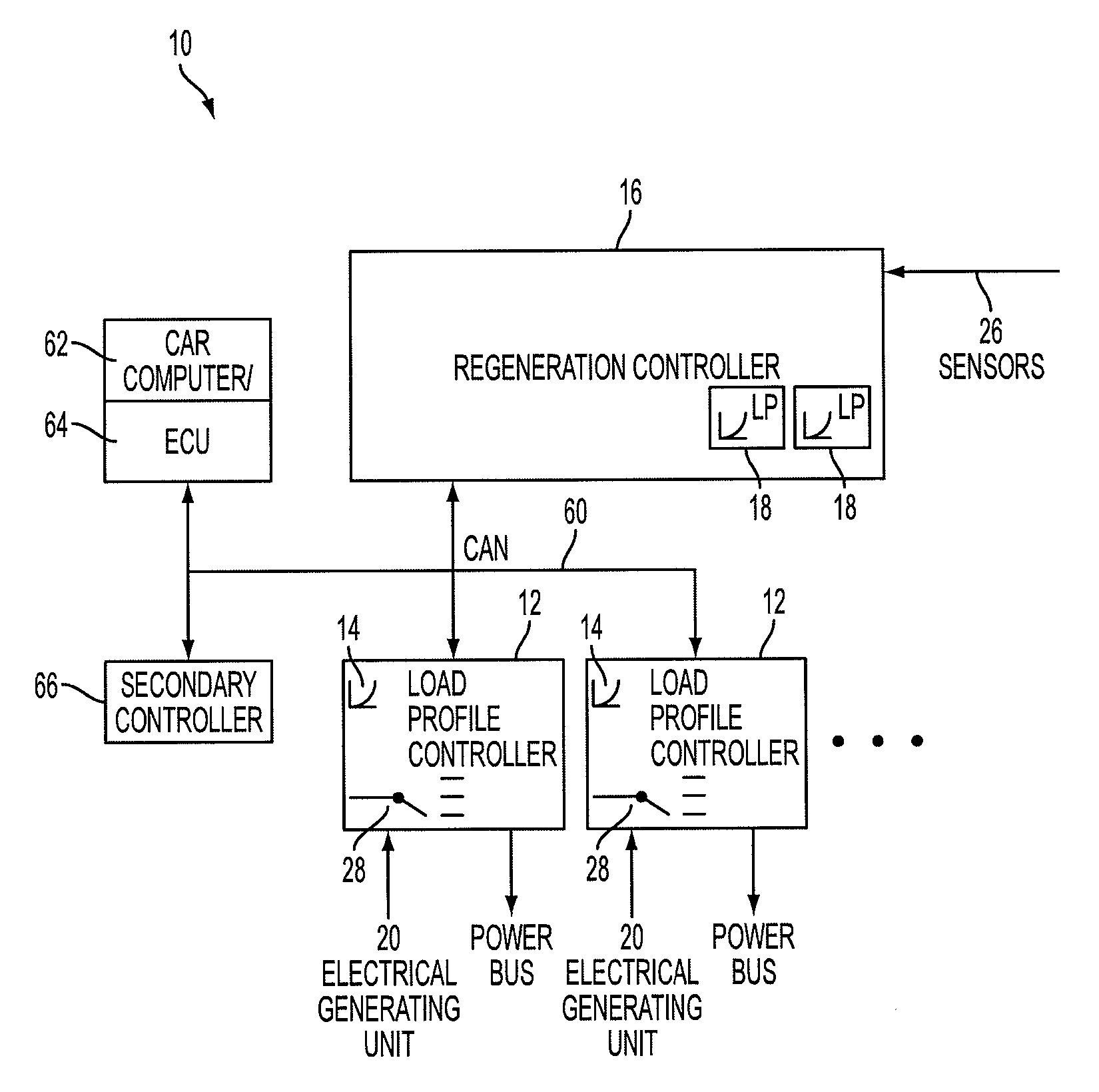

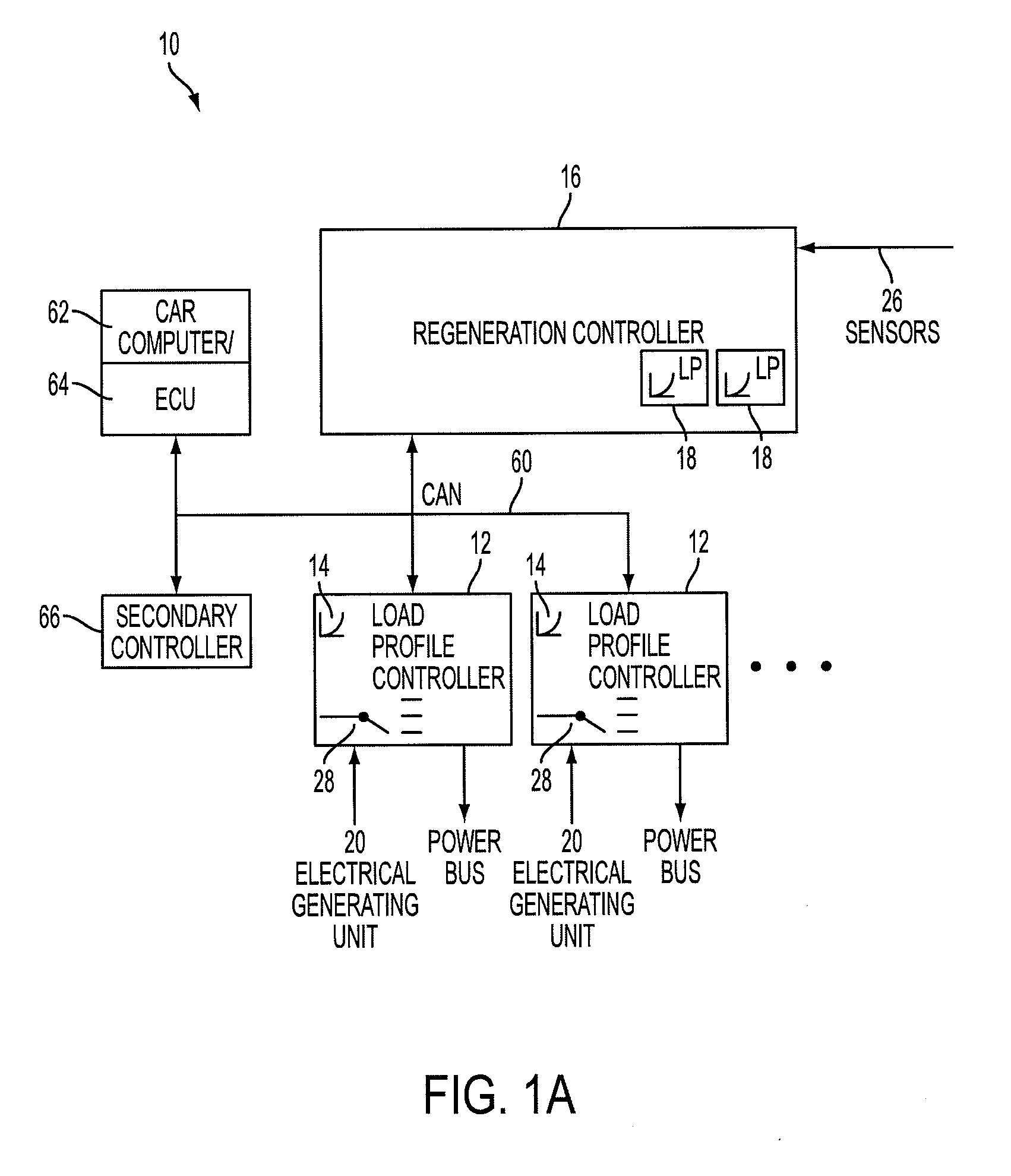

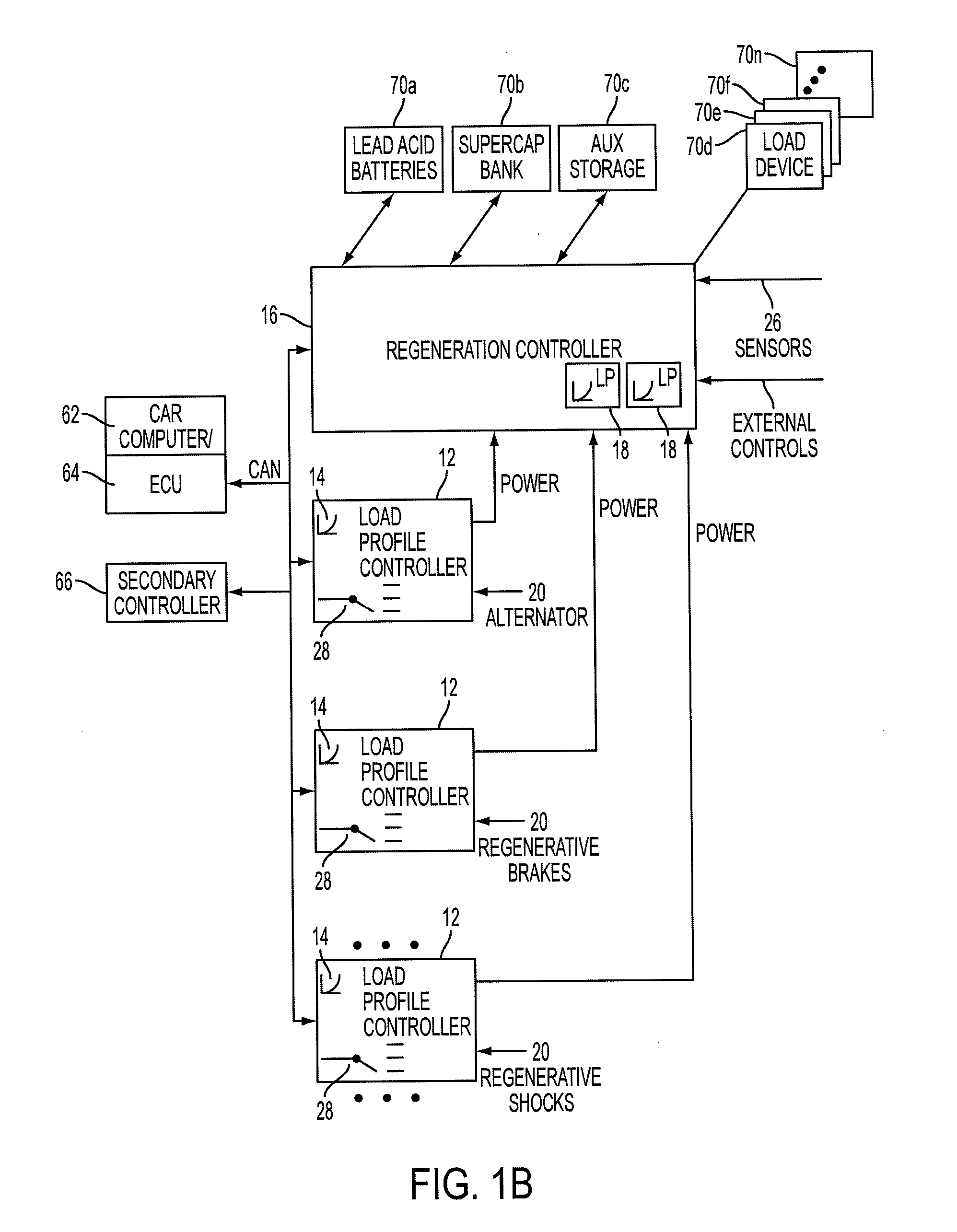

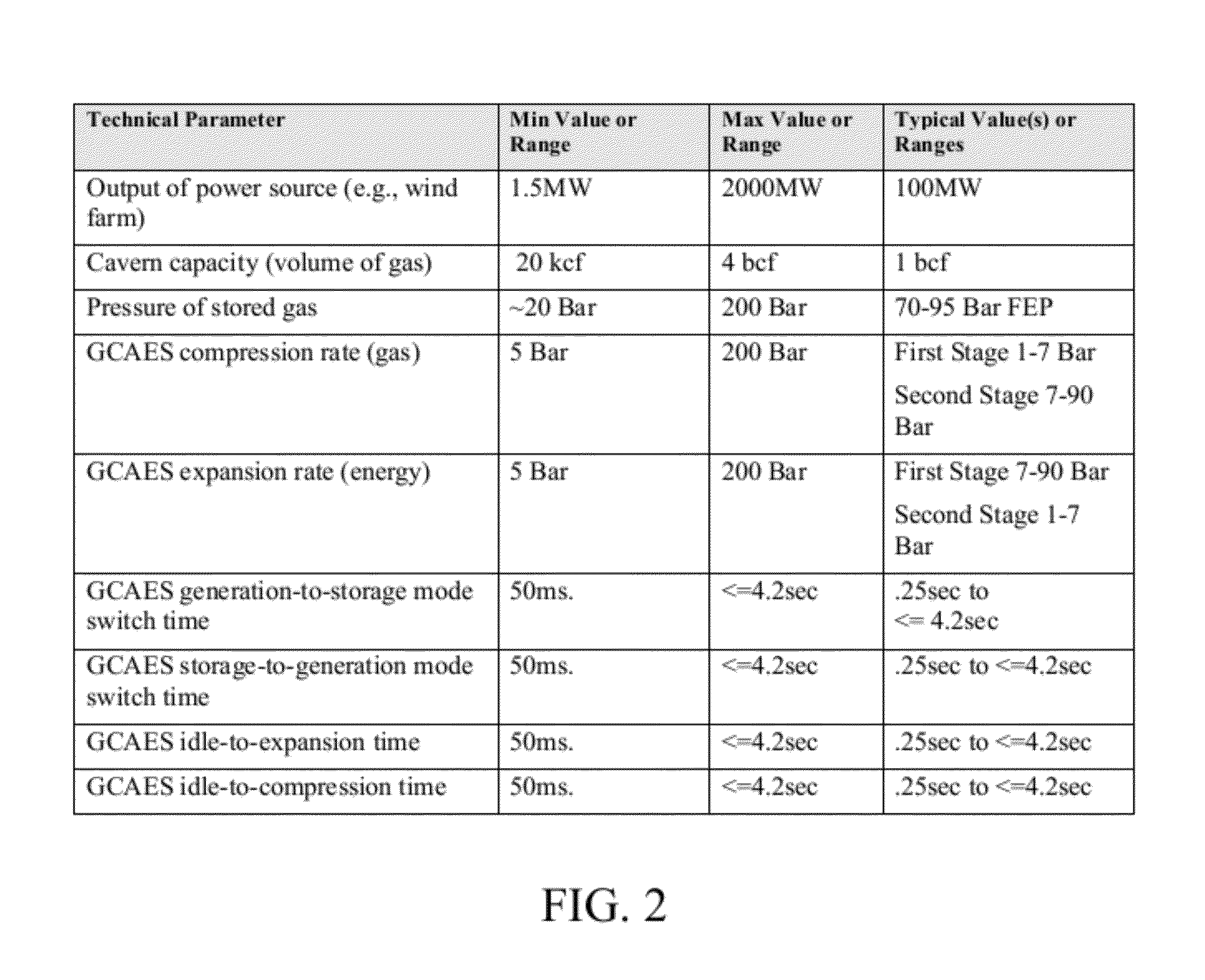

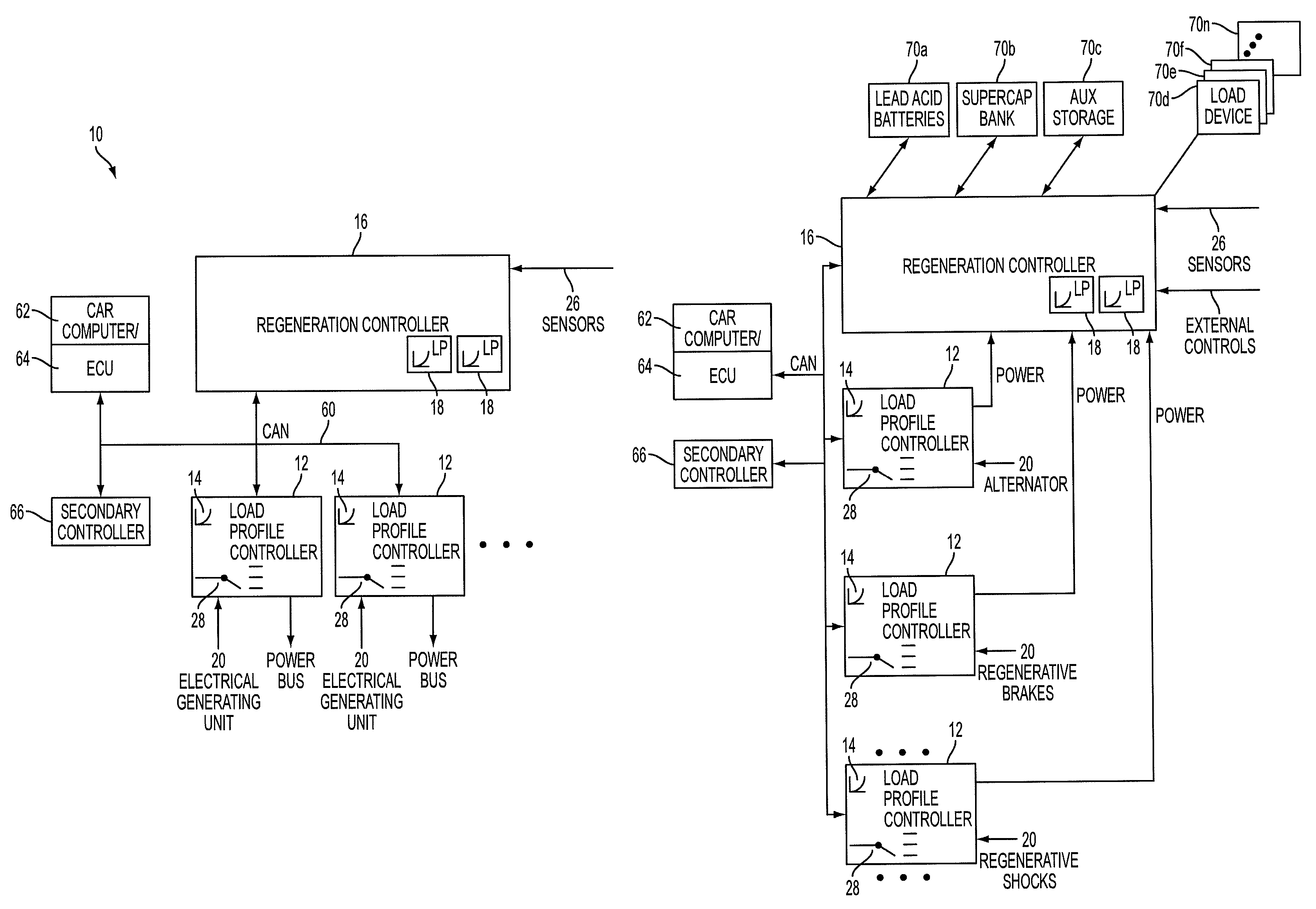

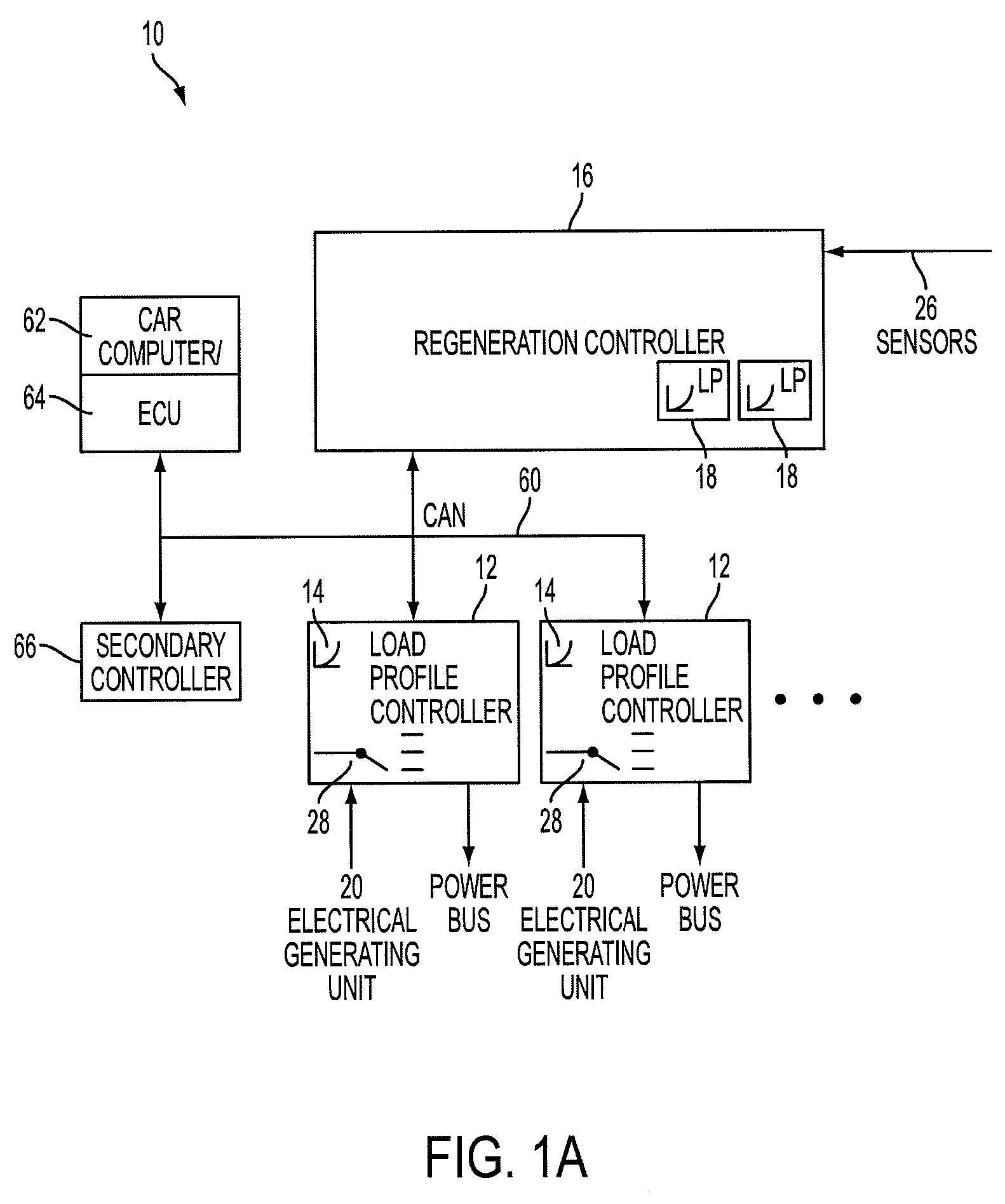

System and method for control for regenerative energy generators

ActiveUS20100262308A1Safe and efficient chargingSupply energyAuxillary drivesLevel controlArea networkOn board

A device and system that can dynamically provide variable load on a generator and intelligently distribute generated power to loads and energy storage devices is disclosed. One system includes load profile controllers that employ a switching strategy to dynamically vary the load the generator induces while producing regenerative energy. This switching strategy may allow for a wide dynamic range of configurable damping characteristics, as well as decouple generator damping and the system output power. Multiple load profile controllers can be used together via a communications network, such as a vehicle controller area network (CAN) bus. A central regeneration controller or existing electronic control unit (ECU) can issue commands to change damping performance in different load profile controllers. By networking multiple load profile controllers together in either a distributed or centralized manner, the system may allow for intelligent power routing, coordination of multiple energy-generating devices (such as regenerative shocks and brakes), and improved utilization of on-board energy storage devices.

Owner:CLEARMOTION INC

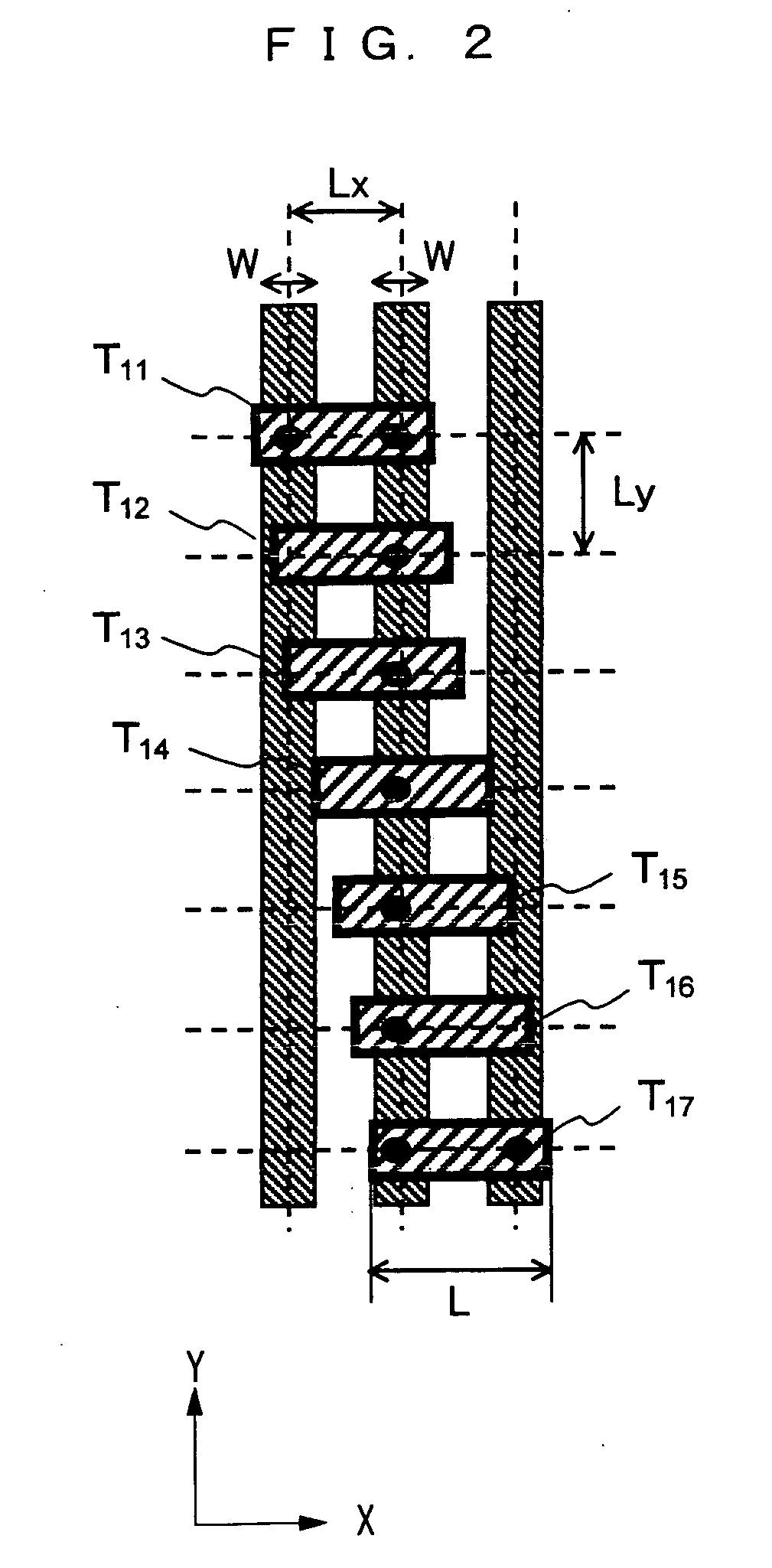

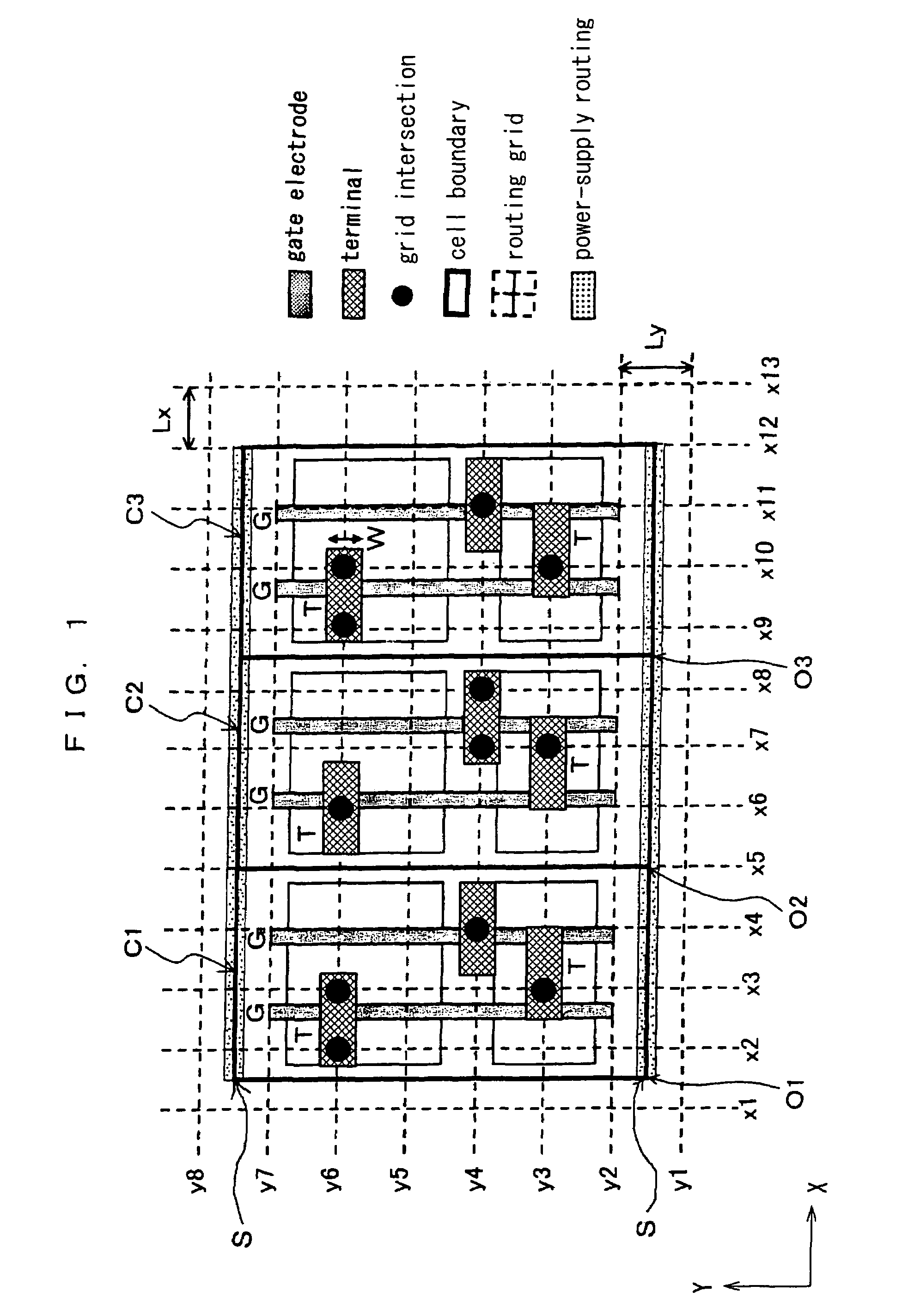

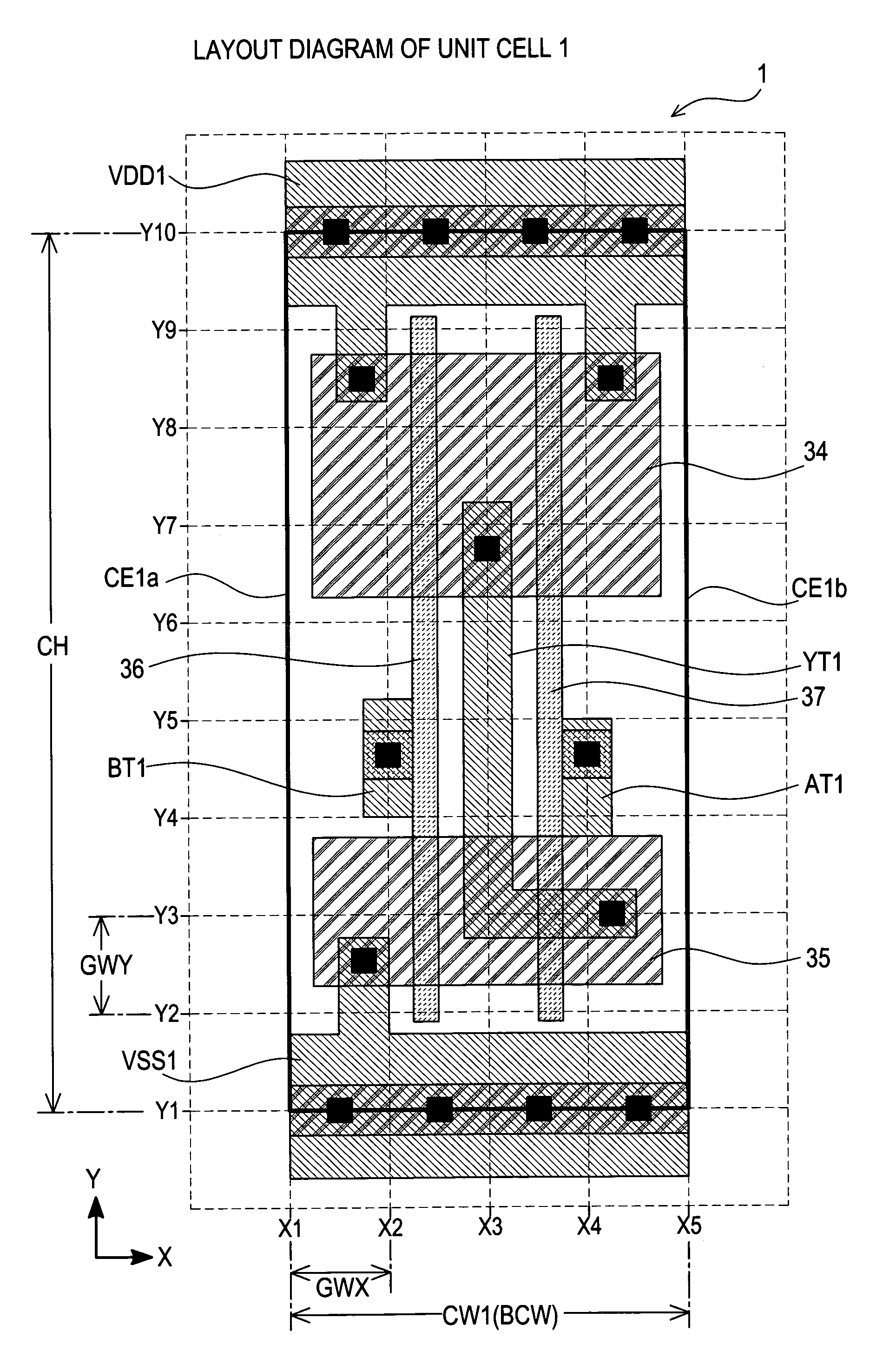

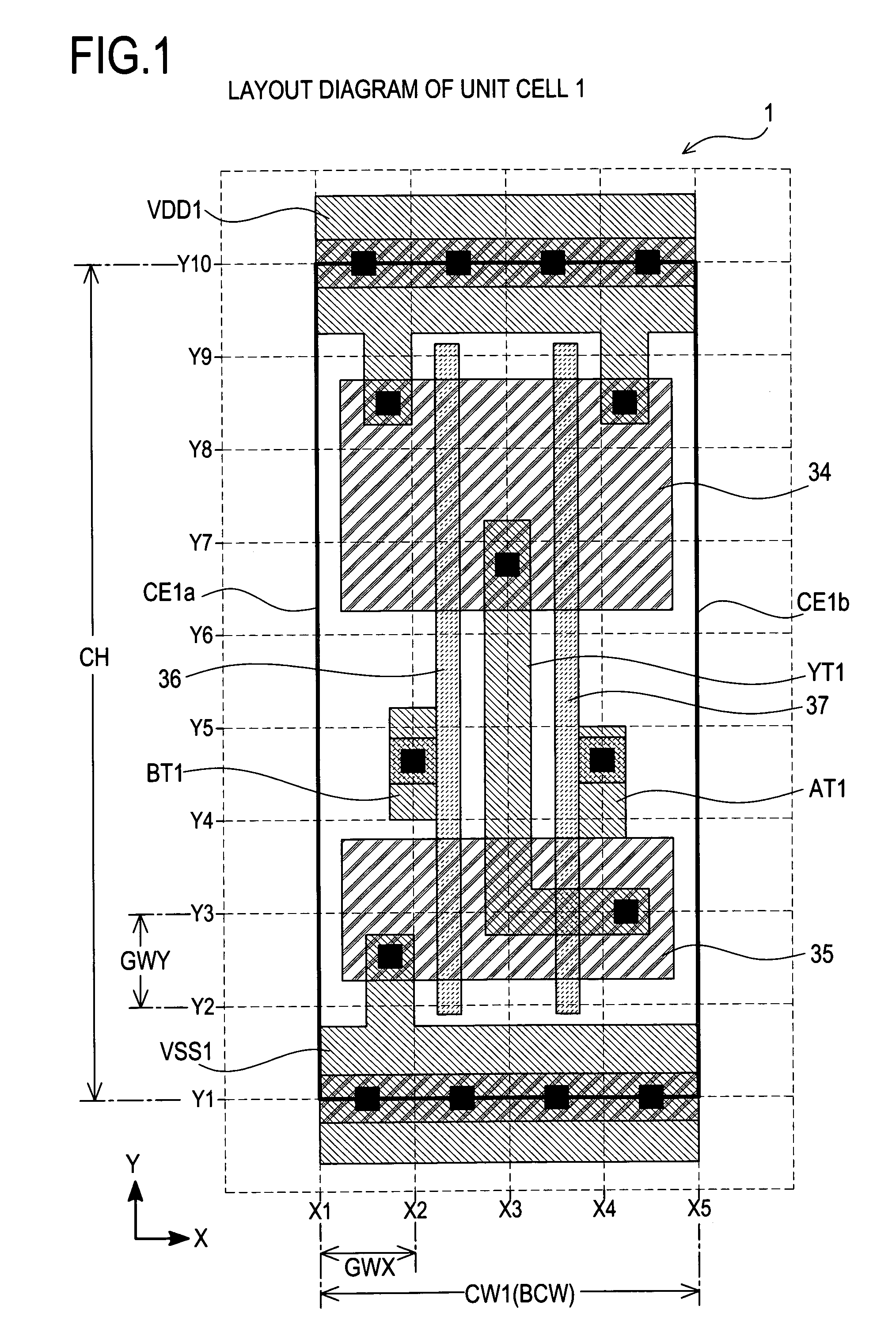

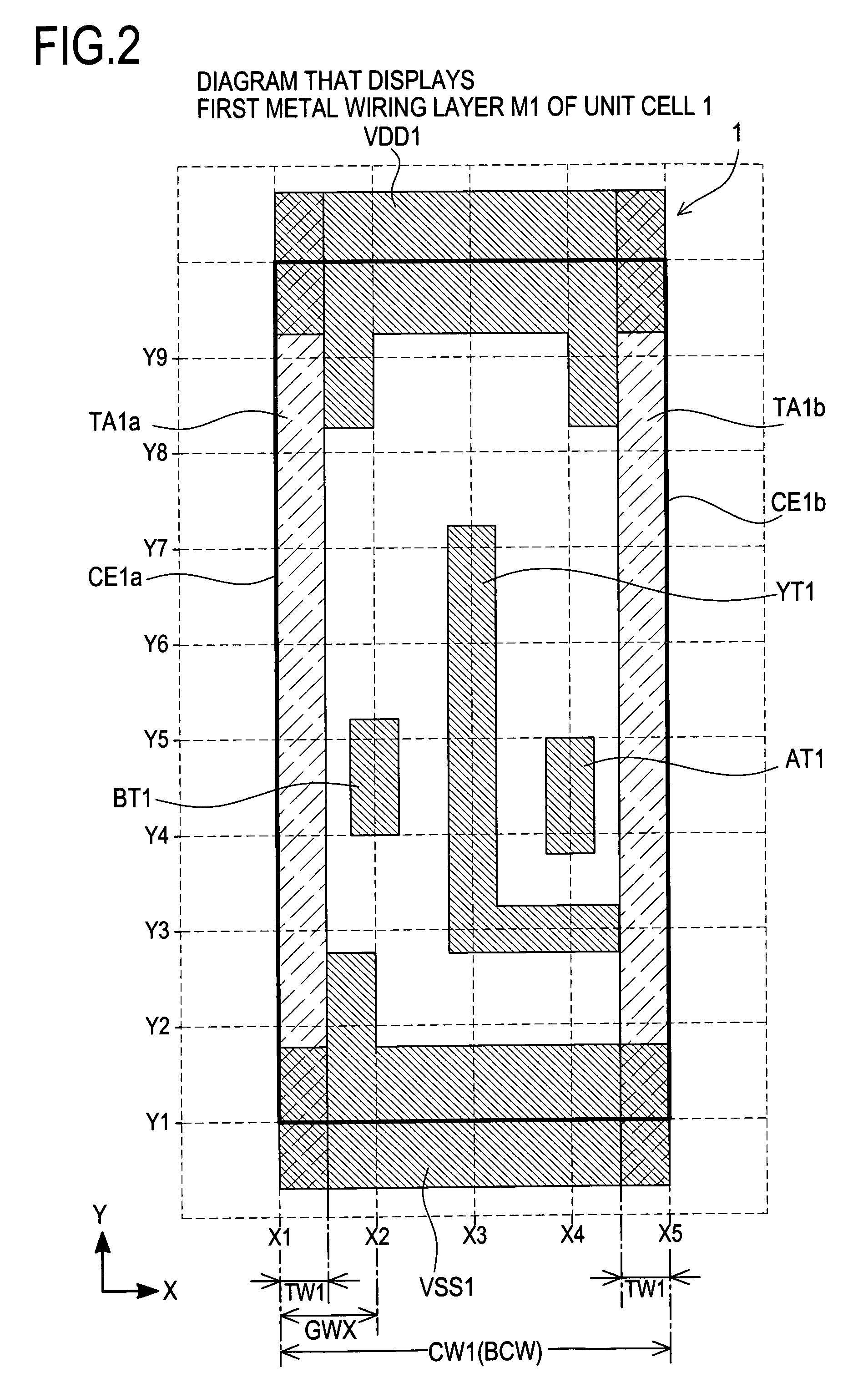

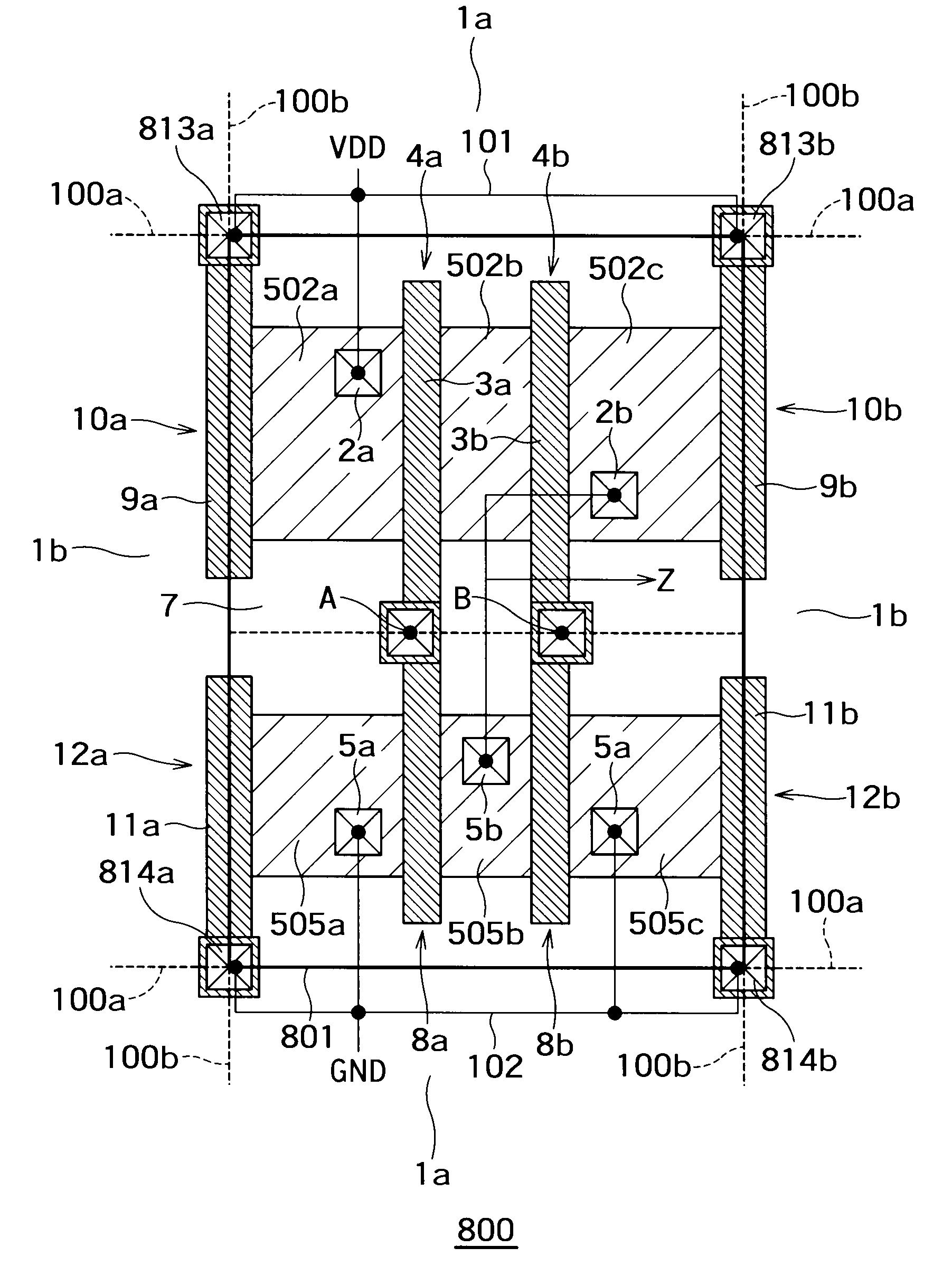

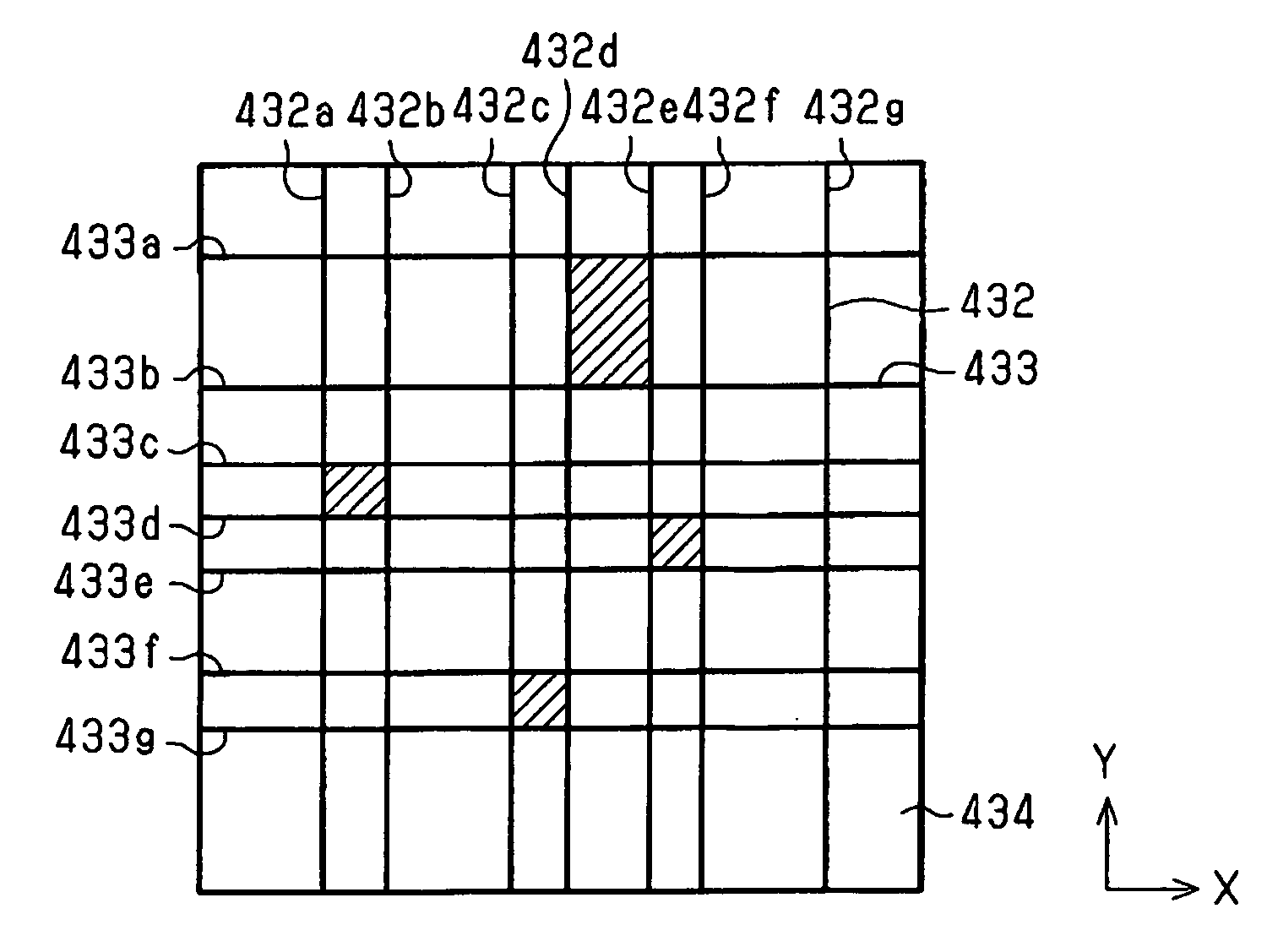

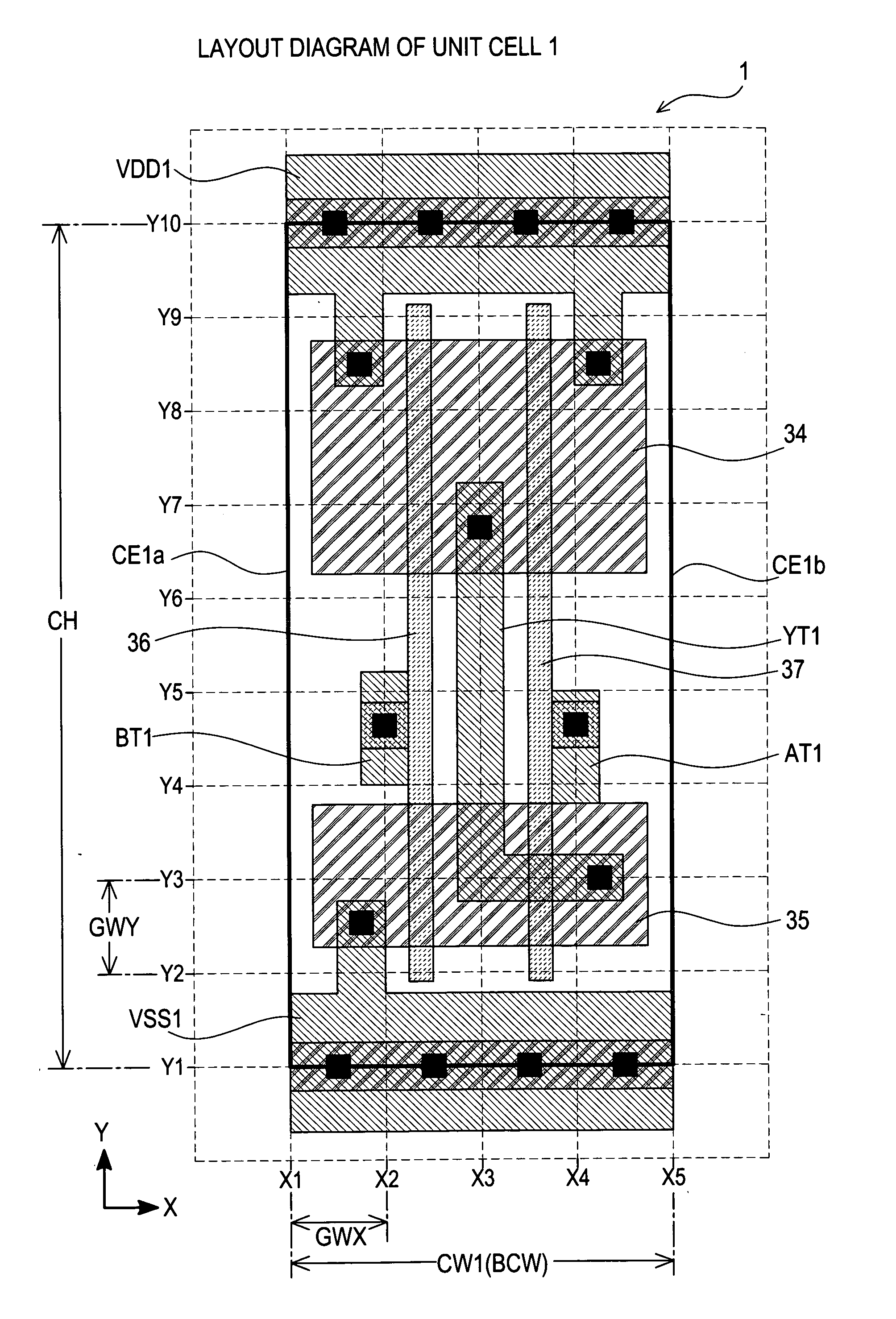

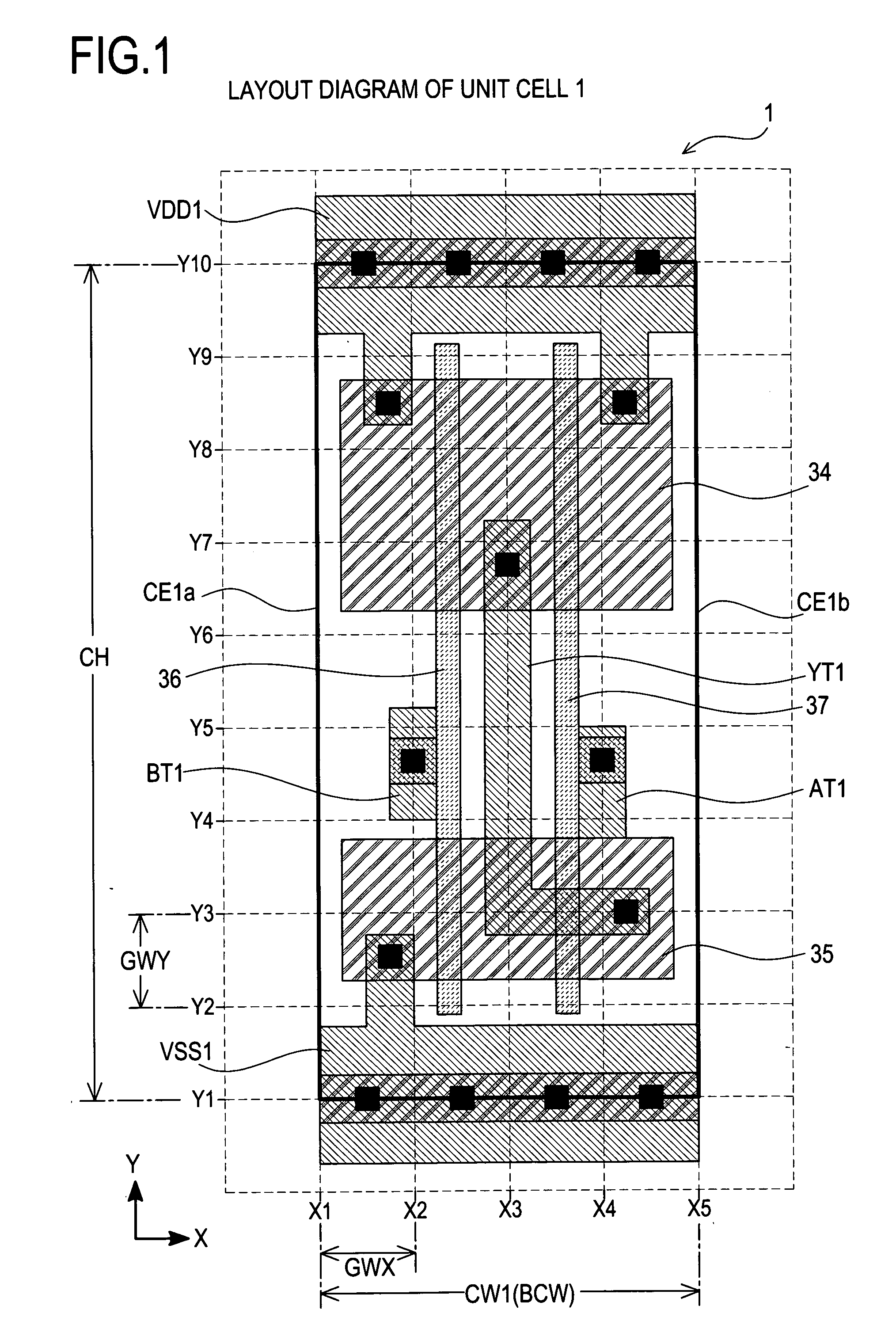

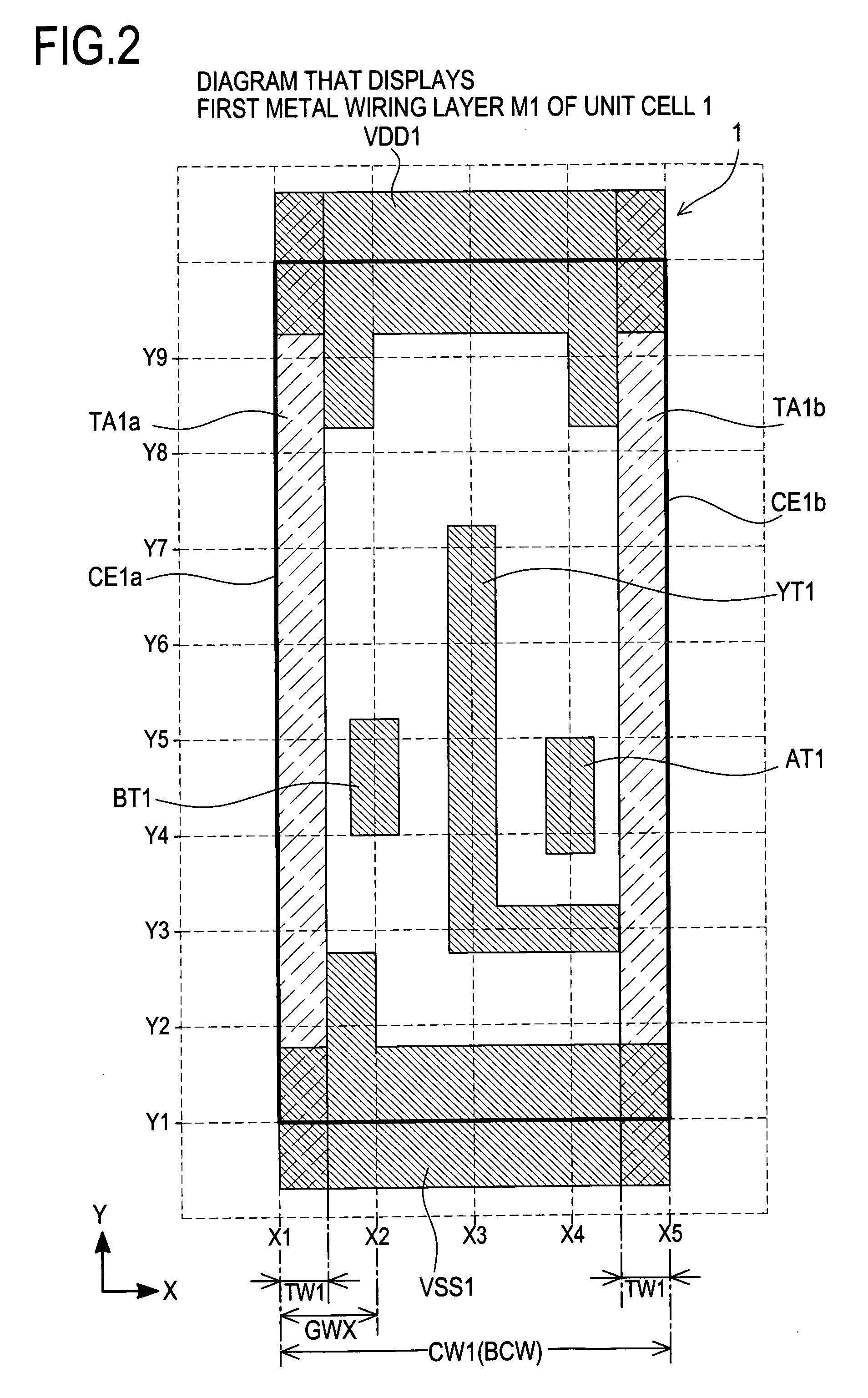

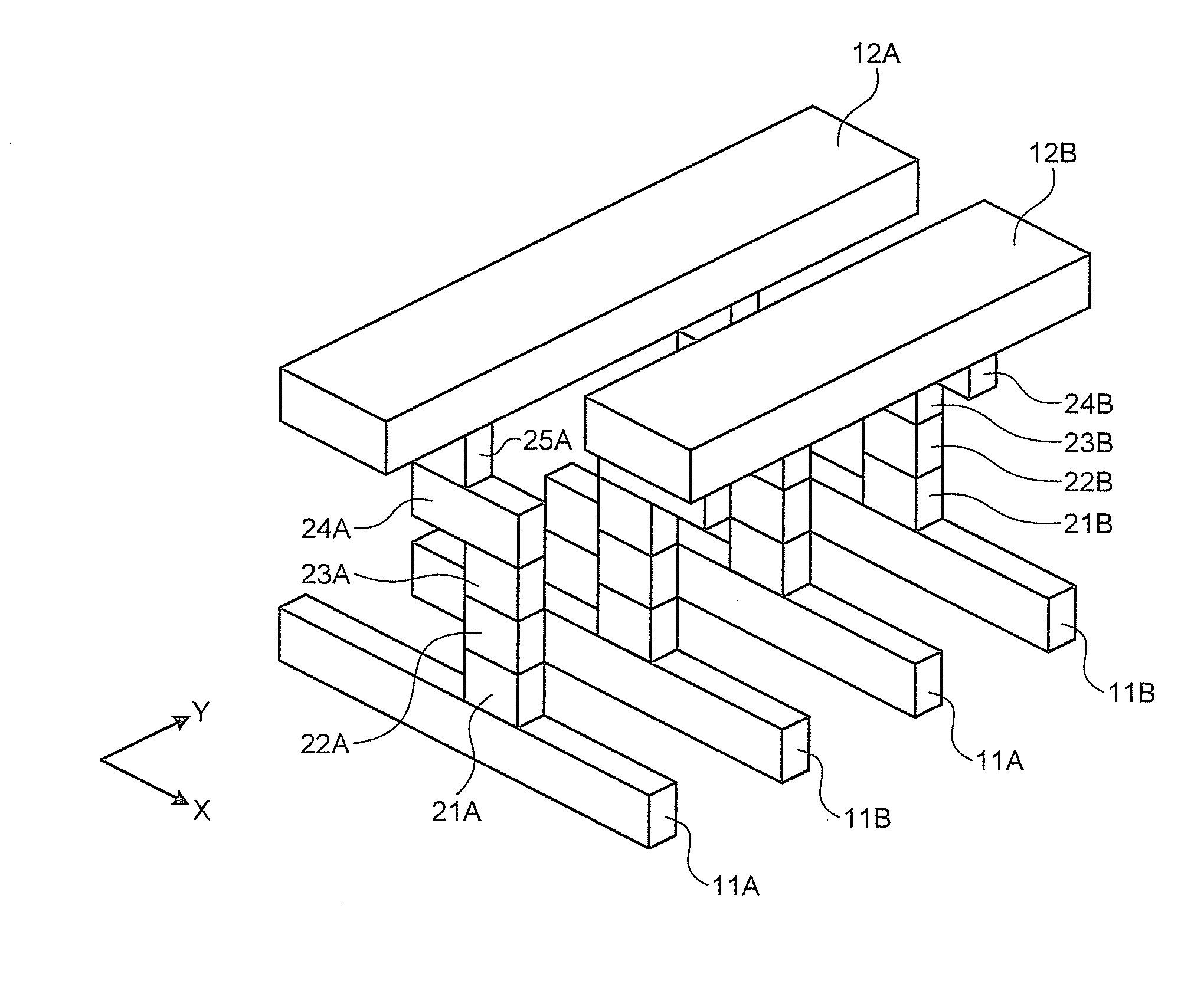

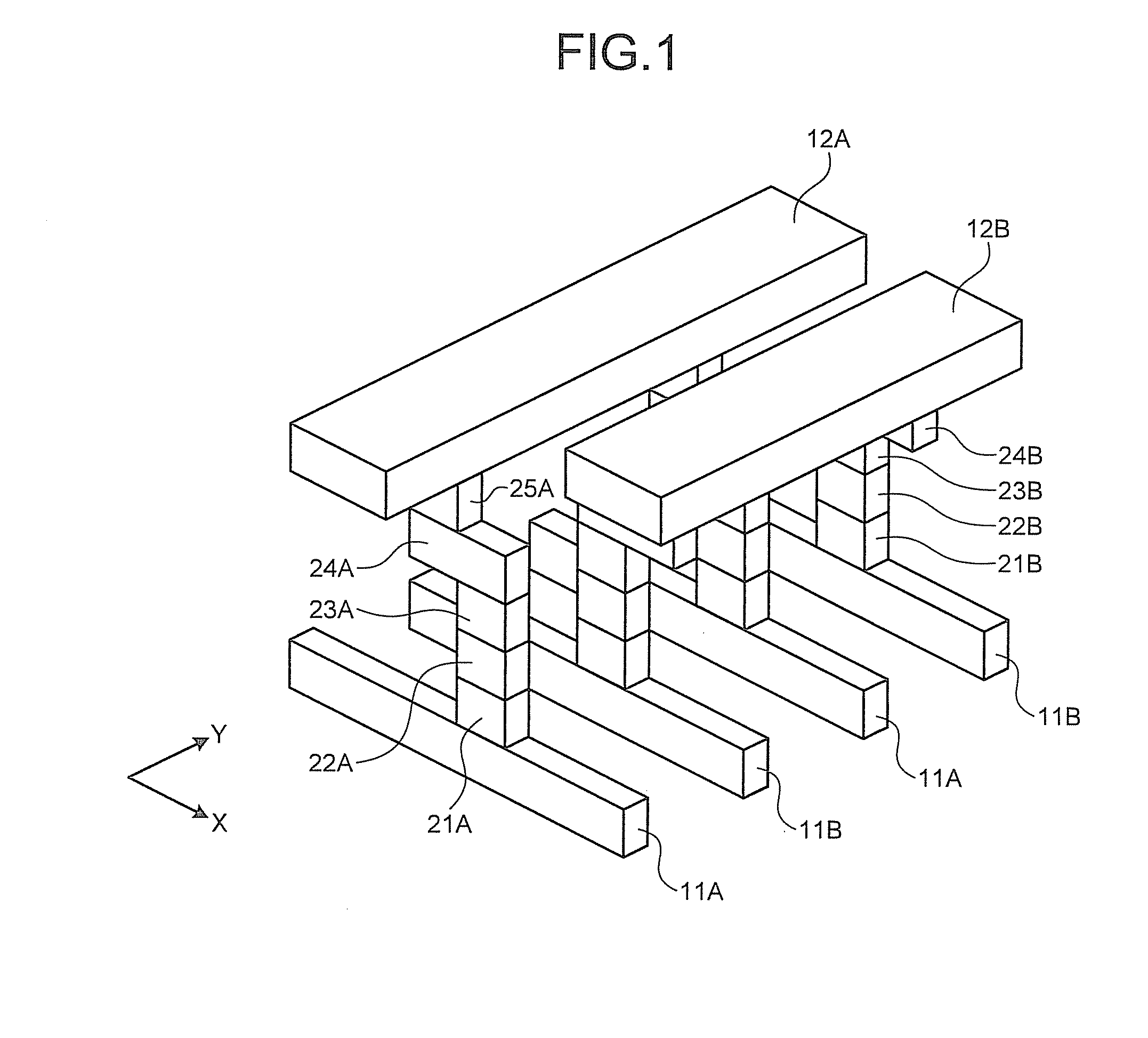

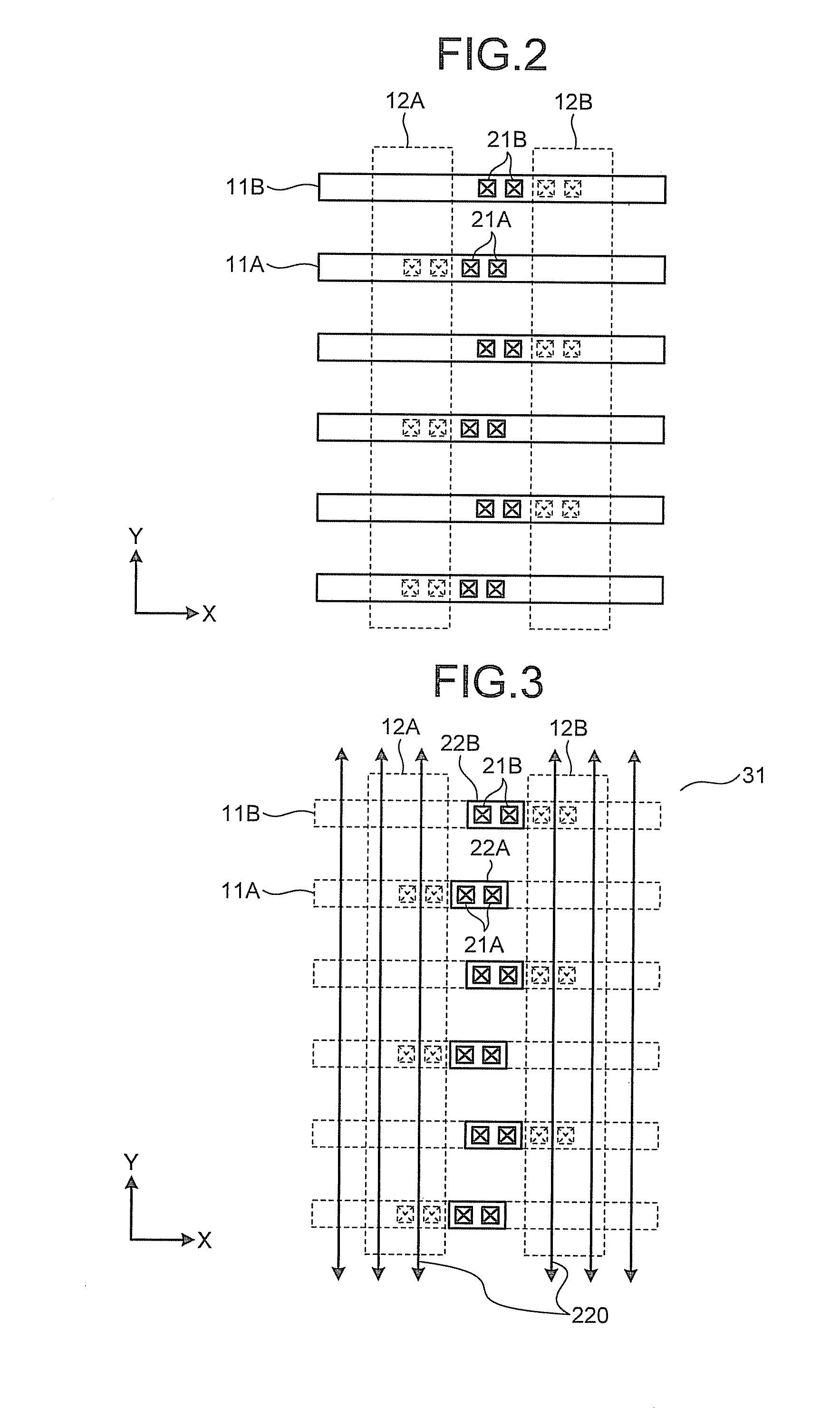

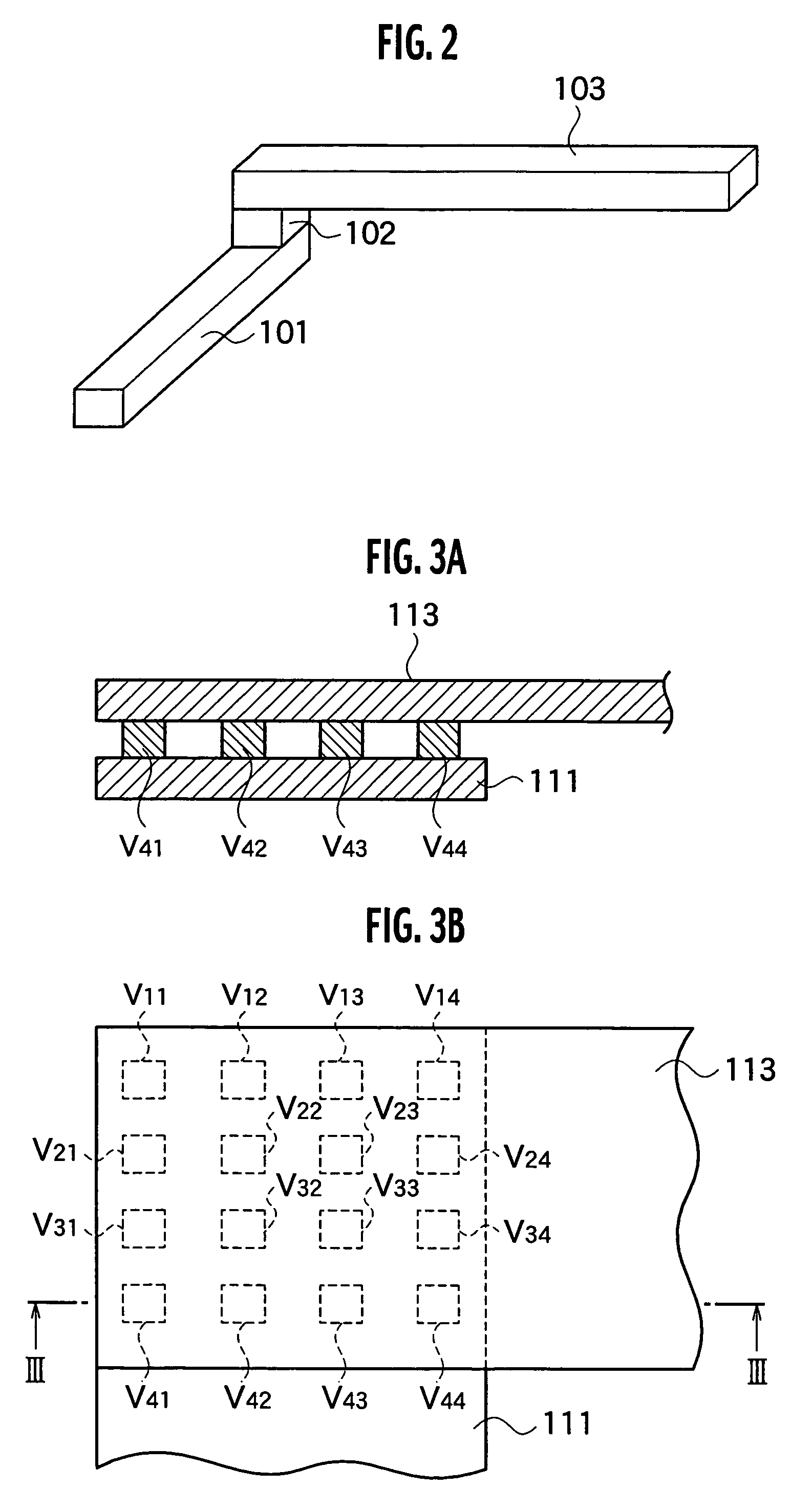

Unit cell of semiconductor integrated circuit and wiring method and wiring program using unit cell

InactiveUS7500211B2Improve wiring efficiencySolid-state devicesSpecial data processing applicationsElectrical batteryEngineering

A unit cell of a semiconductor integrated circuit capable of improving wiring efficiency in layout of a functional circuit block or the like using a unit cell, and a wiring method and wiring program using the unit cell are provided. In a unit cell, auxiliary power wiring regions are formed with reference to grids that exist from a cell edge every basic cell width in the X-direction. Input signal terminals and an output signal terminal are each arranged so as to include at least one wiring connecting portion outside the auxiliary power wiring regions. This makes it possible to wire wiring other than signal wiring in the auxiliary power wiring region. When a functional circuit block is constructed by arranging unit cells in a matrix, auxiliary power wiring regions are formed at a pitch of the basic cell width, through the functional circuit block in the Y-direction.

Owner:SOCIONEXT INC

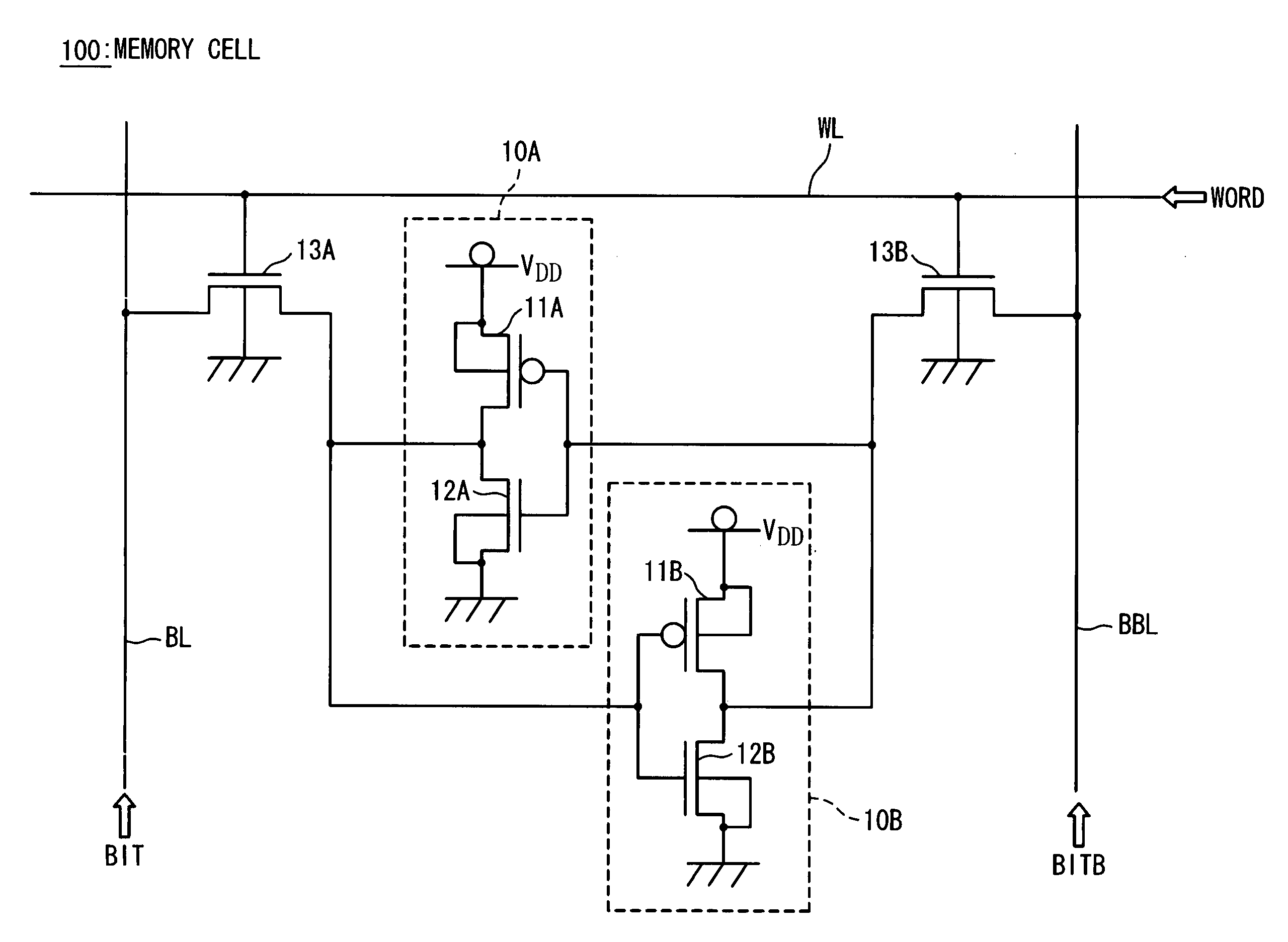

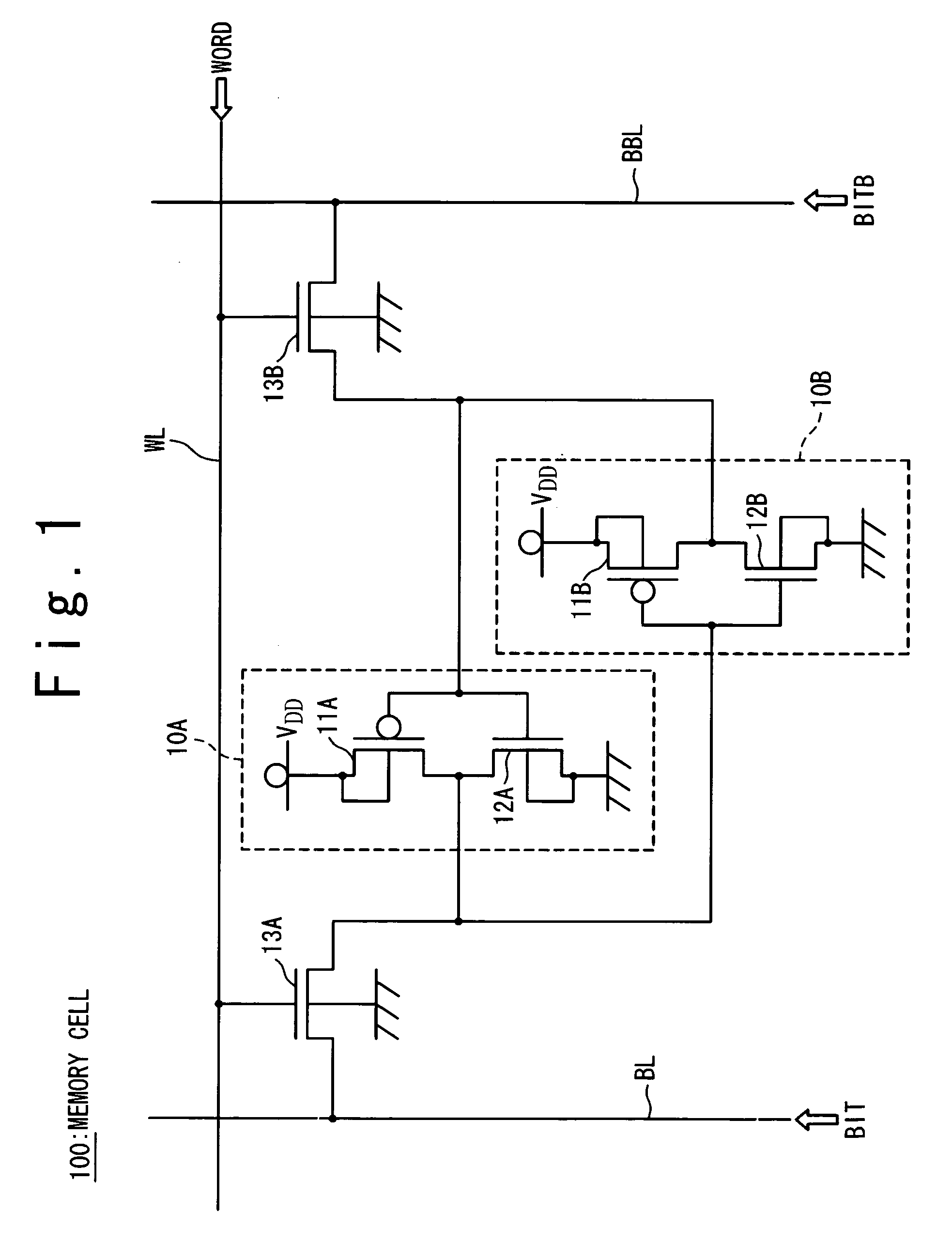

Static semiconductor memory device

A static semiconductor memory device includes a memory cell formed in a memory cell region; and a dummy memory cell formed in a dummy memory cell region. The memory cell includes a power supply wiring and a ground wiring which are provided to extend in a direction of a word line; and inverters provided between the power supply wiring and the ground wiring and cross-connected to each other. The dummy memory cell includes first and second wirings respectively corresponding to the power supply wiring and the ground wiring and extending in the direction of the word line; and two sets of a dummy load circuit and a dummy drive transistor, wherein the two sets are connected with the first and second wirings, which are biased to prevent leakage current from flowing.

Owner:RENESAS ELECTRONICS CORP

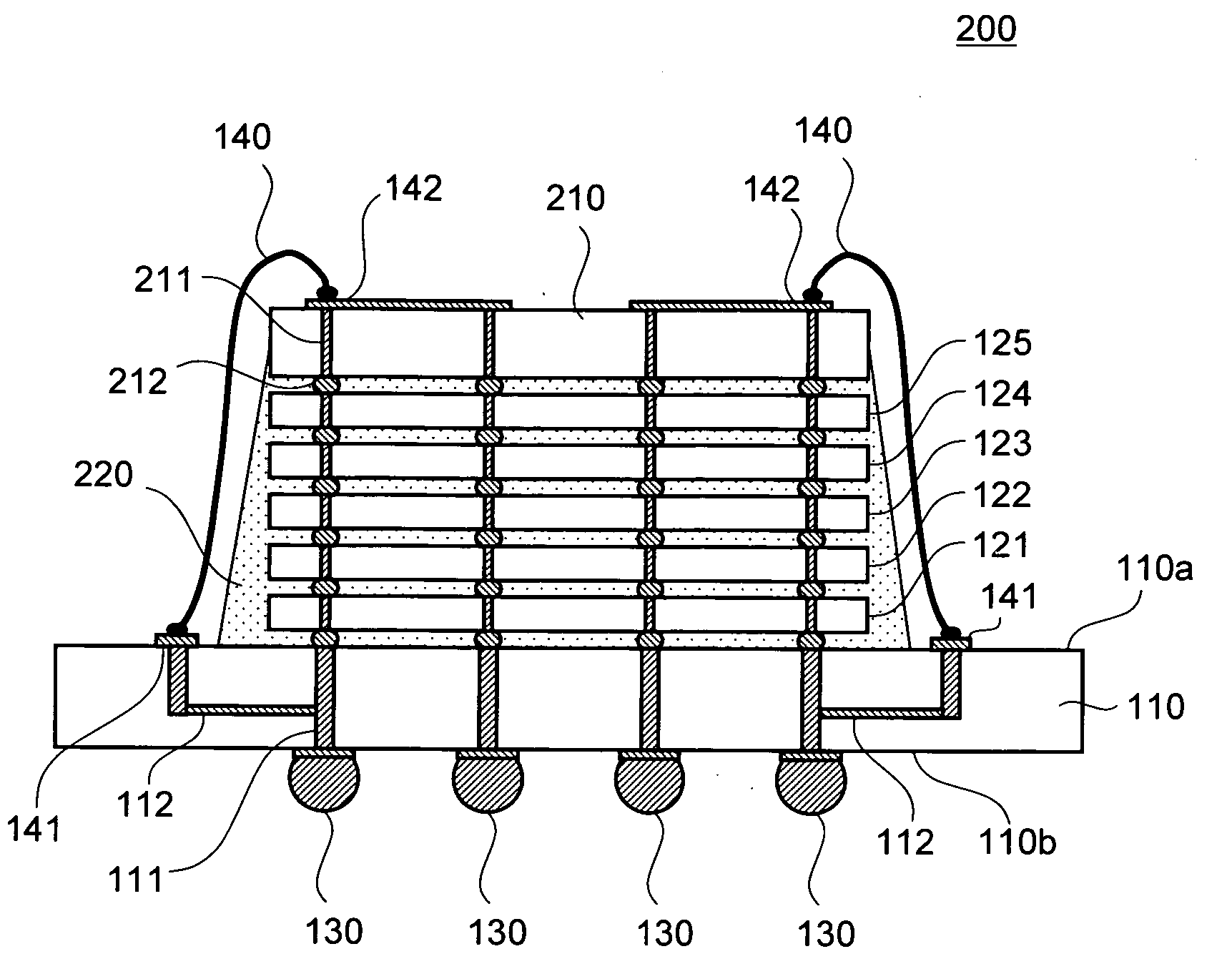

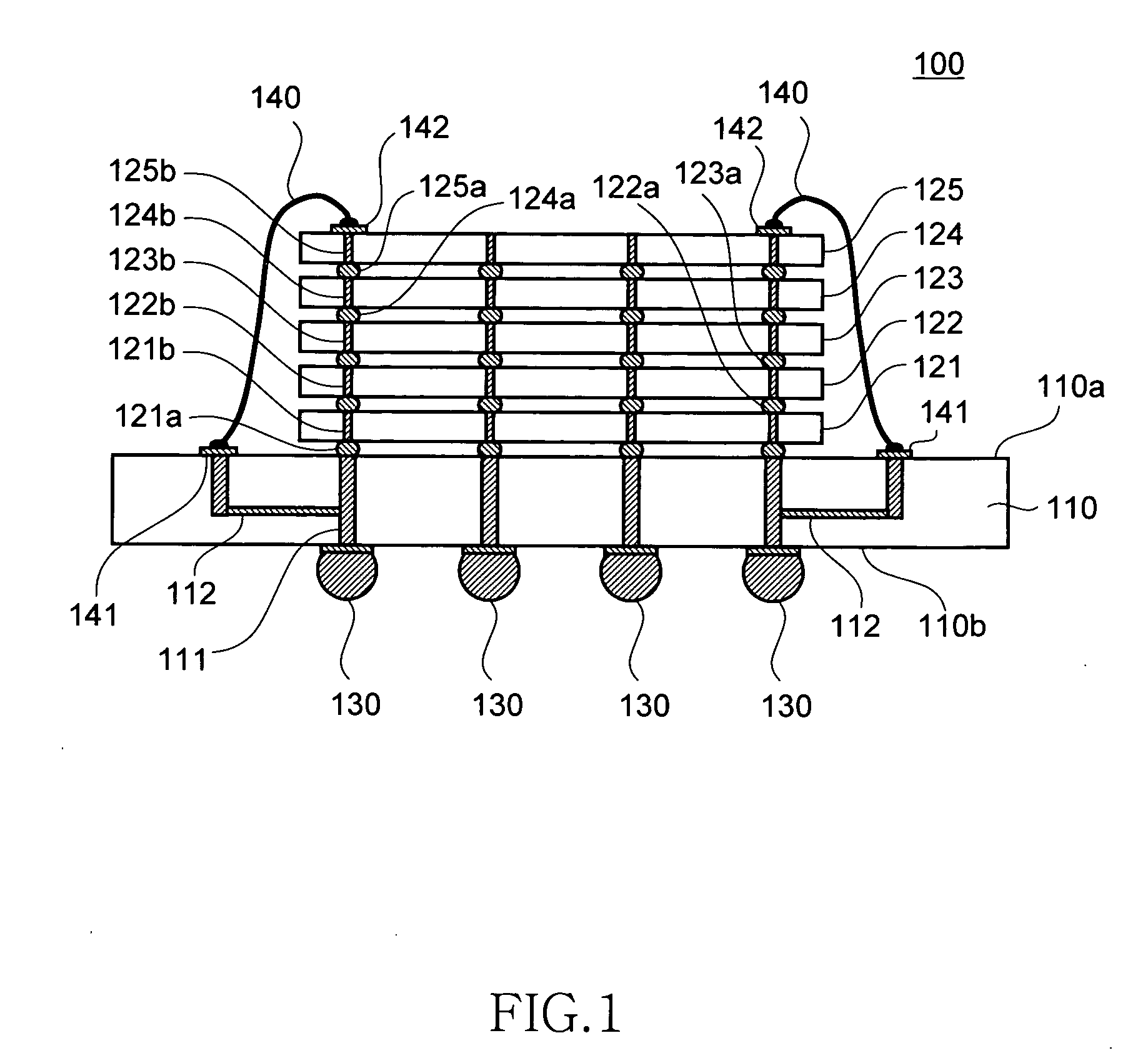

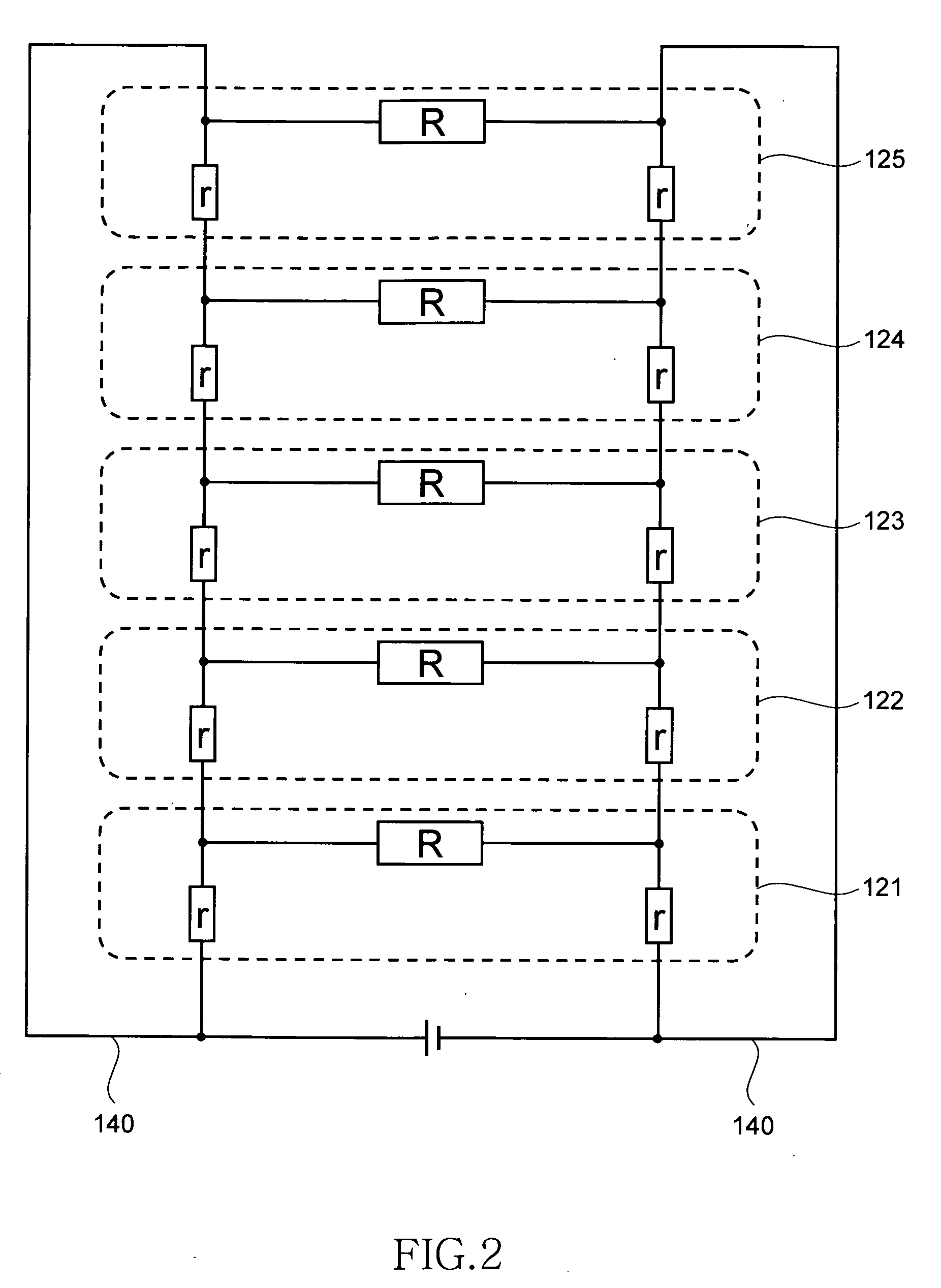

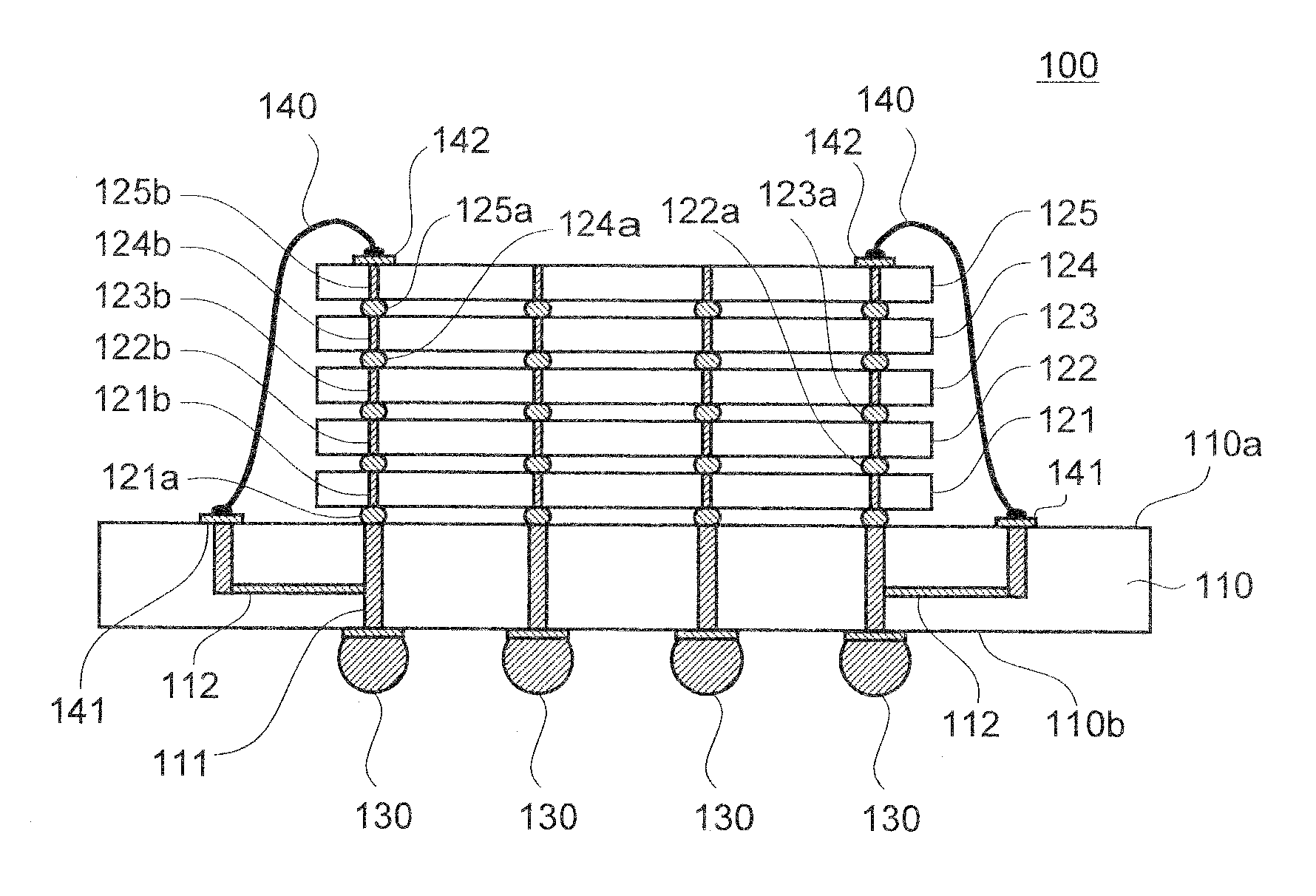

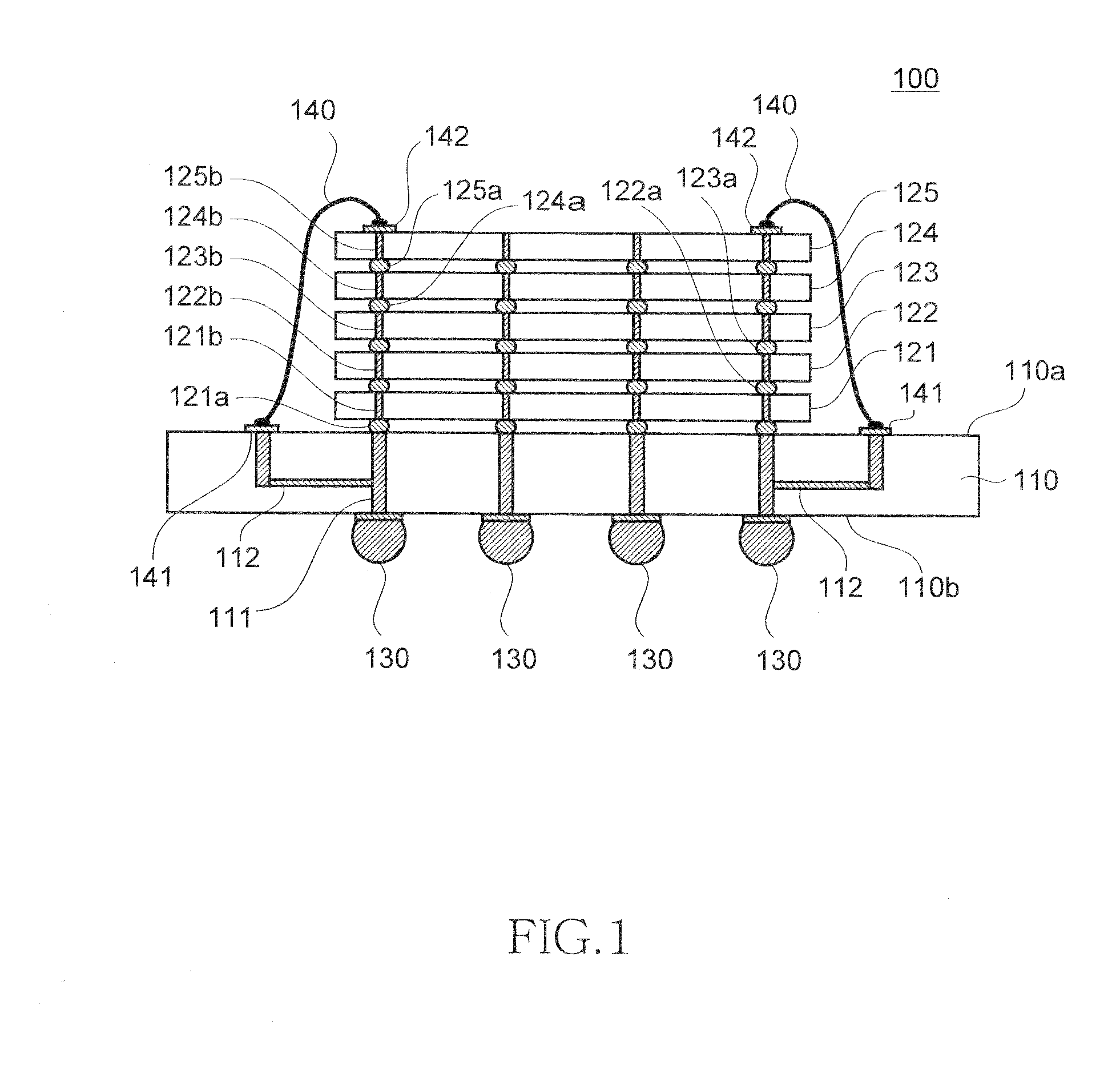

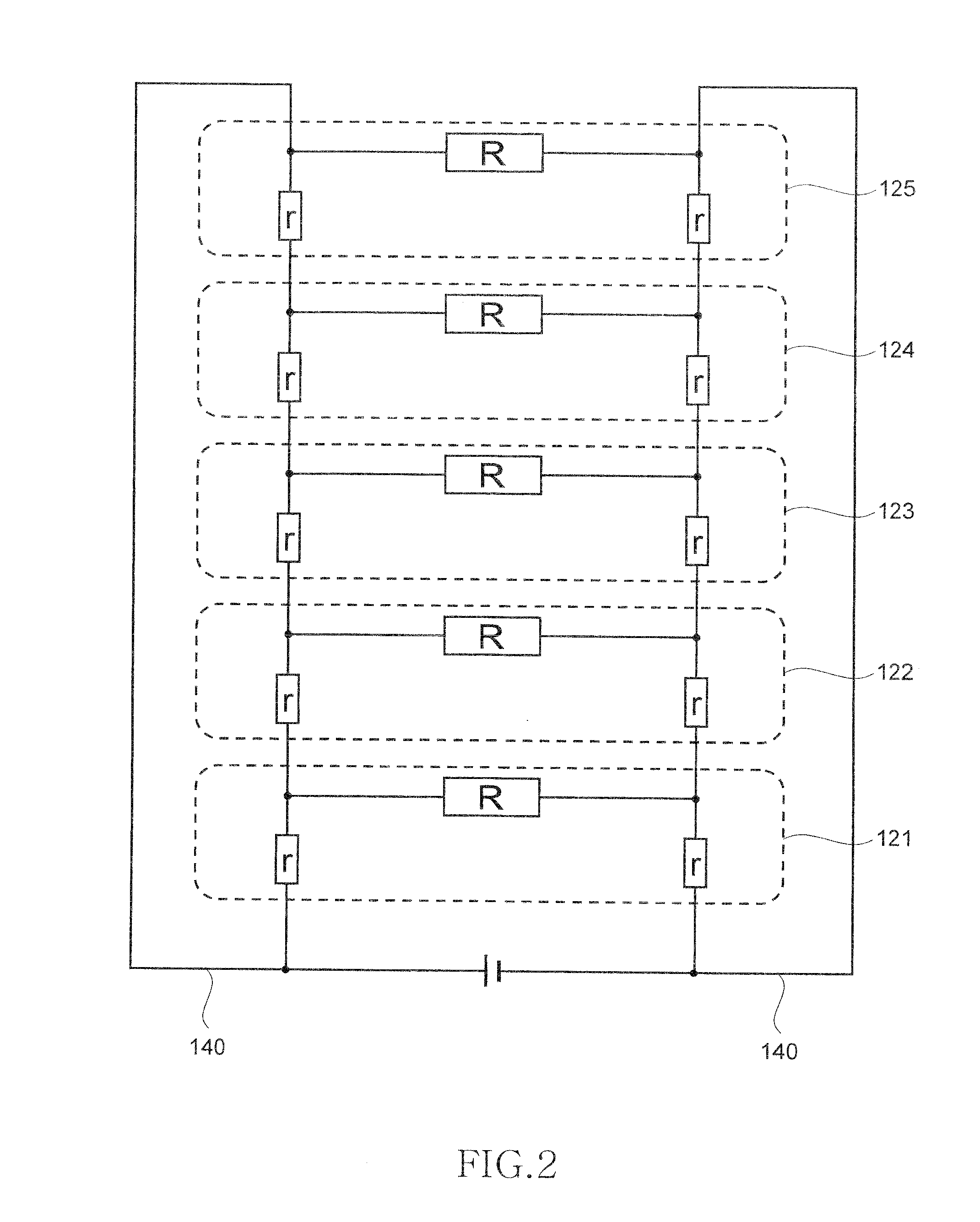

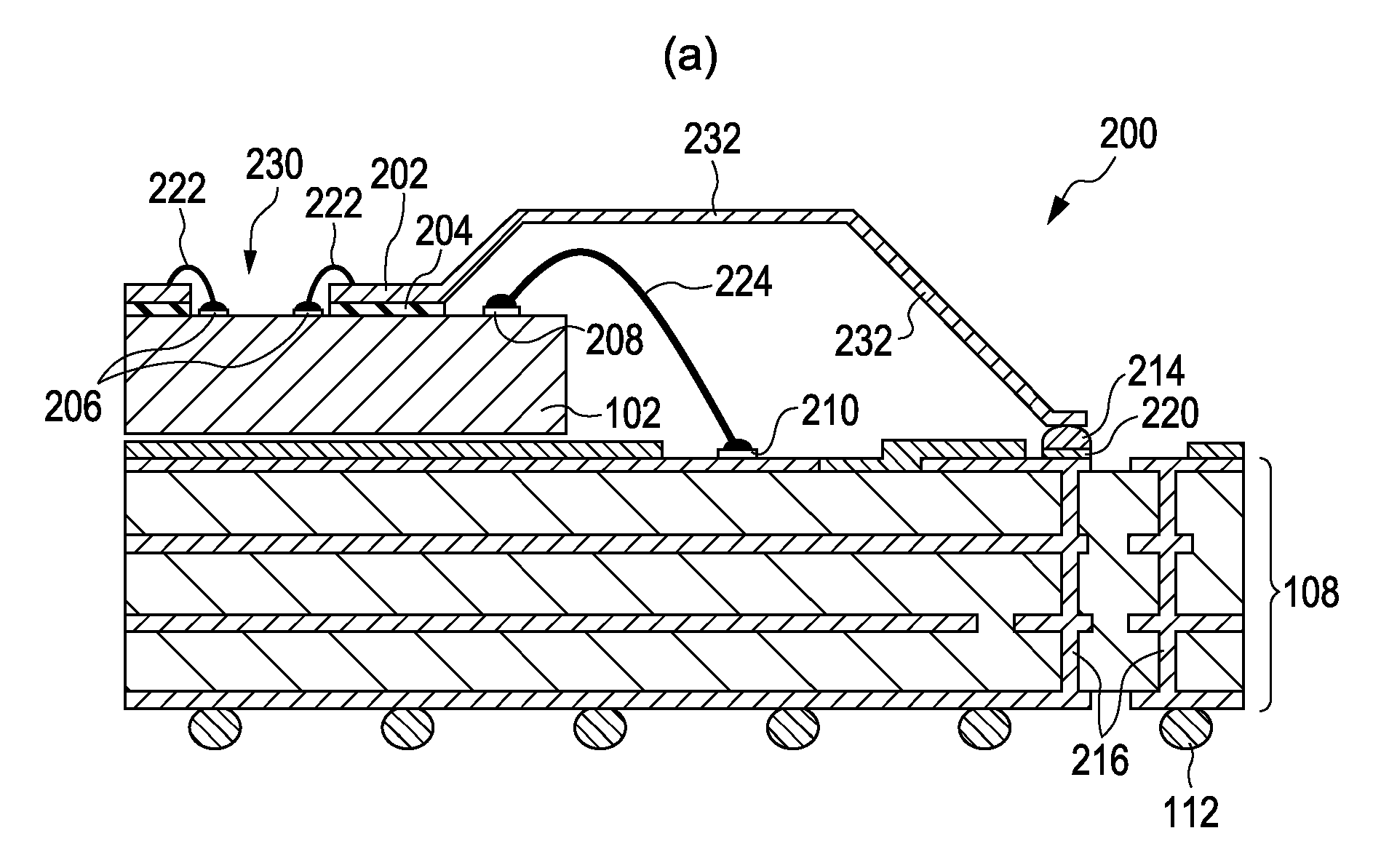

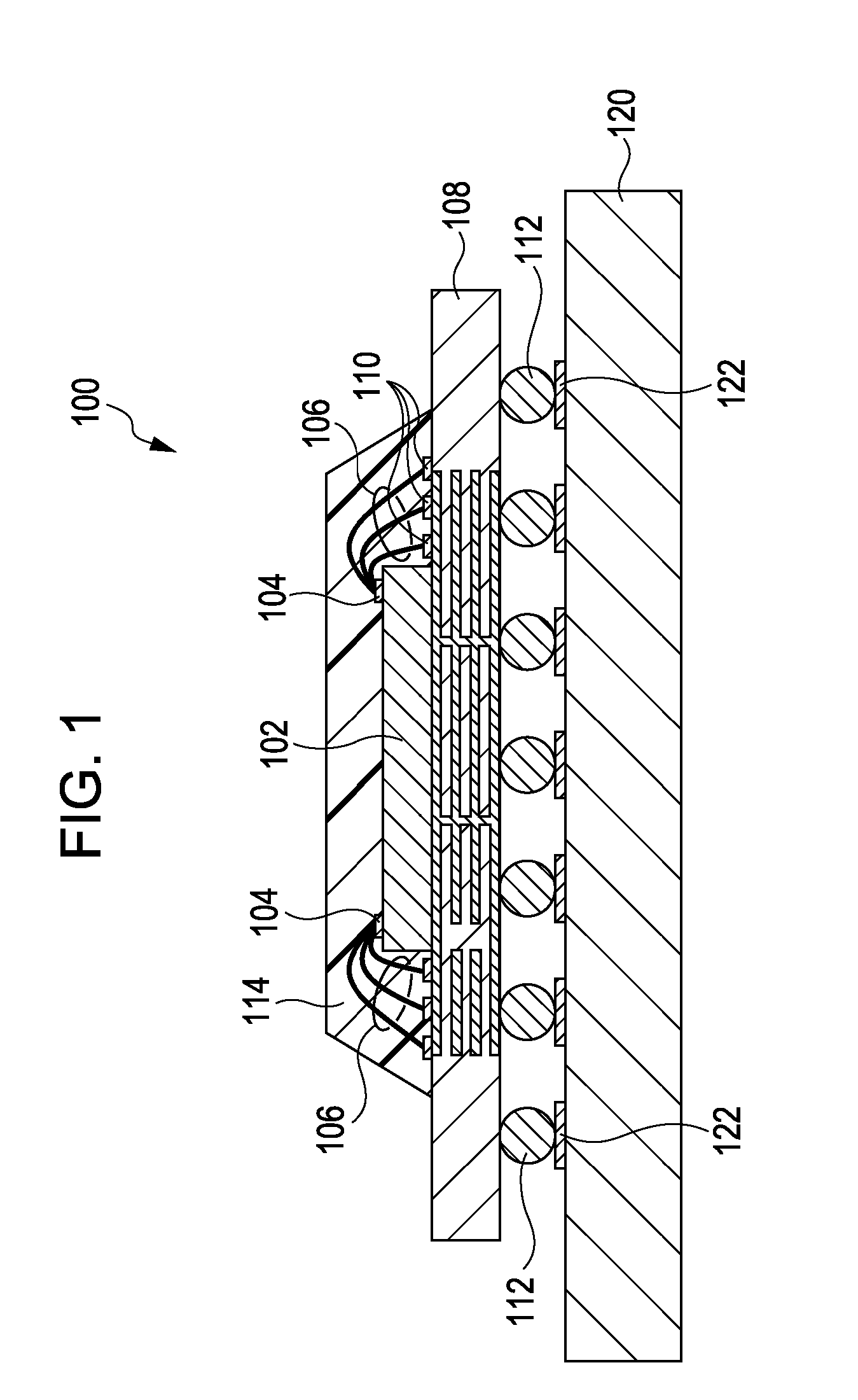

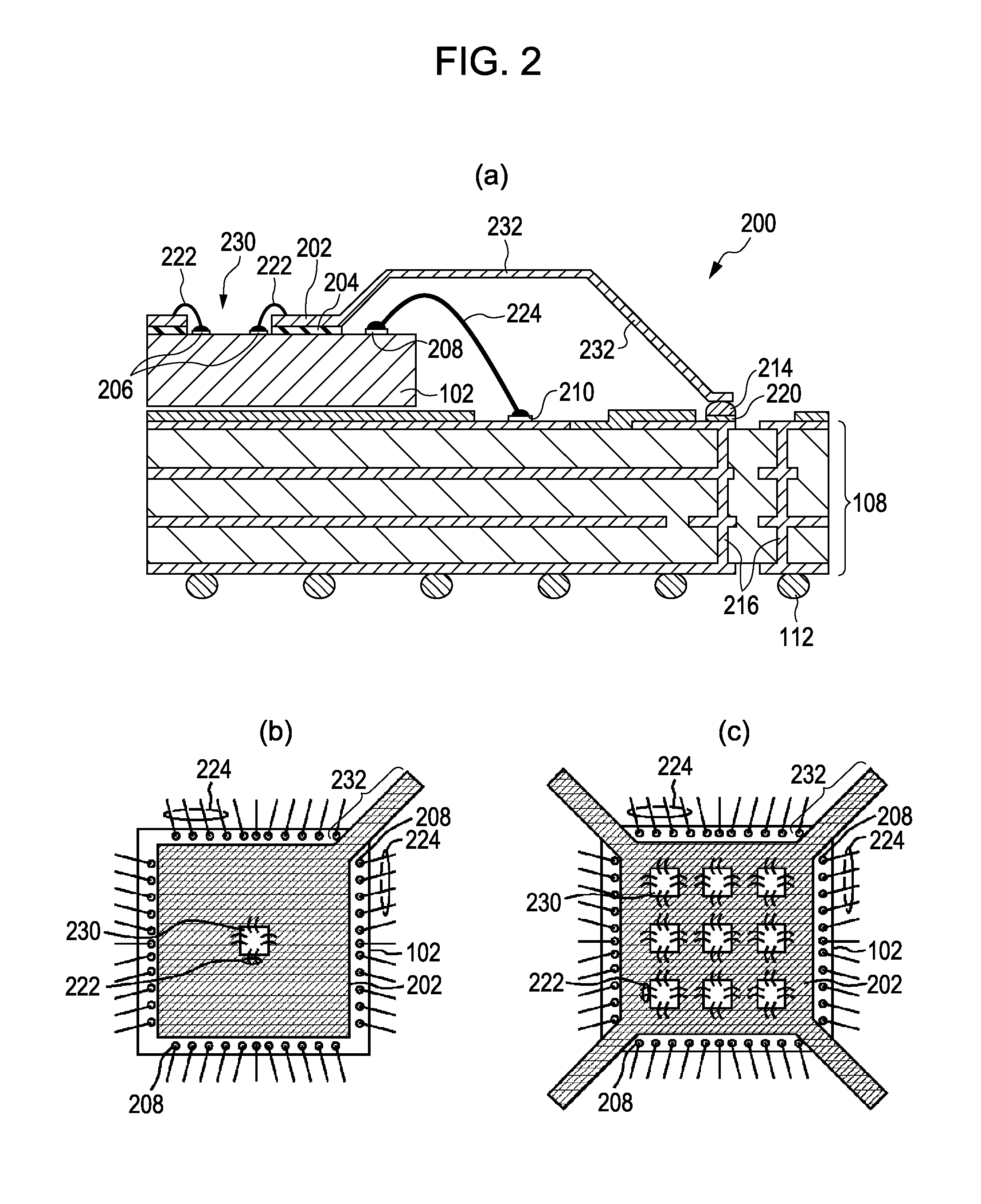

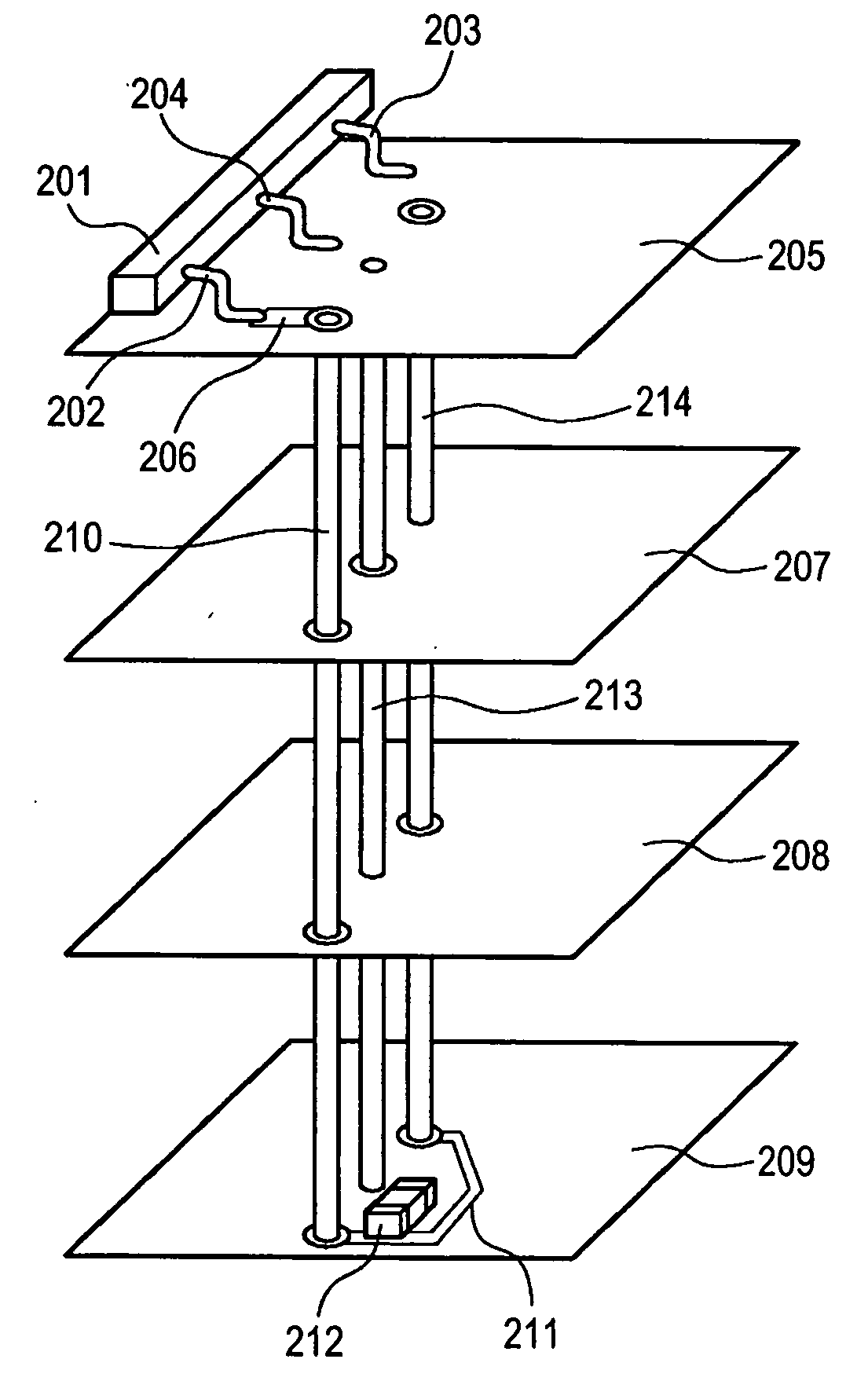

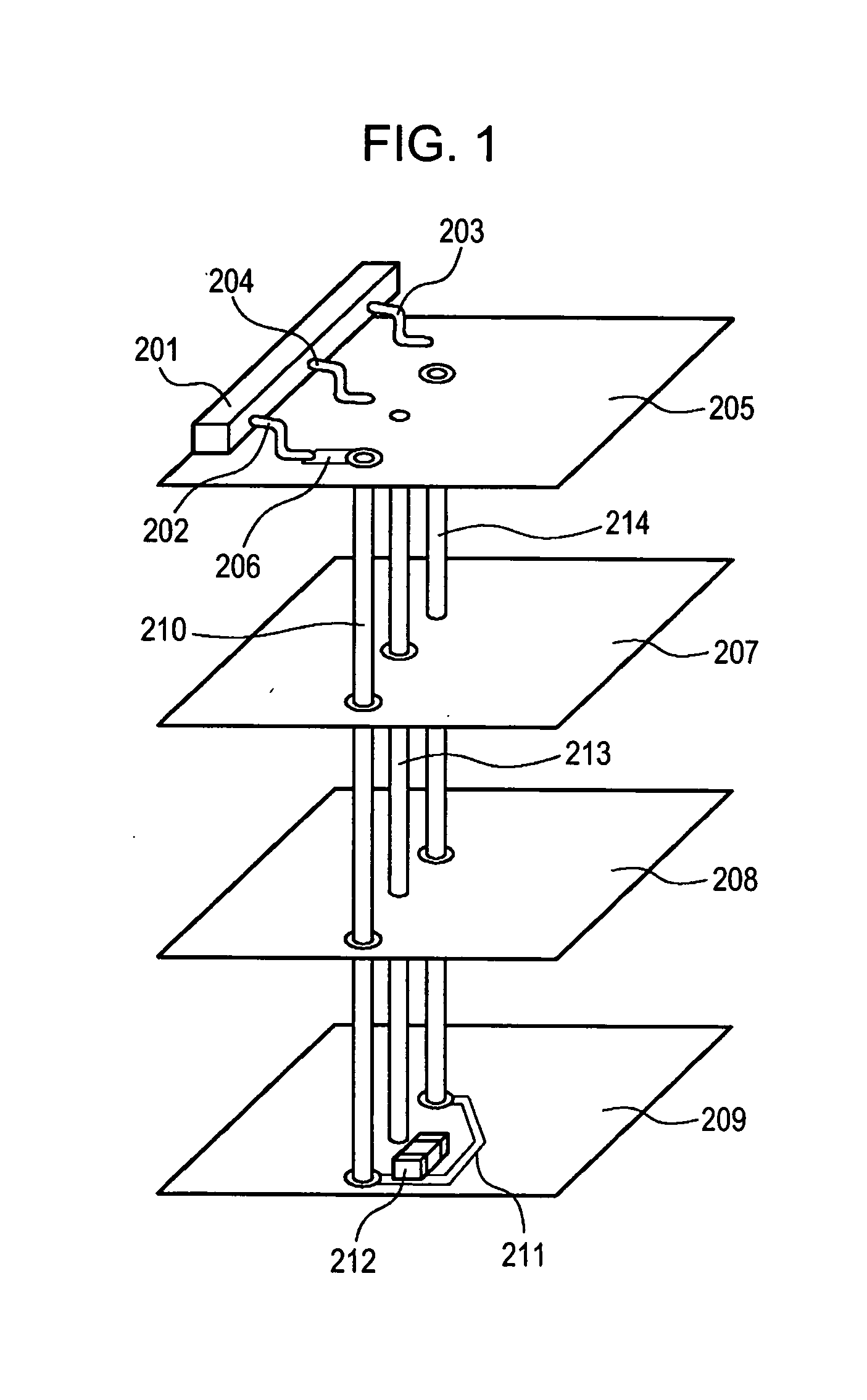

Stacked semiconductor device

ActiveUS20070181991A1Suppress decrease in power source voltageDeterioration levelSemiconductor/solid-state device detailsSolid-state devicesInterposerSemiconductor chip

A stacked semiconductor device includes an interposer substrate having external power supply terminals, and semiconductor chips stacked on the interposer substrate. A power supply wiring arranged in the semiconductor chip located in the bottom layer is connected to the external power supply terminal via a bump electrode, the power supply wiring arranged in the semiconductor chip located in the top layer is connected to the external power supply terminal via a bonding wire, and the power supply wirings each arranged in adjacent semiconductor chips are mutually connected via the through electrode. Such a loop structure can solve a problem such that the higher the semiconductor chip, the larger its voltage drop.

Owner:MICRON TECH INC

Stacked semiconductor device

ActiveUS7531905B2Inhibition decreasedReduce voltageSemiconductor/solid-state device detailsSolid-state devicesInterposerVoltage drop

A stacked semiconductor device includes an interposer substrate having external power supply terminals, and semiconductor chips stacked on the interposer substrate. A power supply wiring arranged in the semiconductor chip located in the bottom layer is connected to the external power supply terminal via a bump electrode, the power supply wiring arranged in the semiconductor chip located in the top layer is connected to the external power supply terminal via a bonding wire, and the power supply wirings each arranged in adjacent semiconductor chips are mutually connected via the through electrode. Such a loop structure can solve a problem such that the higher the semiconductor chip, the larger its voltage drop.

Owner:MICRON TECH INC

Semiconductor Package and Method for Fabricating the Same

InactiveUS20080237856A1More voltage droppingIncrease the number ofSemiconductor/solid-state device detailsSolid-state devicesLead bondingVoltage drop

Owner:GLOBALFOUNDRIES INC

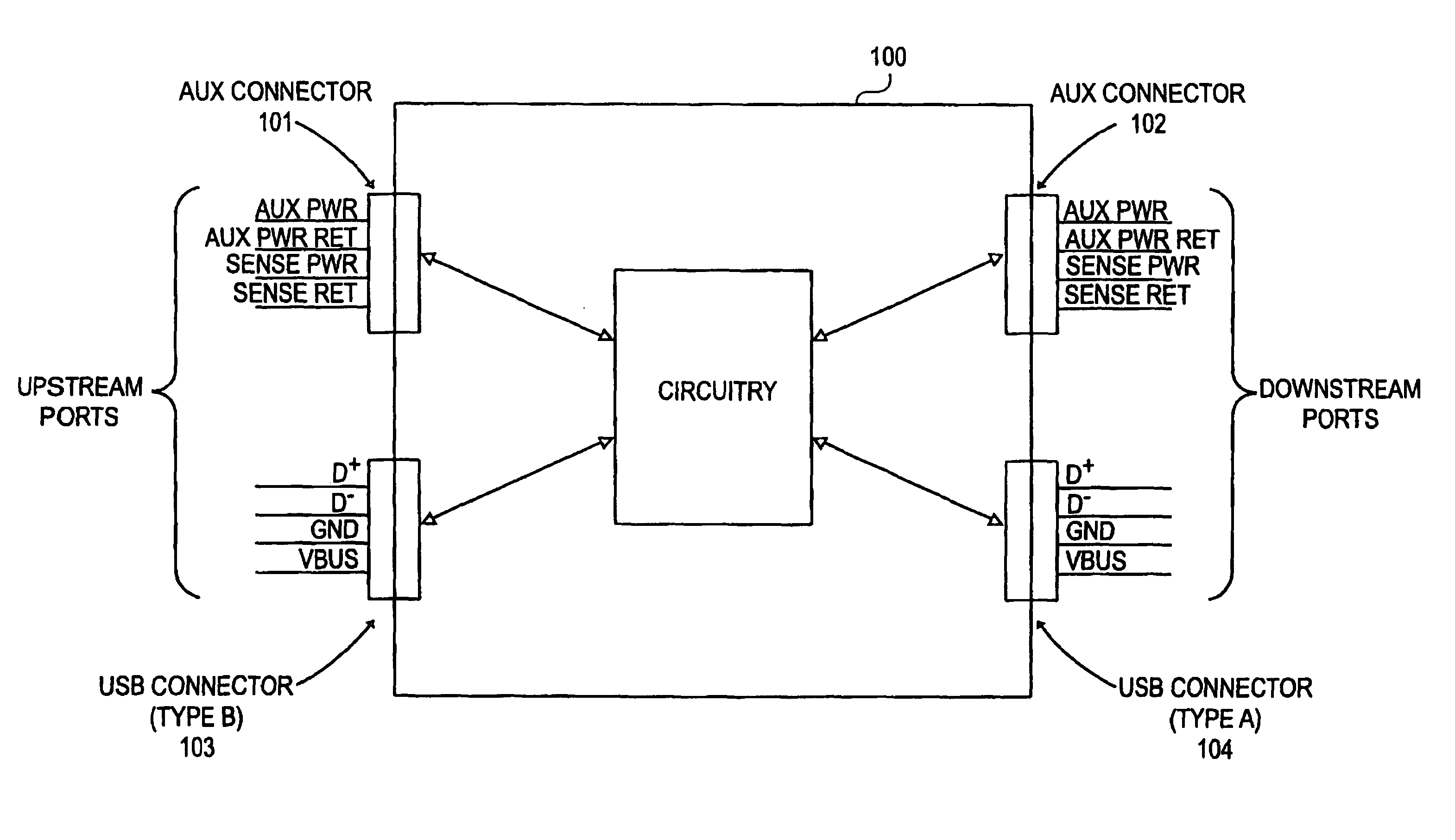

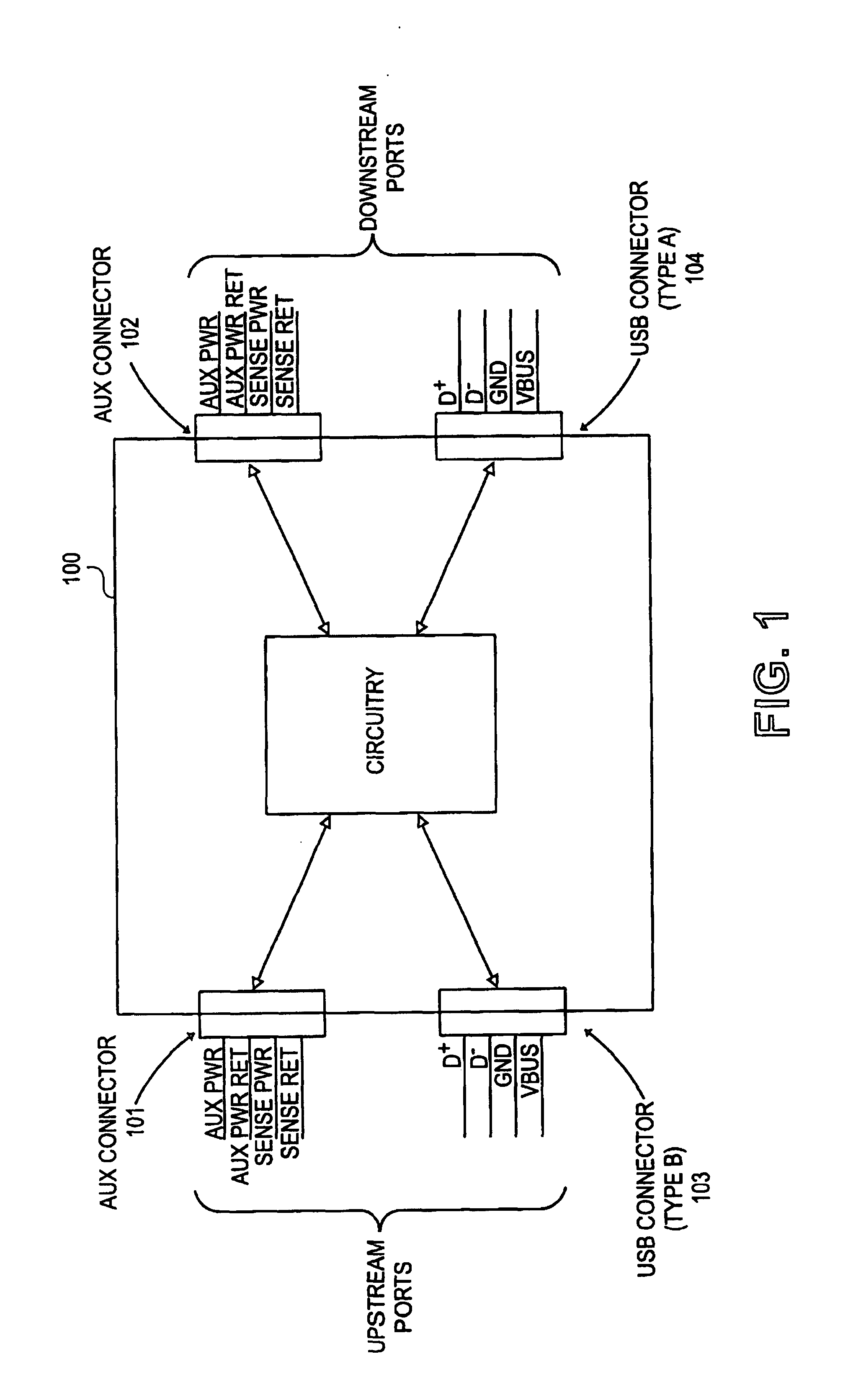

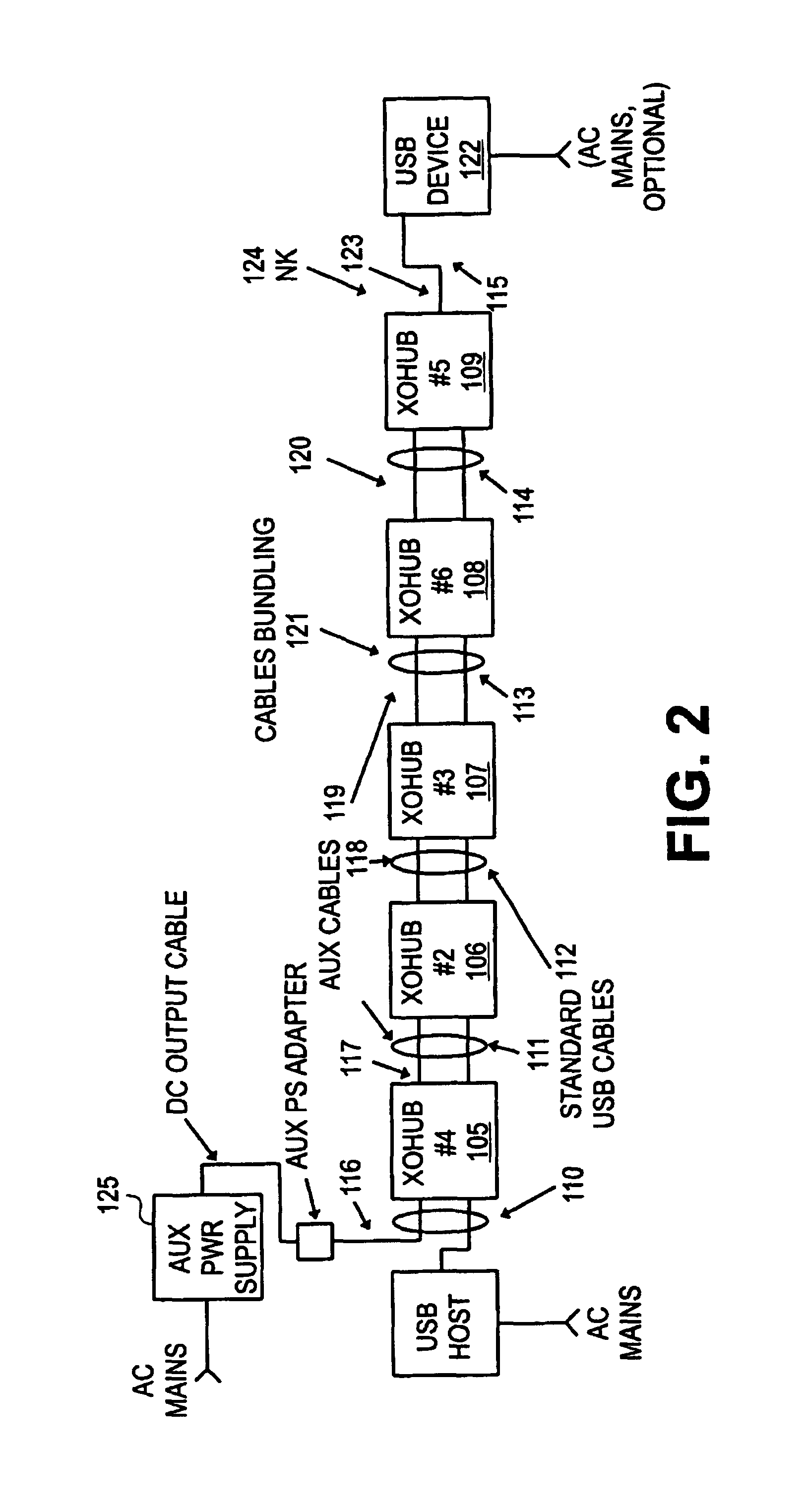

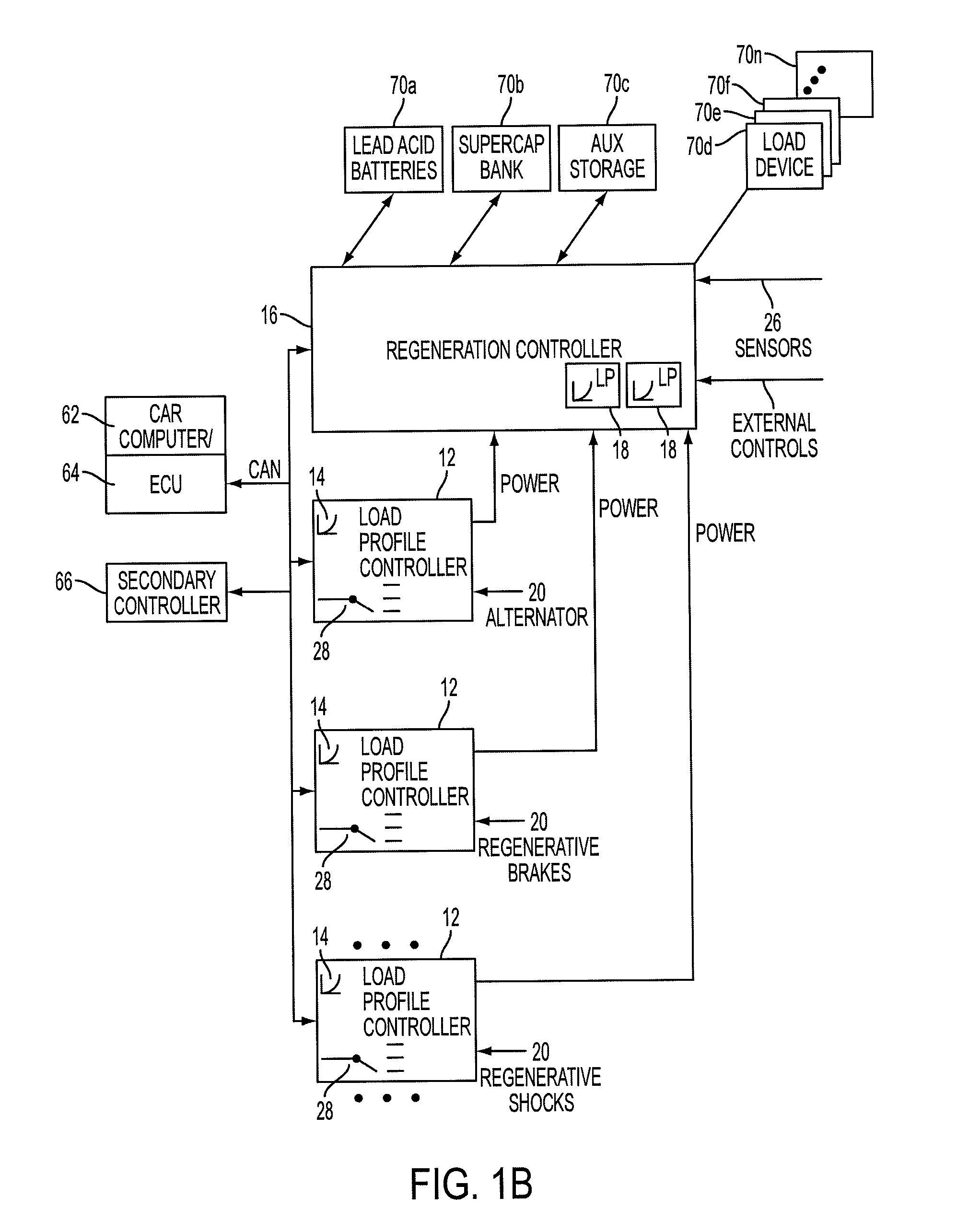

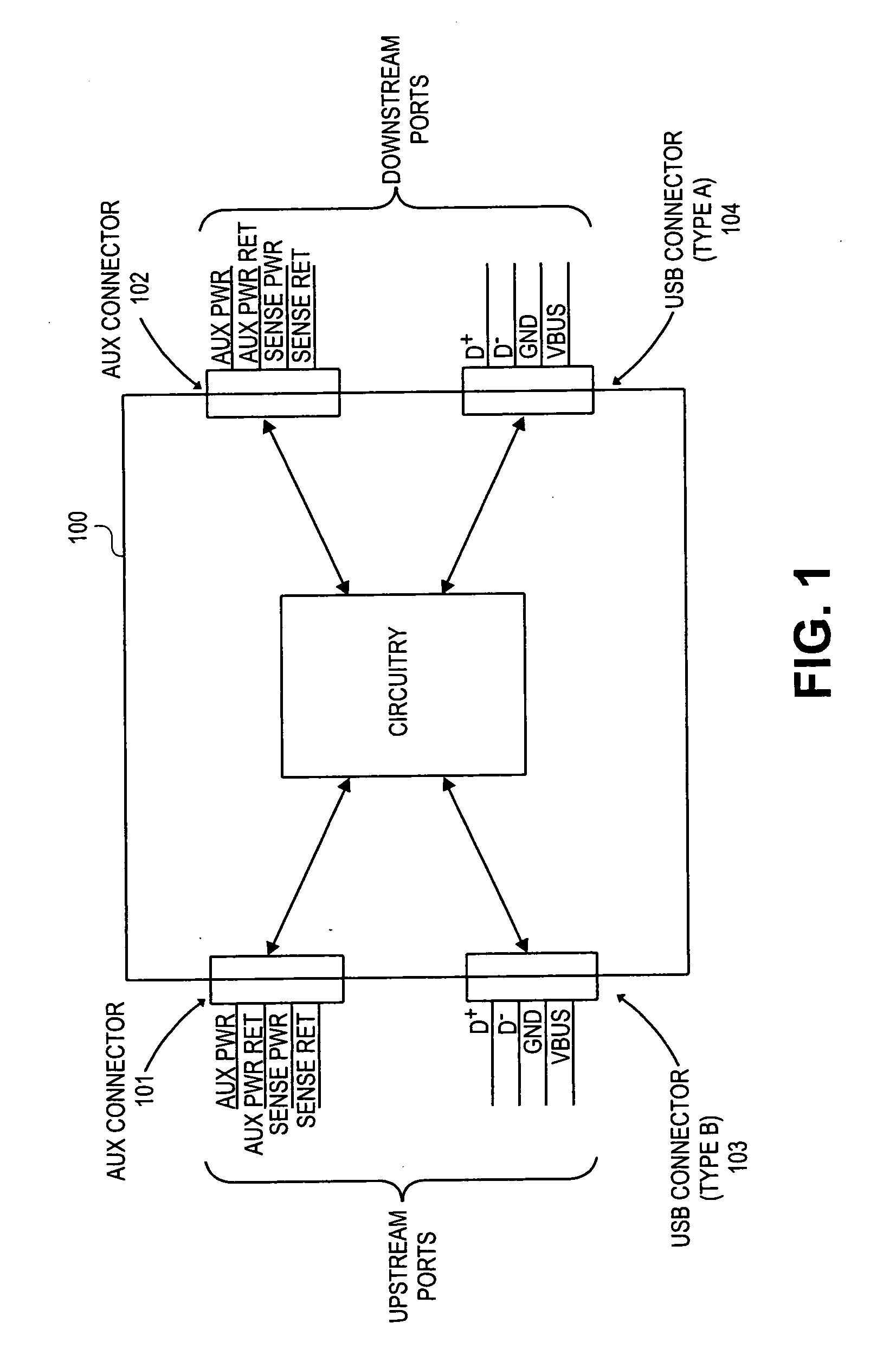

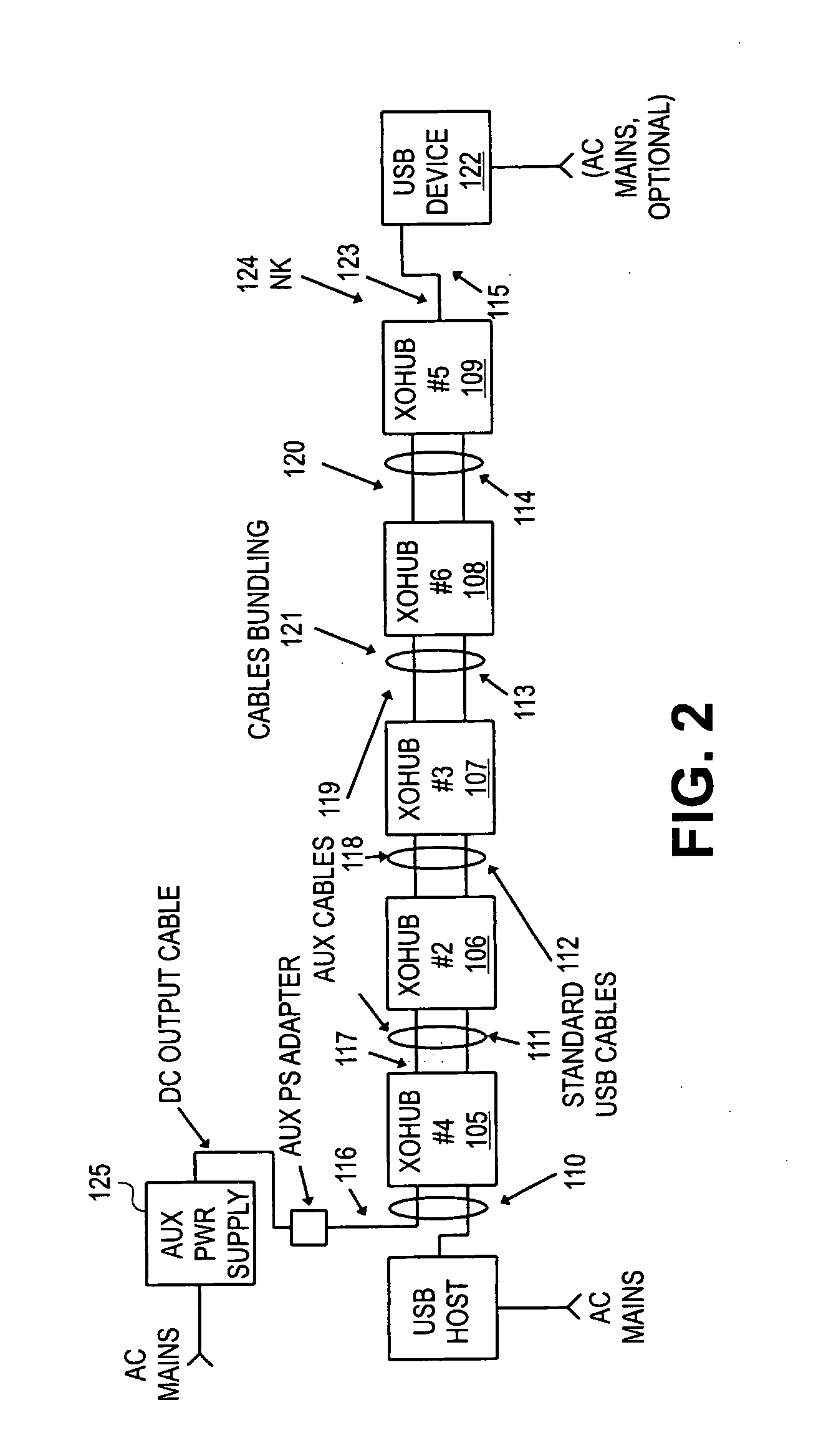

Method and apparatus for extending communications over USB

Method and apparatus are described for improving information transfer over USB. In one approach, hub-based extension is realized wherein power is distributed using auxiliary wiring distinct from signal and power wiring present in conventional USB cabling. Additional signals allow optimization of power distribution for powering attached devices, and for detecting and handling illegal connection configurations.In another approach, improvements are realized through use of alternative signaling techniques which eschew reflective and high-speed common-mode signaling. Described are various configuration, media and signal-protocol combinations, including implementations containing embedded hubs. Methods ensuring reliable system behavior are also described, including determination of extension path delay and use of topology-enforcement hubs.In other approaches, further improvements are realized by allowing information exchanges to take longer than the nominal timeout period, or by allowing host requests to be delayed for transmission until the extended bus is available for use.

Owner:INTEL CORP

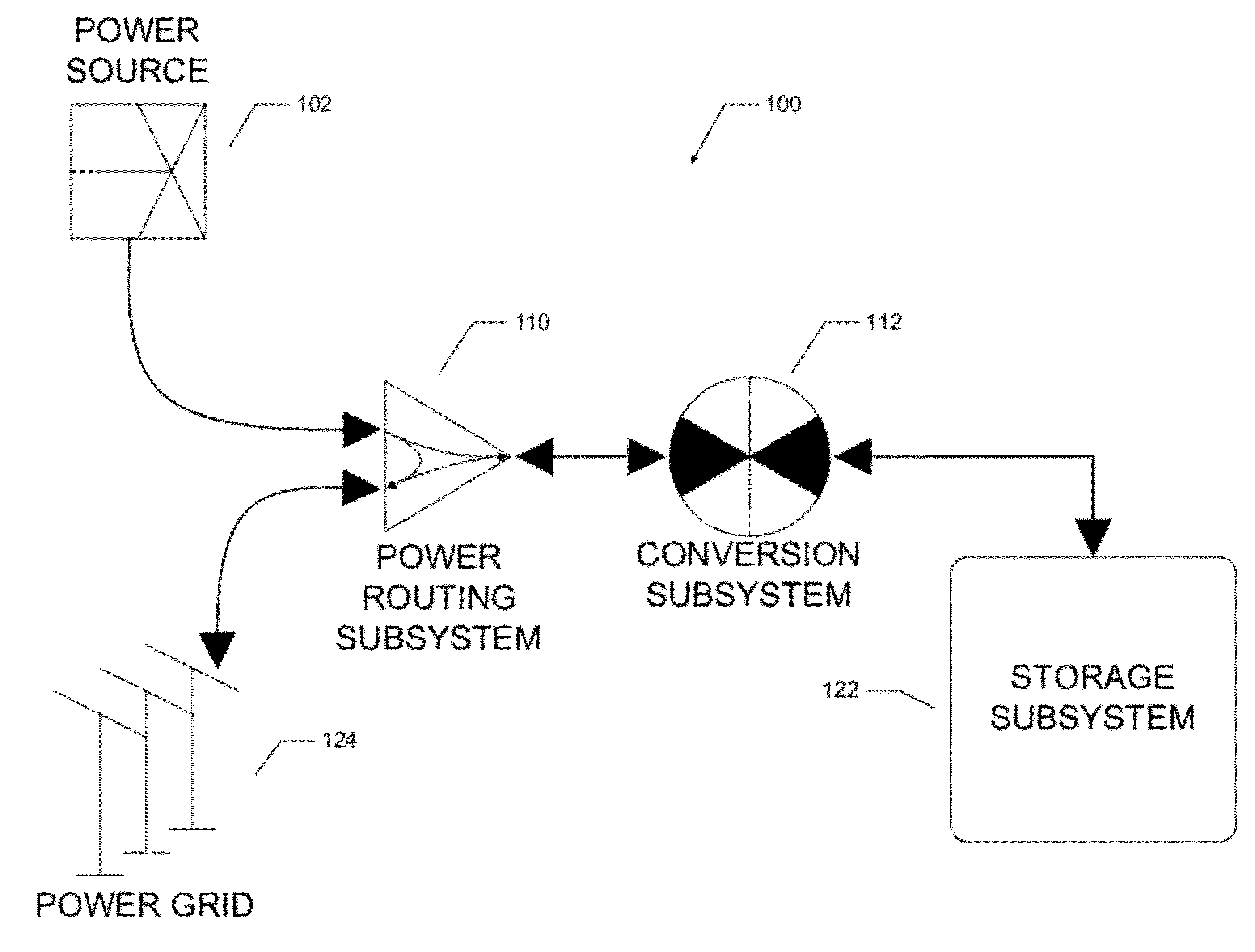

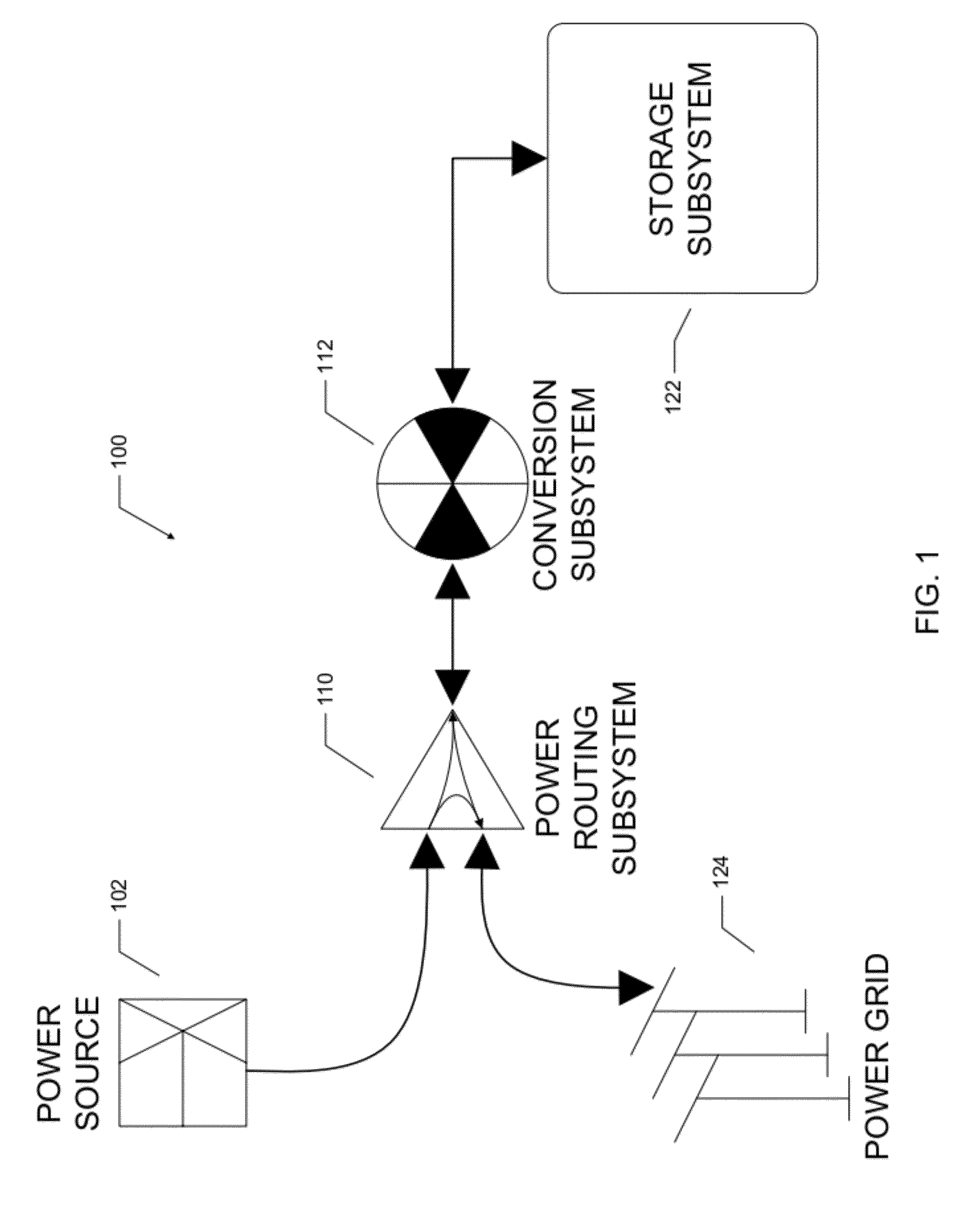

System and method for conserving energy resources through storage and delivery of renewable energy

ActiveUS20120191262A1Winning priceMechanical power/torque controlLevel controlPower gridConservation energy

A system for encouraging the use of renewable energy sources and suitable for the conservation of energy resources through the efficient management of energy storage and delivery includes connections to a power source, an energy storage subsystem, and a power grid. The system includes a power routing subsystem coupled to the source and grid, and adapted to operate in a bypass mode, in which energy is transferred from the source to the grid. The system includes a conversion subsystem coupled to the routing and storage subsystems, and switchable in substantially real-time between a storage mode, in which energy is transferred from the routing to the storage subsystem, and a generation mode, in which energy is transferred from the storage to the routing subsystem for delivery to the grid. The system also includes a controller for directing the modes based at least in part on a market factor.

Owner:NRSTOR INC

Master slice LSI and layout method for the same

InactiveUS6271548B1Semiconductor/solid-state device detailsSolid-state devicesLine widthMiniaturization

A master slice layout technology is provided to improve integration density of a semiconductor integrated circuit such as ASIC. In particular, a plurality of gate basic cells are arranged on a semiconductor chip and then a wiring channel grid having non-uniform pitches is defined on the gate basic cells. If a layout of metal wirings is designed along the wiring channel grid, miniaturizable patterns can be set to smaller values while maintaining line widths of predetermined metal wirings such as power supply wirings at preselected values. Since flexibility for the layout of the metal wiring layers is large, miniaturization of the patterns can be attained even if design rules for basic cell process and wiring process are different.

Owner:KK TOSHIBA

System and method for control for regenerative energy generators

ActiveUS8392030B2Safe and efficient chargingSupply energyAuxillary drivesLevel controlArea networkOn board

A device and system that can dynamically provide variable load on a generator and intelligently distribute generated power to loads and energy storage devices is disclosed. One system includes load profile controllers that employ a switching strategy to dynamically vary the load the generator induces while producing regenerative energy. This switching strategy may allow for a wide dynamic range of configurable damping characteristics, as well as decouple generator damping and the system output power. Multiple load profile controllers can be used together via a communications network, such as a vehicle controller area network (CAN) bus. A central regeneration controller or existing electronic control unit (ECU) can issue commands to change damping performance in different load profile controllers. By networking multiple load profile controllers together in either a distributed or centralized manner, the system may allow for intelligent power routing, coordination of multiple energy-generating devices (such as regenerative shocks and brakes), and improved utilization of on-board energy storage devices.

Owner:CLEARMOTION INC

Method and apparatus for extending communications over USB

InactiveUS20060020736A1Long processEnergy efficient ICTMultiplex communicationEngineeringSignaling protocol

Method and apparatus are described for improving information transfer over USB. In one approach, hub-based extension is realized wherein power is distributed using auxiliary wiring distinct from signal and power wiring present in conventional USB cabling. Additional signals allow optimization of power distribution for powering attached devices, and for detecting and handling illegal connection configurations. In another approach, improvements are realized through use of alternative signaling techniques which eschew reflective and high-speed common-mode signaling. Described are various configuration, media and signal-protocol combinations, including implementations containing embedded hubs. Methods ensuring reliable system behavior are also described, including determination of extension path delay and use of topology-enforcement hubs. In other approaches, further improvements are realized by allowing information exchanges to take longer than the nominal timeout period, or by allowing host requests to be delayed for transmission until the extended bus is available for use.

Owner:INTEL CORP

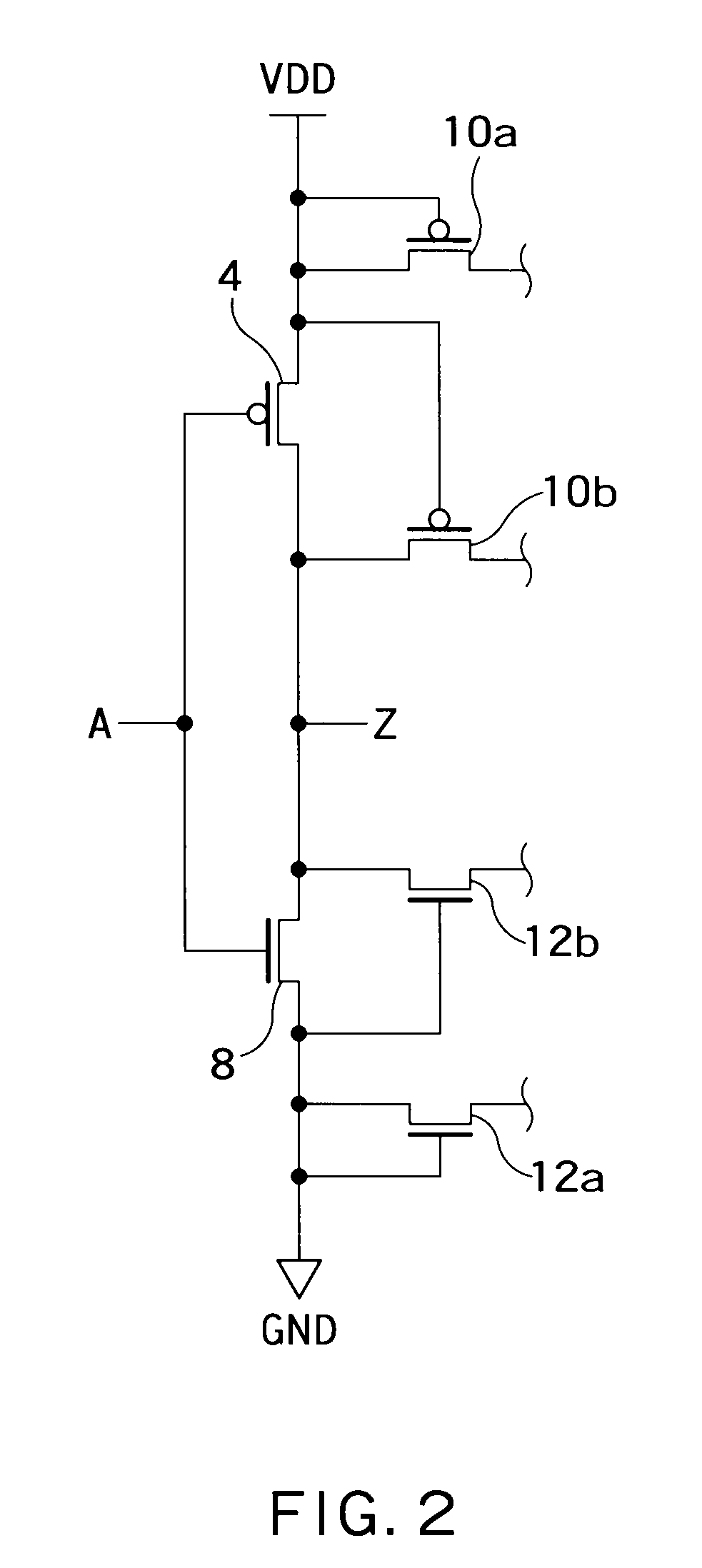

Semiconductor integrated circuit

A semiconductor integrated circuit having a substantially rectangular standard cell divided by first borderlines opposed to other standard cells longitudinally adjacent to the standard cell and second borderlines opposed to other standard cells laterally adjacent to the standard cell, the standard cell has: a p-type MOS transistor having first diffused regions and a first gate electrode; an n-type MOS transistor having second diffused regions and a second gate electrode with STI disposed for device isolation between the n-type MOS transistor and the p-type MOS transistor substantially in parallel with the first borderlines; dummy p-type MOS transistors having third gate electrodes disposed on the second borderlines so as to be adjacent to the first diffused regions of the p-type MOS transistor, the third gate electrodes being connected to power supply wiring so as to turn off the dummy p-type MOS transistors; and dummy n-type MOS transistors having fourth gate electrodes disposed on the second borderlines so as to be adjacent to the second diffused regions of the n-type MOS transistor, the fourth gate electrodes being connected to ground wiring so as to turn off the dummy n-type MOS transistors.

Owner:KK TOSHIBA

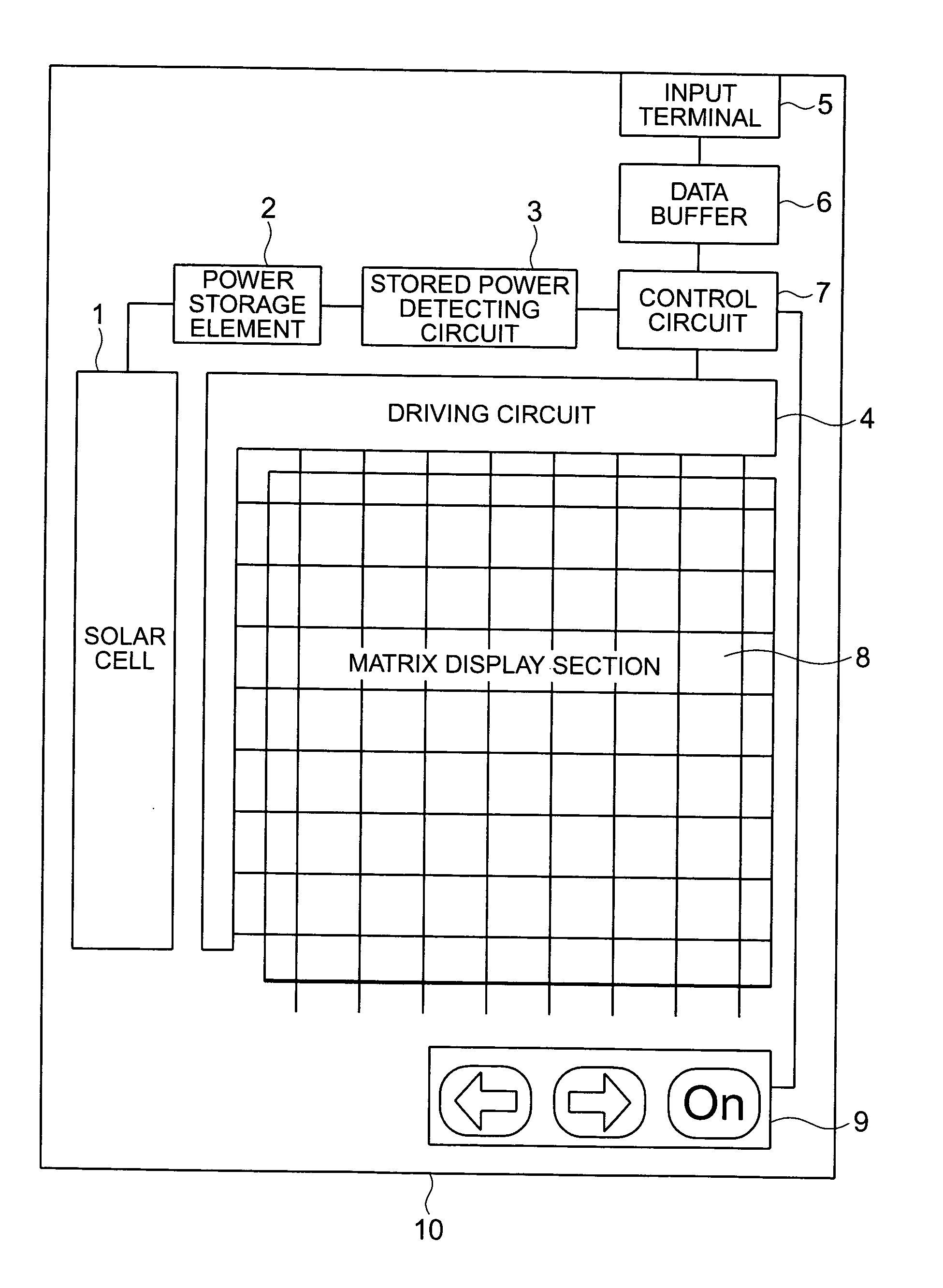

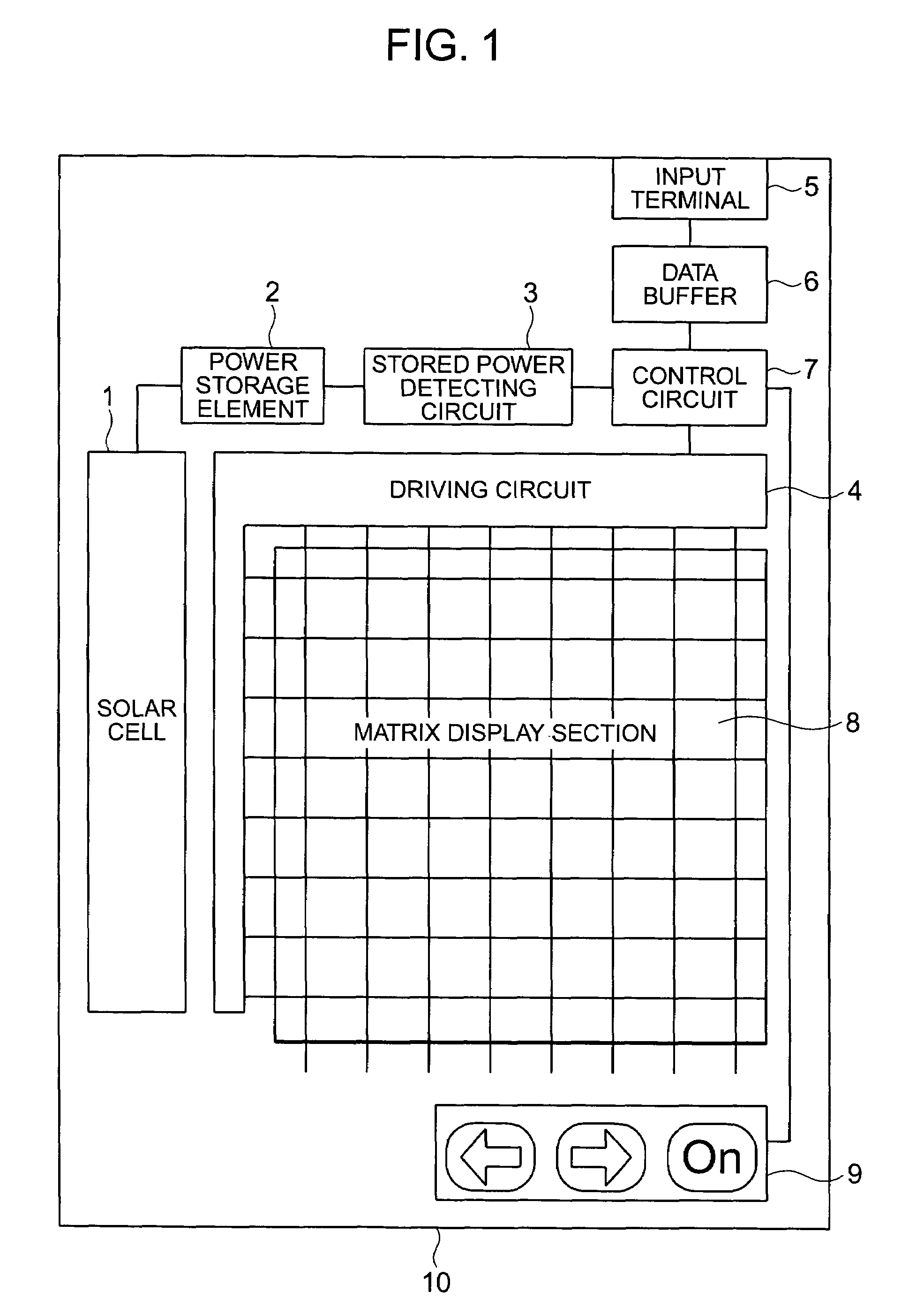

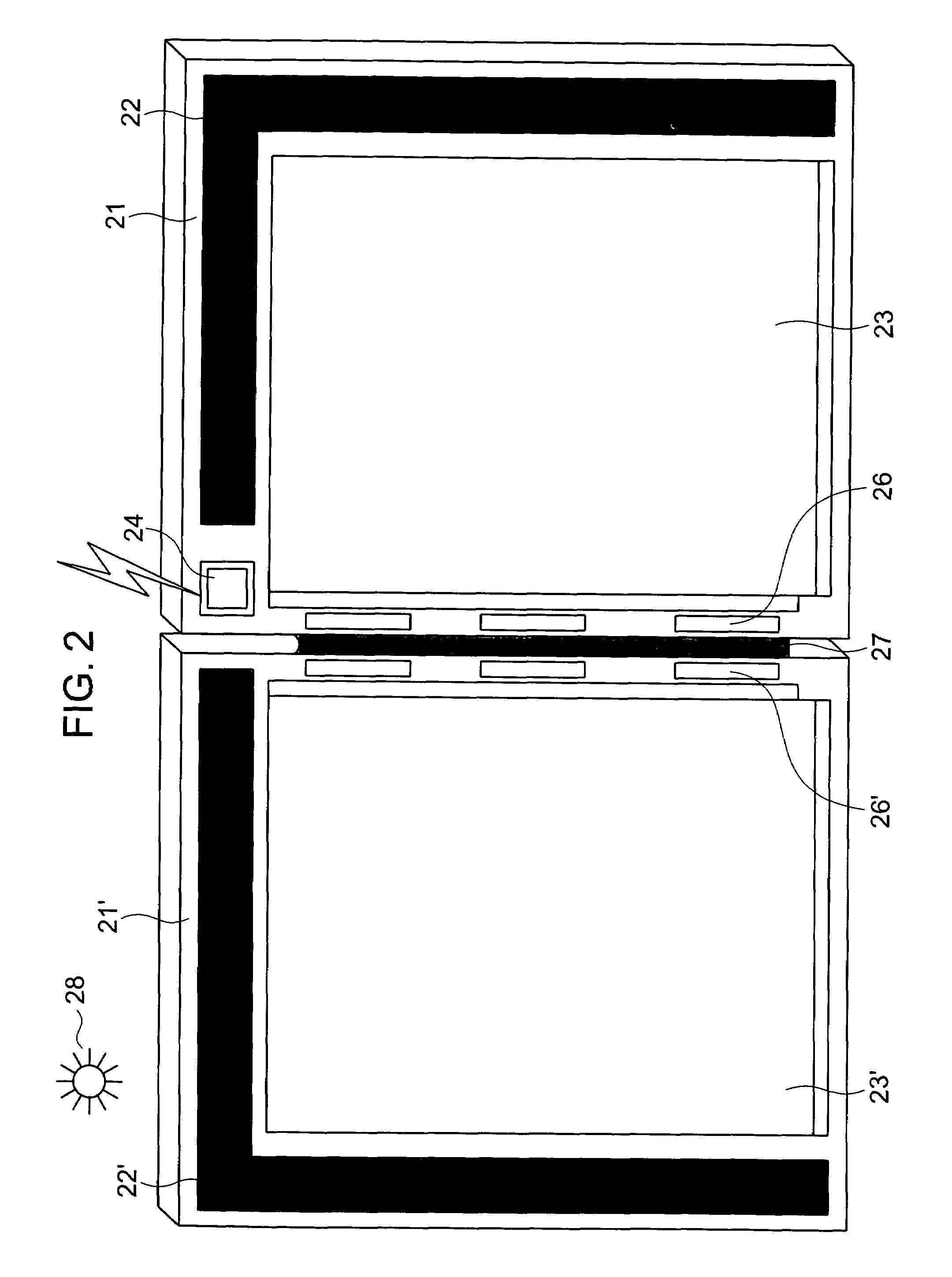

Low-power driven display device

InactiveUS7319465B2Reduce necessityCathode-ray tube indicatorsNon-linear opticsElectrical batteryDisplay device

For a display device having a solar cell and a power buffer for keeping stored electric power, a display system which has a low-power drive mode, self-contained power and no need for recharging or power wiring is provided. The display system includes a solar cell using a thin-film semiconductor, a power storage element for temporarily storing the produced power, a driving circuit, a matrix display unit, a display rewrite instruction unit for inputting screen rewrite and a control circuit and starts rewriting a display when power sufficient to rewrite an image screen is stored in the solar cell. The display device having remarkable portability and no limited battery life, which controls a display mode depending on the power produced by the solar cell, can display even when power generation is low and allows self-contained power even if the storage element has a small capacity, can be obtained.

Owner:HITACHI LTD

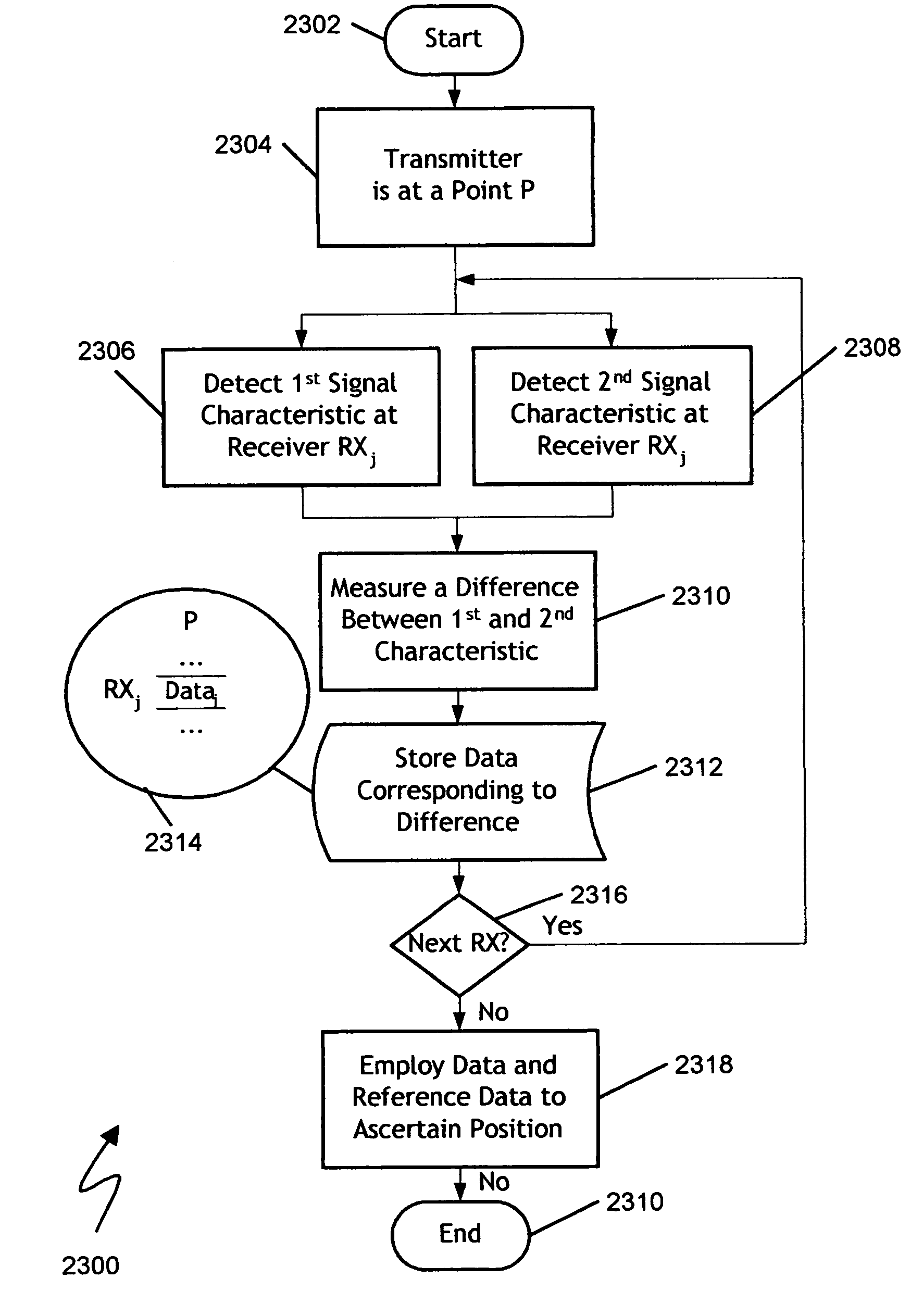

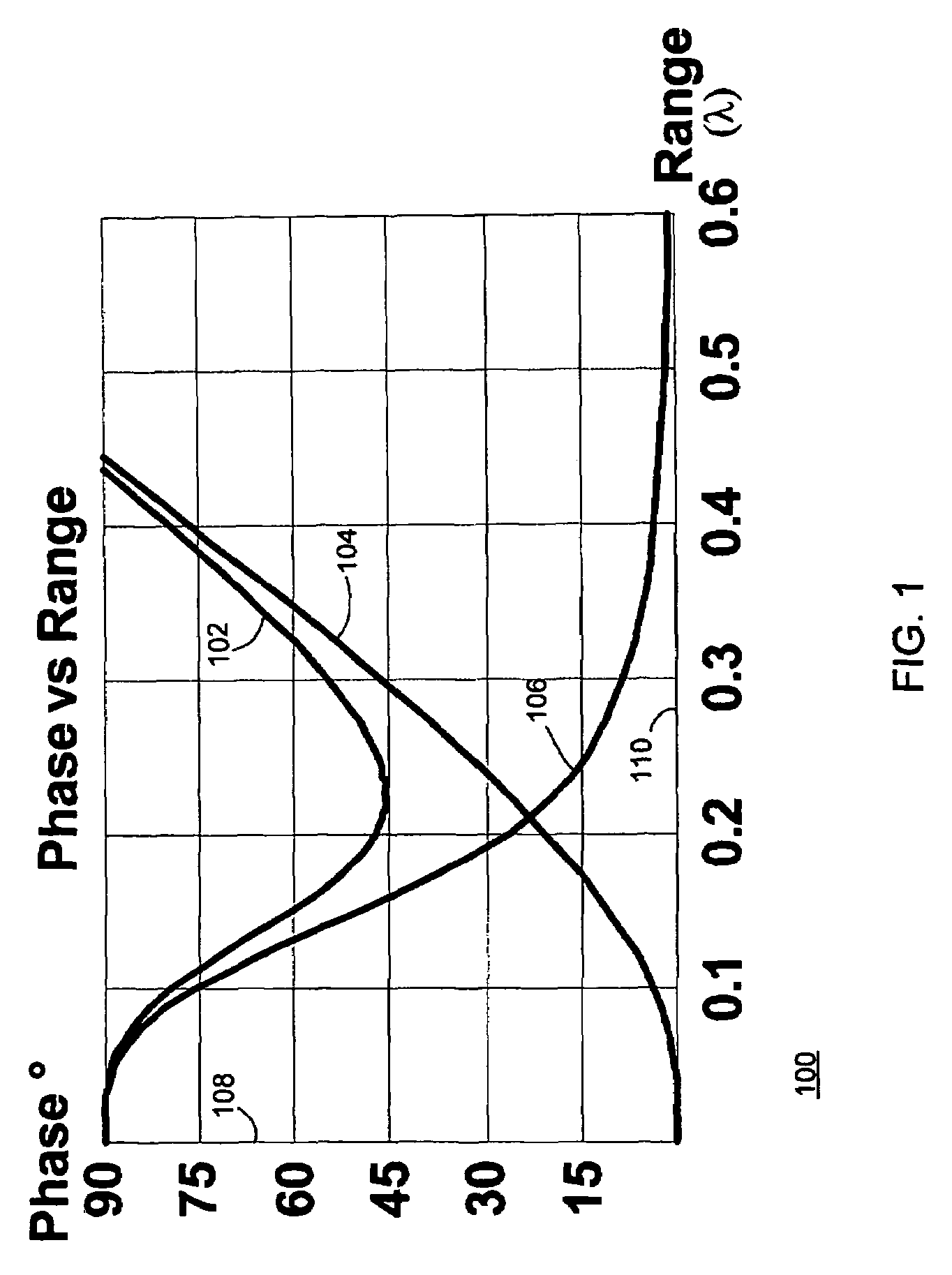

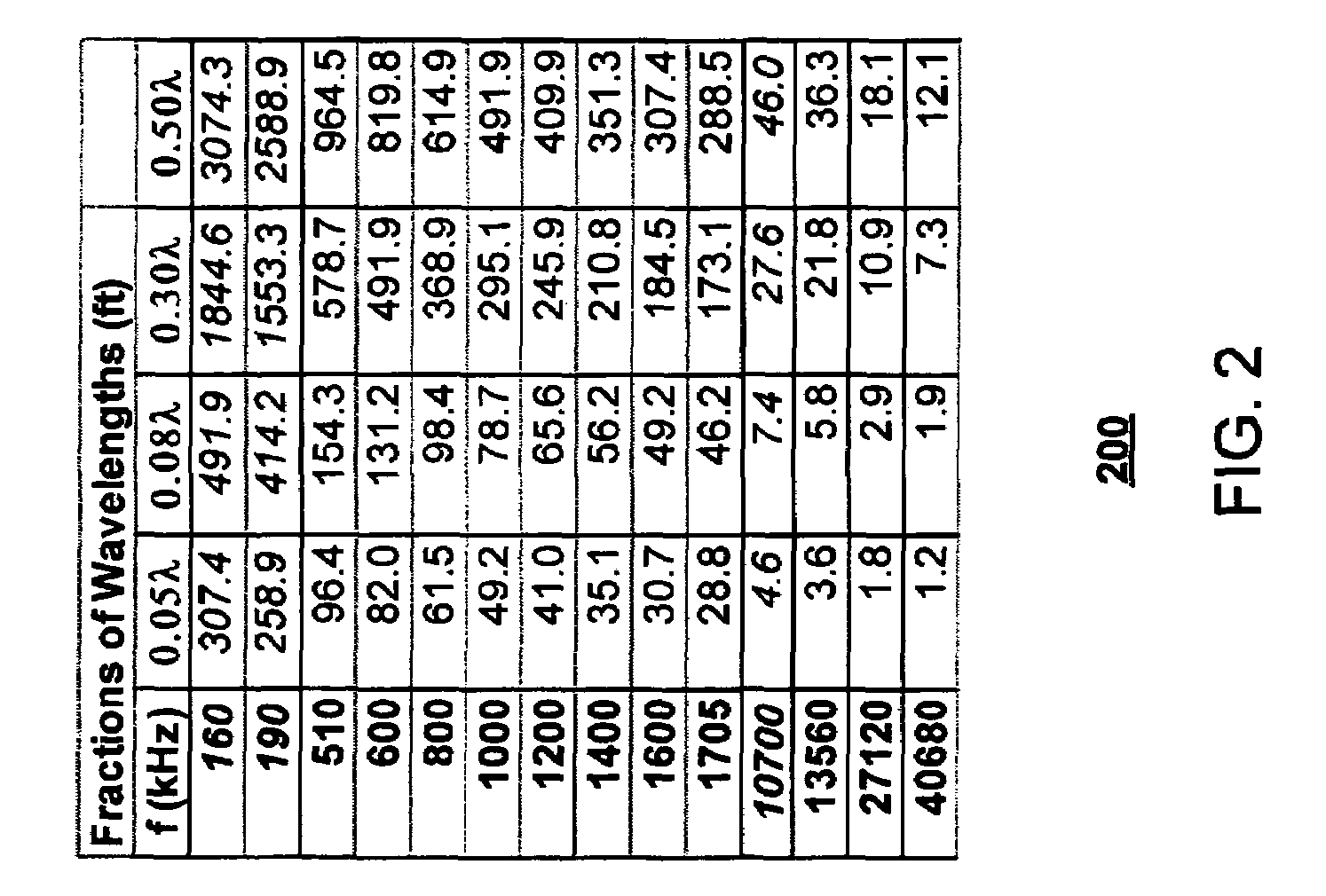

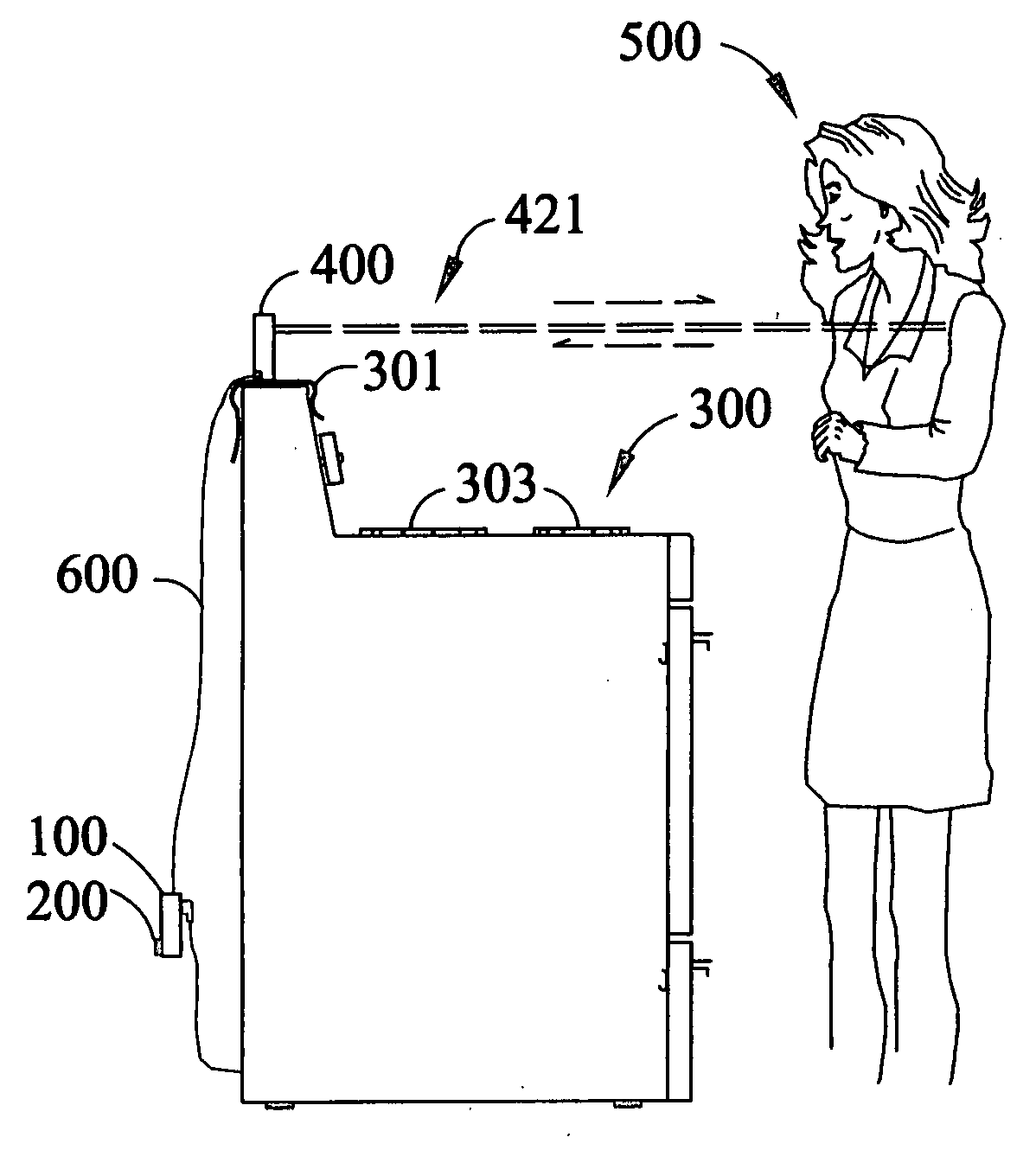

Near field electromagnetic positioning system and method

A system and method for electromagnetic position determination utilizing a calibration process. For calibration, a transmitter is positioned at multiple locations in an area of interest and multiple receivers receive and record signal characteristics from the transmitter to generate a calibration data set. The unknown position of a transmitter may be determined by receiving signals from the transmitter by multiple receivers. A locator data set is generated based on the comparison between two received signal characteristics determined for each receiver. The locator data set is compared with the calibration data set to determine the unknown position. In one embodiment, the signal comparisons are the differences between electric and magnetic field phase. Further embodiments utilize signal amplitude differences. A reciprocal method utilizing a single receiver and multiple transmitter locations is disclosed. A further method is disclosed for determining position by utilizing signals available from existing installed wiring such as power wiring.

Owner:GAN CORP

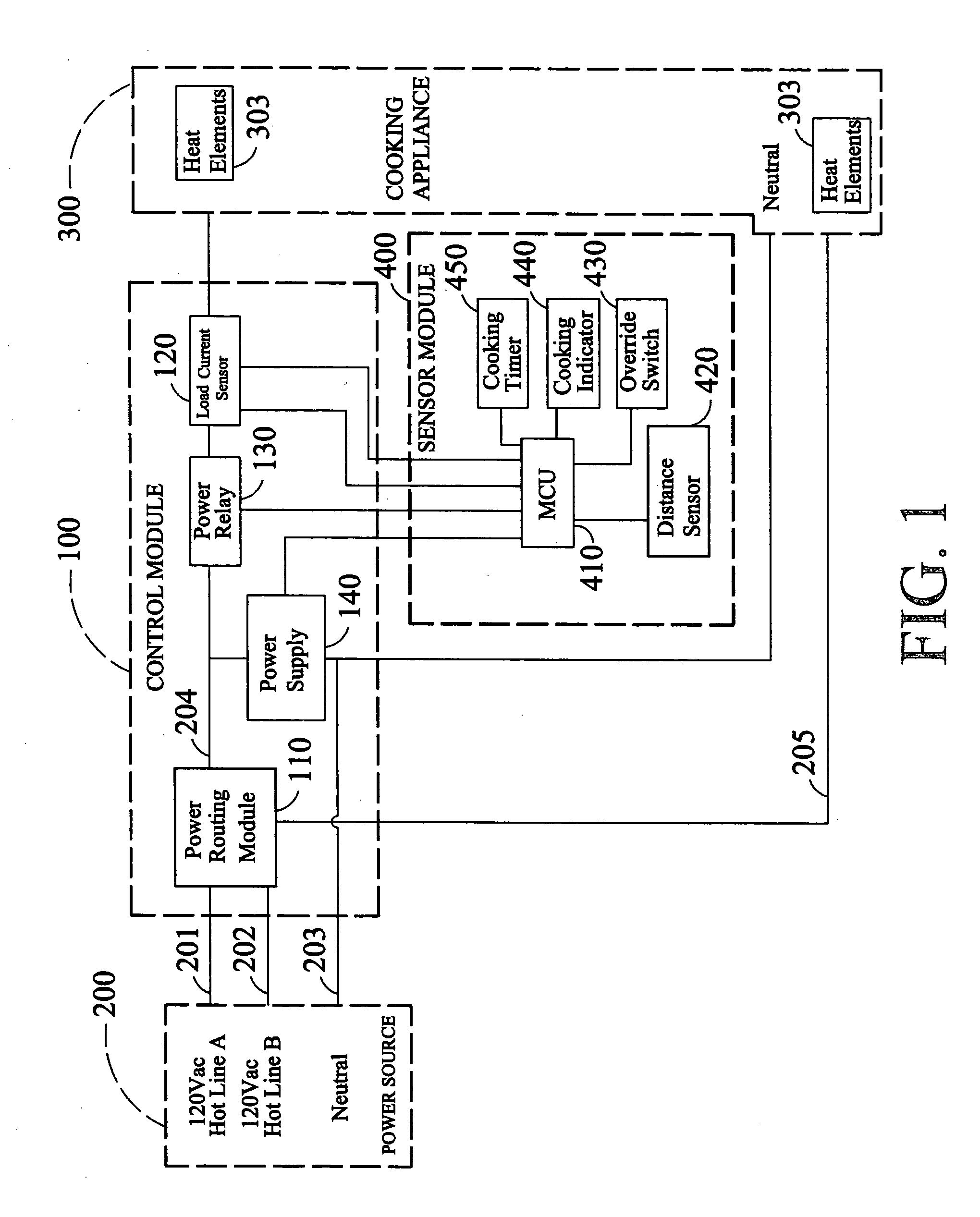

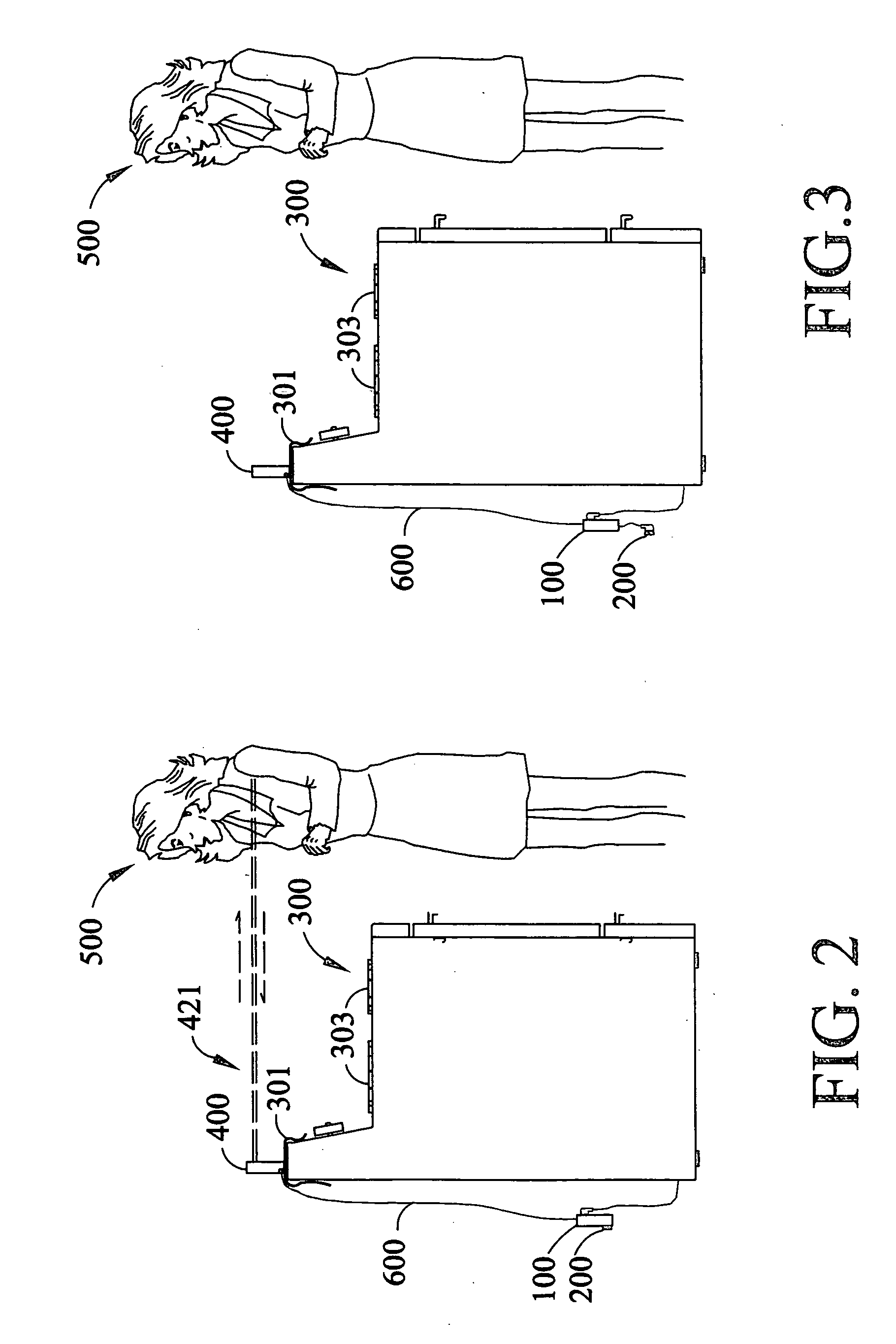

Safety device for regulating electrical power to a cooking appliance

InactiveUS20050109333A1Reduce heat outputReduce electric powerDomestic stoves or rangesLighting and heating apparatusEquipment OperatorEngineering

A safety device for regulating electrical power to a cooking appliance, comprising a control module having a power routing means, a power supply means, a load current sensing means for detecting a load current to the cooking appliance and a power relay means for controlling the electrical current to the cooking appliance, and a sensor module located adjacent to the cooking appliance for observation by an appliance operator and connected to the control module. The sensor module governs the production of the electrical current to the cooking appliance, and has a monitoring means, a distance sensing means, a timer means for showing elapsed cooking time, and a light emitting means. The monitoring means is responsive to outputs of the distance sensing means and includes a timer assembly programmed to a predetermined period of time for responding to the distance sensing means detecting the presence of the appliance operator.

Owner:THOMAS LOWELL RICHARD

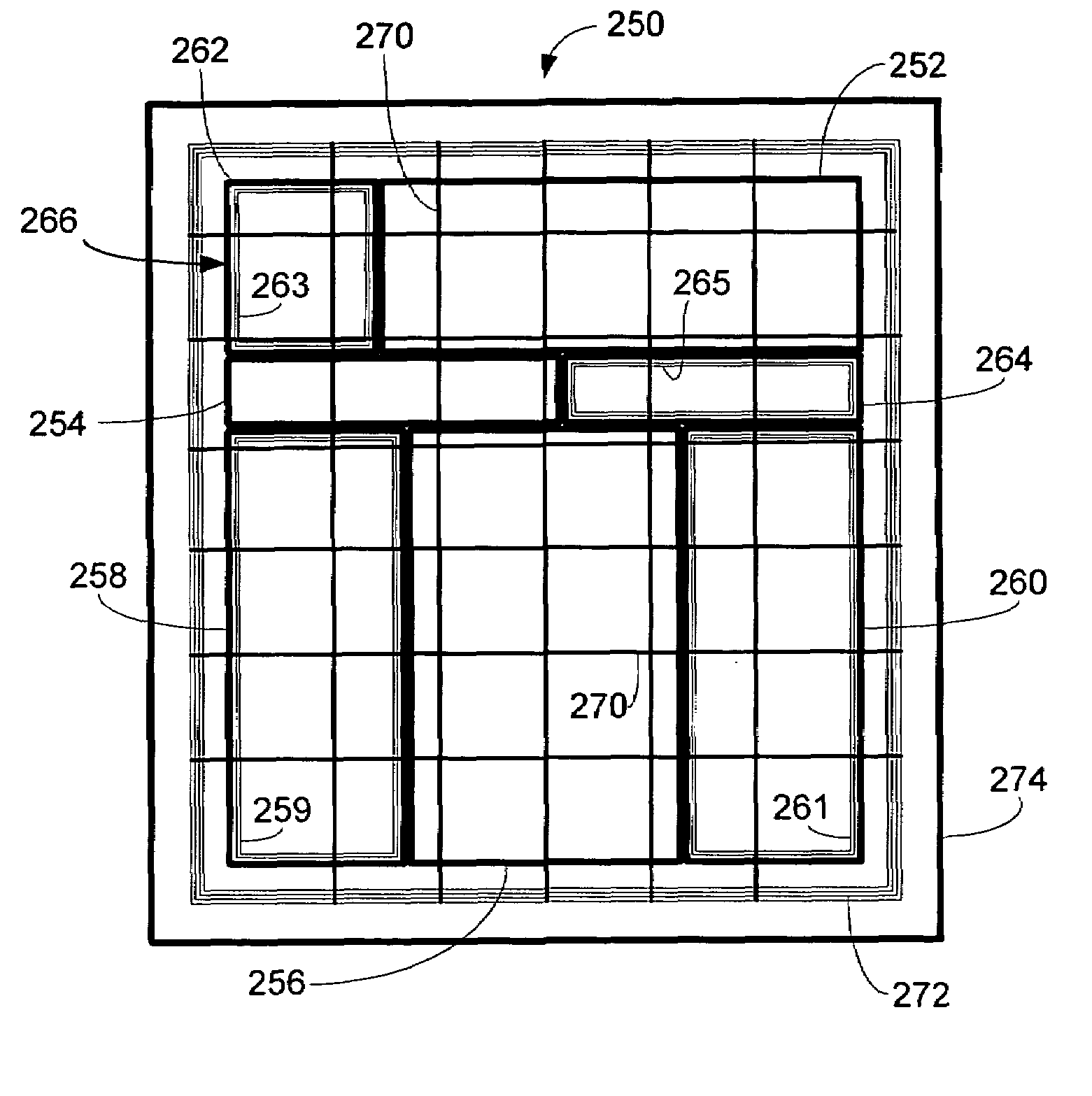

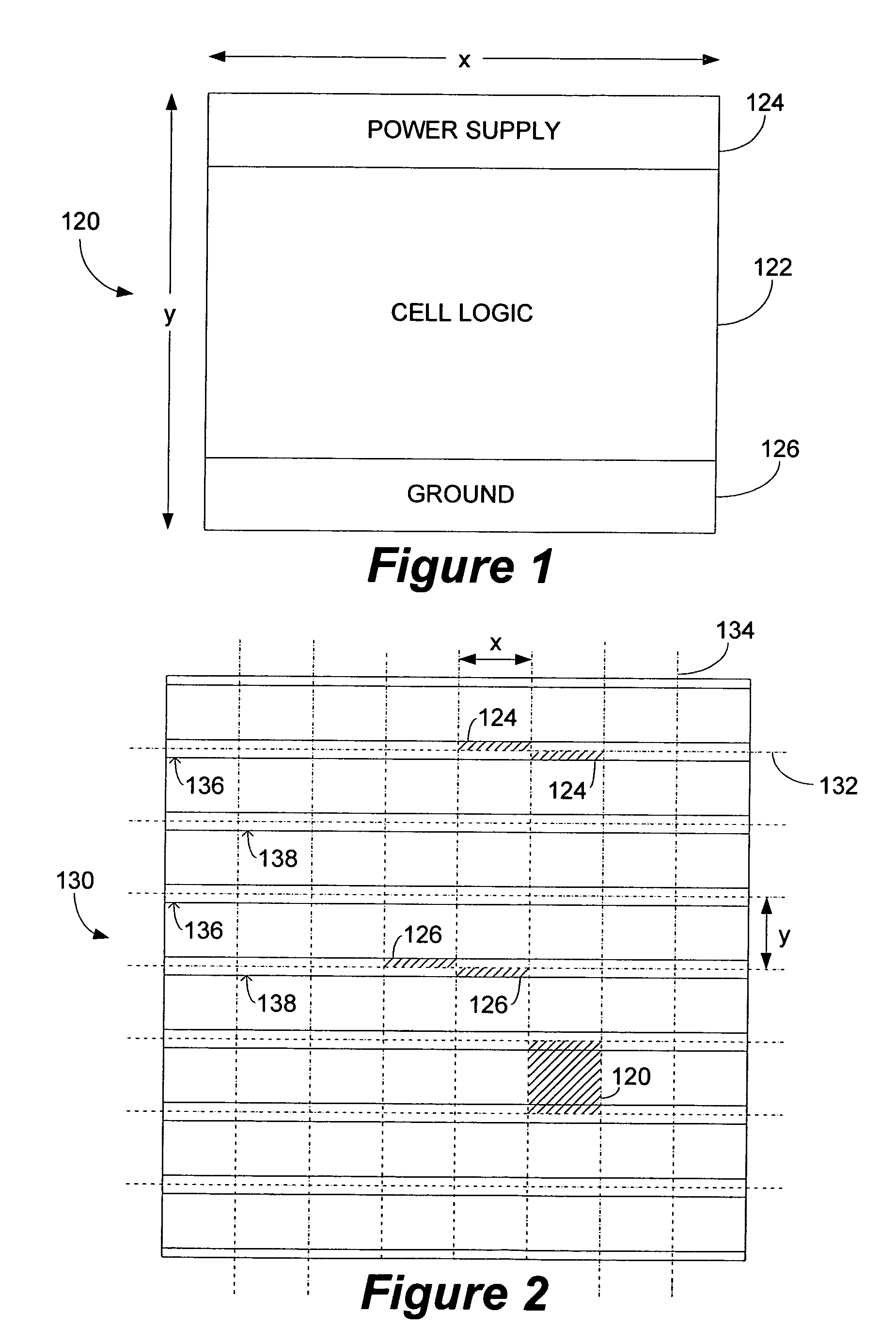

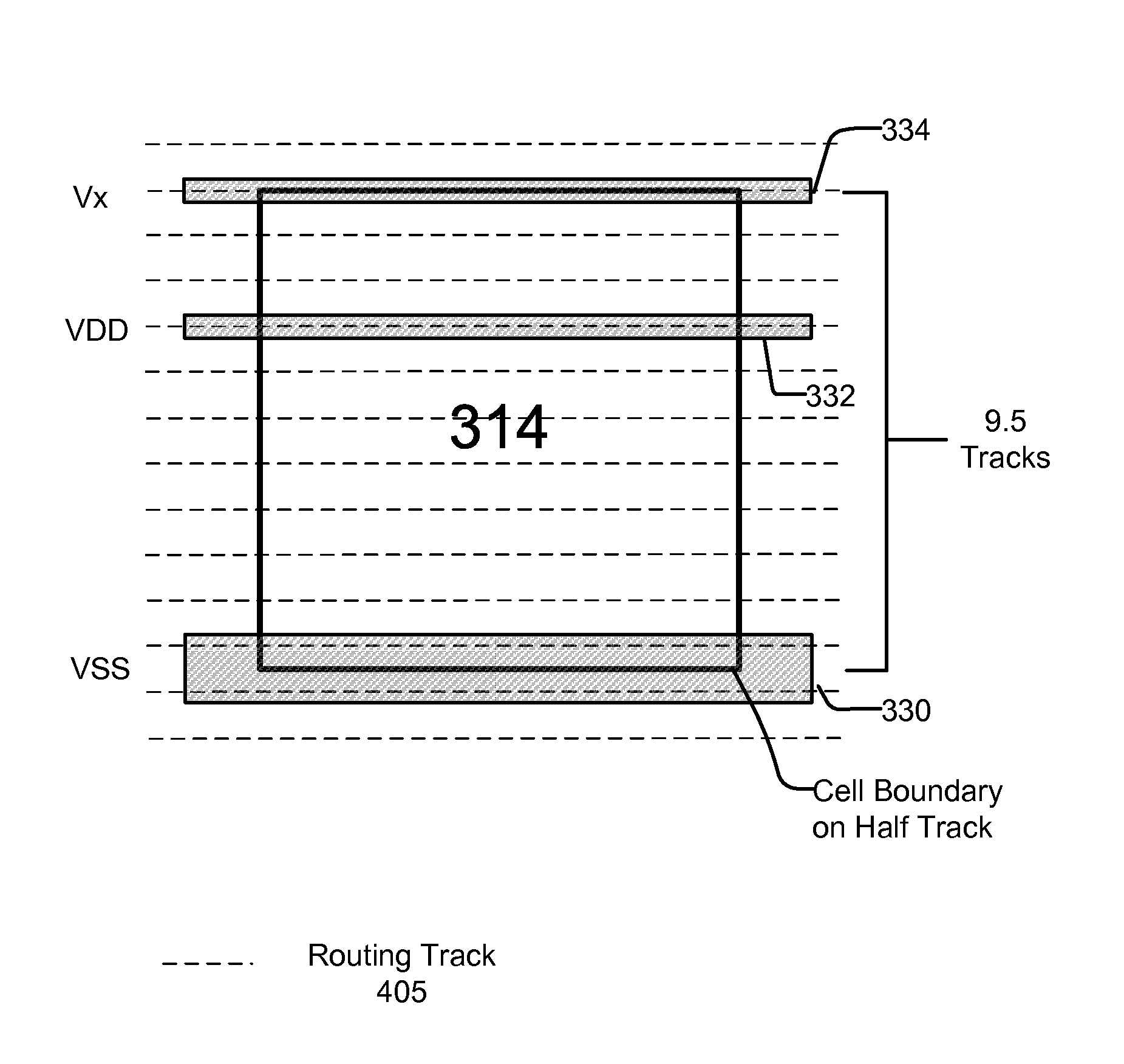

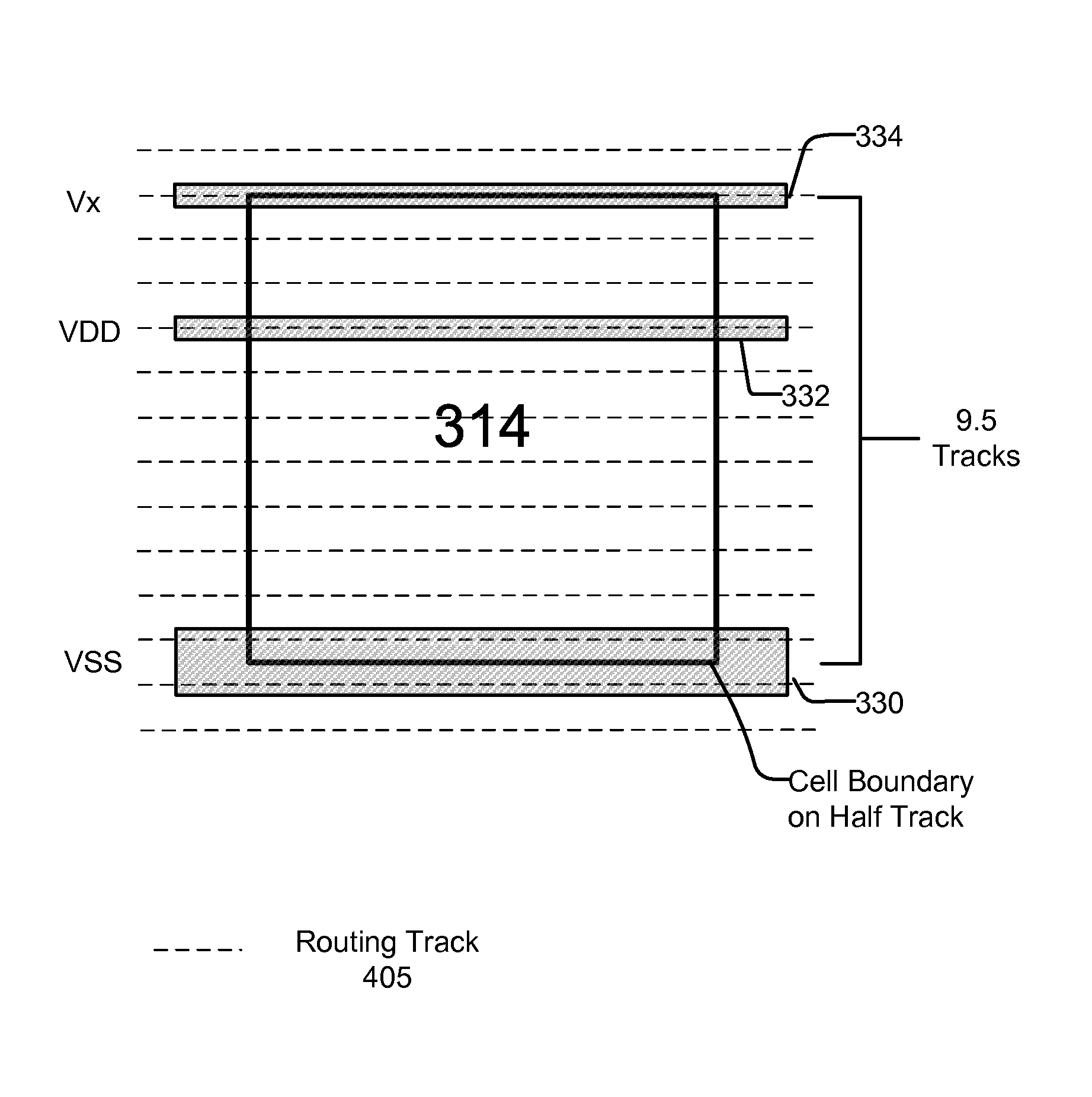

Power Routing in Standard Cell Designs

ActiveUS20120249182A1Small sizePrecise alignmentSolid-state devicesComputer aided designEngineeringCell based

A cell-based architecture for an integrated circuit. A row of cell instances borders a first adjacent row of cell instances along a first boundary and a second adjacent row of cell instances along a second boundary. A first power rail (e.g., carrying an auxiliary voltage) extends along the first boundary. A second power rail (e.g., VSS) extends along the second boundary. The second power rail is wider than the first power rail. Additionally, a third power rail (e.g., VDD) extends across the interior of the second row of cells.

Owner:SYNOPSYS INC

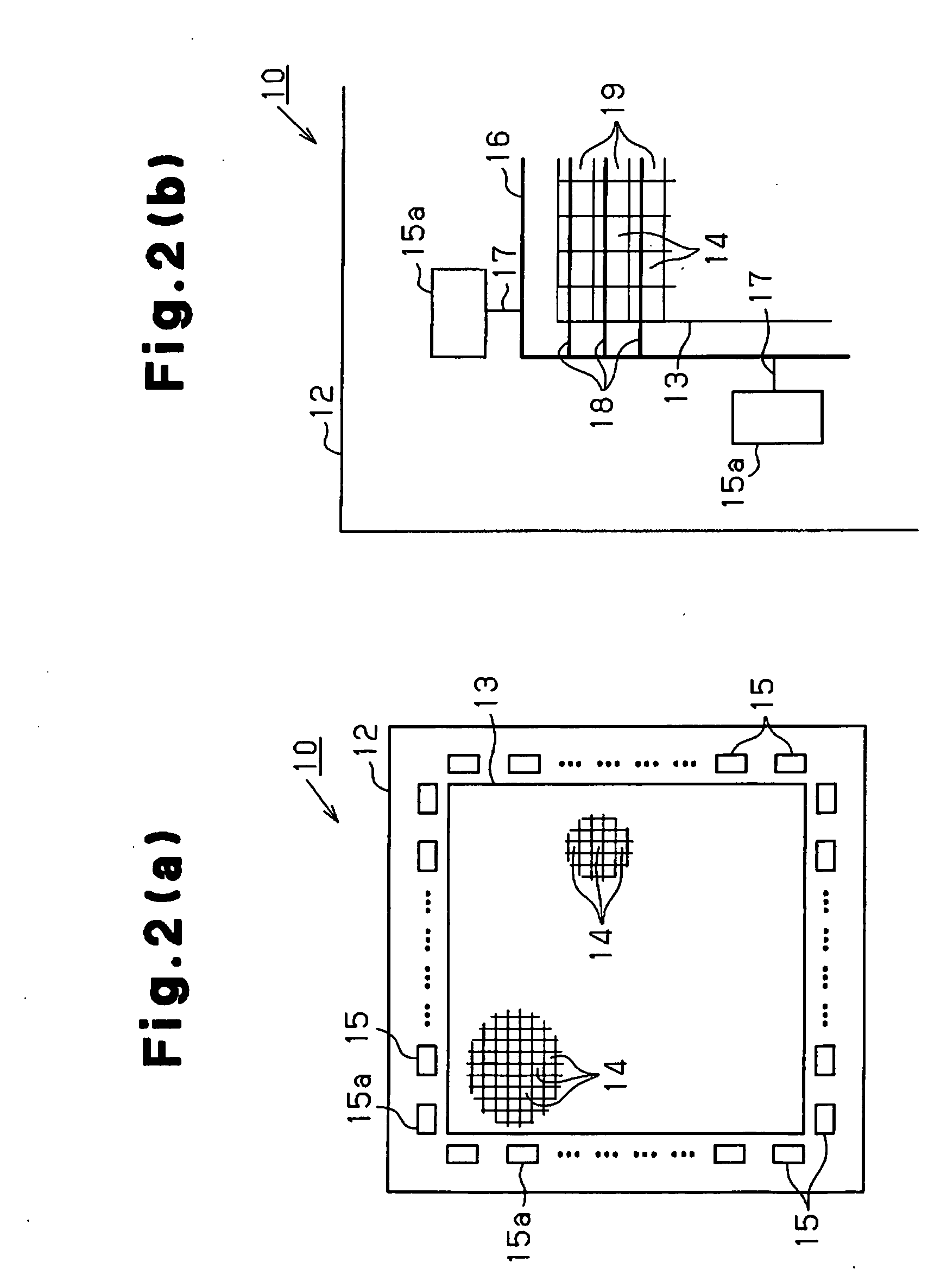

Semiconductor integrated circuit device and its power supply wiring method

InactiveUS20060239102A1Improve stabilityReduce voltage dropSemiconductor/solid-state device detailsSolid-state devicesBasic power supplySemiconductor

The present invention discloses a power supply wiring method for stabilizing operation of a semiconductor integrated circuit device. A power supply mesh 24, which is arranged on an upper layer of a basic power supply wires 18 for supplying power to a logic circuit portion 13, includes vertical reinforcing power supply wires 22 and lateral reinforcing power supply wires 23. The widths of the vertical reinforcing power supply wires and lateral reinforcing power supply wires are optimized to mitigate IR drop or excessive current density in each division unit u0.

Owner:SANYO ELECTRIC CO LTD

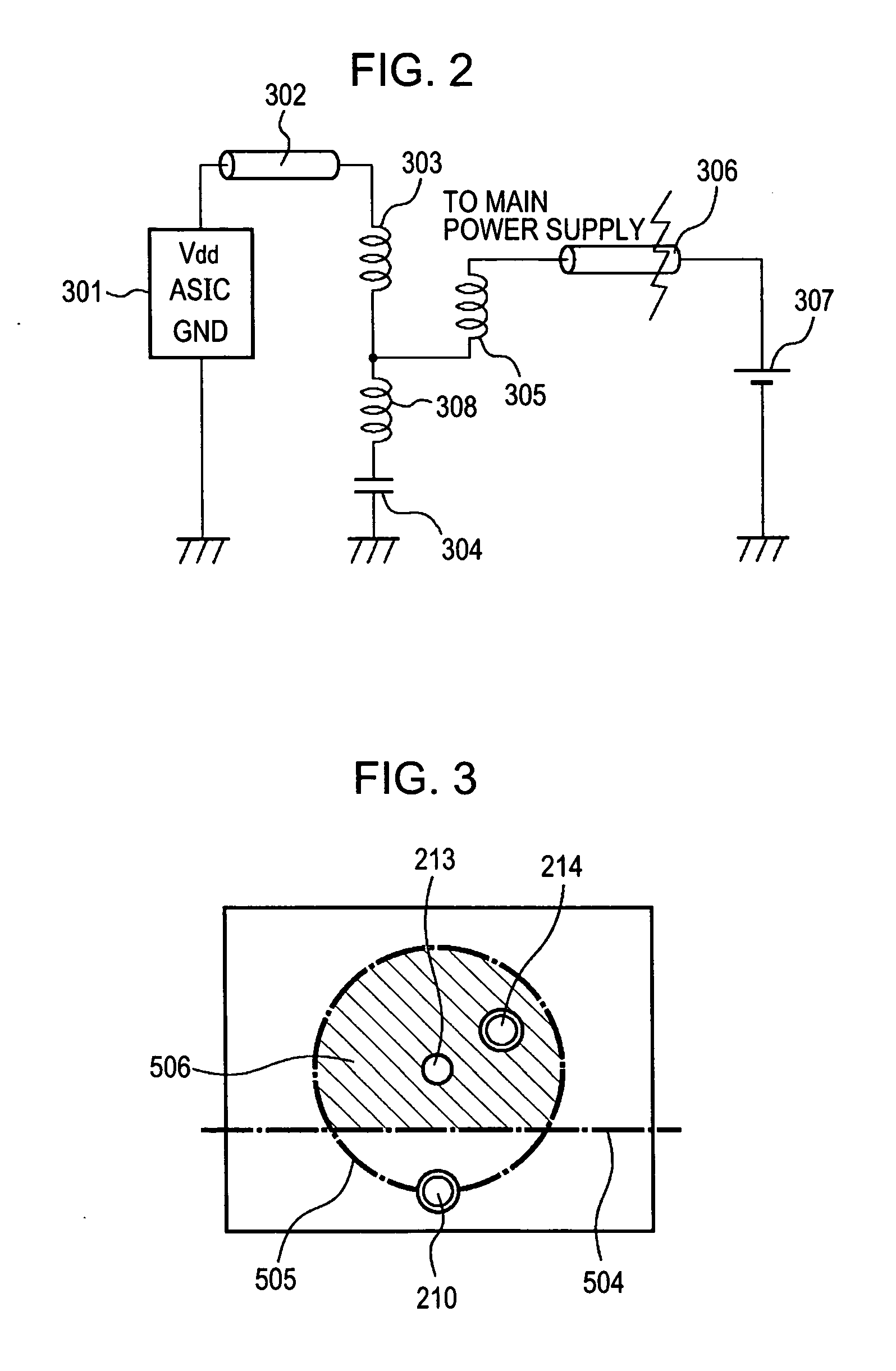

Multilayered printed circuit board

InactiveUS20060050491A1Suppress radiated noiseEasy to useCross-talk/noise/interference reductionPrinted circuit aspectsSurface layerEngineering

A multilayered printed circuit board includes a first surface layer that includes a semiconductor integrated circuit, a second surface layer that includes a bypass capacitor and that is opposite to the first surface layer, a main power supply wiring layer, and a ground layer between the first and second surface layers. In the multilayered printed circuit board, one terminal of the bypass capacitor is connected to a midpoint of a wiring path from the main power supply wiring layer to a power supply terminal of the semiconductor integrated circuit, and an impedance of a first wiring path from the main power supply wiring layer to the terminal of the bypass capacitor is higher than an impedance of a second wiring path from the terminal of the bypass capacitor to the power supply terminal of the semiconductor integrated circuit.

Owner:CANON KK

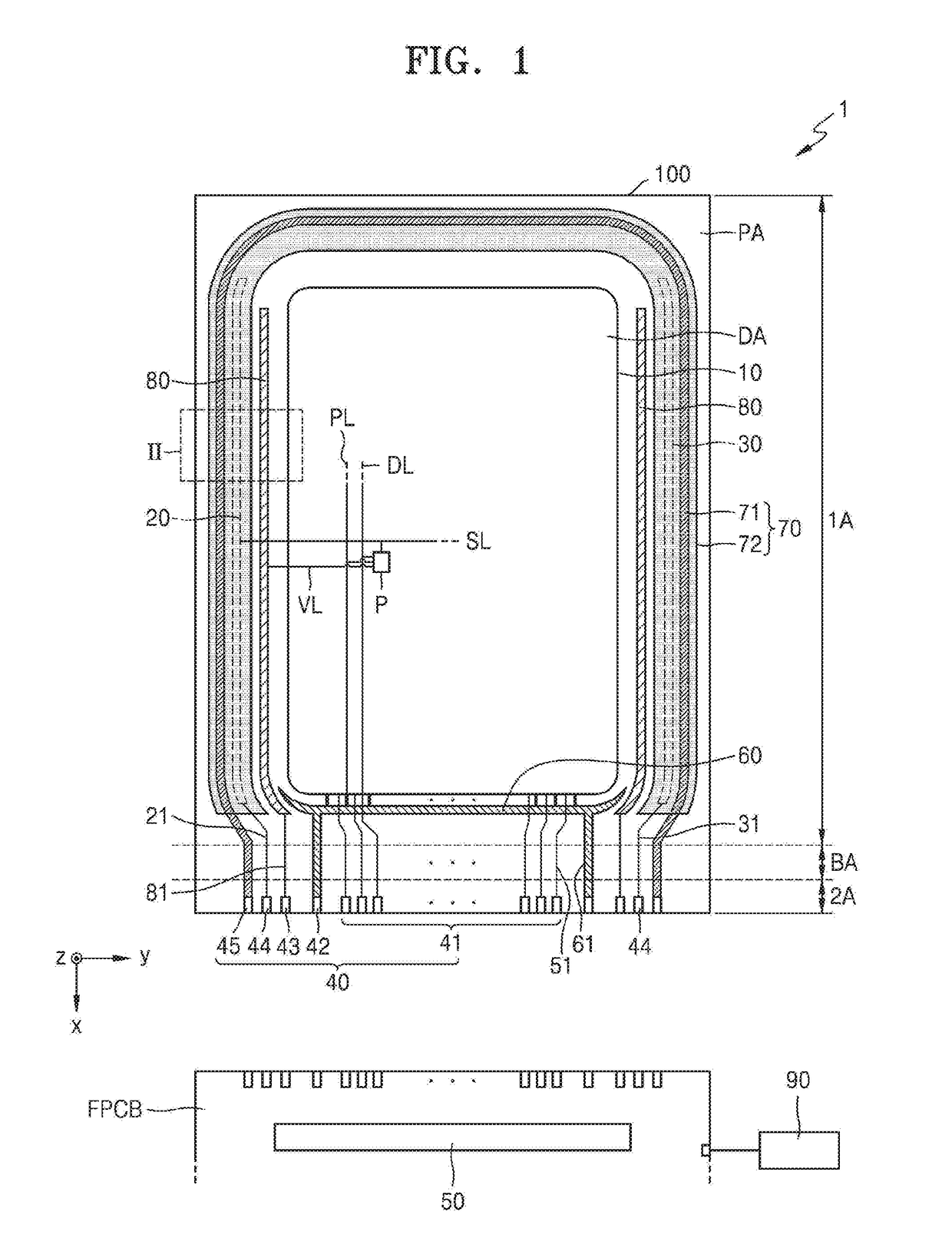

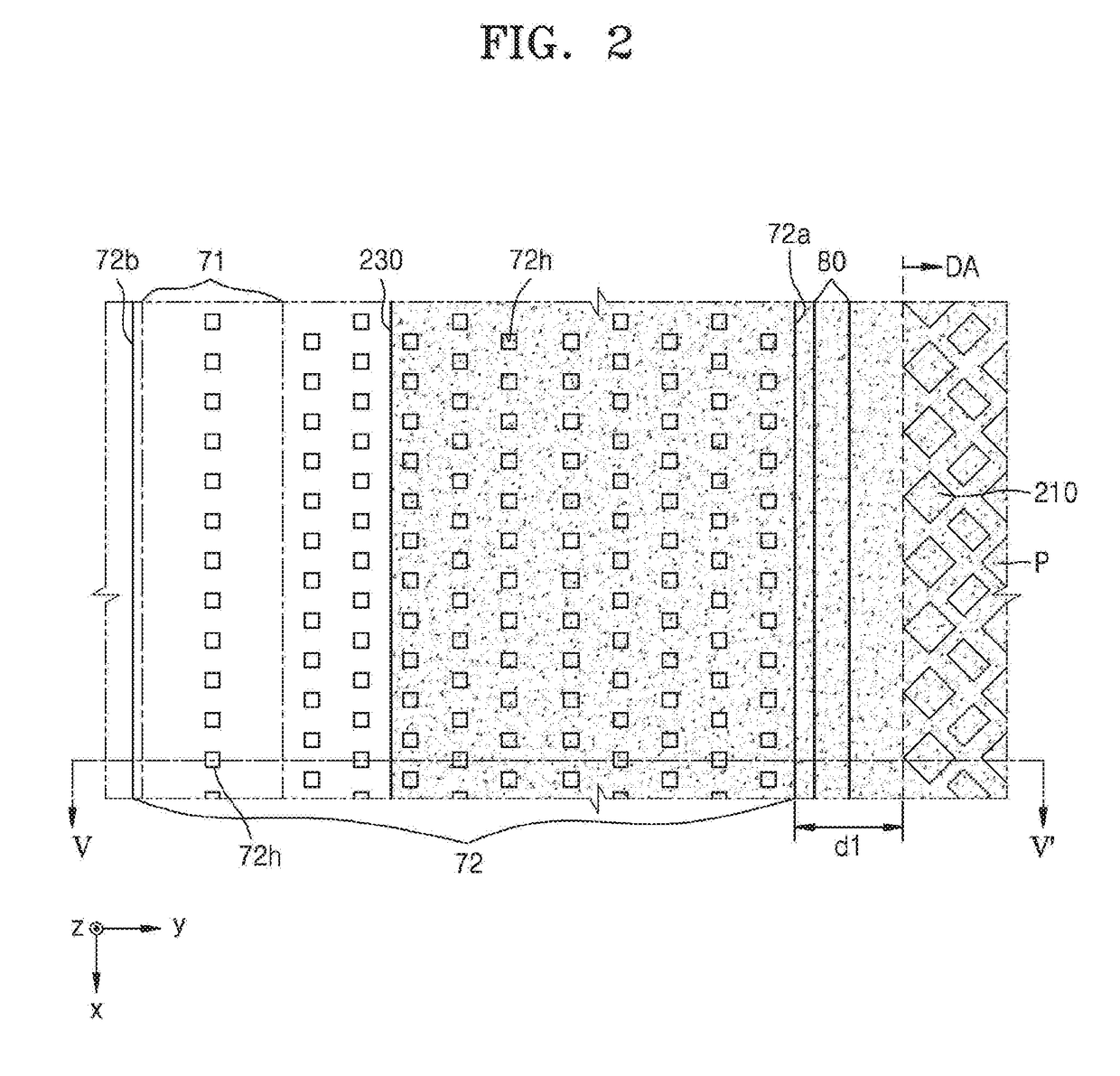

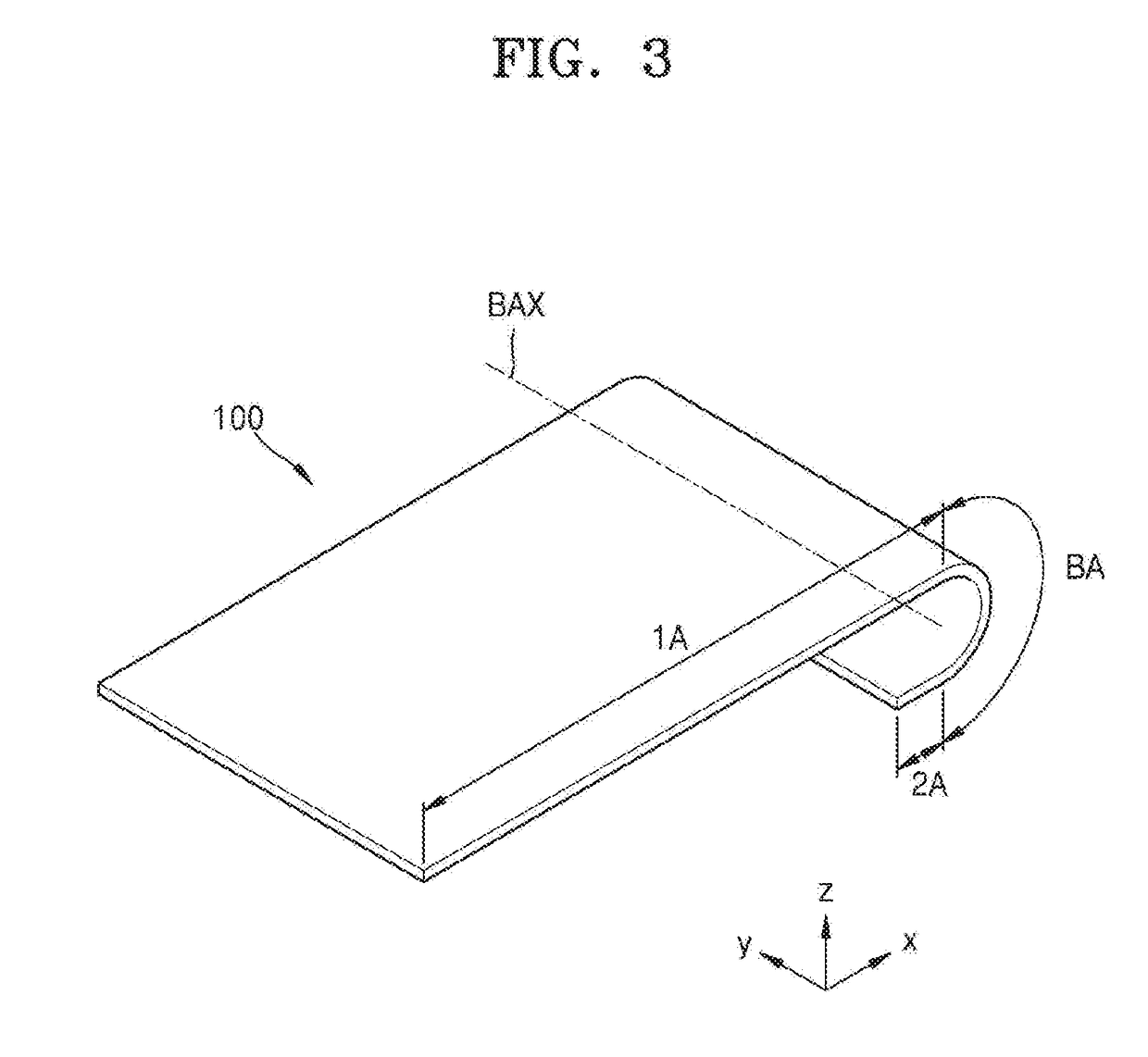

Display device

ActiveUS20190006442A1Quality improvementSolid-state devicesSemiconductor/solid-state device manufacturingInter layerDisplay device

Owner:SAMSUNG DISPLAY CO LTD

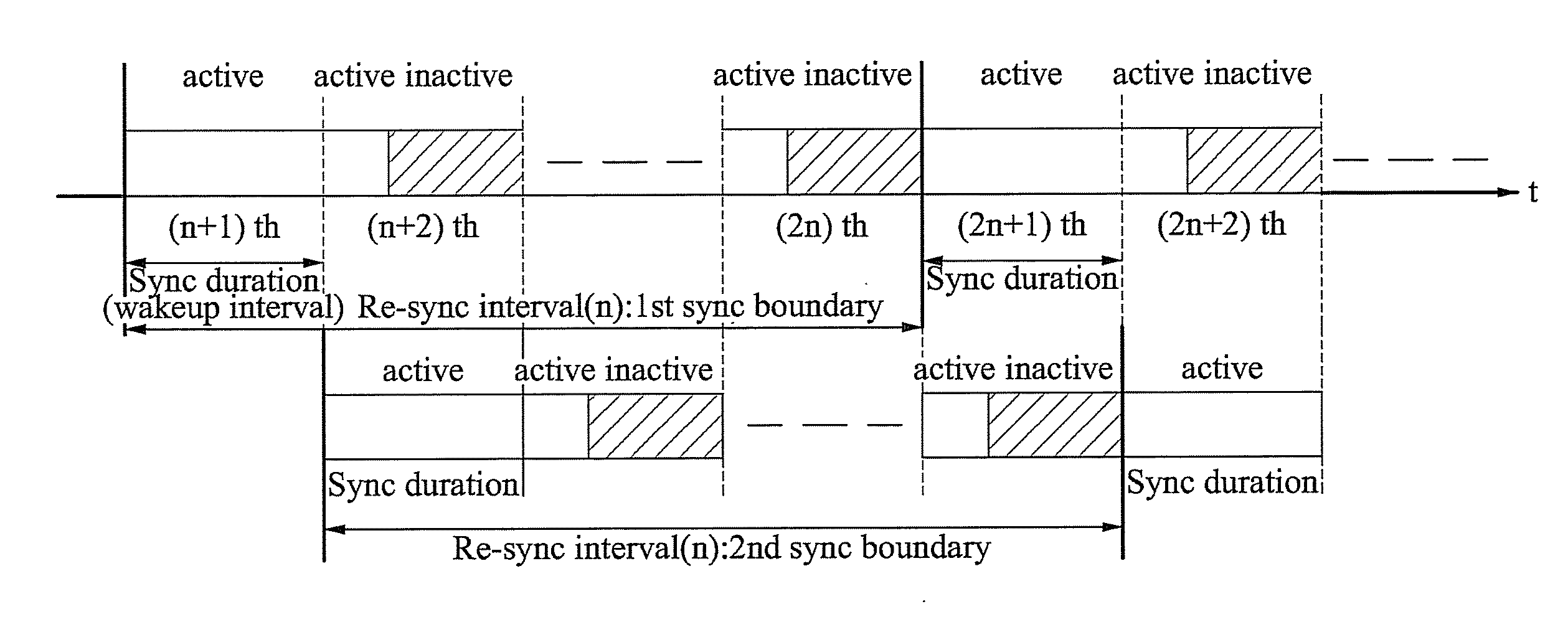

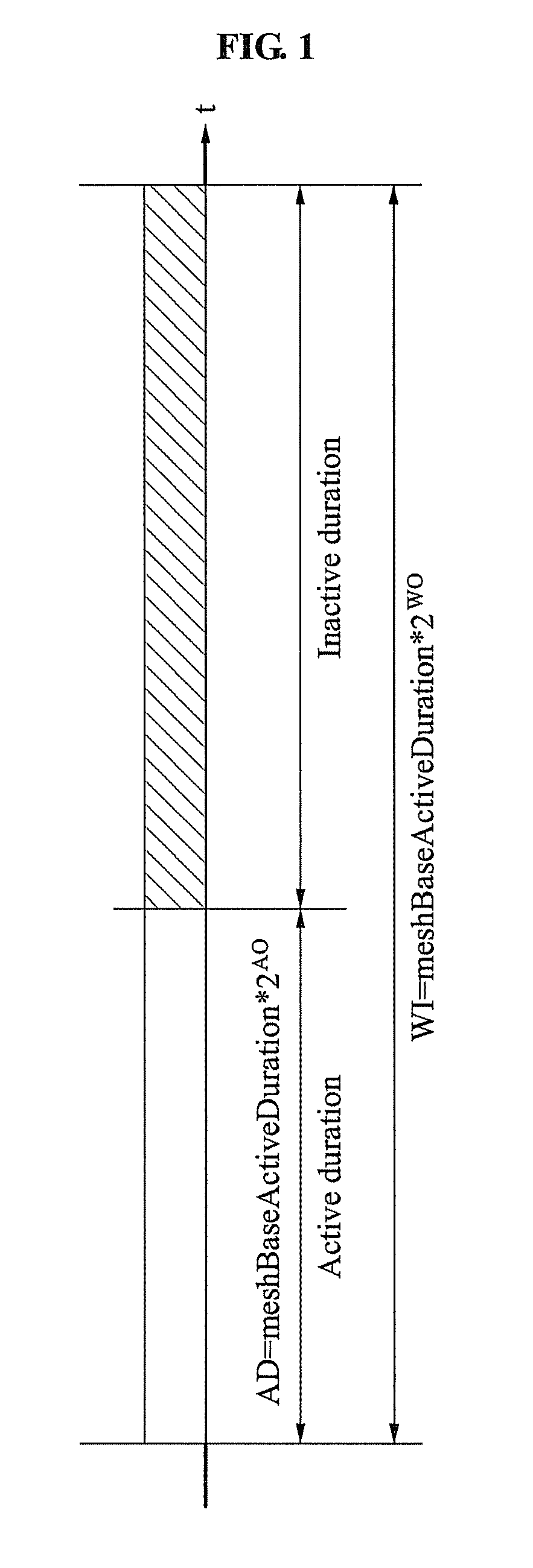

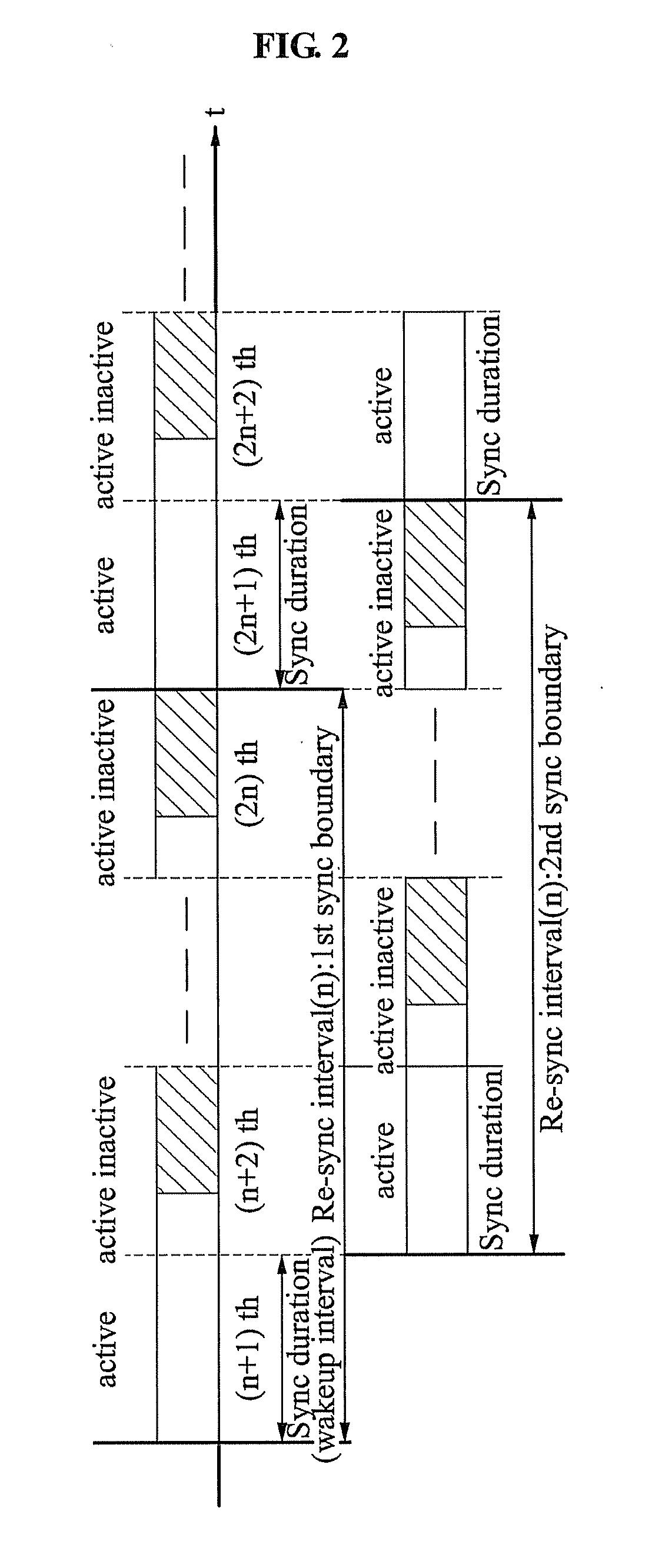

Time synchronization and routing method in wireless sensor network, and apparatus for enabling the method

ActiveUS20110002251A1Reduce end-to-end latency and power consumption of each nodeReduce the probability of collisionEnergy efficient ICTPower managementData synchronizationTimestamp

A time synchronization method in a wireless sensor network, a low power routing method using a reservation scheme, and an apparatus for performing the method are provided. The time synchronization method in the wireless sensor network may include: receiving a first synchronization request command packet from a parent node that manages time synchronization for a predetermined synchronization region; receiving, from the parent node, a second synchronization request command packet that has a transmission timestamp value of the first synchronization request command packet; and performing time synchronization for a child node based on a reception time of the first synchronization request command packet, a reception time of the second synchronization request command packet, and the transmission timestamp value of the first synchronization request command packet.

Owner:ELECTRONICS & TELECOMM RES INST

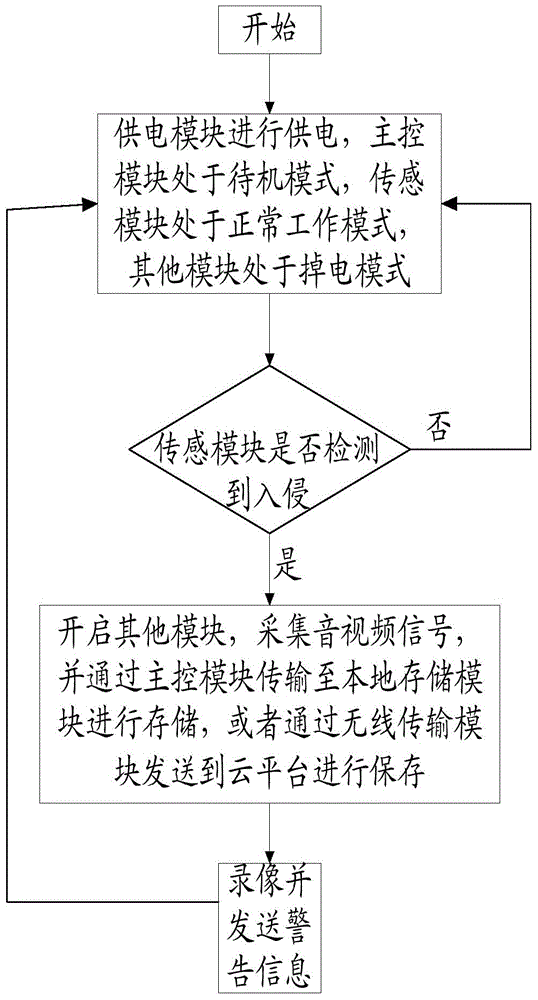

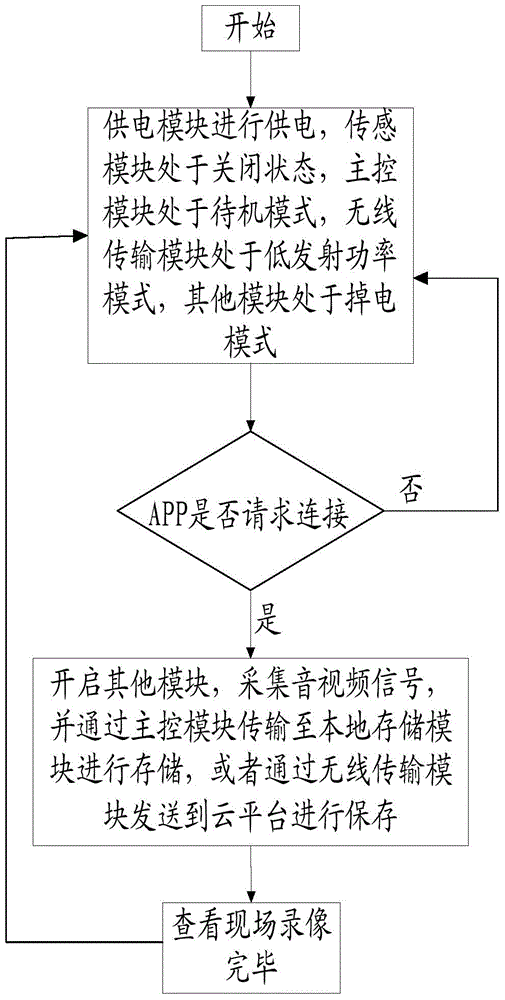

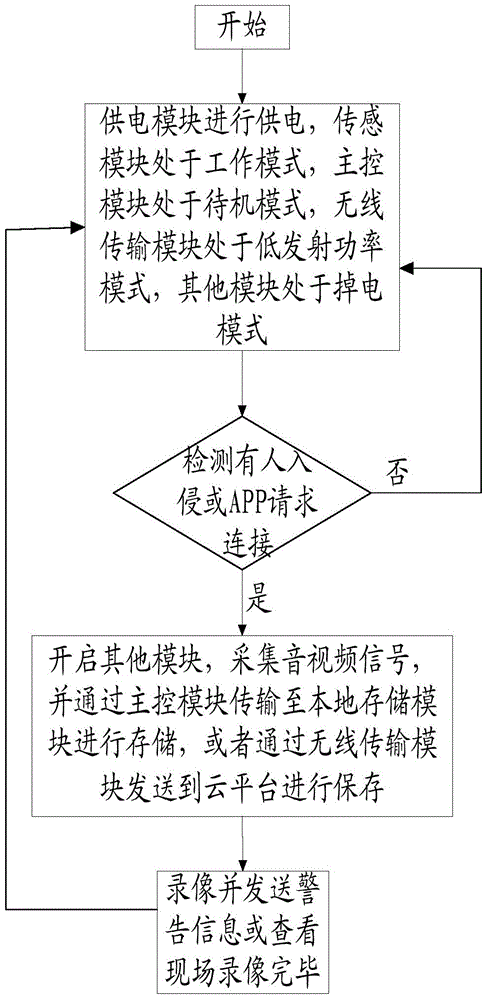

Control method for low power consumption of network camera supplied by battery

InactiveCN104883483ATroubleshoot Wiring ProblemsReduce power consumptionTelevision system detailsColor television detailsProcess optimizationWireless transmission

The invention provides a control method for low power consumption of a network camera supplied by a battery. The method includes following steps: firstly, a power supply module and a master control module are in a standby mode, a sensing module is in a normal work mode, and other modules are in a power-down mode; secondly, when the sensing module detects the invasion of someone, the master control module switches the standby mode to a work mode, and the other modules are turned on; thirdly, video signals are acquired by a video acquisition module, and audio signals are simultaneously acquired by an audio acquisition module; fourthly, the audio and video signals are transmitted to a local storage module via the master control module, or the audio and video signals are sent to a cloud platform via a wireless transmission module; and fifthly, recording is realized via a cloud server and warning information is forwarded to an APP of a user mobile terminal. According to the control method, the problem of power supply wiring of the household network camera is solved, the average power consumption of the equipment is reduced via the reduction of the power consumption in a non-usage period of the camera, and the service lifetime of the battery is extended via process optimization.

Owner:FUJIAN STAR NET COMM

Unit cell of semiconductor integrated circuit and wiring method and wiring program using unit cell

InactiveUS20070228419A1Improve wiring efficiencySolid-state devicesSpecial data processing applicationsSemiconductorIntegrated circuit

A unit cell of a semiconductor integrated circuit capable of improving wiring efficiency in layout of a functional circuit block or the like using a unit cell, and a wiring method and wiring program using the unit cell are provided. In a unit cell, auxiliary power wiring regions are formed with reference to grids that exist from a cell edge every basic cell width in the X-direction. Input signal terminals and an output signal terminal are each arranged so as to include at least one wiring connecting portion outside the auxiliary power wiring regions. This makes it possible to wire wiring other than signal wiring in the auxiliary power wiring region. When a functional circuit block is constructed by arranging unit cells in a matrix, auxiliary power wiring regions are formed at a pitch of the basic cell width, through the functional circuit block in the Y-direction.

Owner:SOCIONEXT INC

Power routing in standard cell designs

ActiveUS8513978B2Small sizePrecise alignmentSolid-state devicesComputer aided designEngineeringCell based

A cell-based architecture for an integrated circuit. A row of cell instances borders a first adjacent row of cell instances along a first boundary and a second adjacent row of cell instances along a second boundary. A first power rail (e.g., carrying an auxiliary voltage) extends along the first boundary. A second power rail (e.g., VSS) extends along the second boundary. The second power rail is wider than the first power rail. Additionally, a third power rail (e.g., VDD) extends across the interior of the second row of cells.

Owner:SYNOPSYS INC

Integrated circuit device and electronic instrument

InactiveUS20070013074A1Static indicating devicesSemiconductor/solid-state device detailsMetal interconnectElectronic instrument

An integrated circuit device having a display memory, wherein a plurality of first power supply interconnects for supplying a first power supply voltage to a plurality of memory cells are provided in a metal interconnect layer in which a plurality of bitlines are formed; wherein a second power supply interconnect for supplying a second power supply voltage to the memory cells is provided in a metal interconnect layer in which a plurality of wordlines are formed, the second power supply voltage being higher than the first power supply voltage; wherein a plurality of bitline protection interconnects are formed in a layer above the bitlines, each of the bitline protection interconnects at least partially covering one of the bitlines in a plan view; and wherein a third power supply interconnect for supplying a third power supply voltage to circuits of the integrated circuit device other than the display memory is provided in a layer above the bitline protection interconnects, the third power supply voltage being higher than the second power supply voltage.

Owner:138 EAST LCD ADVANCEMENTS LTD

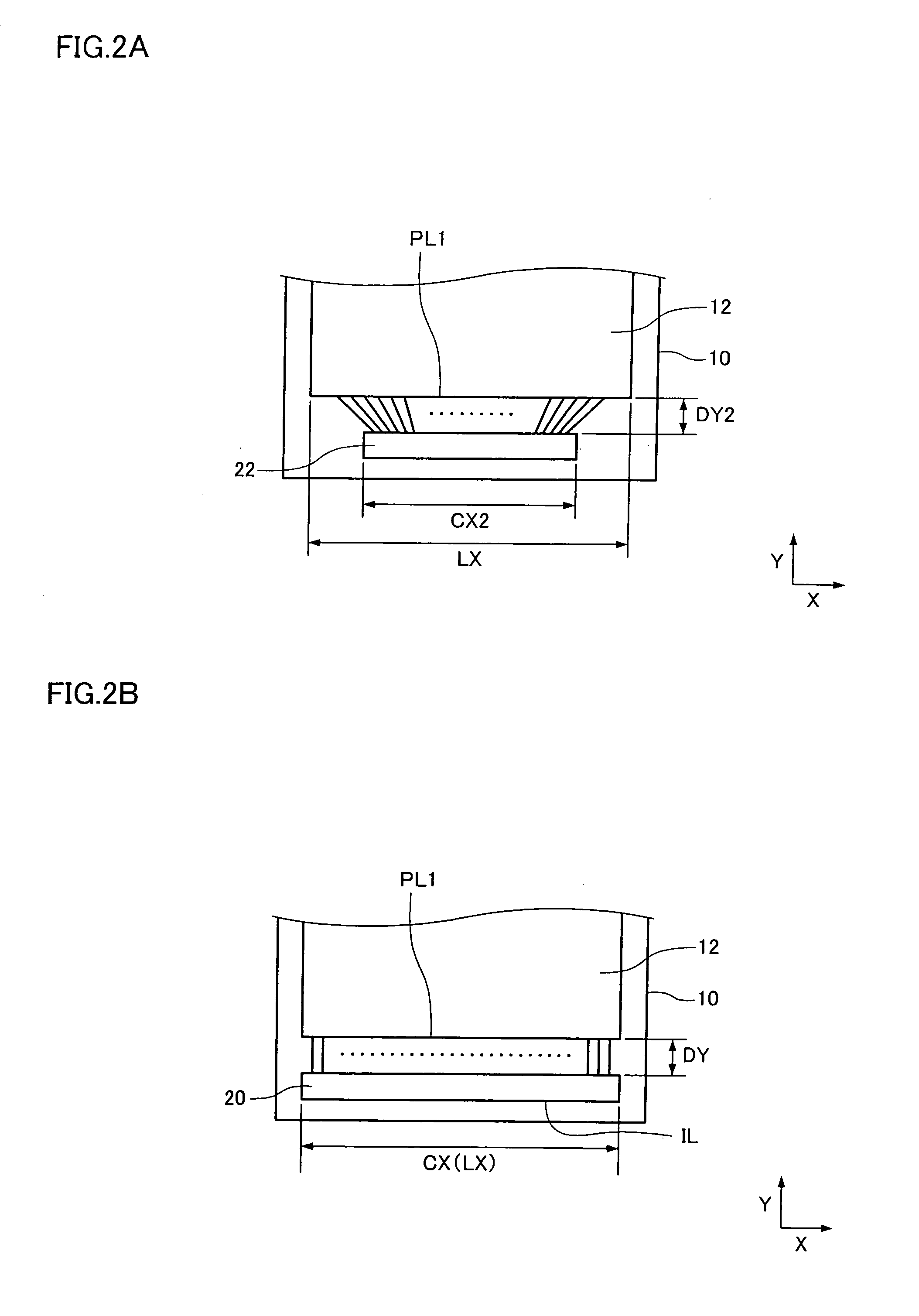

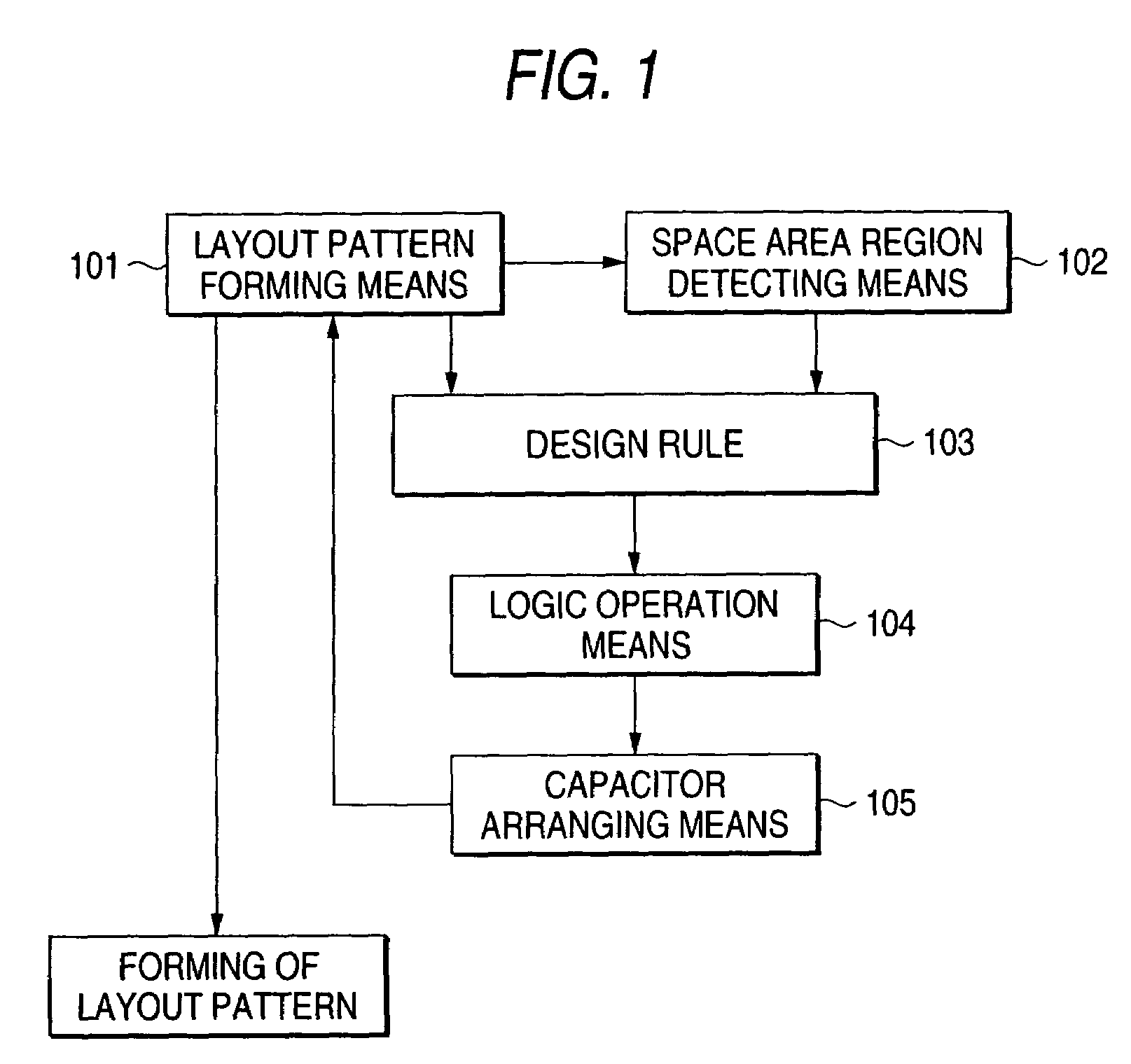

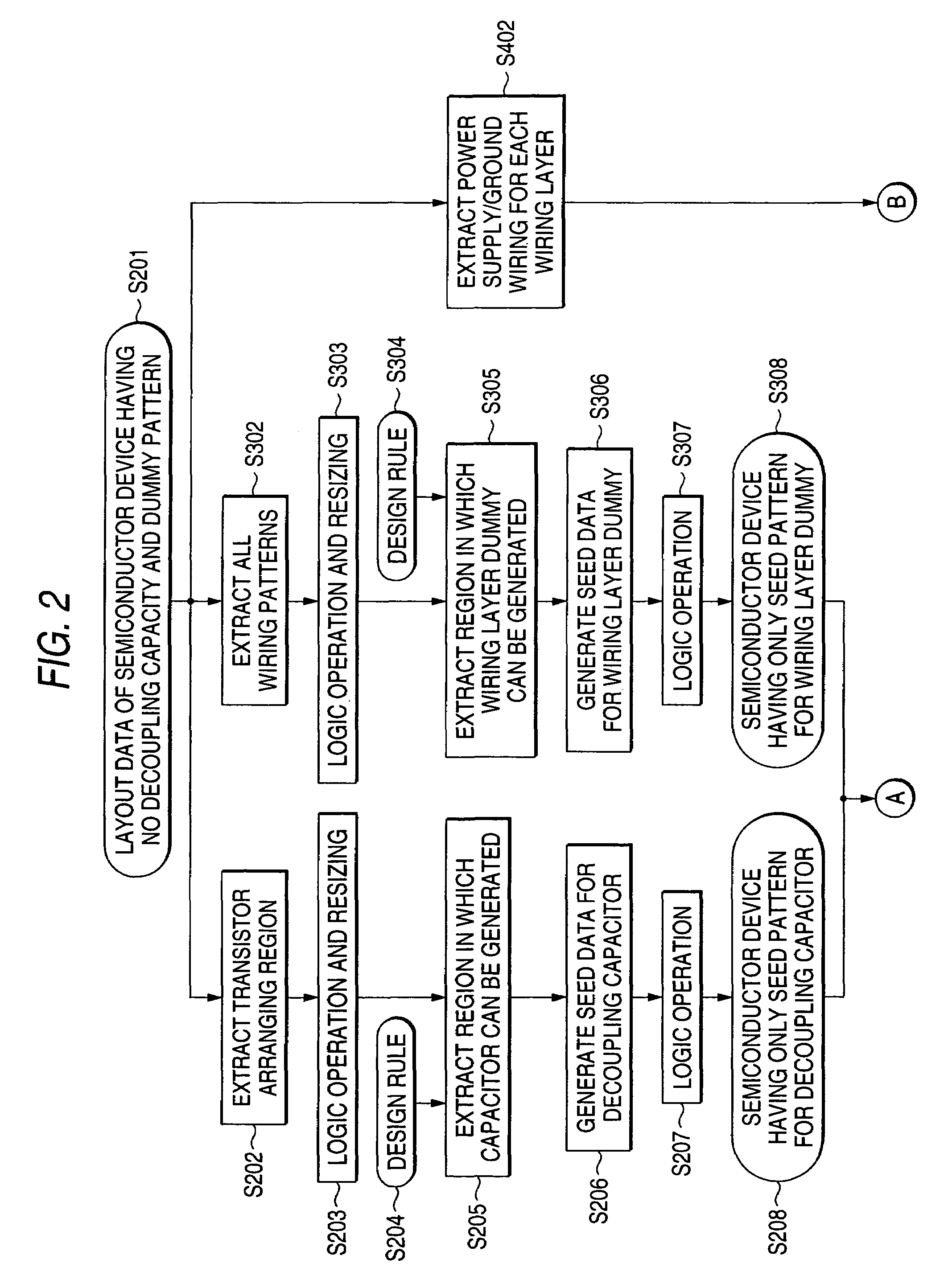

Semiconductor device, method of generating pattern for semiconductor device, method of manufacturing semiconductor device and device for generating pattern used for semiconductor device

InactiveUS7062732B2Stable operation of circuitEfficient supplySemiconductor/solid-state device detailsSolid-state devicesDiffusion layerDecoupling capacitor

To provide a semiconductor device characterized in that: a decoupling capacitor can be increased; noise generated from an electric power supply can be effectively absorbed; and a stable operation of a circuit can be realized.Irrespective of whether or not a region is close to a power supply wiring or a ground wiring, MOS is spread all over a spare area of a chip and connected to a power supply wiring and ground wiring by utilizing a wiring layer and diffusion layer.

Owner:SOCIONEXT INC

Power-supply wiring structure for multilayer wiring and method of manufacturing multilayer wiring

InactiveUS20100237508A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringPower routing

Owner:KK TOSHIBA

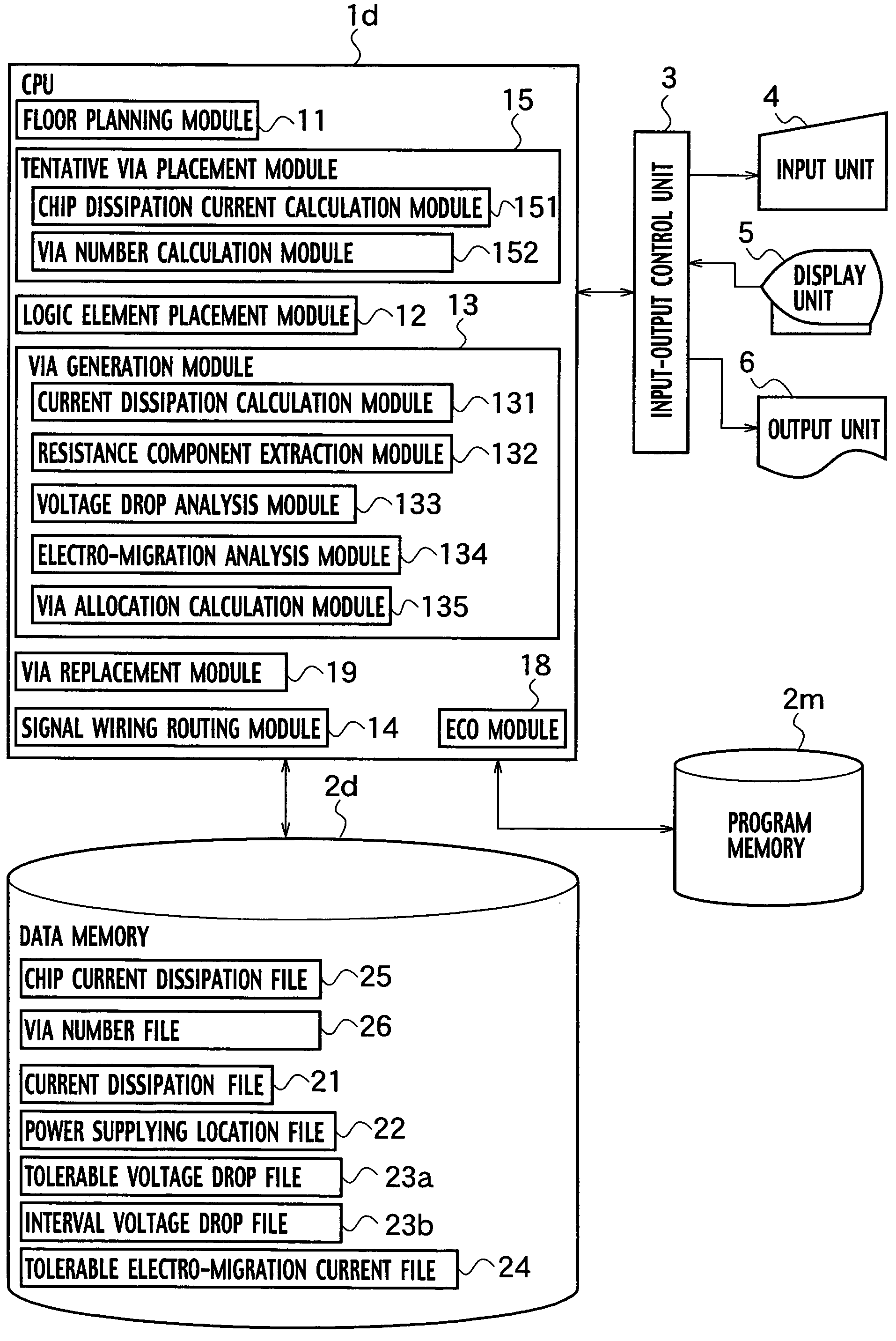

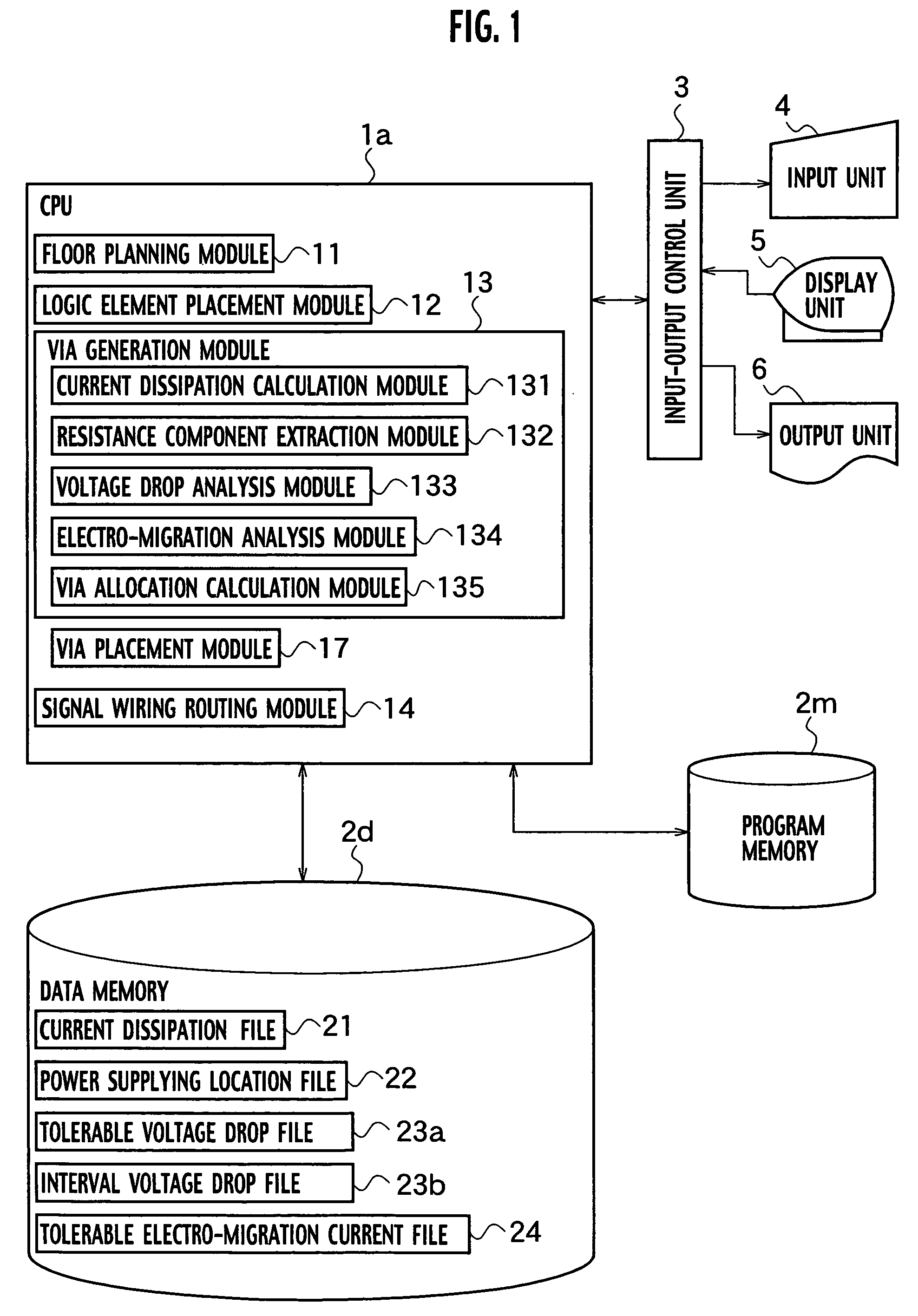

Semiconductor integrated circuit having multi-level interconnection, CAD method and CAD tool for designing the semiconductor integrated circuit

InactiveUS20050160391A1Small voltage dropSemiconductor/solid-state device detailsSolid-state devicesComputer Aided DesignVoltage drop

A computer-aided design method of an integrated circuit includes: calculating current dissipation consumed by logic elements, in a ladder network embracing a plurality of current paths connected between subject first- and second-potential-level power supply wiring; analyzing a tolerable electro-migration current of the subject first-potential-level power supply wiring; analyzing an interval voltage drop between a control point and a specific position on the subject first-potential-level power supply wiring; and comparing a summation of through-currents flowing the logic elements from the control point to the specific point, with the tolerable electro-migration current, and comparing the interval voltage drop with a tolerable voltage drop to determine an optimum location of a via configured to supply power from the subject first-potential-level power supply wiring to the logic elements.

Owner:KK TOSHIBA