Image display system comprising low temperature poly silicon thin film transistor and its manufacture method

An image display system and thin-film transistor technology, which is applied in transistors, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve problems such as oxide layer charge diffusion, N-type thin-film transistor components cannot be turned off normally, and critical voltage shift

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

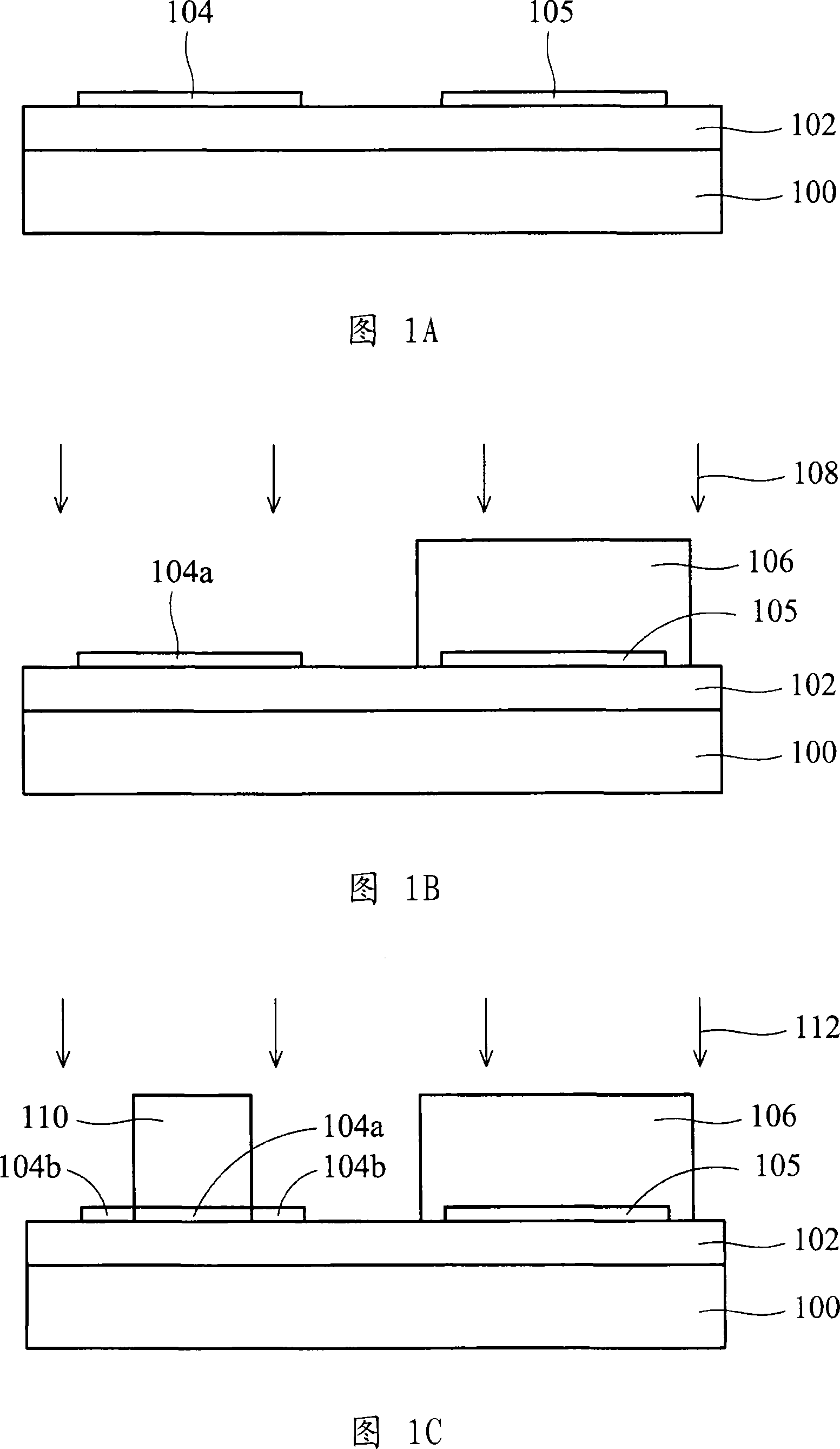

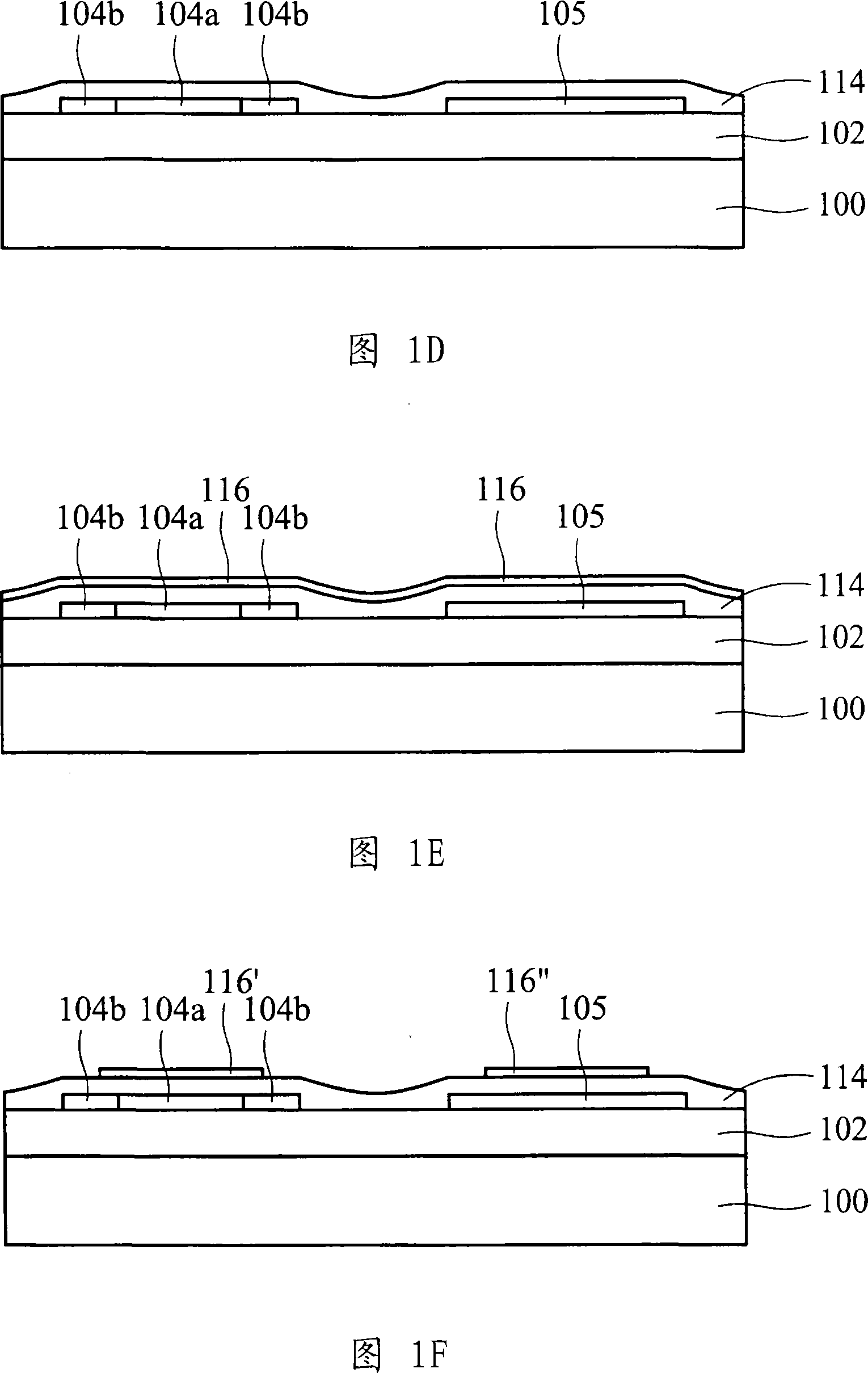

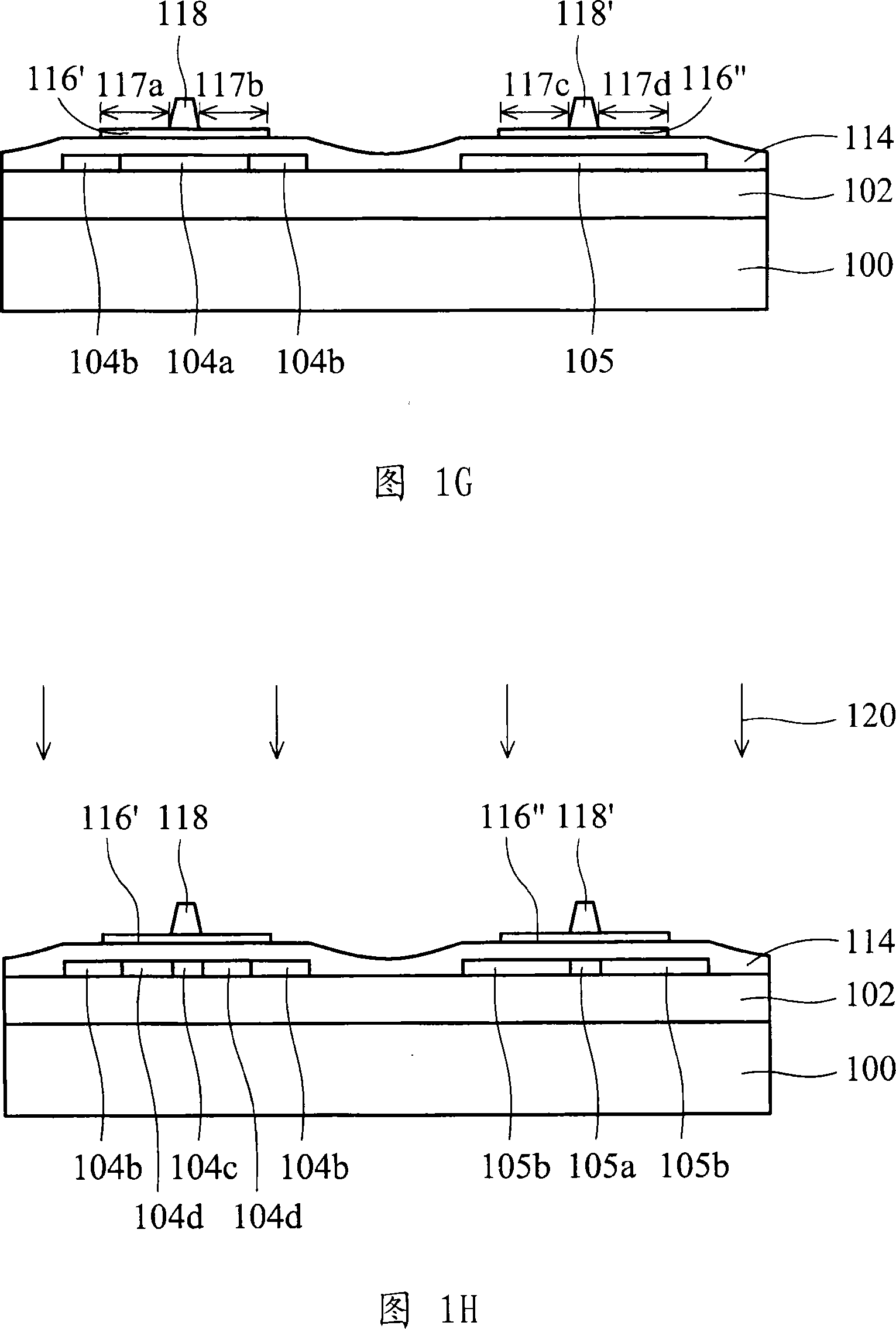

[0018] As shown in FIG. 1L , in the low temperature polysilicon thin film transistor liquid crystal display of the first embodiment, a buffer layer 102 is located on the substrate 100 . An active layer is located on the buffer layer 102, and at least includes a first active layer or a second active layer or both; the first active layer includes a channel region 104c, a lightly doped source / drain 104d, a source / drain electrode 104b; the second active layer includes a channel region 105a and a source / drain electrode 105c. The gate insulating layer 114 is located on the active layer and the buffer layer 102 . A dielectric layer is located on the gate insulating layer 114, and at least includes a first dielectric layer 116' or a second dielectric layer 116" or both. A first gate electrode 118 and a second gate The electrodes 118' are located on the first dielectric layer 116' or the second dielectric layer 116", respectively. The interlayer dielectric layer 126 is located on th...

no. 2 example

[0031] As shown in FIG. 2F , in the low temperature polysilicon thin film transistor liquid crystal display of the first embodiment, a buffer layer 202 is located on the substrate 200 . An active layer is located on the buffer layer 202, and at least includes a first active layer or a second active layer or both; the first active layer includes a channel region, lightly doped source / drain 204d, source / drain The drain electrode 204a; the second active layer includes a channel region 205b and a source / drain electrode 205c. The gate insulating layer 214 is located on the patterned active layer and the buffer layer 202 . A patterned dielectric layer is located on the gate insulating layer 214, and at least includes a first dielectric layer 216' or a second dielectric layer 216" or both. A first gate electrode 218 and a second The gate electrode 218' is located on the first dielectric layer 216' or the second dielectric layer 216", respectively. A first patterned protective layer...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More