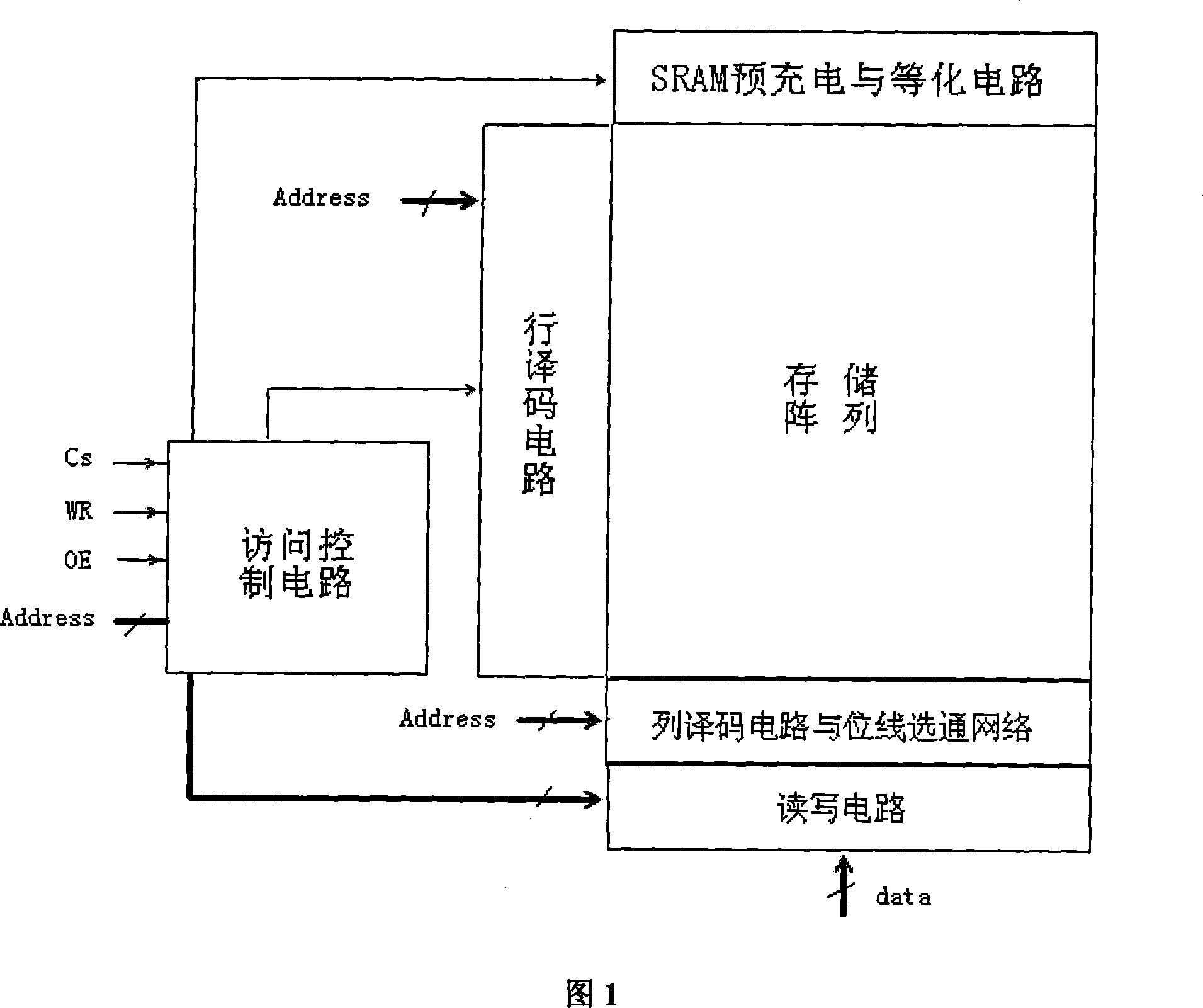

Self-timing SRAM access control circuit

A control circuit and access control technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problems of long design cycle, heavy load, redesign of access control circuit, etc., and achieve the effect of low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

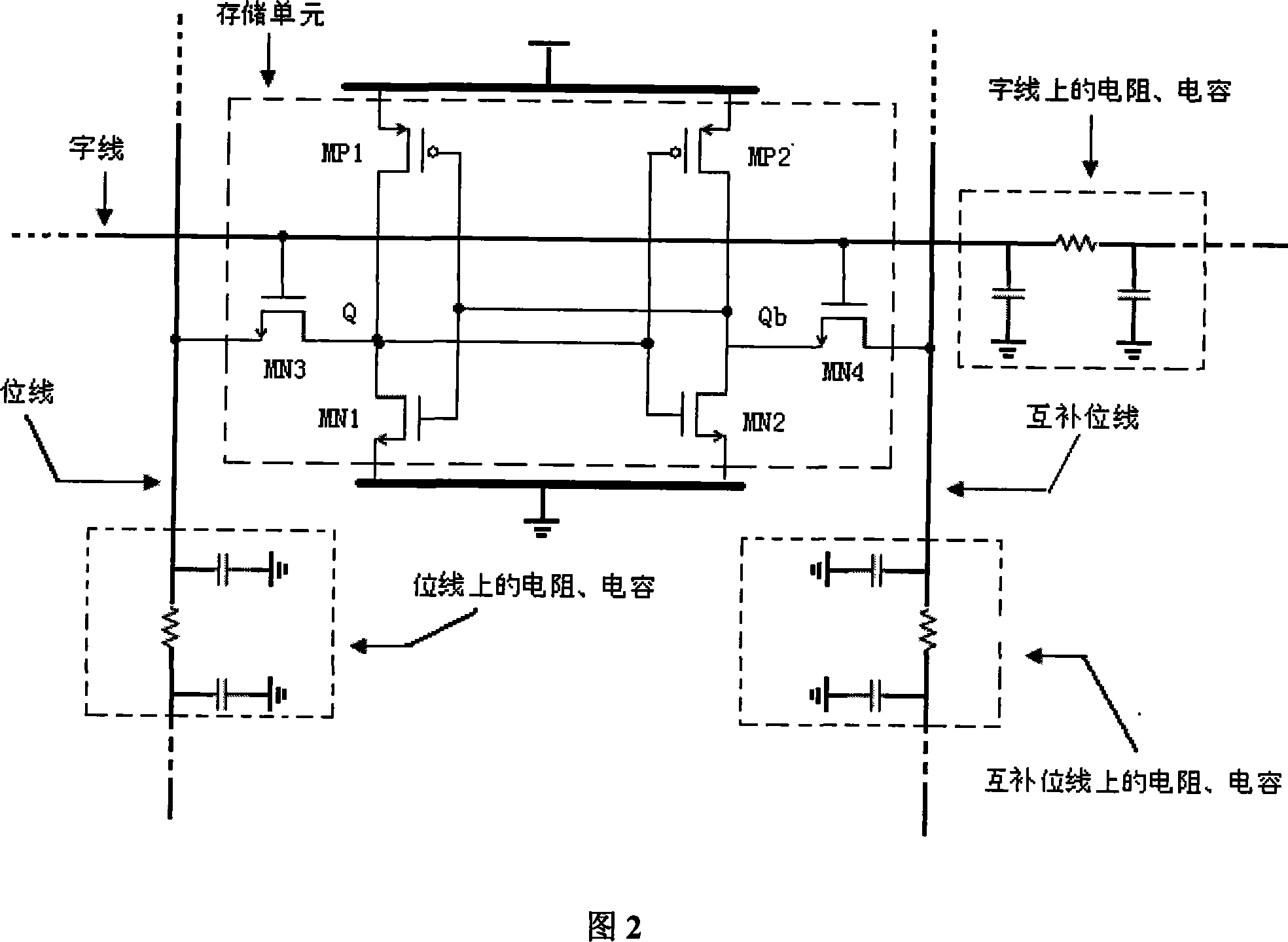

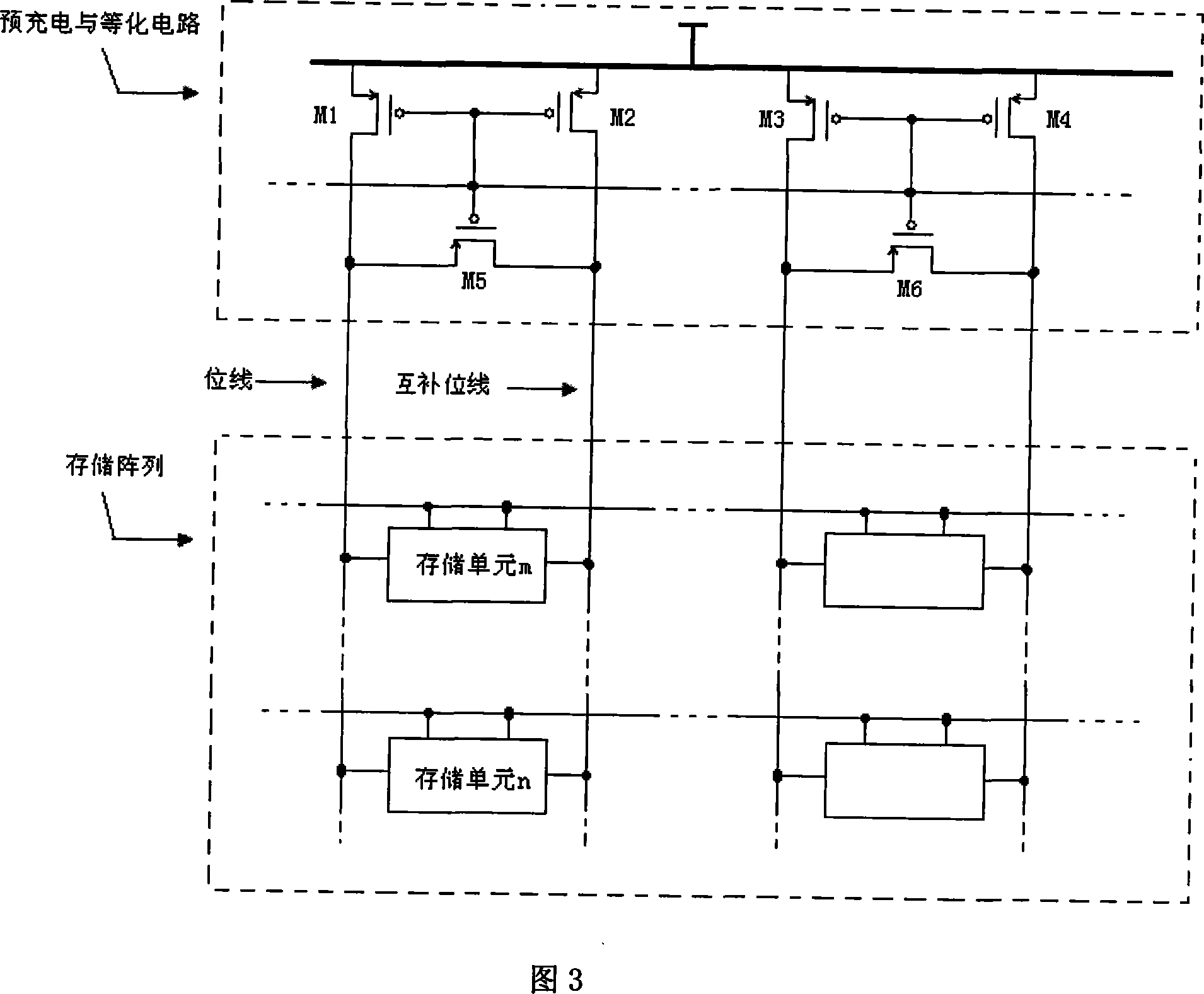

Method used

Image

Examples

Embodiment Construction

[0049] Specific implementation examples

[0050] 7, the self-timed SRAM access control circuit of the present invention consists of a first reference bit line 100, a second reference bit line 200, an address conversion monitoring circuit 300, a precharge and equalization control circuit 400 and a read-write access control circuit 500 Composition, wherein, the first reference bit line 100 is connected to the precharge and equalization control circuit 400, the second reference bit line 200 is connected to the read and write access control circuit 500, and the word line signal of the SRAM circuit, and the address conversion monitoring circuit 300 is connected to the SRAM The address signal line [Addr_0:Addr_n] of the circuit, the chip select signal line CS, the read and write control signal line WR are connected to the precharge and equalization control circuit 400, and the precharge and equalization control circuit 400 is connected to the first reference bit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com