LDMOS transistor

A transistor and seed crystal technology, applied in the field of LDMOS transistors, can solve problems such as reducing the life of LDMOS transistors, and achieve the effect of weakening Idq degradation and improving linear efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

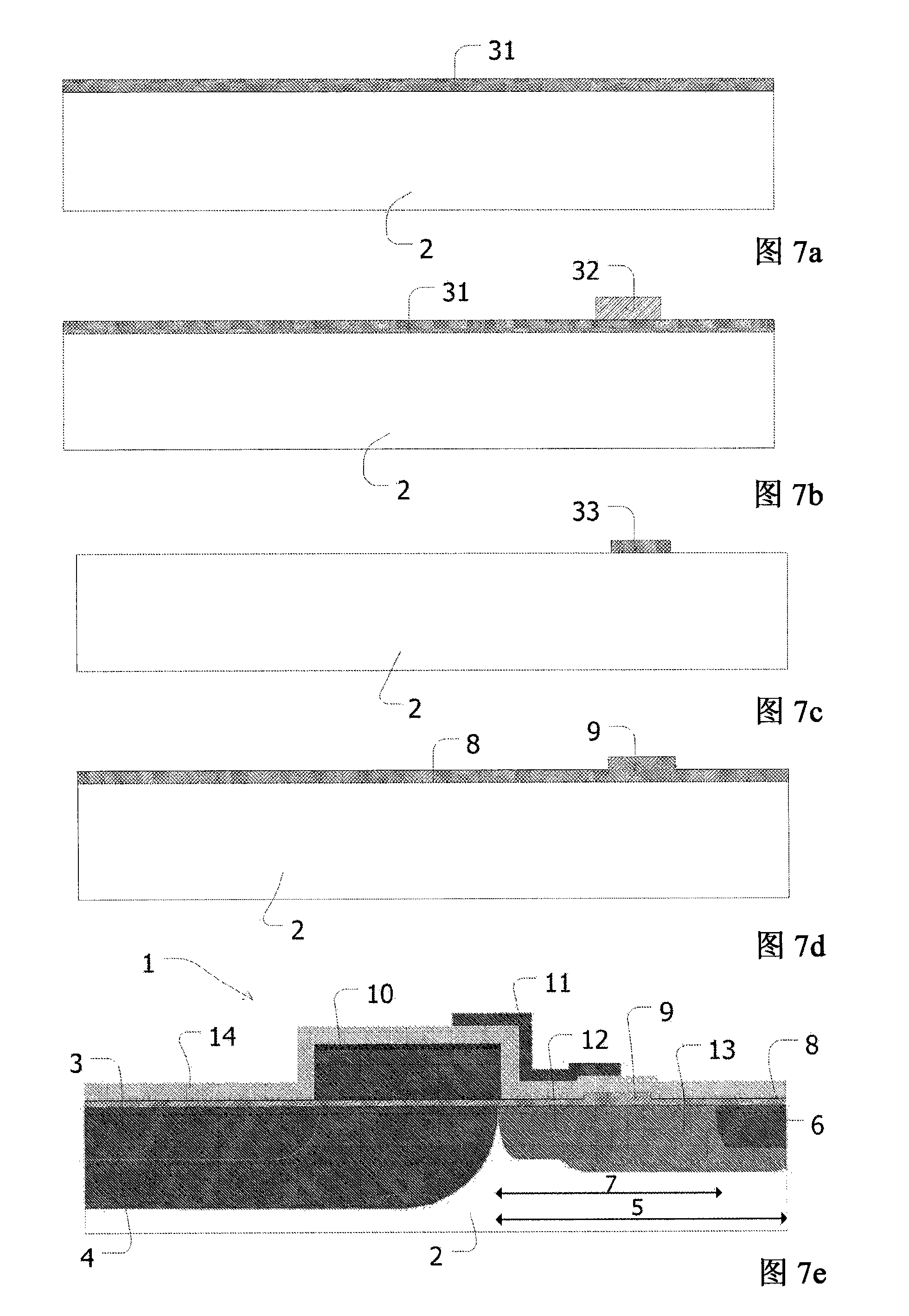

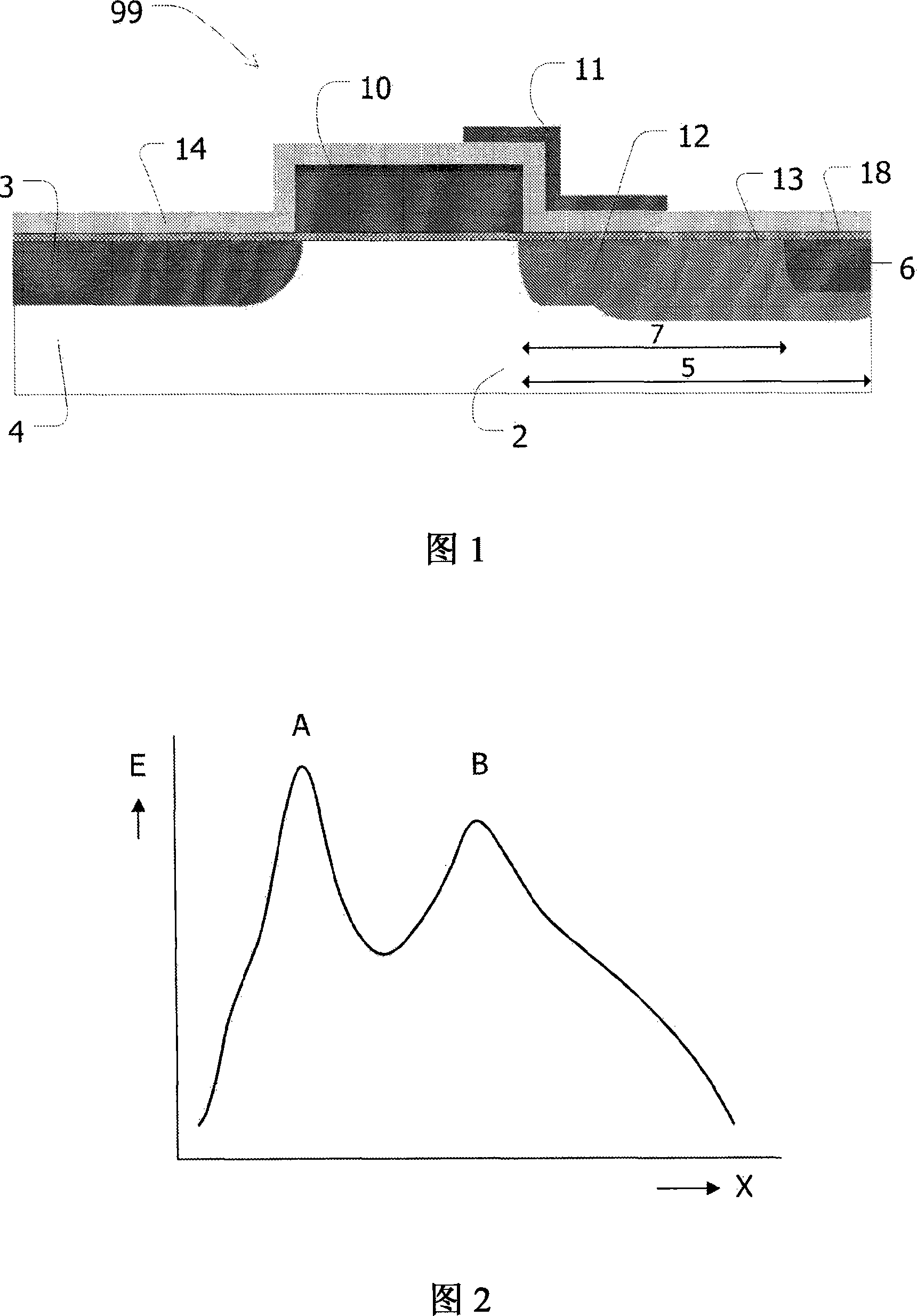

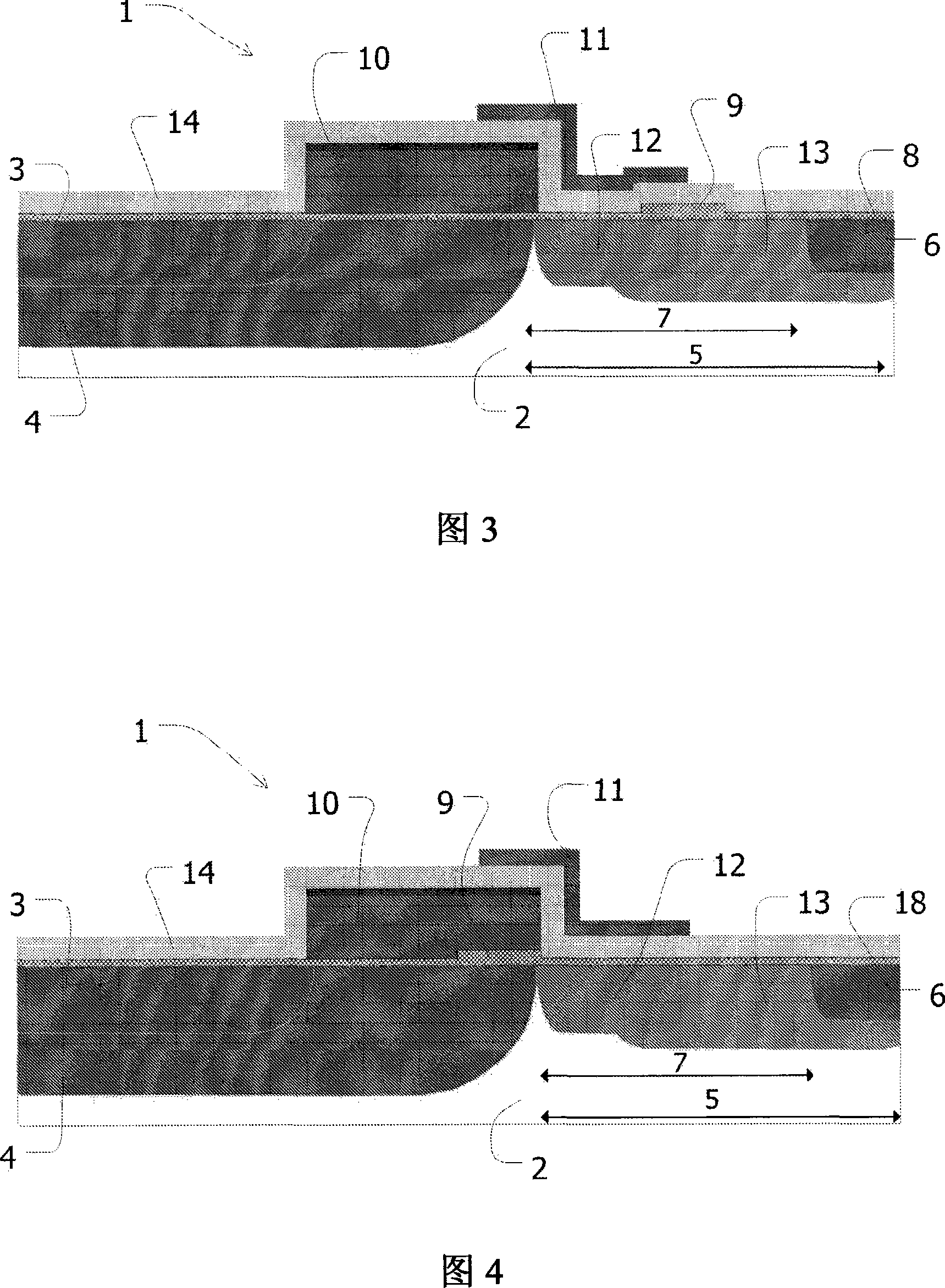

[0022] The figures are not drawn to scale. In general, like components are designated with like reference numerals in these figures.

[0023] FIG. 1 shows a cross-sectional view of a conventional LDMOS transistor 99 according to the prior art. The LDMOS transistor 99 comprises a substrate 2 of semiconductor material, here p-type silicon. The LDMOS transistor 99 further comprises a silicided polysilicon gate electrode 10 extending through the p-type channel region 4 , and the n-type source region 3 and n-type drain region 5 , which are connected to each other through the p-type channel region 4 . Channel region 4 , source region 3 and drain region 5 are fabricated within substrate 2 . In this example, channel 4 is a laterally diffused p-type region. The gate electrode 10 and the substrate 2 are separated by a gate oxide layer 18, wherein the gate oxide layer 18 comprises thermally grown silicon dioxide, for example.

[0024] The drain region 5 includes an n-type drain epita...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More