Semiconductor integrated circuit

An integrated circuit and semiconductor technology, applied in the field of semiconductor integrated circuits, can solve the problems of reduced threshold voltage of MOS transistors and increased sub-threshold leakage current, etc., and achieves the effects of high manufacturing yield, reduced operating power consumption and changes in signal delay amount.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] "Representative Implementation Mode"

[0042] First, representative embodiments of the technical solutions disclosed in the present application will be briefly described. The reference numerals put in parentheses and referred to in the brief description of the representative embodiments are merely examples of members included in the concept of the constituent elements to which the numerals are attached.

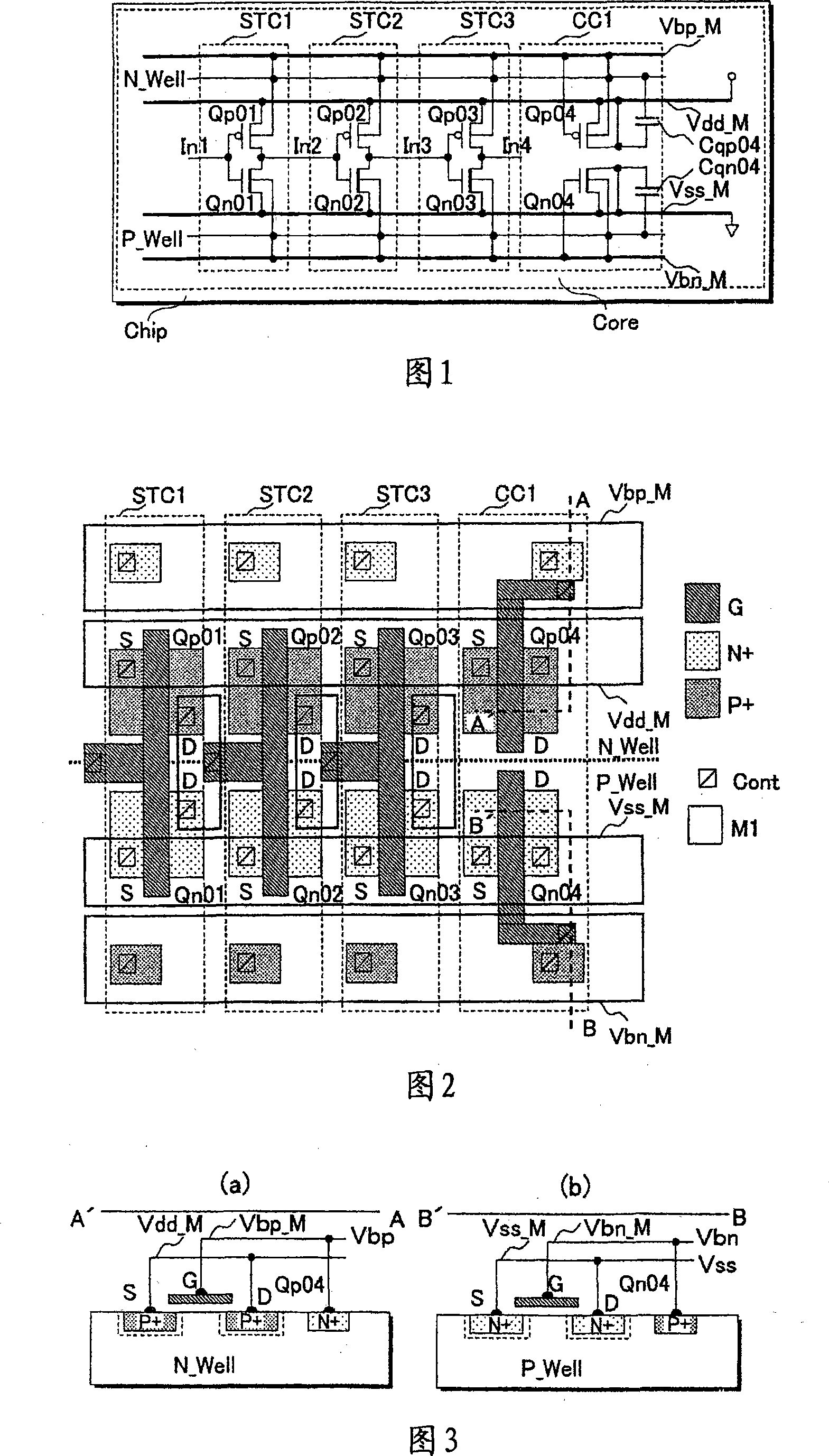

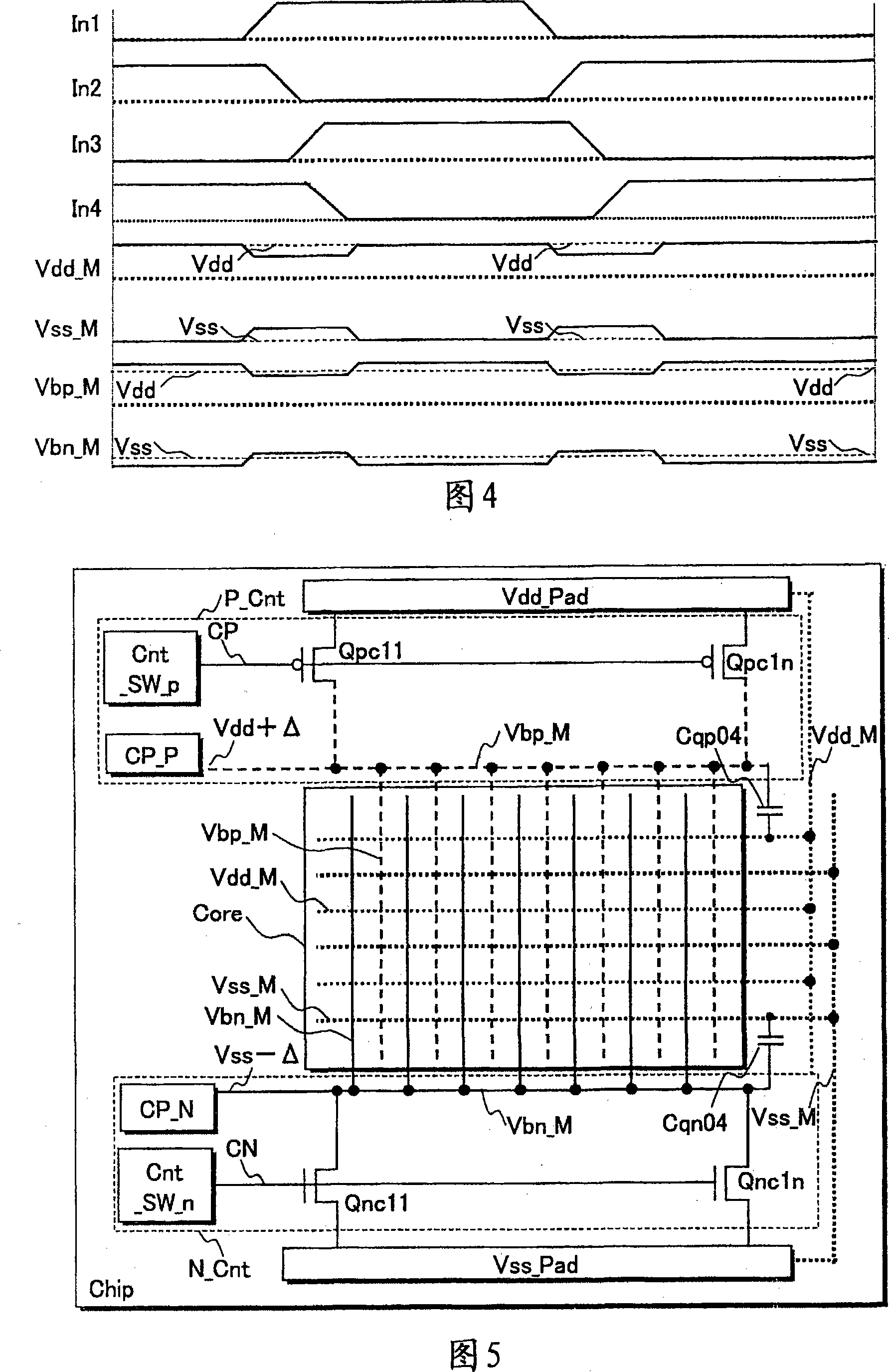

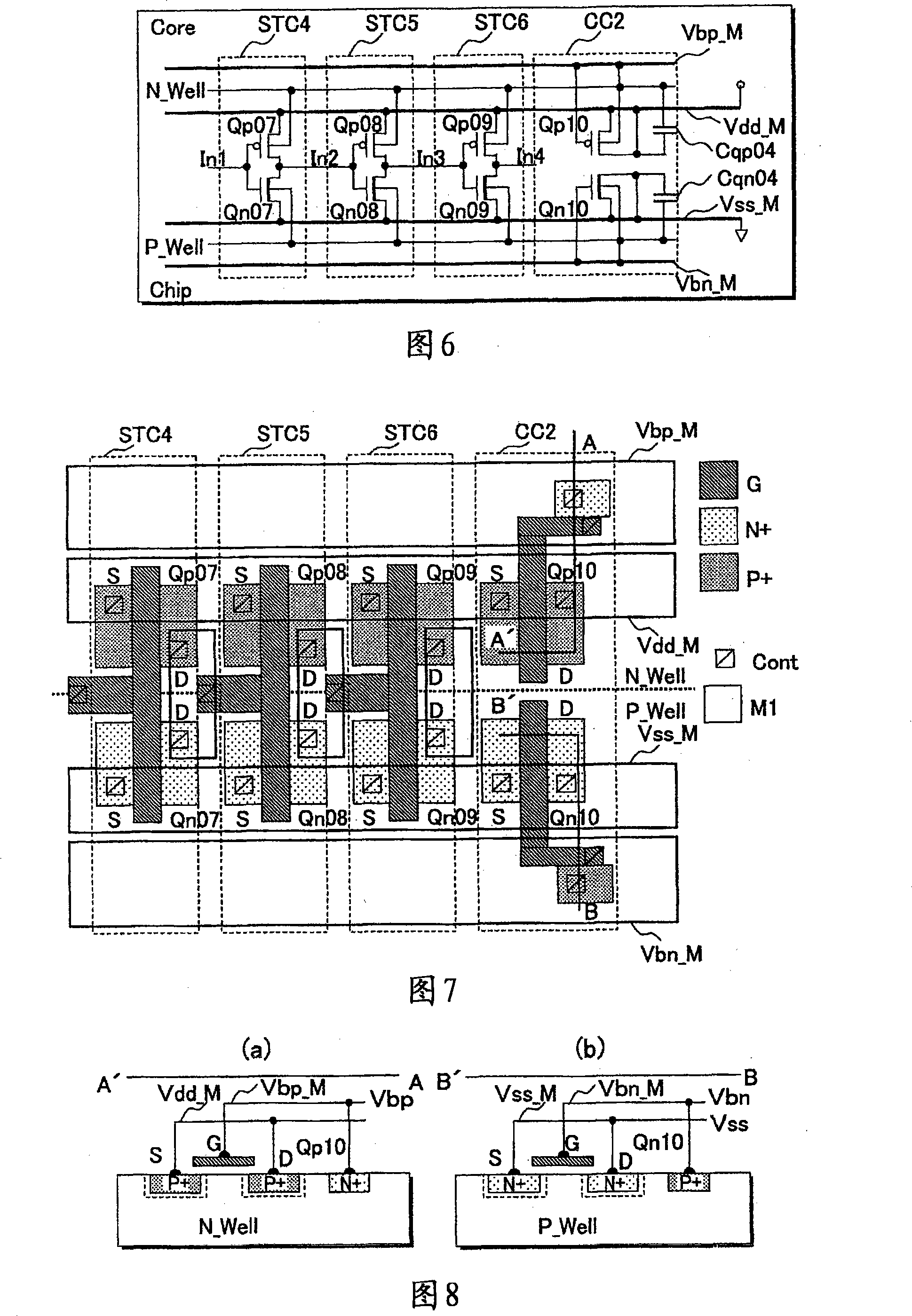

[0043] (1) A semiconductor integrated circuit (Chip) according to a typical embodiment of the present invention includes CMOS circuits (ST1, ST2, ST3) for processing an input signal (In1), and additional chips manufactured by the same manufacturing process as the above-mentioned CMOS circuits. Capacitor circuit (CC1). The above CMOS circuit includes PMOS (Qp01, Qp02, Qp03) with N well (N_Well) and NMOS (Qn01, Qn02, Qn03) with P well (P_Well), and the above additional capacitance circuit includes an additional PMOS (Qp04) with N well and additional NMOS (Qn04) with P-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More