Heterogeneous multi-core system thread-level dynamic dispatching method based on configurable processor

A heterogeneous multi-core, dynamic scheduling technology, applied in the computer field, can solve the problem of low efficiency of static scheduling and allocation, and achieve the effect of reducing complexity and learning time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

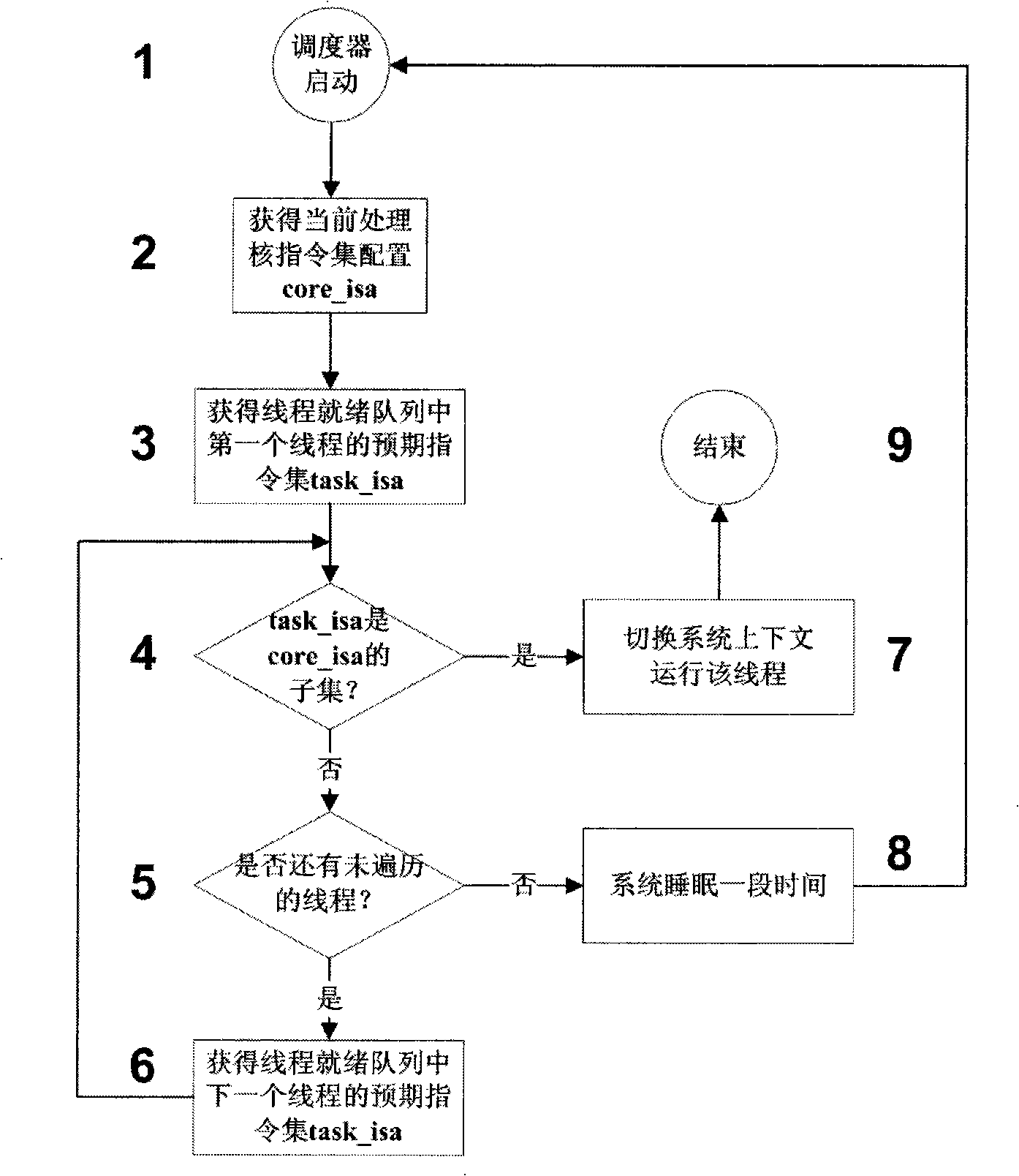

[0029] The embodiments of the present invention are described in detail below in conjunction with the accompanying drawings: this embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following the described embodiment.

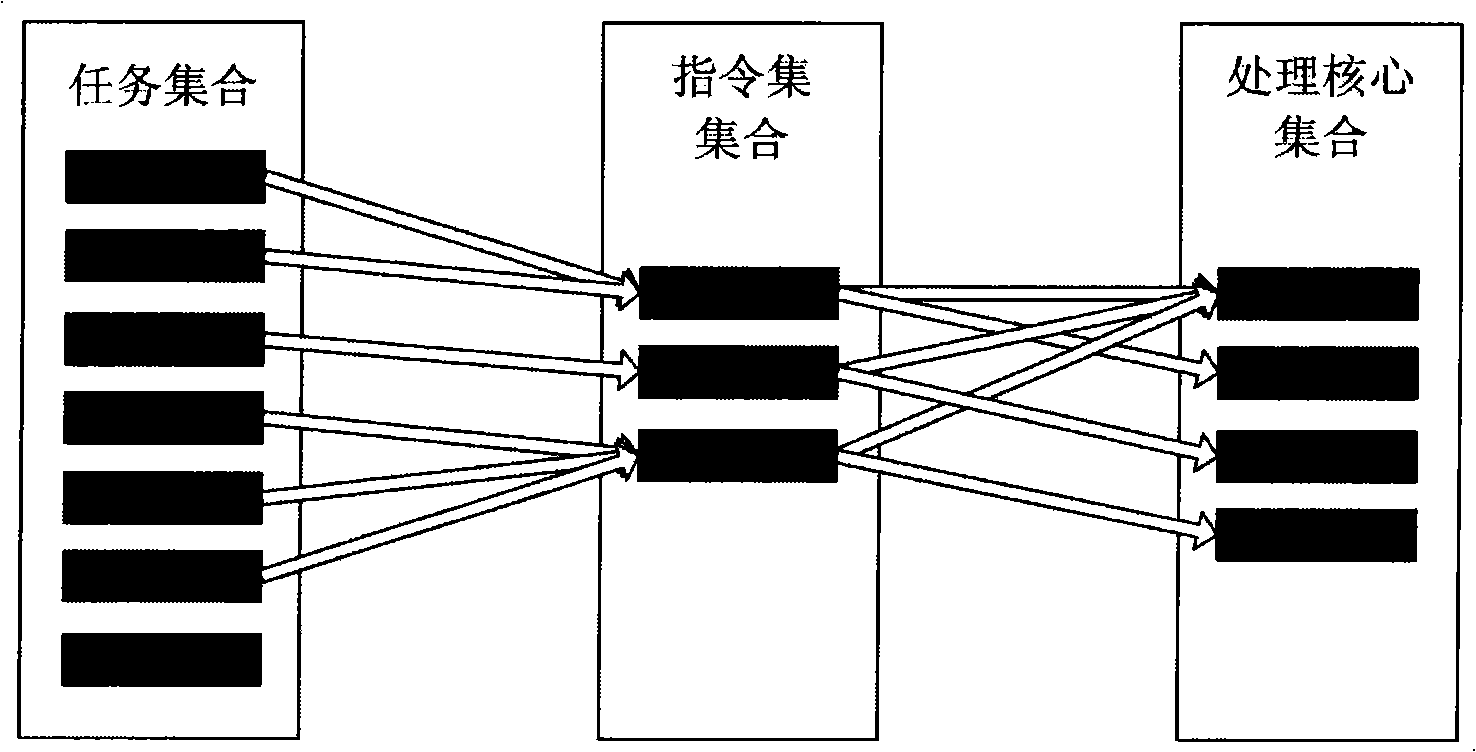

[0030] The specific implementation manner of the present invention will be described below by taking a heterogeneous multi-core system composed of three processing cores as an example.

[0031] a) Choose a heterogeneous multi-core structure

[0032] Each core has a hardware number, starting with 0 and increasing in sequence. The three cores are respectively recorded as core0, core1, and core2. Each processing core has a set of common instruction sets, which are recorded as ISA1. Core1 is extended with a set of instruction sets, which is recorded as ISA2. Core2 is ext...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More