Stack type chip packaging structure and method for preparing stack encapsulation structure

A technology of chip packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as warping of the packaging substrate and the first chip, and achieve the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] In order to make the above-mentioned features and advantages of the present invention more comprehensible, preferred embodiments are specifically cited below and described in detail with accompanying drawings.

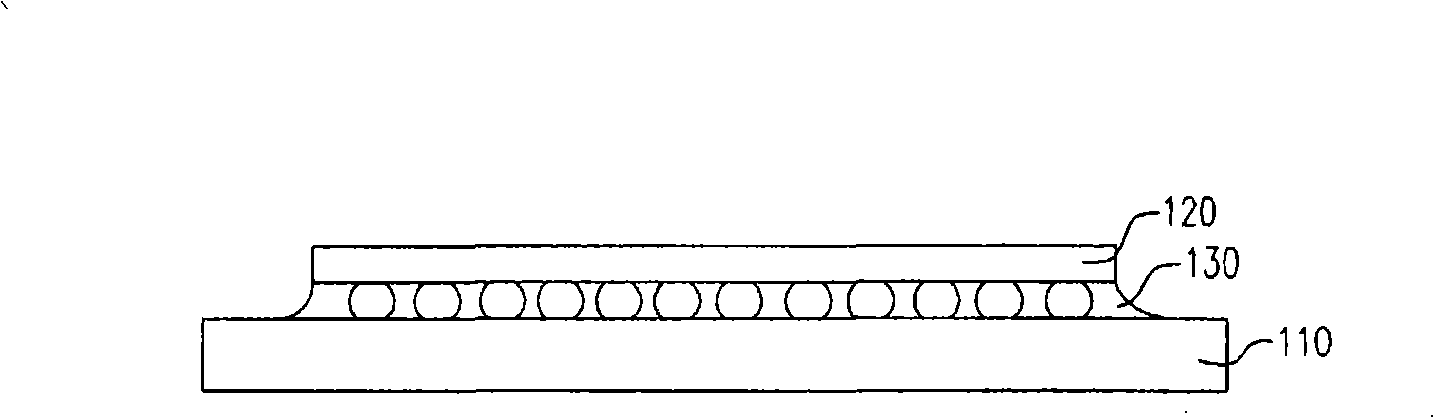

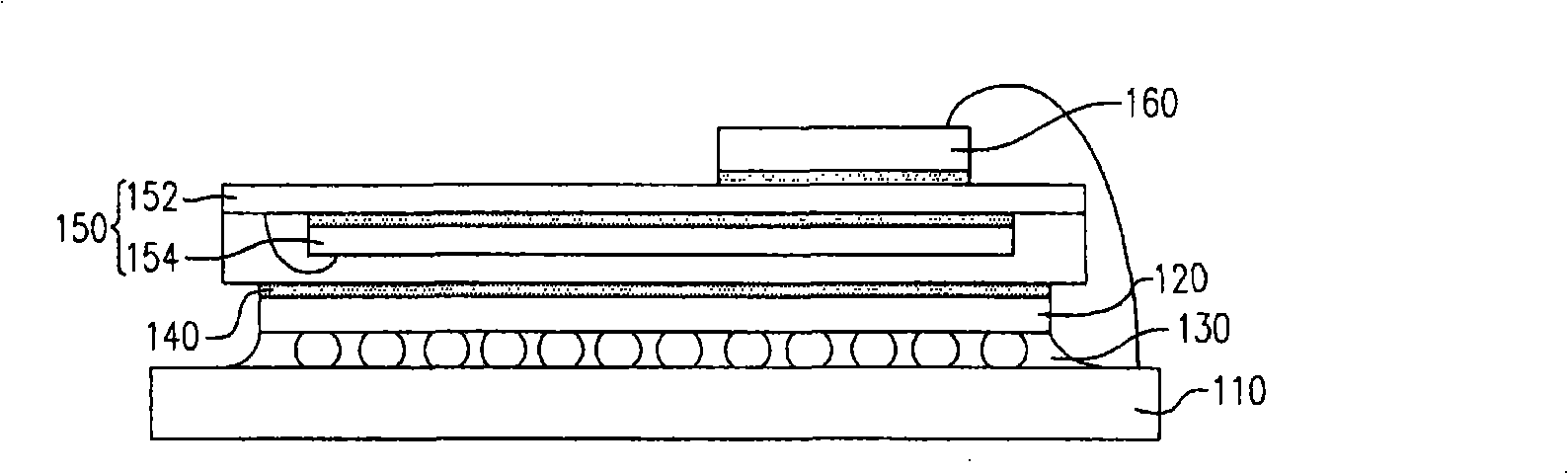

[0065] Figure 2A-2F Shown is a schematic cross-sectional view of the manufacturing process of a stacked chip packaging structure according to an embodiment of the present invention. First, please refer to Figure 2A As shown, a substrate 210 , a first chip 220 and a second chip 230 are provided. Wherein, the substrate 210 has an upper surface 210a and a lower surface 210b opposite to it; the first chip 220 has a first surface 220a and a second surface 220b opposite to it; the second chip 230 has a third surface 230a and its opposite Opposite to a fourth surface 230b, and the second chip 230 has a plurality of bumps 232 disposed on the fourth surface 230b. Next, please refer to Figure 2B As shown, the third surface 230 a of the second chip 230 is fixed on t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More