Semiconductor device and its grid and metal line forming method

A metal circuit pattern and semiconductor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problem that the electrical characteristics of MOS transistors are different from expected values, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

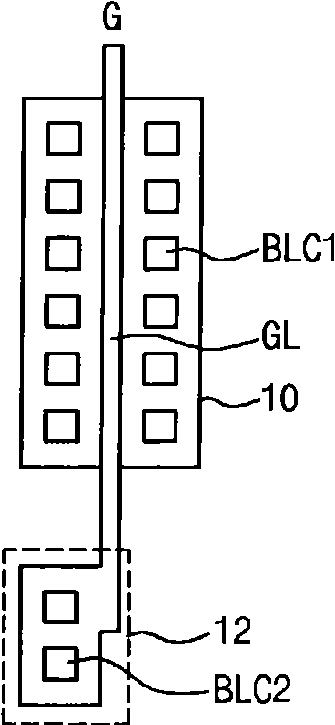

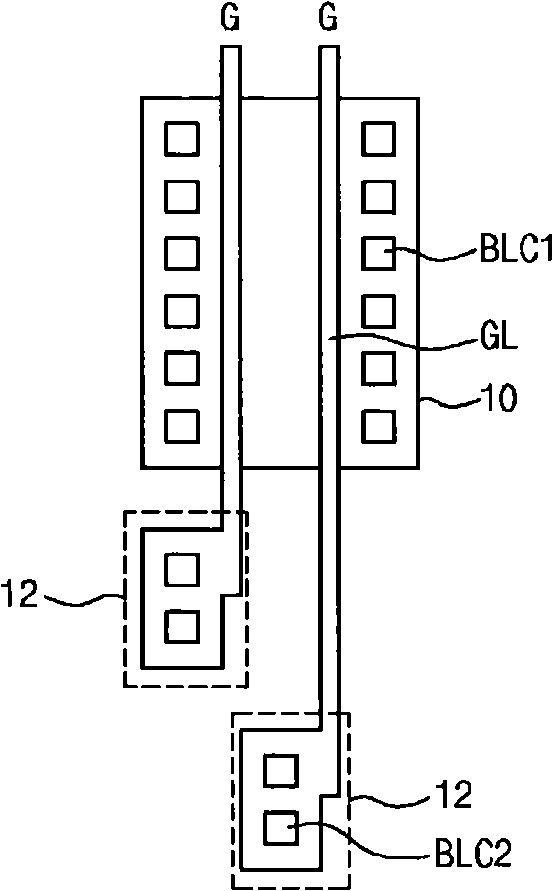

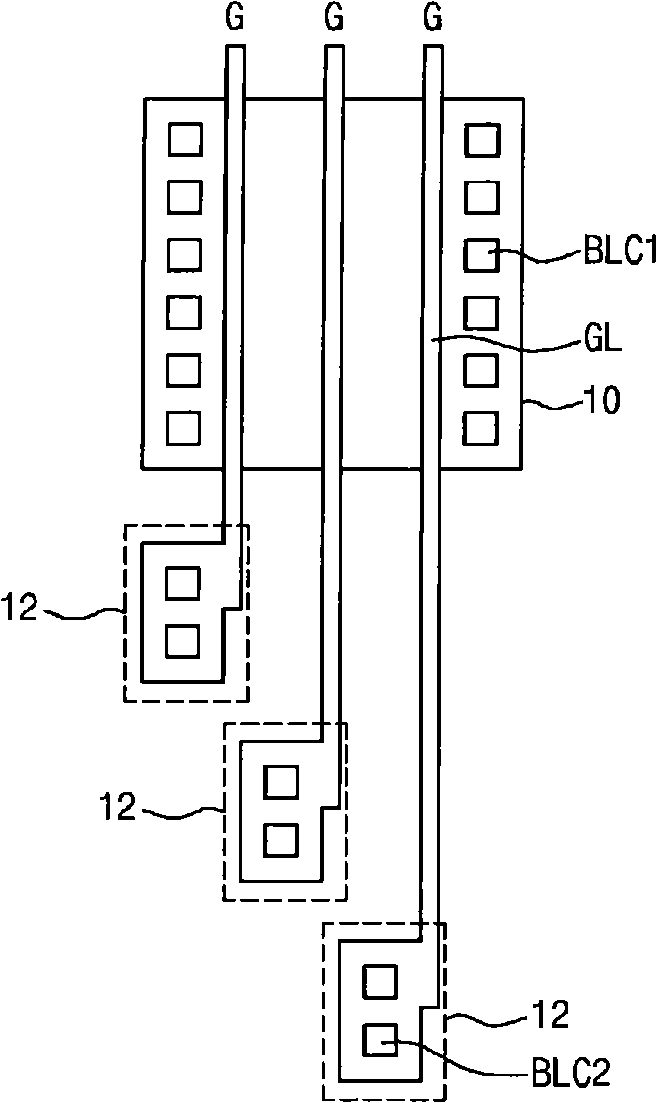

The semiconductor device of the present invention includes a plurality of MOS transistors arranged in a row in a predetermined well region, and the gate of each MOS transistor is composed of an integrated gate line and a gate pad, and one side of the gate line is The gate pad is disposed on the same surface as the gate line based on the extension line of the edge, and the gate pad has a regular shape with one side connected to the extension line.

Specifically, the semiconductor device of the present invention includes a prescribed MOS transistor, the gate of which has a gate line formed on an active region and a gate pad for electrically connecting with a metal line of an upper layer. One structure. Wherein, the gate has a shape as shown in FIG. 8A to FIG. 8E .

First, referring to FIG. 8A , a gate G is formed on the active region 30 , and a channel region is formed in the active region 30 overlapping the gate G. Also, a drain region and a source region are formed on both si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More