Chip, chip interconnection system and method for calibrating chip interconnection

A chip and syndrome technology, applied in the electronic field, can solve problems such as the complexity of chip interconnection verification, and achieve the effect of simple technology and convenient testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

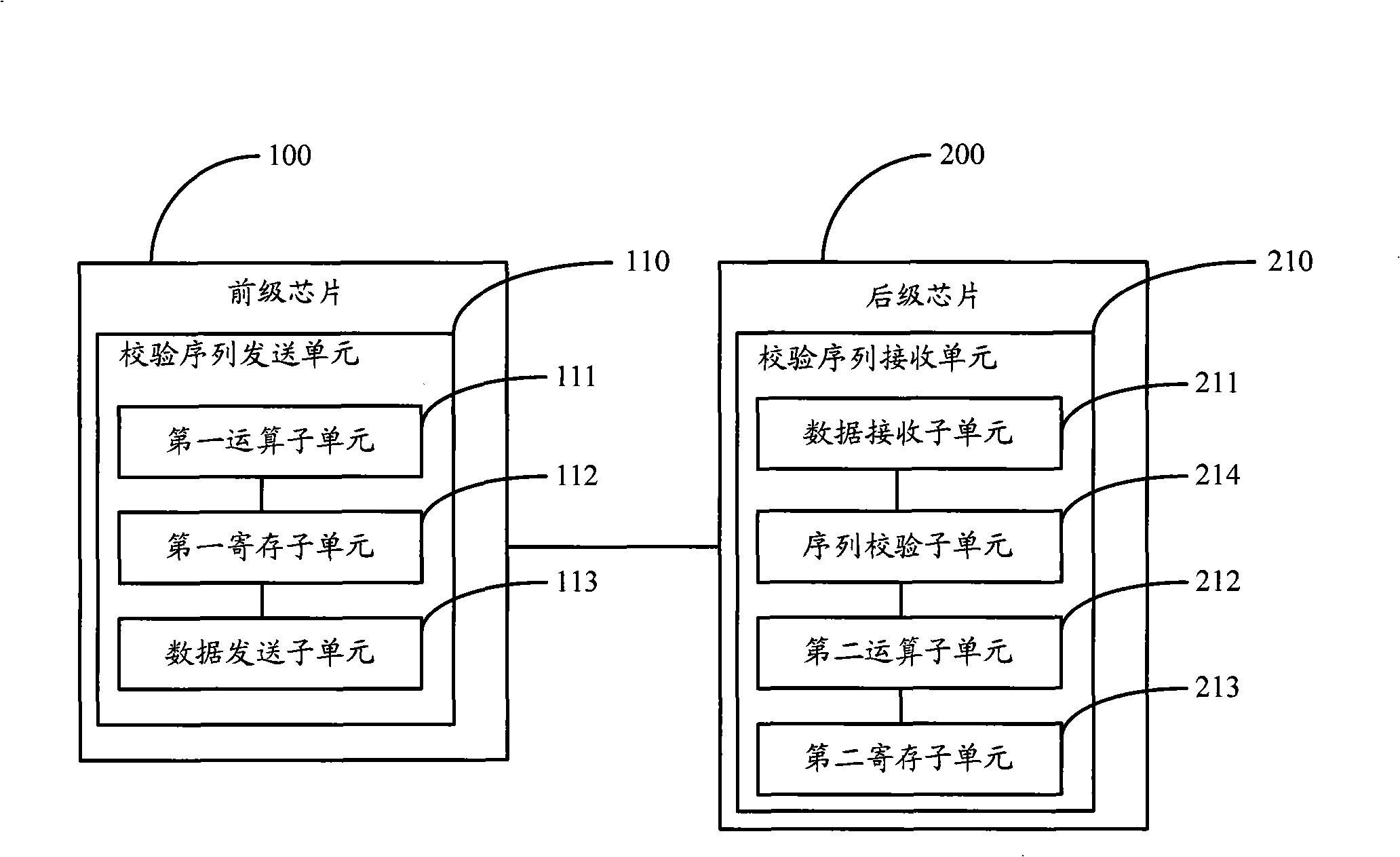

[0018] The invention discloses a chip interconnection system, an embodiment of which is as follows figure 1 As shown, it includes an interconnected front-end chip 100 and a back-end chip 200 , the front-end chip 100 includes a check sequence sending unit 110 , and the back-end chip 200 includes a check sequence receiving unit 210 . Wherein, the check sequence sending unit 110 uses a plurality of single-bit data to generate a shifted check sequence according to a preset check algorithm, and sends the data of the shifted check sequence to the subsequent chip 200 in sequence; the check sequence receives The unit 210 uses the same multiple single-bit data as the check sequence sending unit 110, and generates a shifted comparison sequence according to the same check algorithm as that in the check sequence sending unit 110, and then compares the shifted compar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More