Fast fourier transform architecture

A Fourier transform, fast technology, applied in special data processing applications, complex mathematical operations, instruments, etc., to achieve the effect of high data processing rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

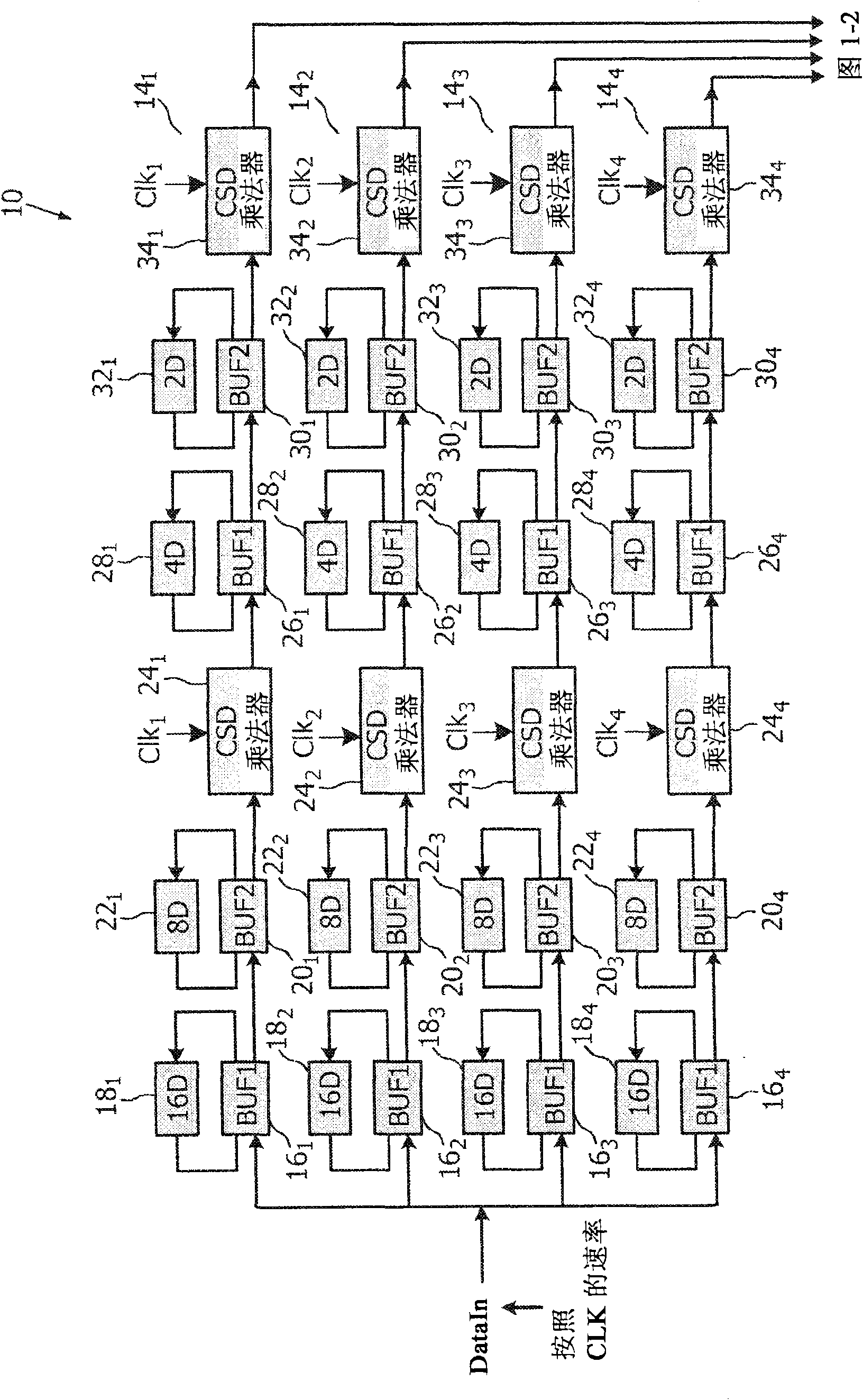

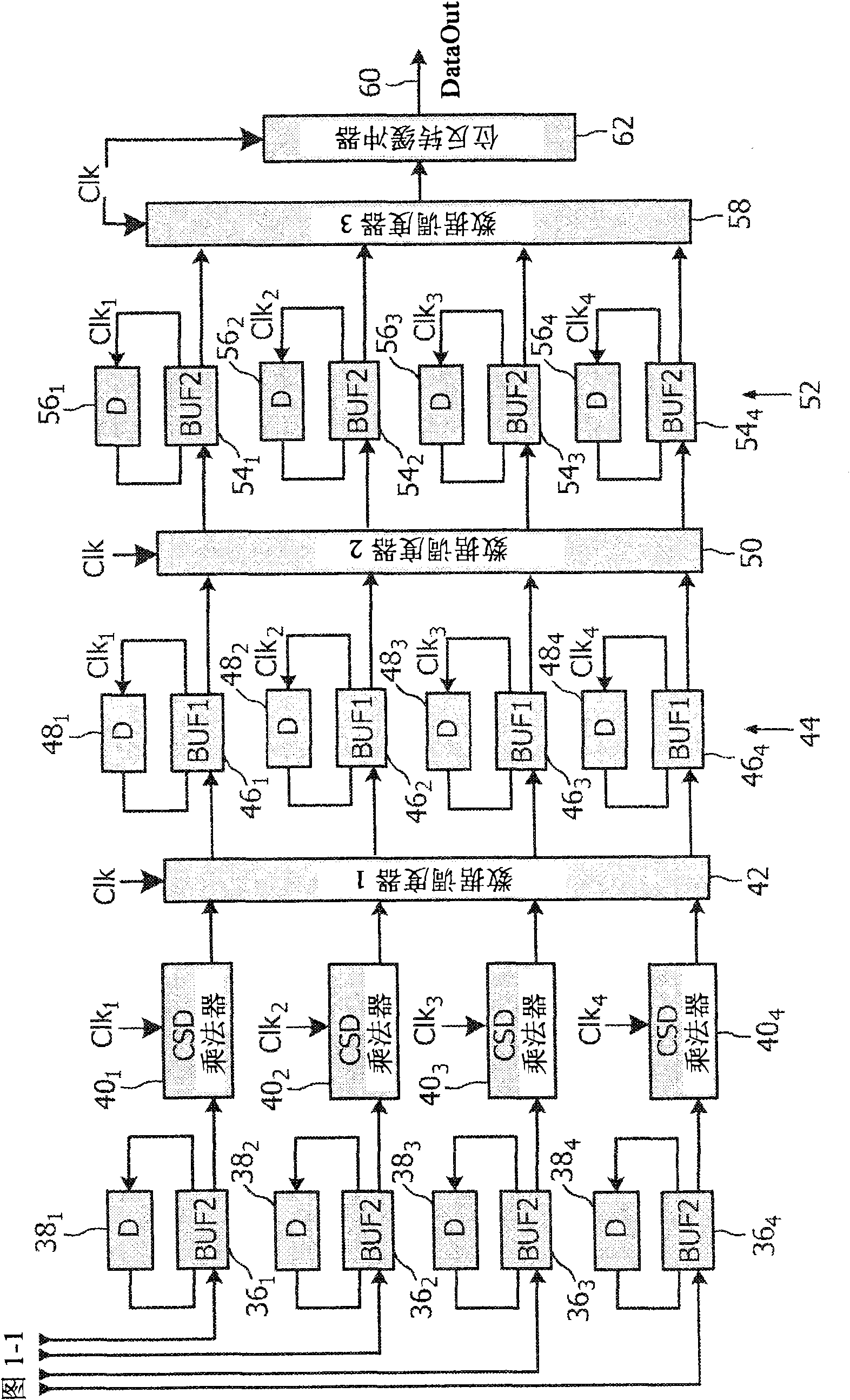

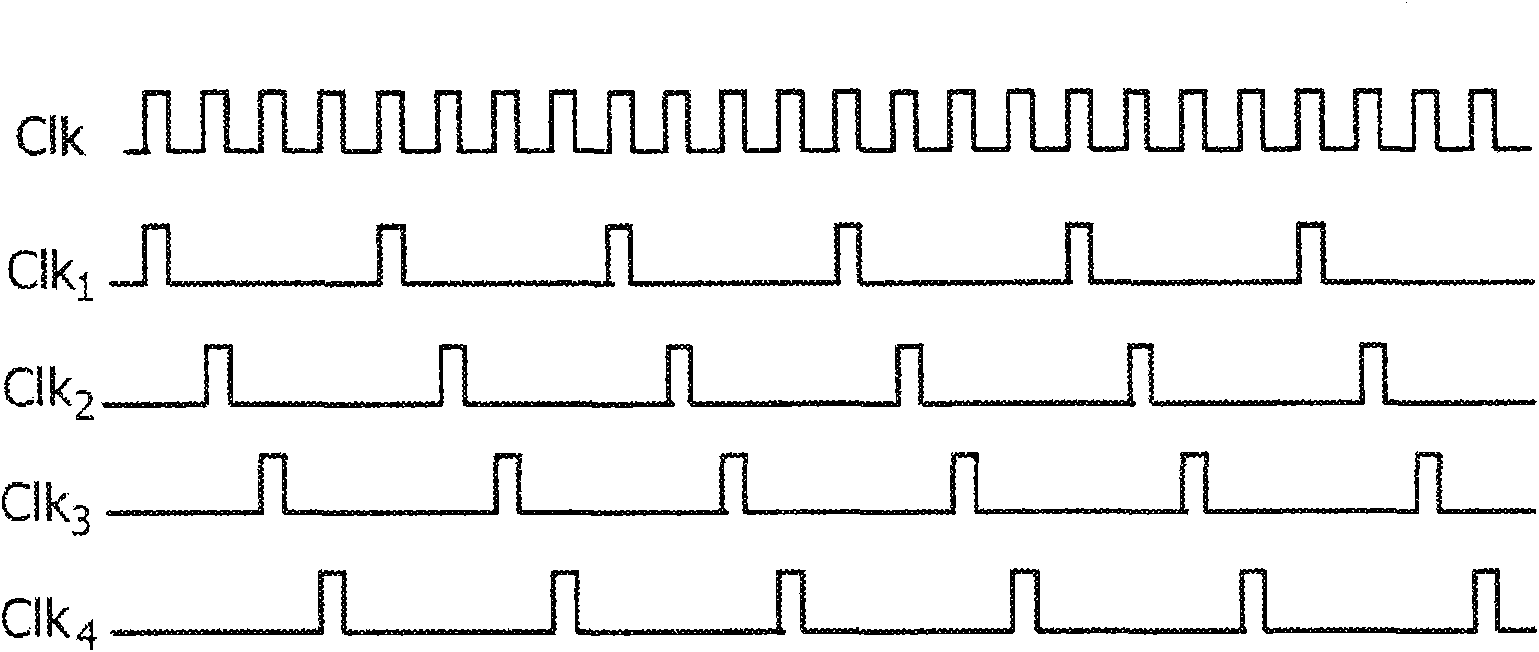

[0027] FIG. 1 shows a fast Fourier transform processor 10 . Input data DataIn is received on input line 12 with a data rate corresponding to the frequency of clock signal Clk. Input data in four data processing channels 14 1 、14 2 、14 3 and 14 4 be divided between. Since the four data processing channels 14 1 、14 2 、14 3 and 14 4 are essentially the same, so only the first data processing channel 14 will be described in detail below 1 . with the first data processing channel 14 1 The characteristics of the same second, third and fourth data processing channels 14 2 、14 3 and 14 4 Corresponding features of are identified in FIG. 1 by the same reference numerals with subscripts relative to the numbers of the data processing lanes.

[0028] Although this embodiment of the invention has four parallel data processing lanes, it should be understood that other degrees of parallel processing can be used as desired.

[0029] Although this illustrated embodiment of the in...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap