Verification environment system and construction method thereof

A technology for verifying environment and signals, applied in the field of verification, can solve the problems of shortened development cycle, relying on manual editing, lack of unified construction of the main line and automated construction ideas, etc., to achieve the effect of rapid construction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

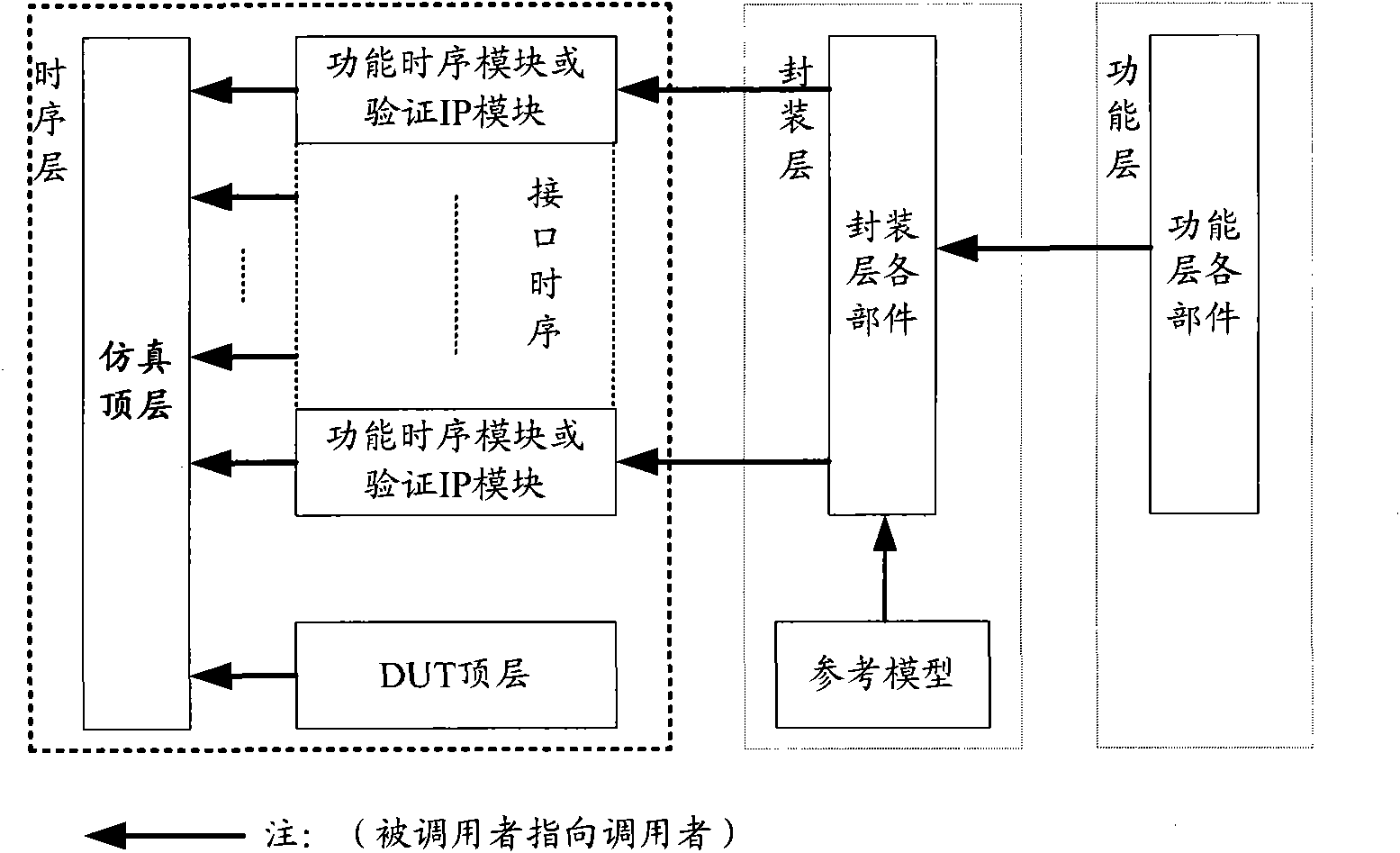

[0029] The embodiment of the present invention provides a method for building a verification environment and a verification environment system. Through the port information at the top layer of the DUT, the construction instructions are transmitted in the direction of the reverse configuration flow, so as to realize the signal-based functional layering and effective reuse of environmental components, and Reduce the gap between design and verification.

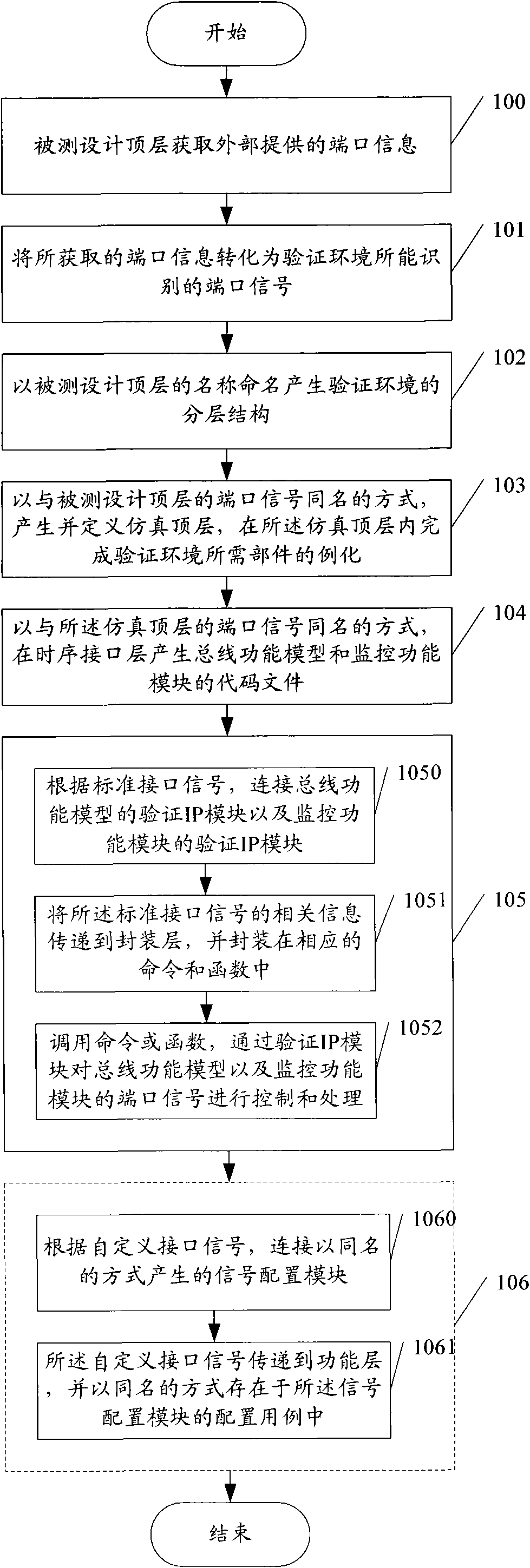

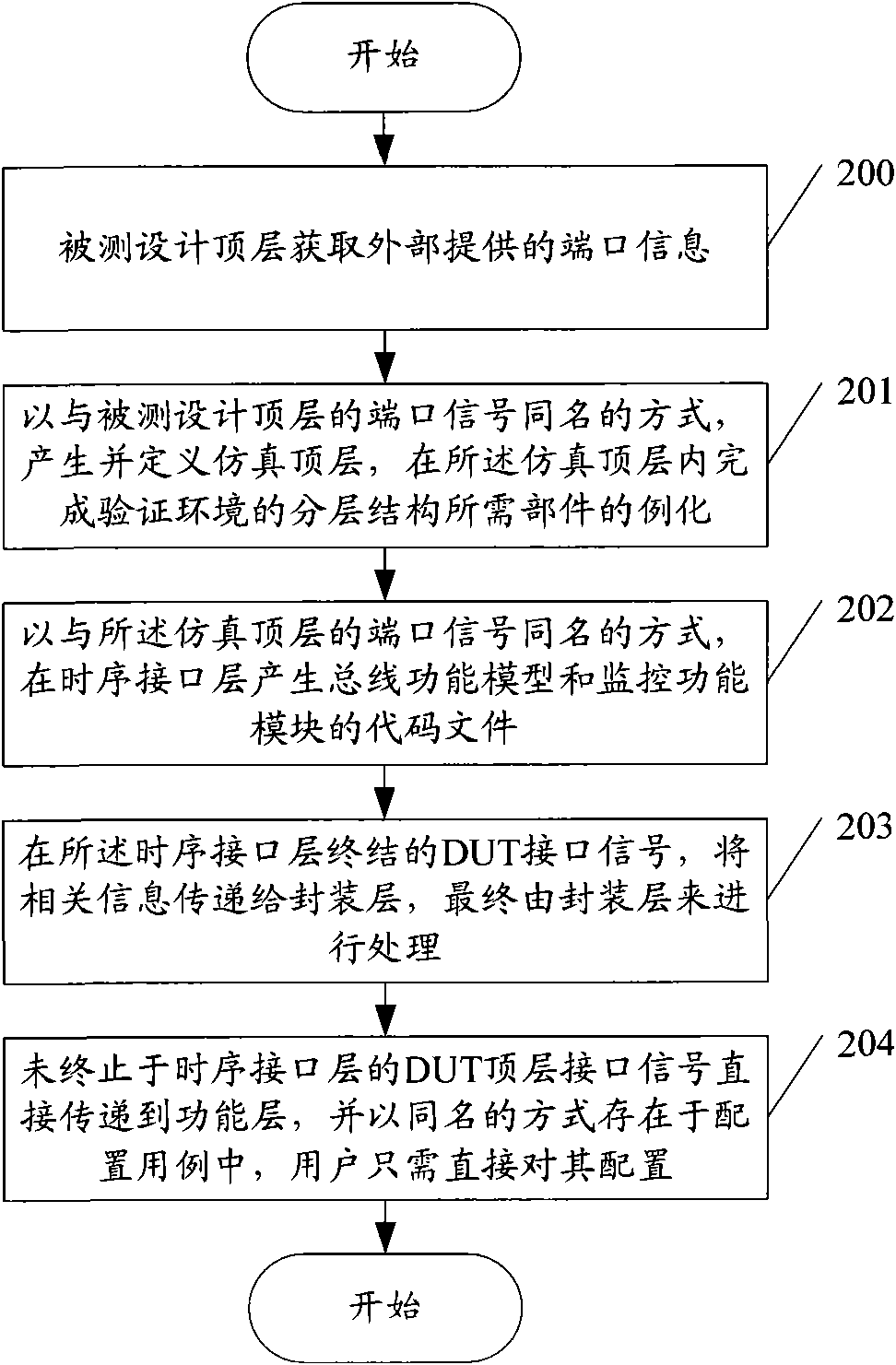

[0030] see figure 2 , is a schematic flowchart of the first embodiment of the verification environment building method provided by the embodiment of the present invention.

[0031] In step 100, the top layer of the design under test obtains externally provided port information;

[0032] In step 101, the obtained port information is converted into a port signal that can be recognized by the verification environment;

[0033] In step 102, according to the port signal, a hierarchical structure starting from the top layer of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More