Semiconductor memory device

A storage device and semiconductor technology, applied in information storage, static memory, digital memory information and other directions, can solve the problems of time delay in writing, inability to read data, wrong writing, etc., to ensure the read and write operation margin. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

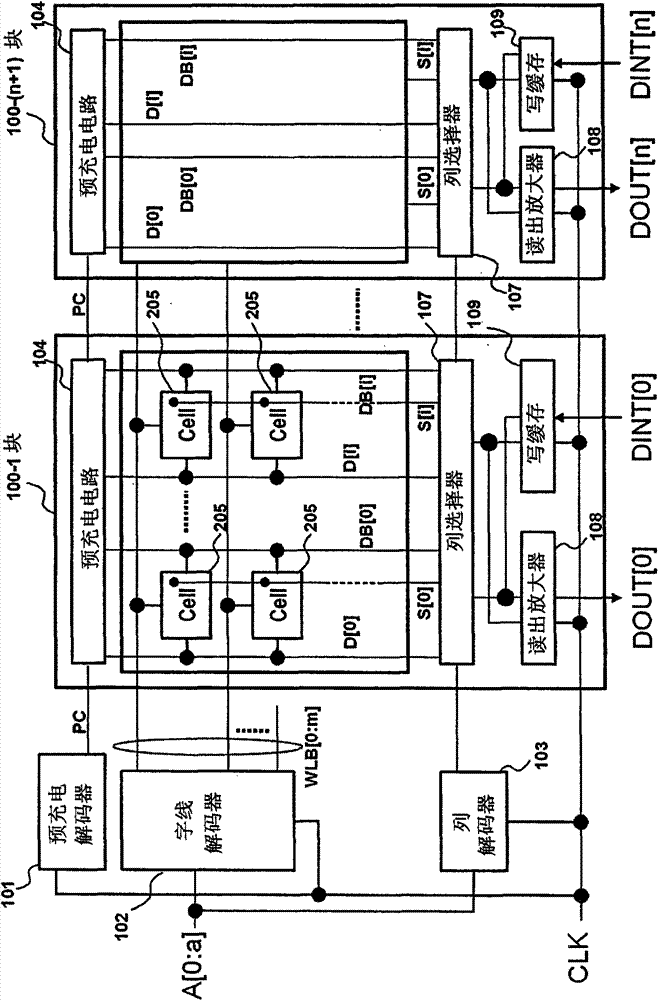

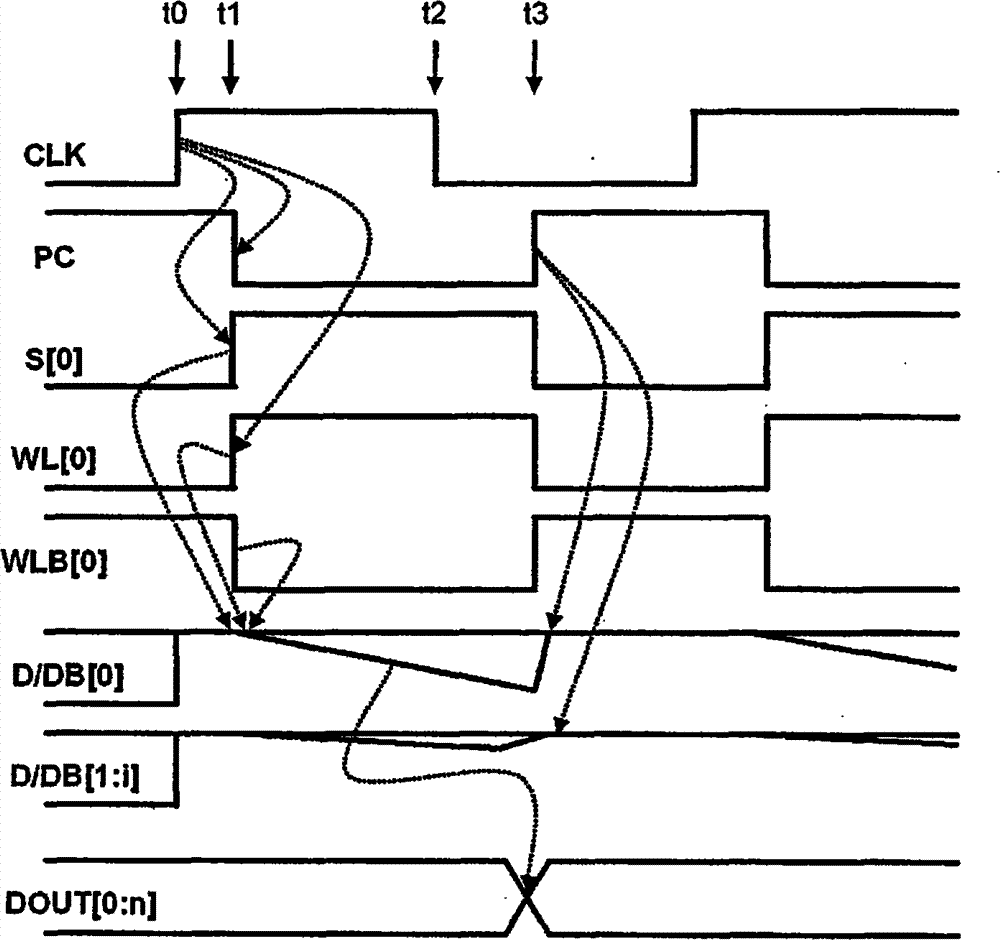

[0053] figure 1 It is an overall block diagram of the semiconductor memory device of the first embodiment. figure 1 The semiconductor memory device is composed of n+1 (bit) memory blocks of 100-1 to 100-(n+1). Each memory block is composed of i+1 columns from 0 to i, and the address is specified and accessed through m+1 word lines from 0 to m, so the whole is [(m+1)×(i+1)] word The configuration of ×(n+1) bits (digits). In addition, corresponding to this configuration, a precharge decoder 101 , a word line decoder 102 , and a column decoder 103 are provided. In addition, each memory block is provided with: memory cells 205 arranged as (m+1)×(i+1), AND charging circuits 104, column selectors 107, sense amplifiers 108, and write buffers respectively arranged according to each bit line. 109. Further, the memory cells 205 are connected to column selection lines S[0:i]. By this column selection line S[0:i], the bit line pairs other than the selected bit line pair are separat...

Embodiment 2

[0070] Figure 4 It is an overall circuit block diagram showing a semiconductor memory device according to Embodiment 2 of the present invention. In the second embodiment, the parts having basically the same structure as that of the first embodiment are given the same symbols in the drawings as those of the first embodiment, and detailed description thereof will be omitted. Figure 4 and figure 1 The difference is that the memory blocks (100-1 to 100-(n+1)) are not only wired with the word line (logic inversion) WLB[0:m], but also wired with the word line (positive logic) WL[ 0:m]. Other constitution and embodiment 1 figure 1 basically the same.

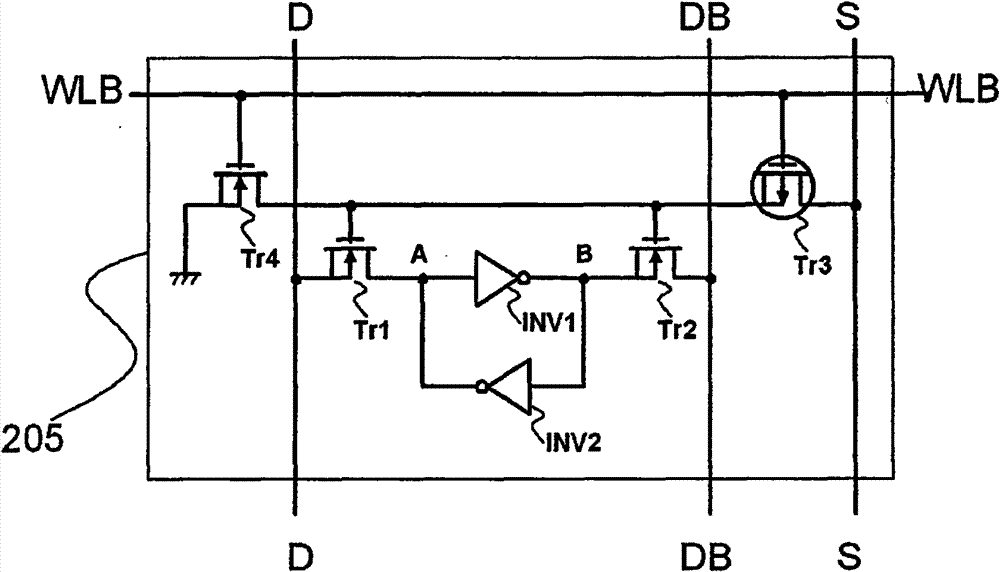

[0071] Figure 5 yes means Figure 4 A block diagram of the construction of the storage unit 305 is shown. and Example 1's figure 2Compared with the memory cell of the above, the difference is that, between the column selection line S[0:i] and the gates of the access transistors Tr1 and Tr2, a second access transistor cont...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More