High-precision voltage reference circuit

A voltage reference, high-precision technology, applied in the direction of adjusting electrical variables, control/regulation systems, instruments, etc., can solve the problem of low precision, achieve high output impedance, meet power consumption requirements, and stabilize the drain current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

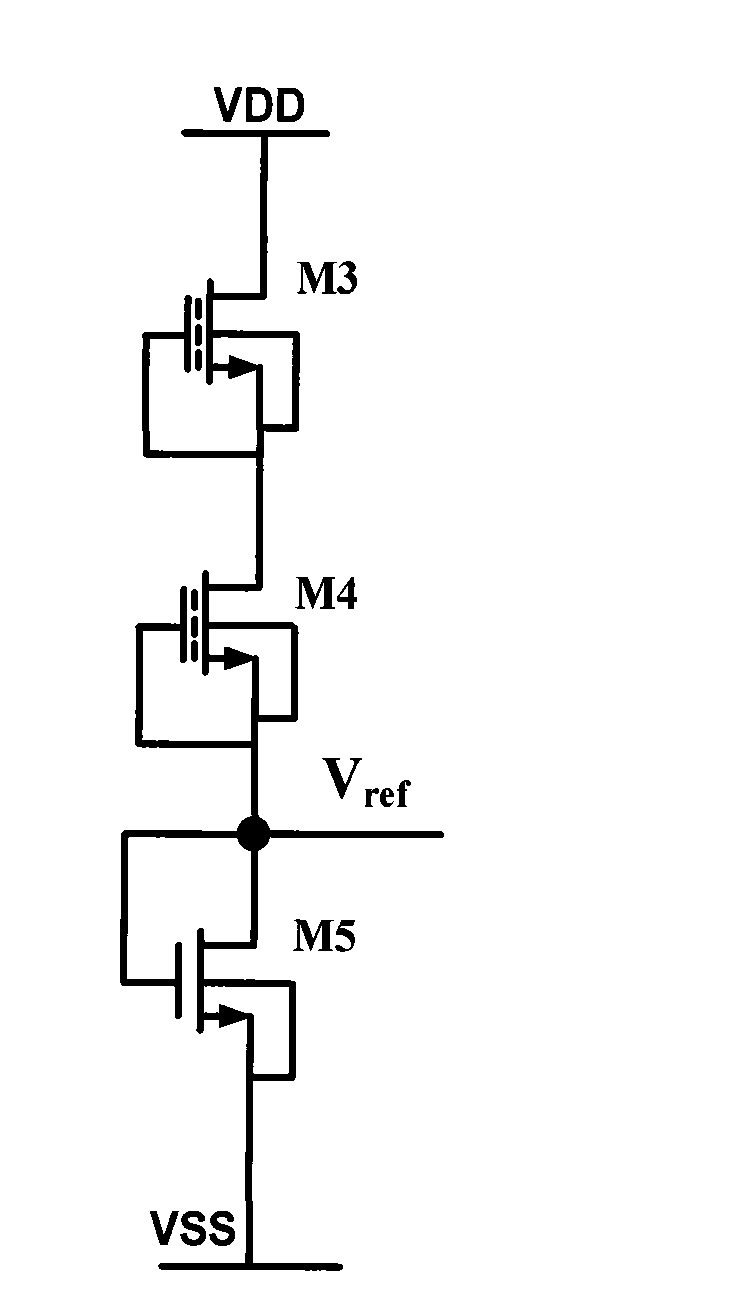

[0022] Embodiment 1: refer to figure 1 , The voltage reference circuit is composed of a depletion NMOS transistor M3 and a depletion NMOS transistor M4, and an enhancement NMOS transistor M5. The drain of the depletion NMOS transistor M3 is connected to the positive power supply VDD, the gate of the depletion NMOS transistor M3 is connected to the source and is connected to the drain of the depletion NMOS transistor M4. The gate and source of the depletion NMOS transistor M4 are connected and connected to the drain of the enhancement NMOS transistor M5. The gate of the enhanced NMOS transistor M5 is connected to the drain, and the source of the enhanced NMOS transistor M5 is connected to the negative power supply VSS. The gate of the enhancement NMOS transistor M5 is the output terminal of the voltage reference. The substrates of all NMOS transistors are connected to their respective sources.

[0023] The sources of the depletion NMOS transistor M3 , the depletion NMOS tra...

Embodiment 2

[0035] Embodiment 2: refer to figure 2 , A voltage reference circuit that outputs a low voltage reference. The circuit is composed of a depletion NMOS transistor M3 and a depletion NMOS transistor M4, and an enhancement NMOS transistor M5. The drain of the depletion NMOS transistor M3 is connected to the positive power supply VDD, and the gate and source of the depletion NMOS transistor M3 are connected to the drain of the depletion NMOS transistor M4. The gate of the depletion NMOS transistor M4 is connected to the source of the enhancement NMOS transistor M5, and the source of the depletion NMOS transistor M4 is connected to the drain of the enhancement NMOS transistor M5. The gate of the enhanced NMOS transistor M5 is connected to the drain, and the source of the enhanced NMOS transistor M5 is connected to the negative power supply VSS. The gate of the enhancement NMOS transistor M5 is the output terminal of the voltage reference. The substrates of all CMOS transistors ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More