Method and system for switching main and backup clocks

A master/standby switchover and clock switchover technology, applied in transmission systems, digital transmission systems, electrical components, etc., can solve problems such as discontinuity of clock phases, complex connections between master and standby boards, hidden dangers in reliability, etc., and achieve simple structure, Phase and system stability and good reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings.

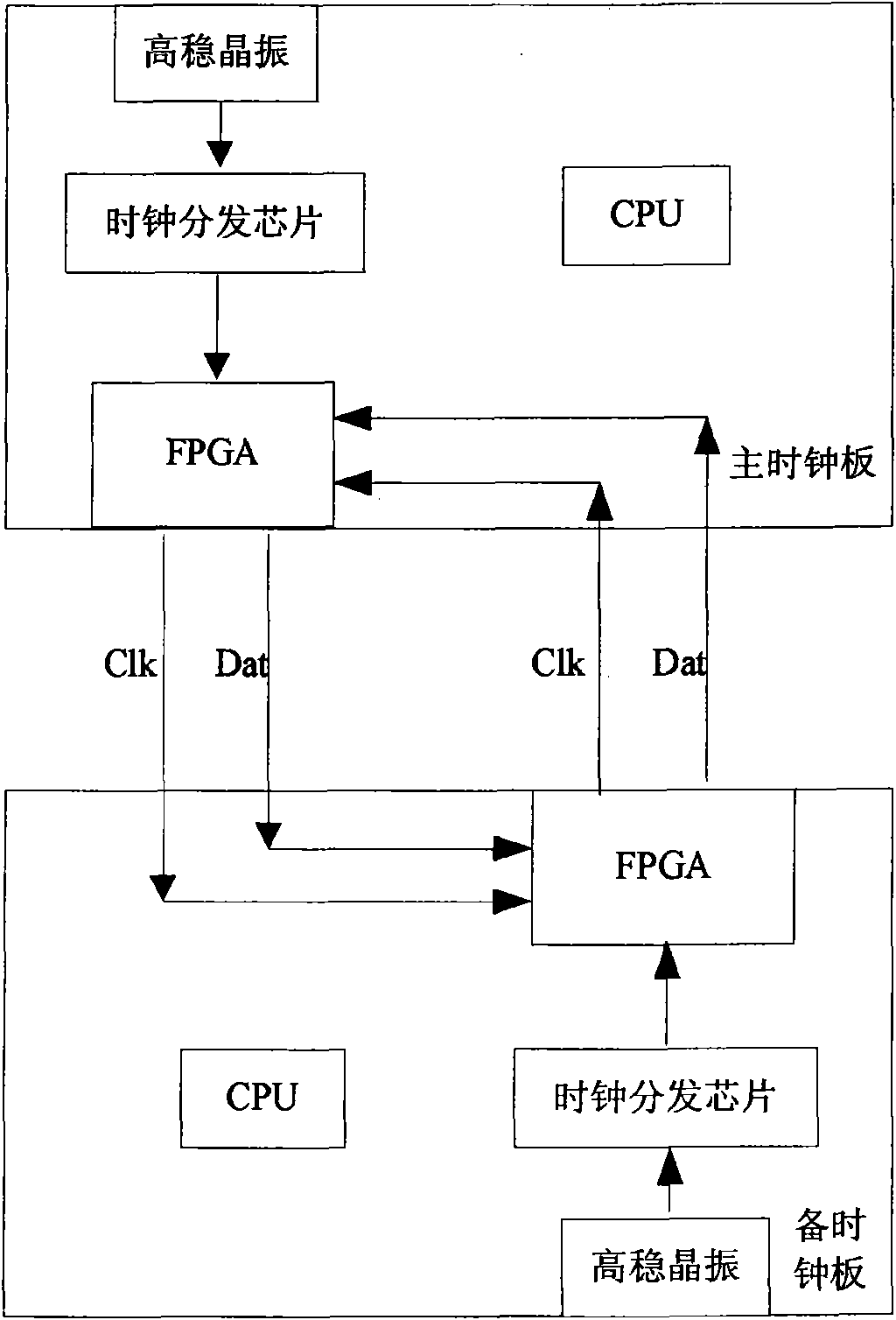

[0056] Such as figure 1 As shown, the system for realizing master-standby clock switching in this embodiment includes a master clock board and a slave clock board, both of which have a CPU, a clock source of the same frequency, a clock distribution chip and a logic chip. The logic chip of this embodiment is implemented by a Field Programmable Gate Array module (Field Programmable Gate Array, FPGA for short), and the same-frequency clock source is implemented by a high-stable crystal oscillator. The clocks of the main clock board and the standby clock board respectively track the same-frequency high-stable crystal oscillator of the clock board, so that the output frequencies of the main and standby clocks are basically the same. The logic chips of the main clock board and the standby clock board are connected by two pairs of mu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More