On-line programming FPGA reconfigurable device

A bus and signal line technology, applied in the field of FPGA reconfigurable devices with online programming, can solve the problems of not meeting the original intention of reconfigurable design, waste of hardware resources, complicated design process, etc., to achieve flexible and convenient transmission or sharing, and hardware structure. Simple, small time slot effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

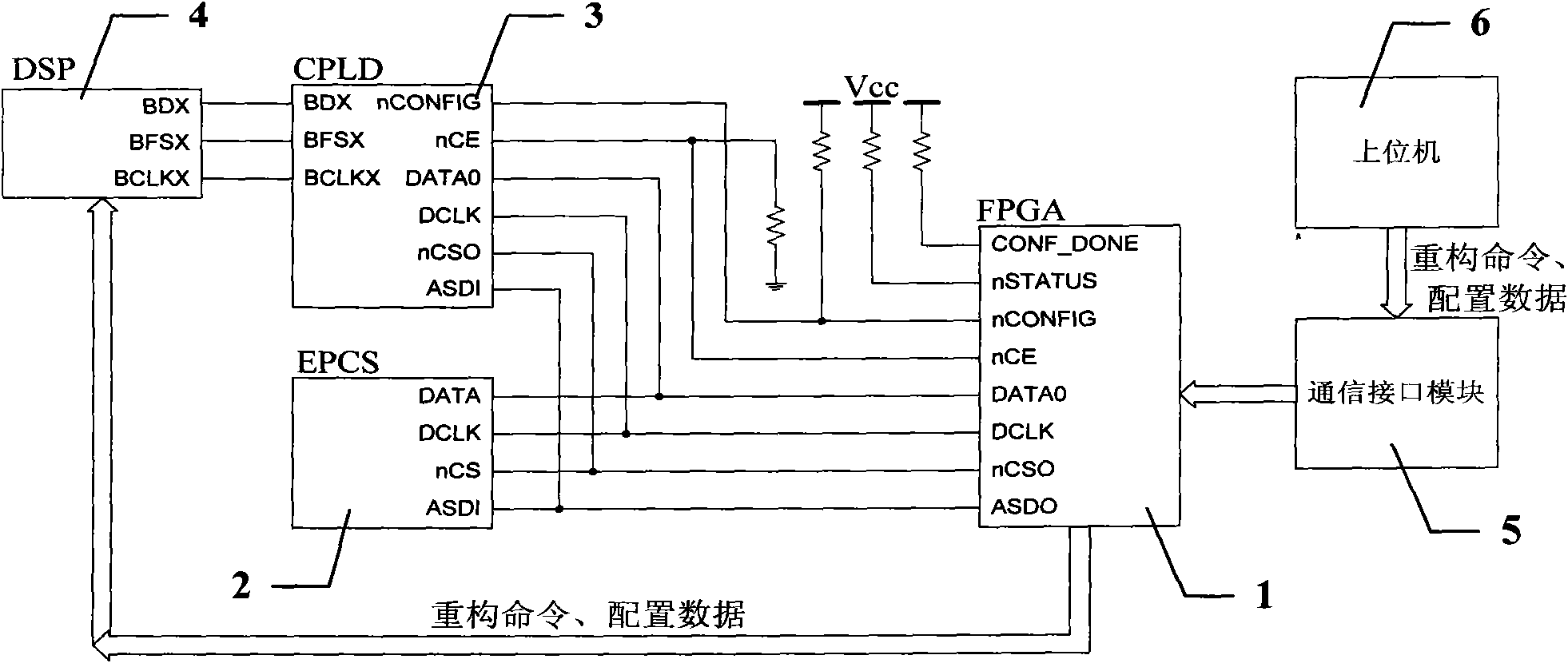

[0019] figure 1 It is a circuit principle block diagram of a specific embodiment of the FPGA reconfigurable device for online programming of the present invention. In this example, if figure 1 As shown, the FPGA reconfigurable device for online programming includes an FPGA 1 , a configuration chip 2 , a configuration chip controller 3 , a DSP processor 4 and a communication interface module 5 . In this embodiment, the communication between the DSP processor 4 and the upper computer 6 is through the communication interface module 5 and the reconstruction command and configuration data are transmitted to the DSP processor 4 with the cooperation of the FPGA.

[0020] In this embodiment, the configuration chip 2 is an EPCS, that is, a serial memory, whose nCS, DCLK, ASDI, and DATA signal lines are connected to the FPGA 1 for storing configuration data of the FPGA 1 . After the FPGA 1 is powered on or the FPGA configuration data in the configuration chip 2 is updated, the FPGA 1 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More