Thin SOI longitudinal bipolar transistor and manufacturing method thereof

A technology of bipolar transistor and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the complex process, large capacitance between base and emitter and collector, and quasi-precision requirements Advanced problems, to achieve the effect of reducing the difficulty of the process, improving the frequency performance, and reducing the complexity of the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The thin SOI vertical bipolar transistor of the present invention and its manufacturing method will be further described in detail below.

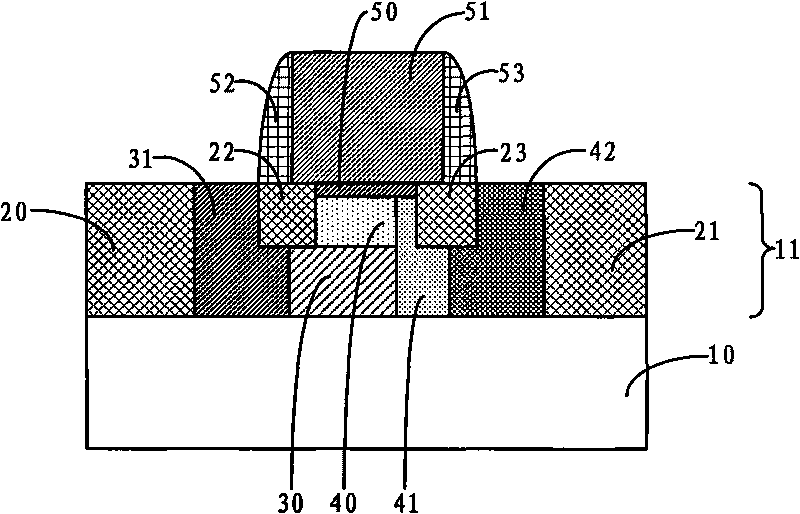

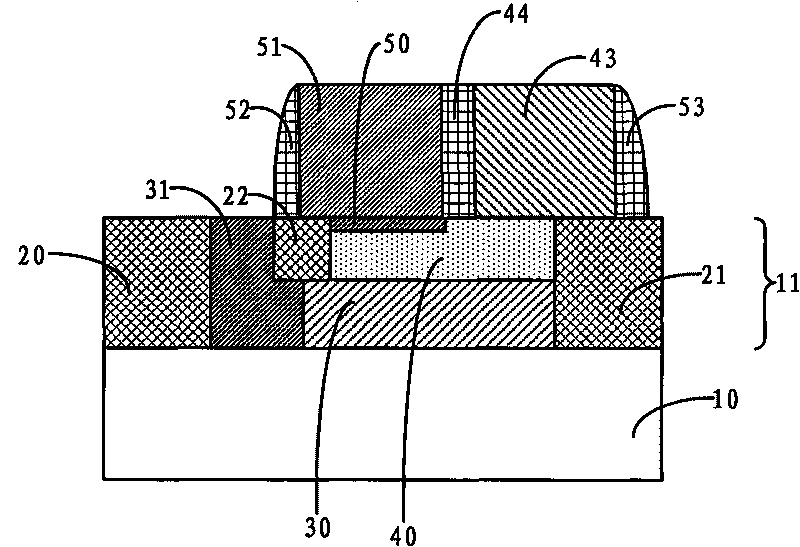

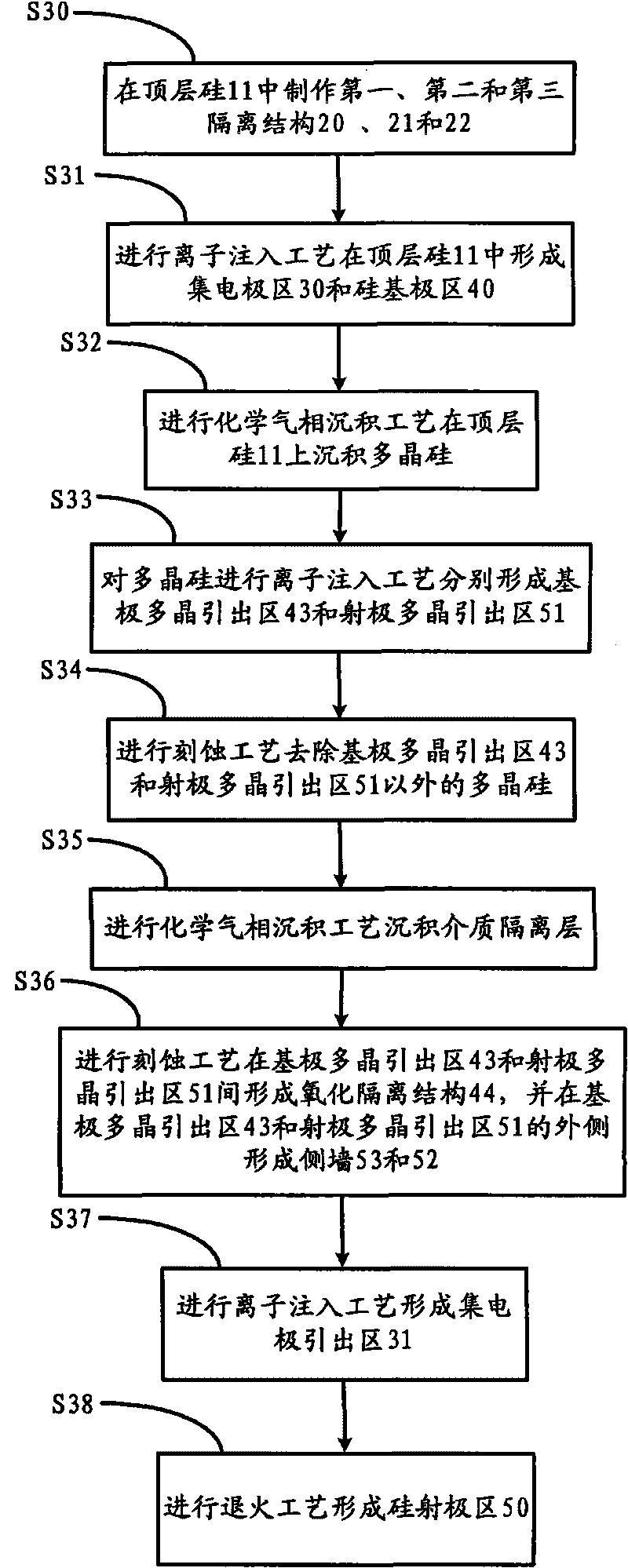

[0027] see figure 2 , which shows the composition structure of the thin SOI vertical bipolar transistor of the present invention, as shown in the figure, the thin SOI vertical bipolar transistor of the present invention is fabricated in the top layer silicon 11 and located in the first and second isolation structures 20 and 21, the top layer of silicon 11 is fabricated on the insulating buried layer 10, and there is also a third isolation structure 22 in the top layer of silicon 11. Under the insulating buried layer 10 is a silicon substrate (not shown), and the insulating buried layer 10 is usually silicon oxide. The thin SOI vertical bipolar transistor of the present invention includes a collector region 30, a silicon base region 40, a silicon emitter region 50, a collector lead-out region 31, a polycrystalline base region 43 and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More