Patents

Literature

57results about How to "Improve frequency performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Hybrid frequency offset estimator

ActiveUS20050058229A1Improve frequency performanceImprove performancePolarisation/directional diversityLine-faulsts/interference reductionPacket lossSignal-to-noise ratio (imaging)

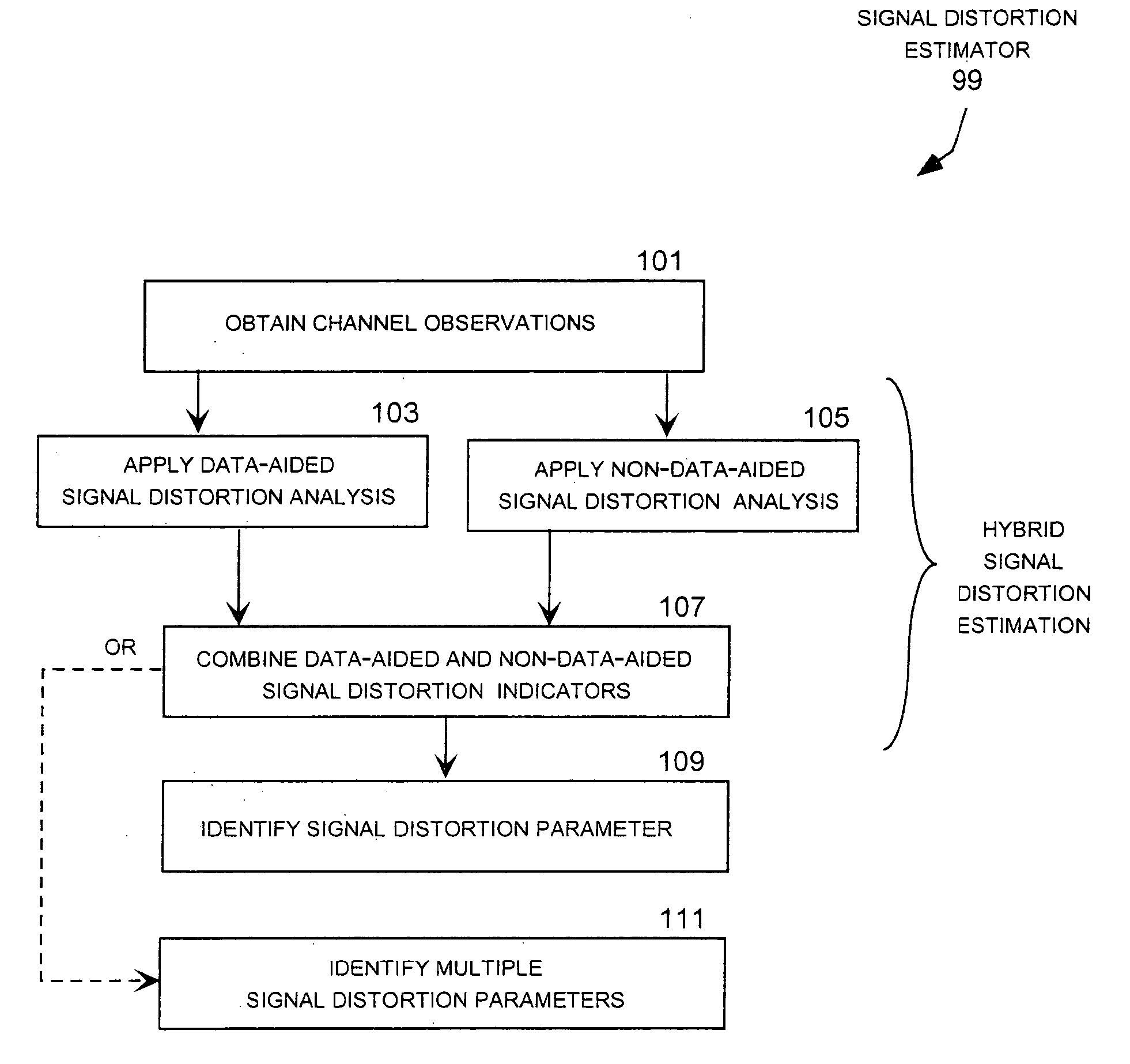

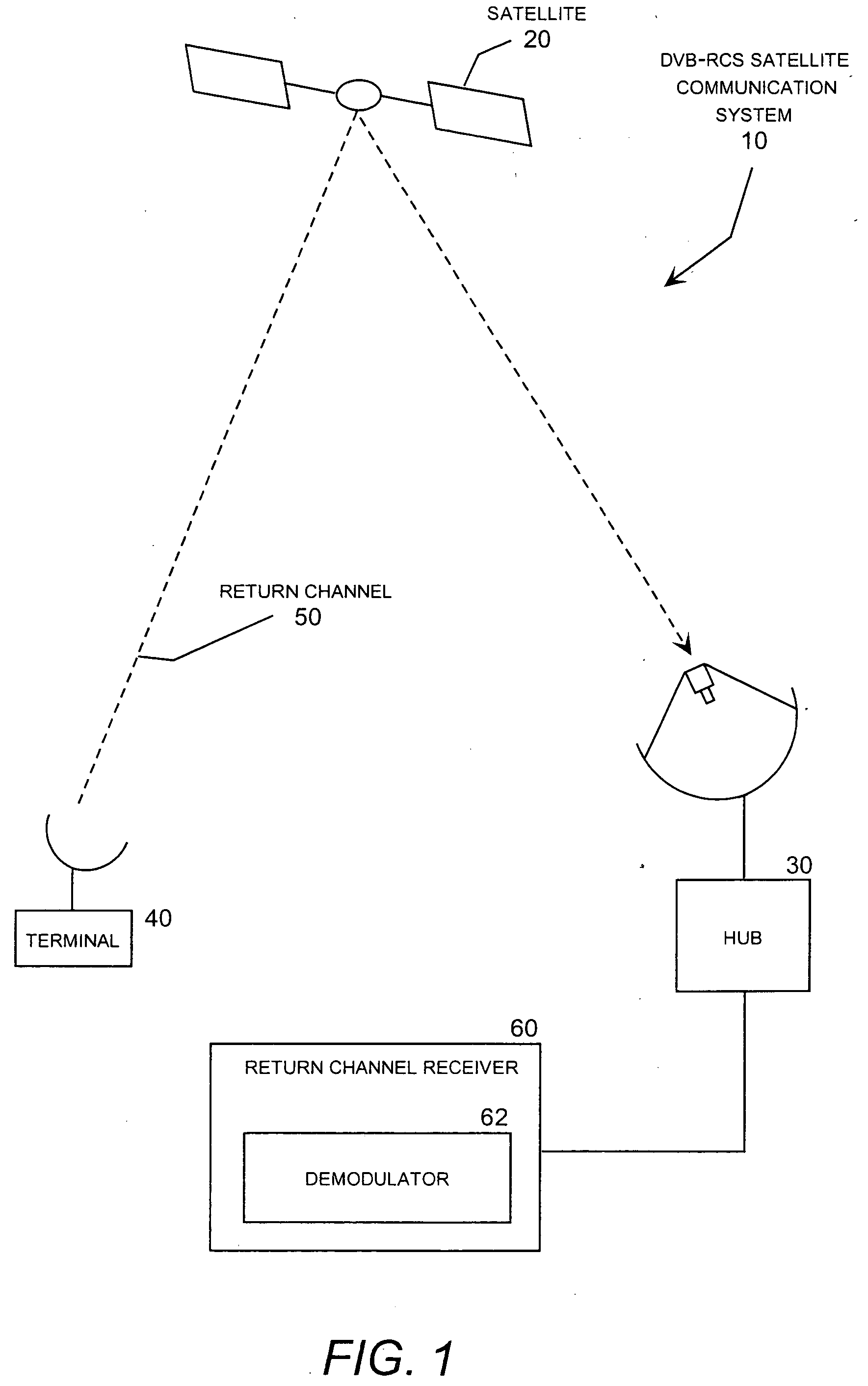

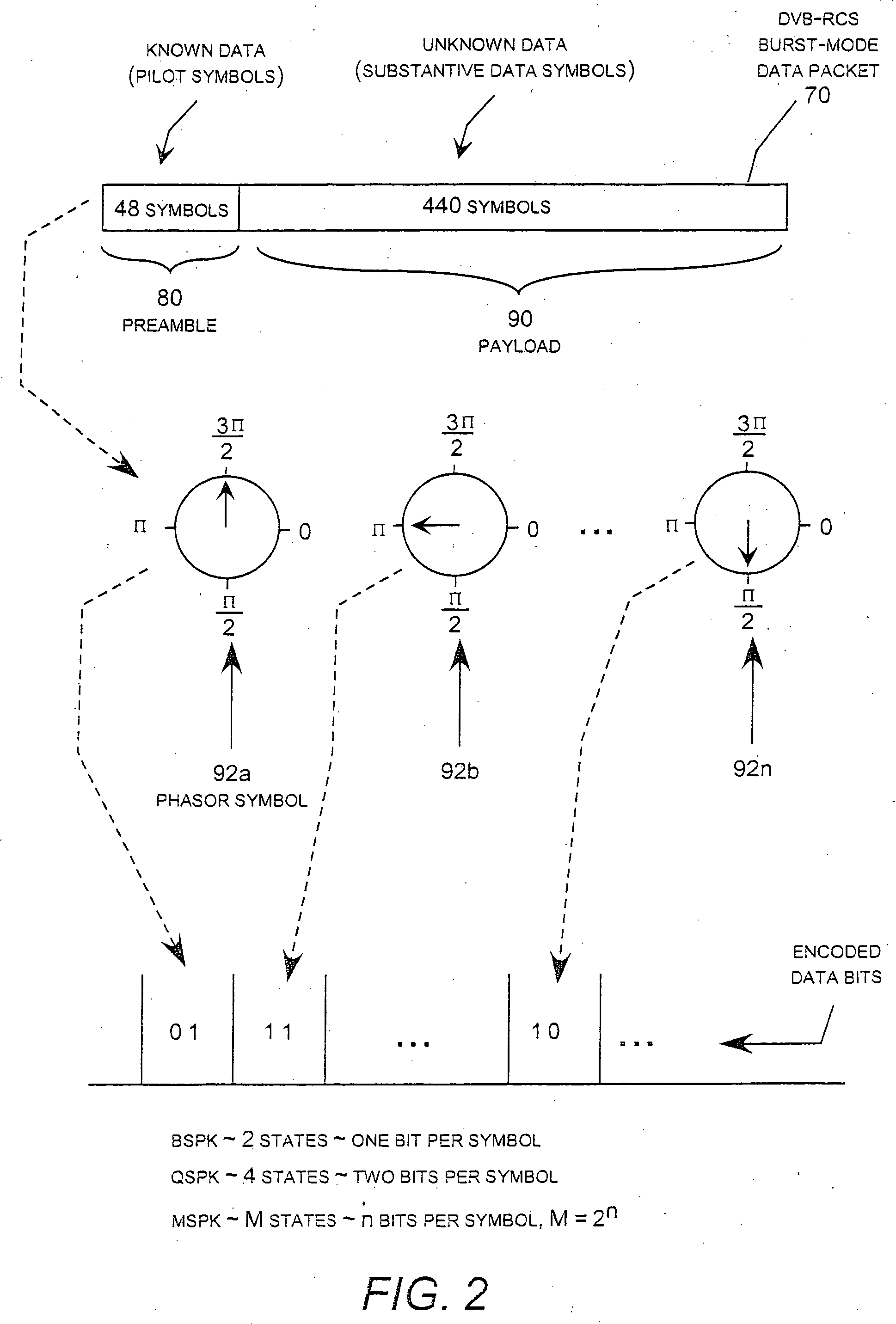

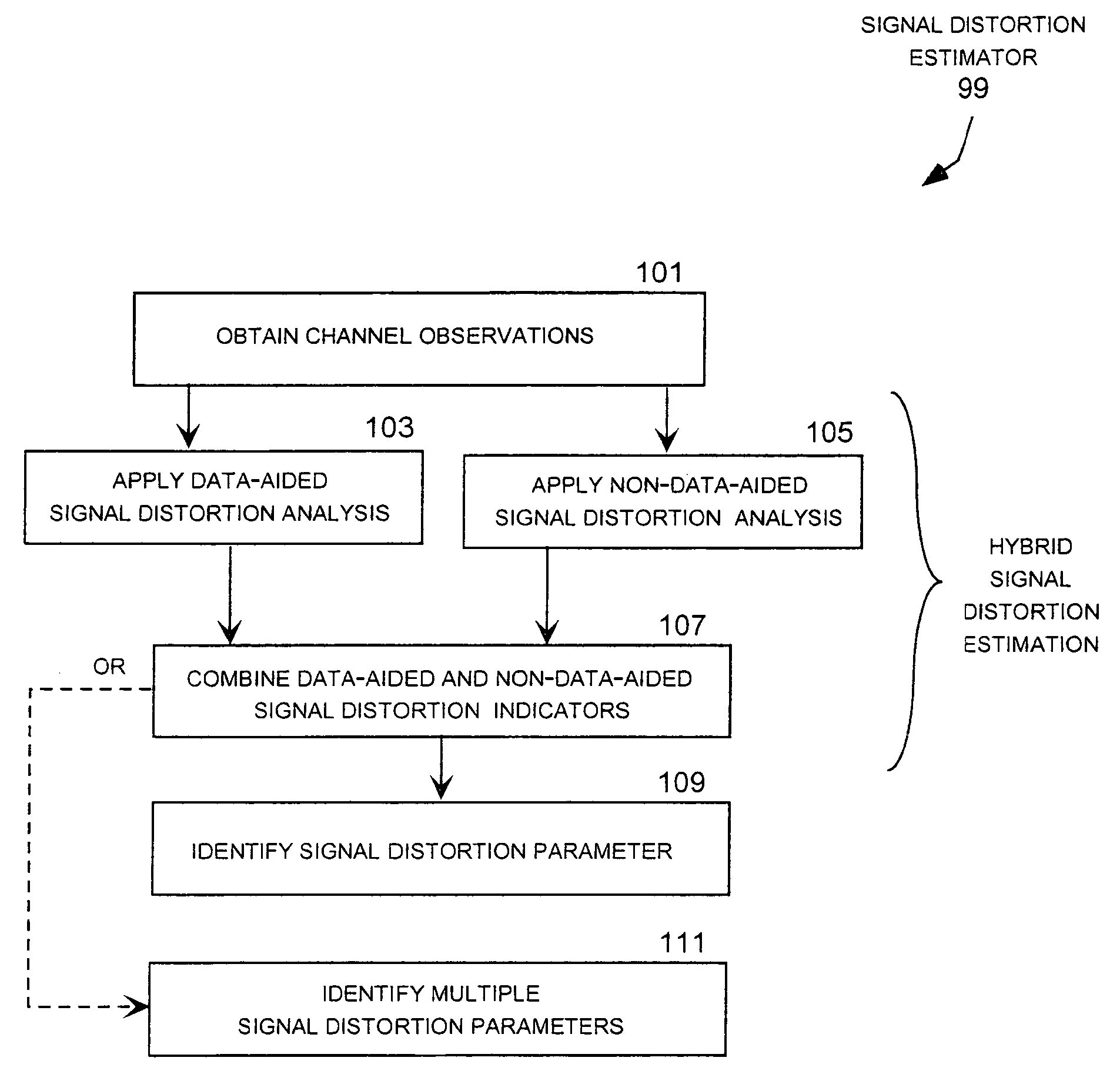

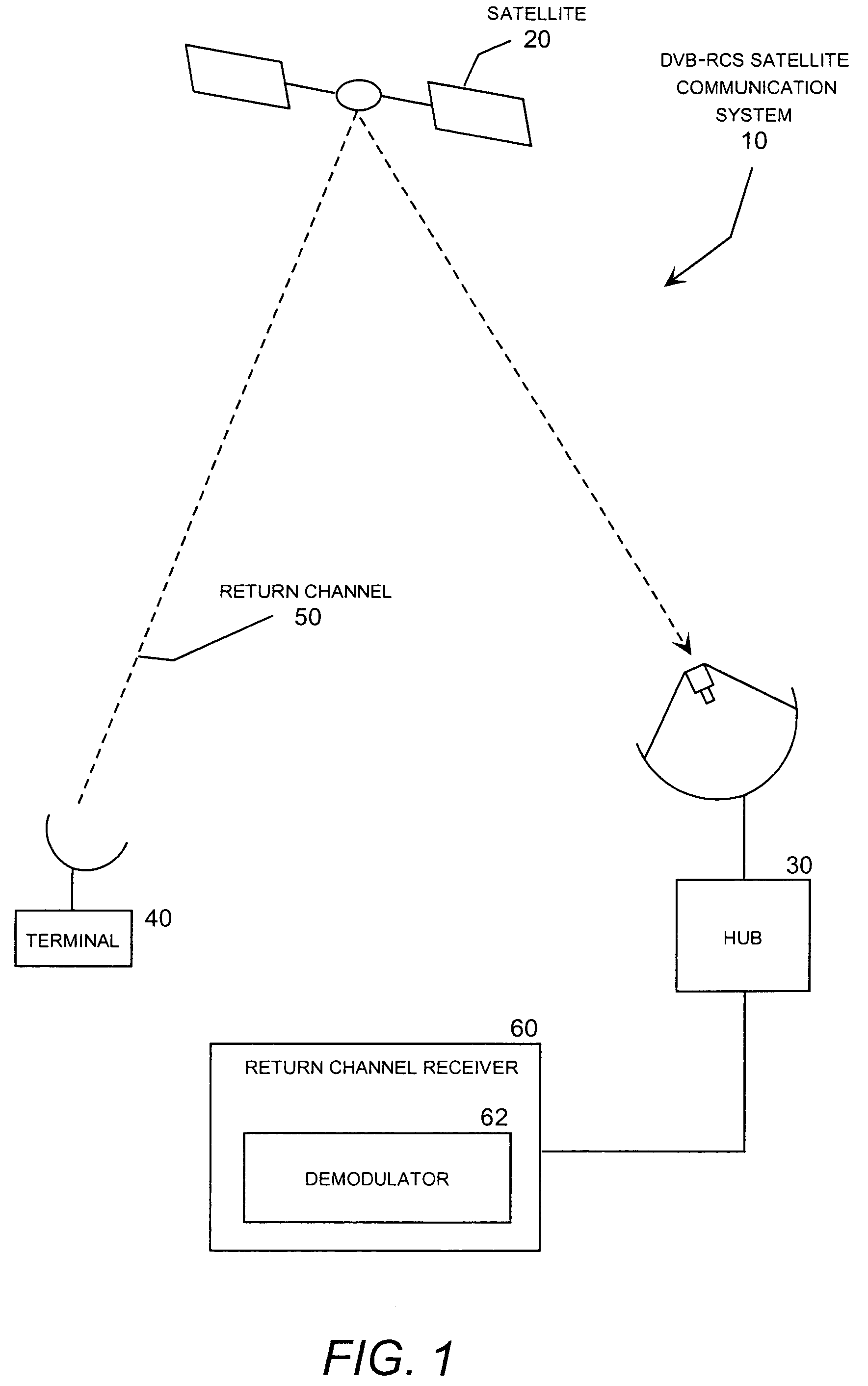

A hybrid carrier frequency offset estimator that uses data-aided and non-data-aided signal processing techniques to produce multiple candidates for the carrier frequency offset within a return channel receiver in a DVB-RCS system using turbo coding and quadrature phase shift keying (QPSK) data modulation. In this system, the invention is employed to estimate signal distortion caused by carrier frequency offset so that this particular source of signal distortion can be removed to improve the ability of the receiver to maintain synchronization in low signal-to-noise conditions. This, in turn, allows the receiver to meet the DVB-RCS performance target, measured in terms of packet loss ratio, in low signal-to-noise ratio conditions and in particular for burst-mode data transmission with a short data packet size.

Owner:ADVANTECH SATELLITE NETWORKS

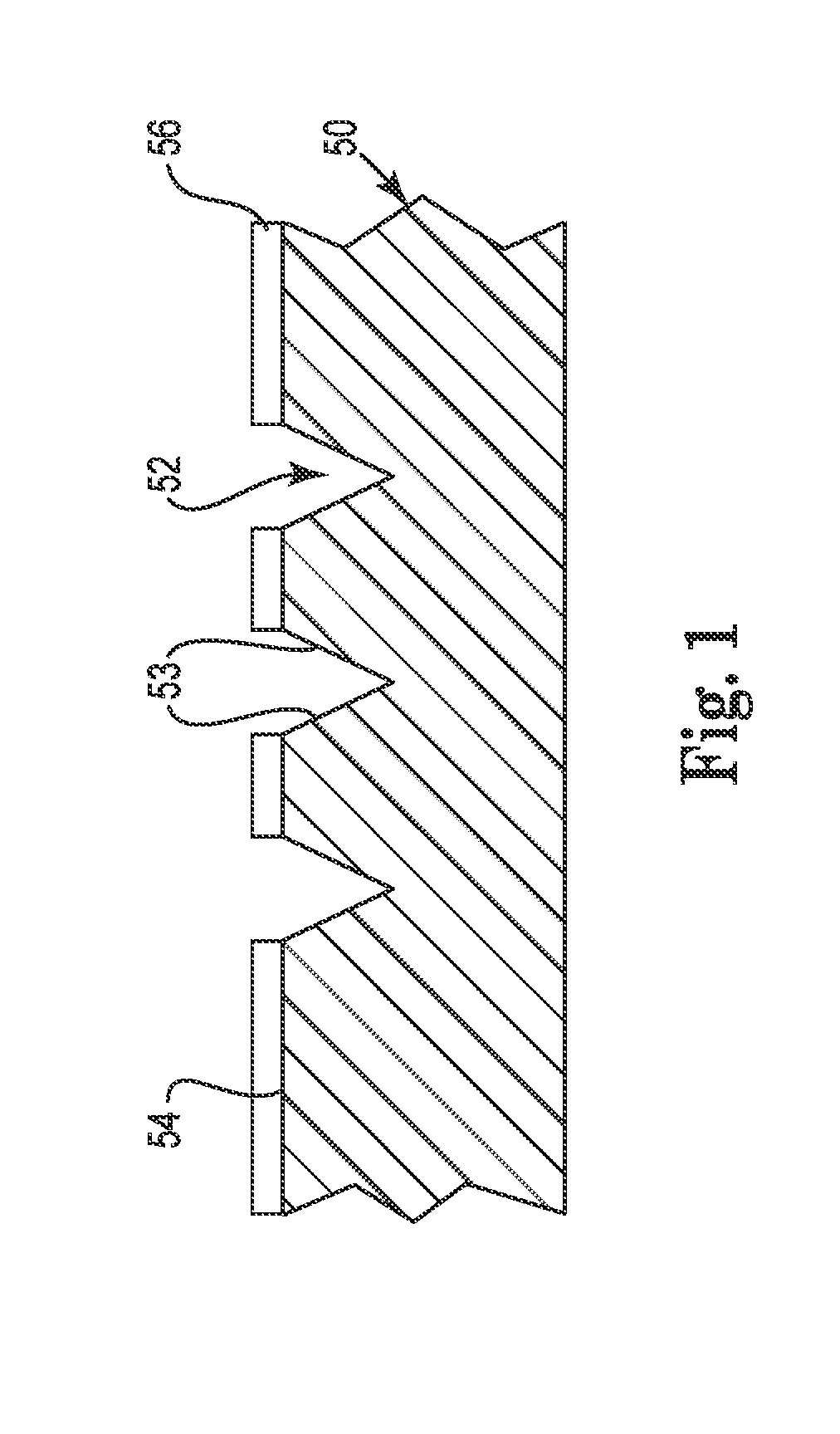

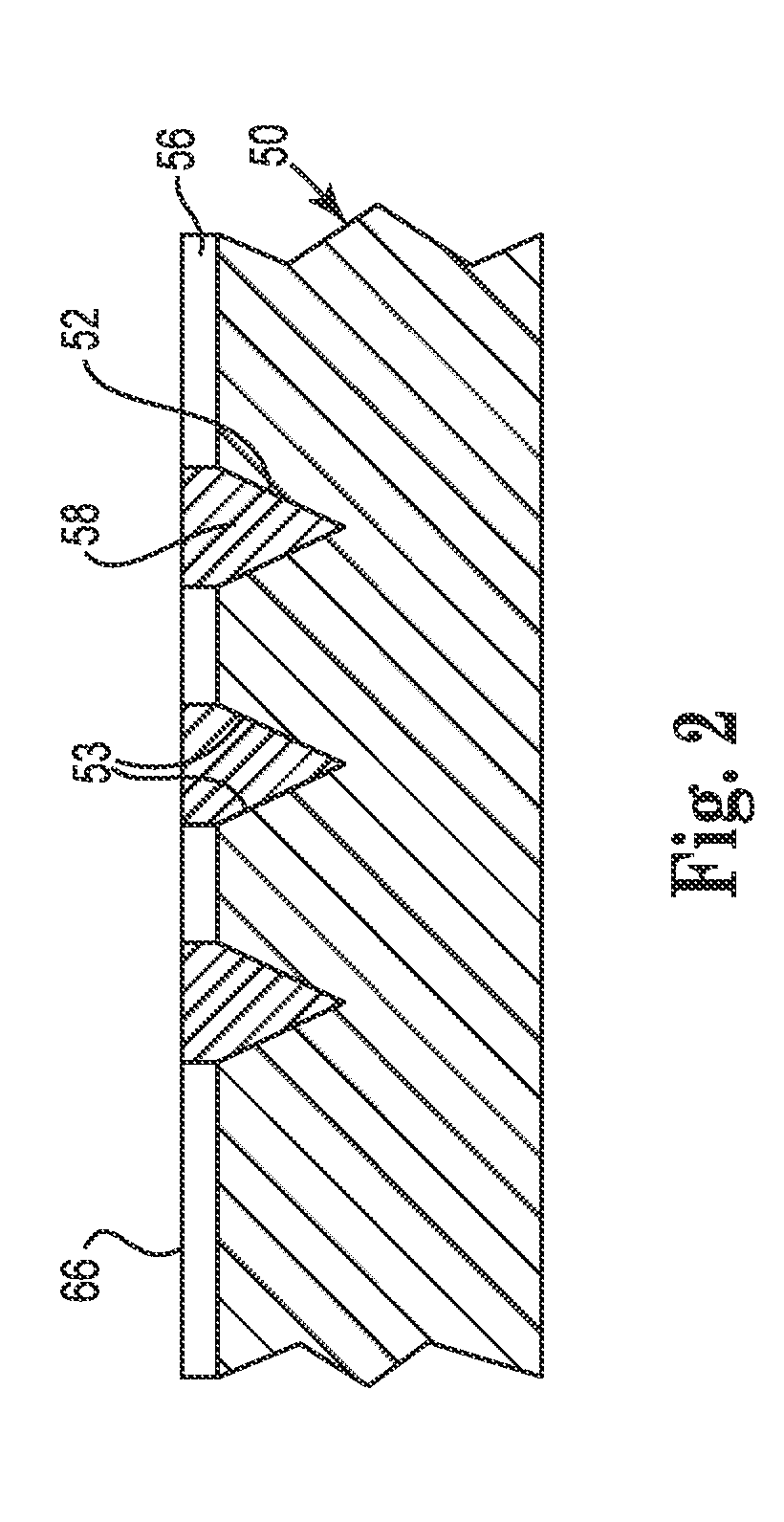

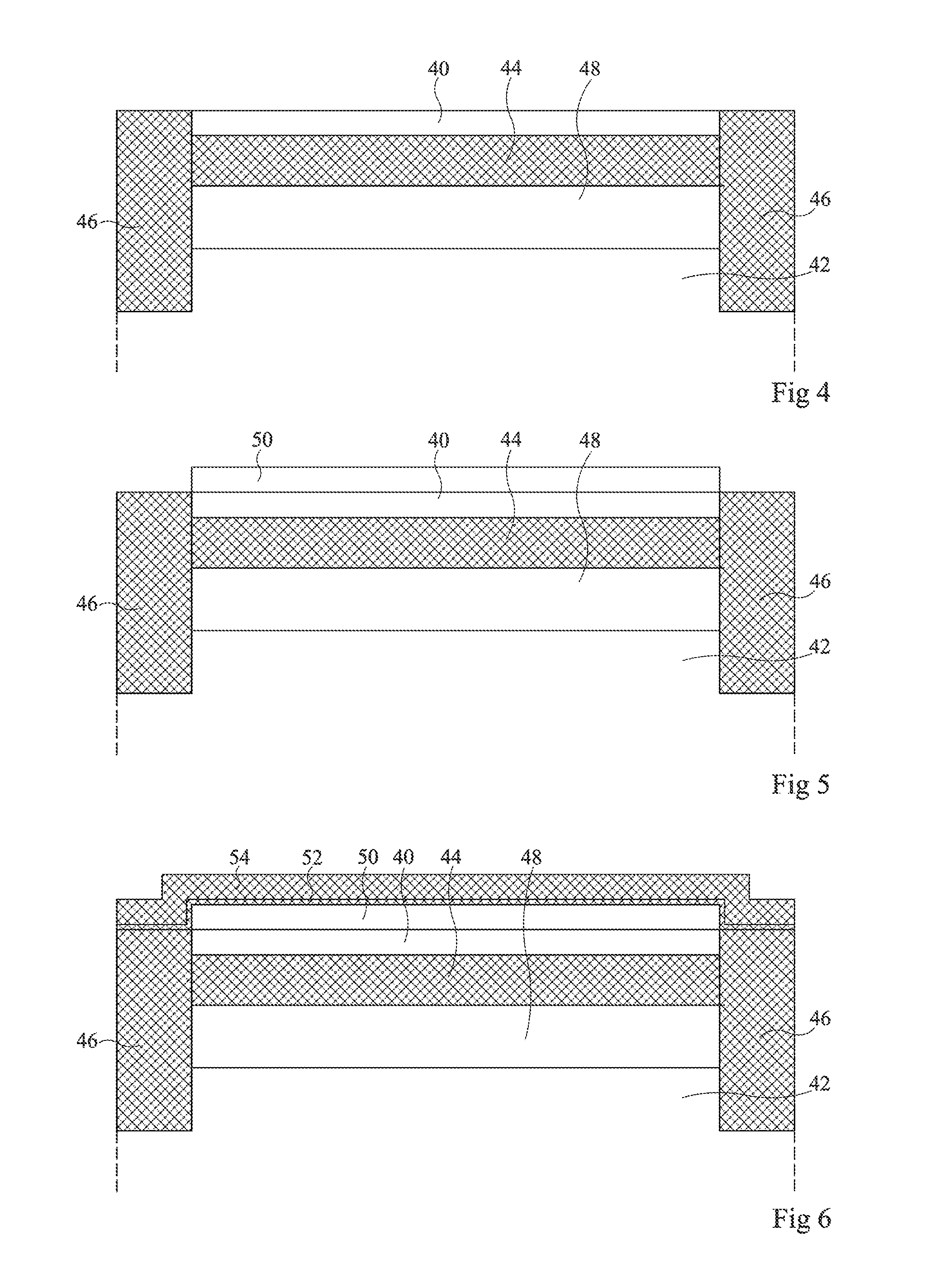

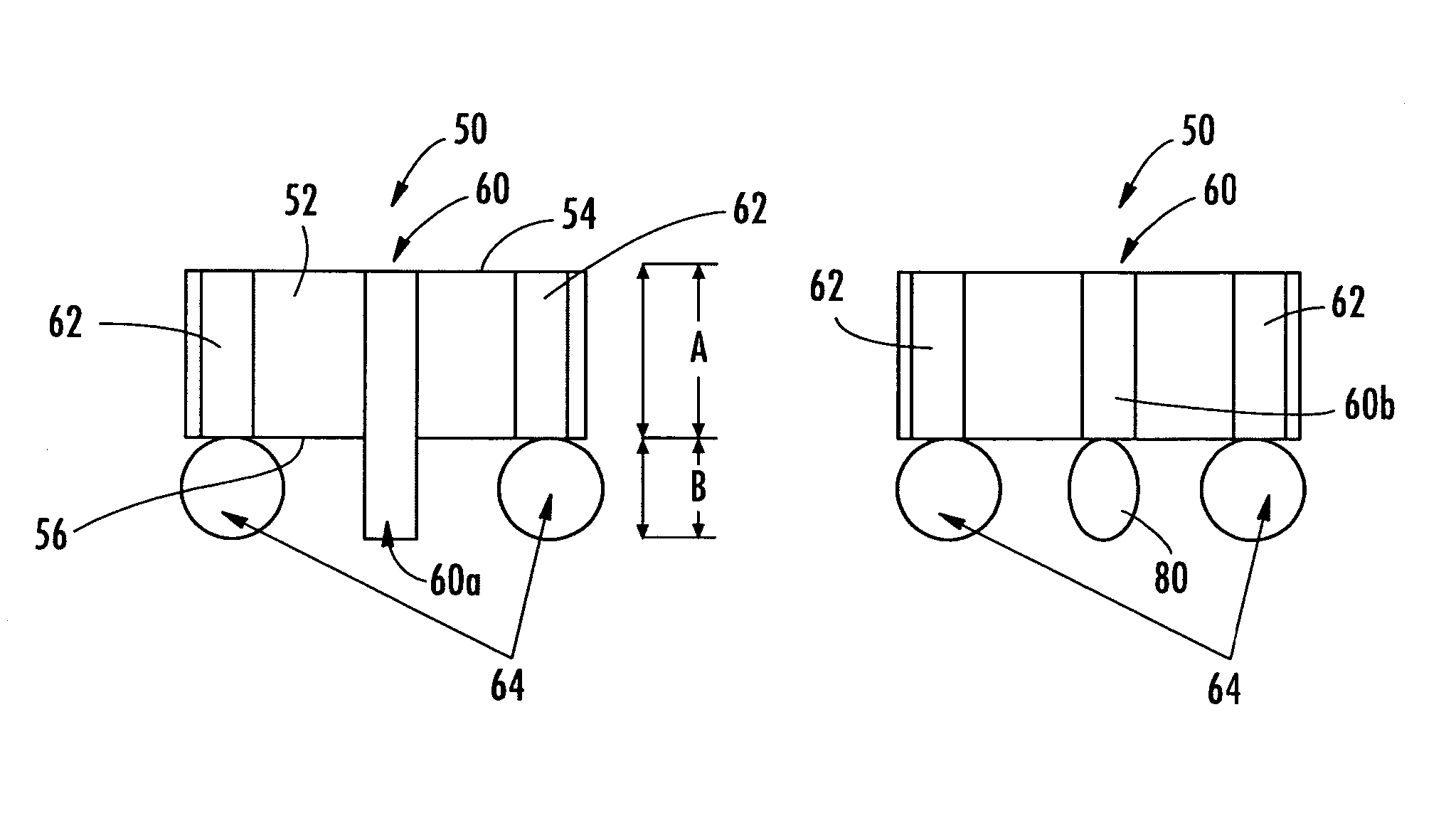

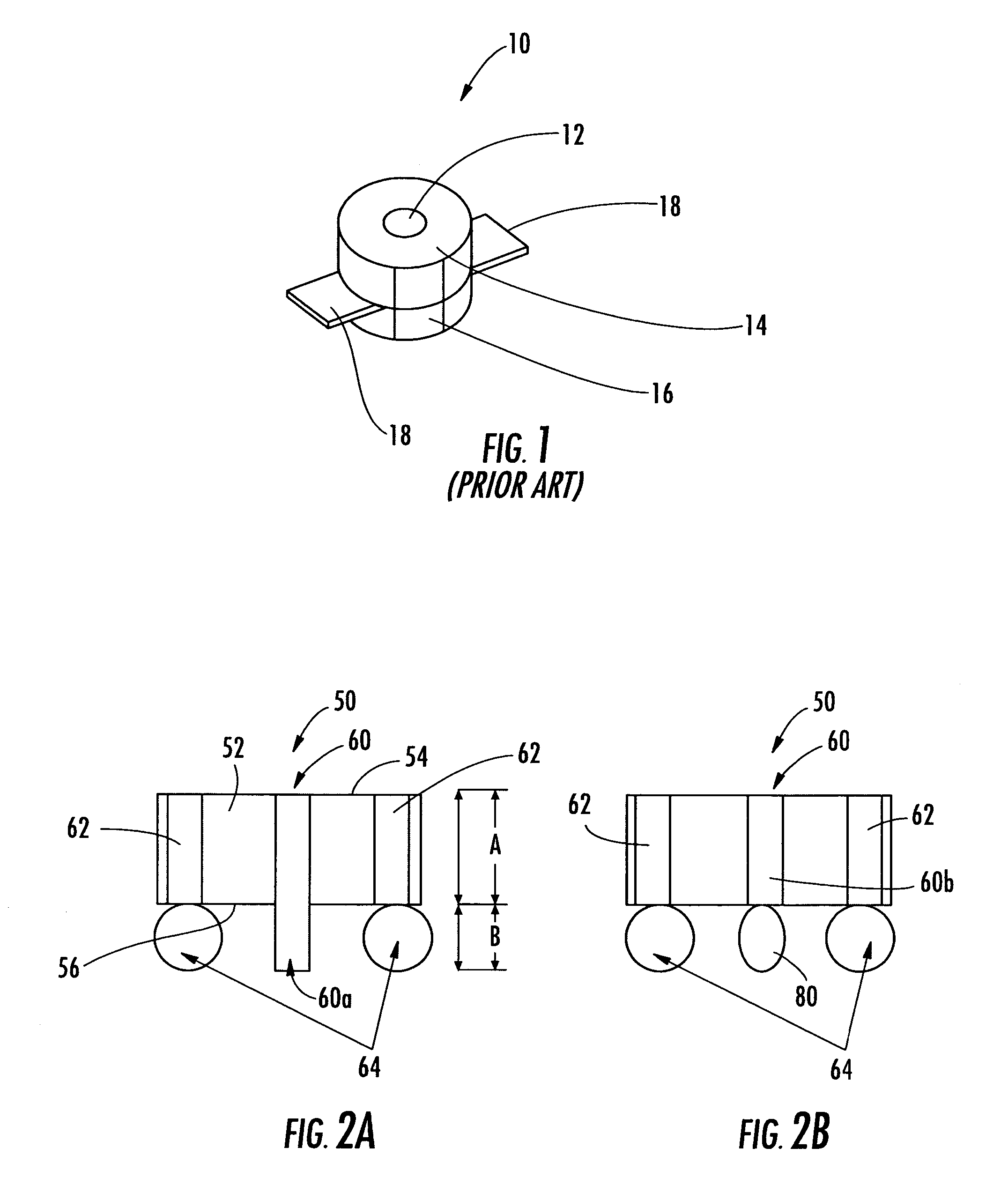

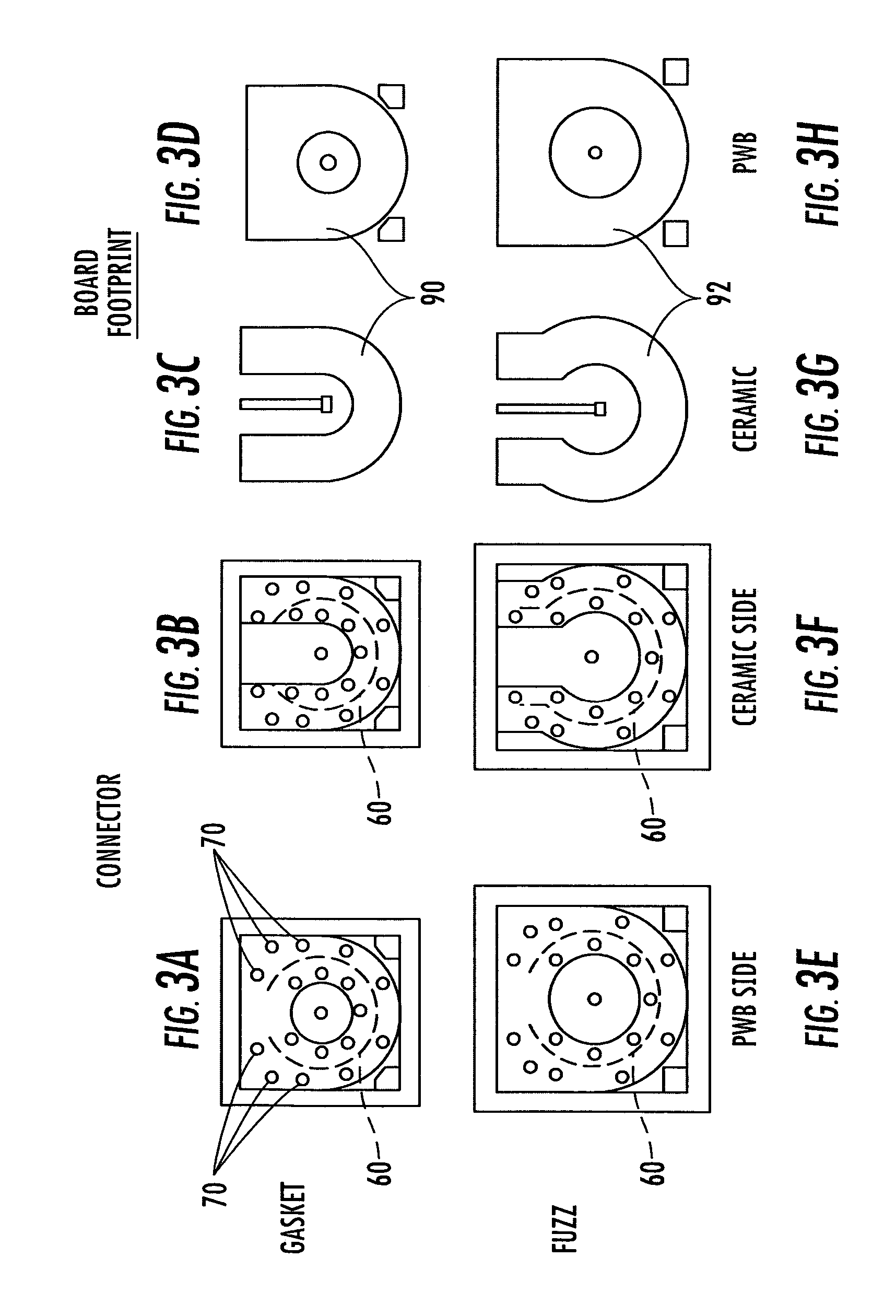

Singulated semiconductor device separable electrical interconnect

ActiveUS20120058653A1High performance test capabilityIncrease surface areaCoupling device connectionsElectrical measurement instrument detailsConductive materialsDielectric layer

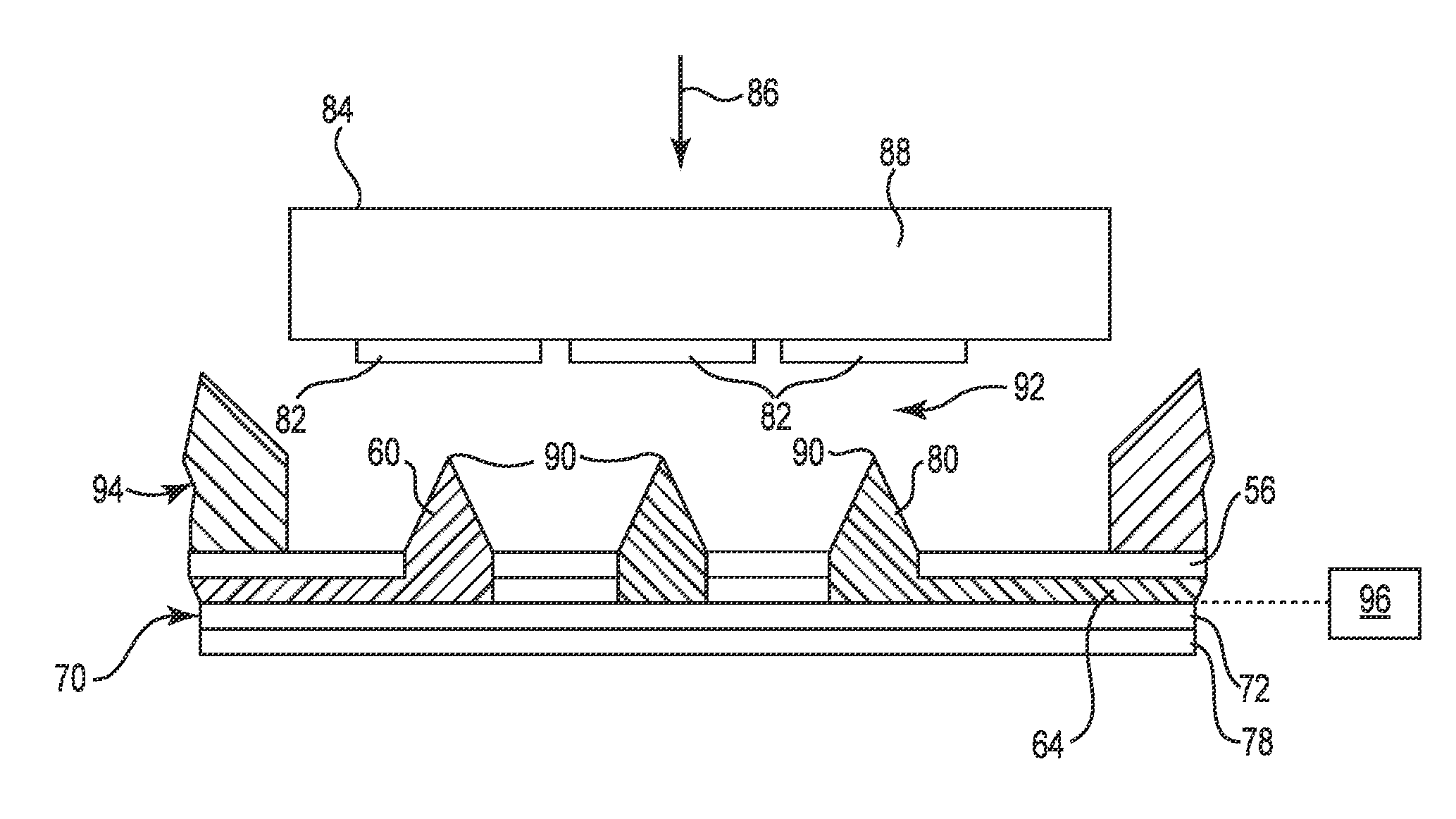

A socket assembly that forms a solderless electrical interconnection between terminals on a singulated integrated circuit device and another circuit member. The socket housing has an opening adapted to receive the singulated integrated circuit device. The compliant printed circuit is positioned relative to the socket housing to electrically couple with the terminals on a singulated integrated circuit device located in the opening. The compliant printed circuit includes a dielectric base layer printed onto a surface of a fixture, while leaving cavities in the surface of the fixture exposed. A plurality of contact members are formed in the plurality of cavities in the fixture and coupled to the dielectric base layer. The contact members are exposed wherein the compliant printed circuit is removed from the fixture. At least one dielectric layer with recesses corresponding to a target circuit geometry is printed on the dielectric base layer. A conductive material is deposited in at least a portion of the recesses to form conductive traces electrically coupling the contact members to the other circuit member.

Owner:HSIO TECH

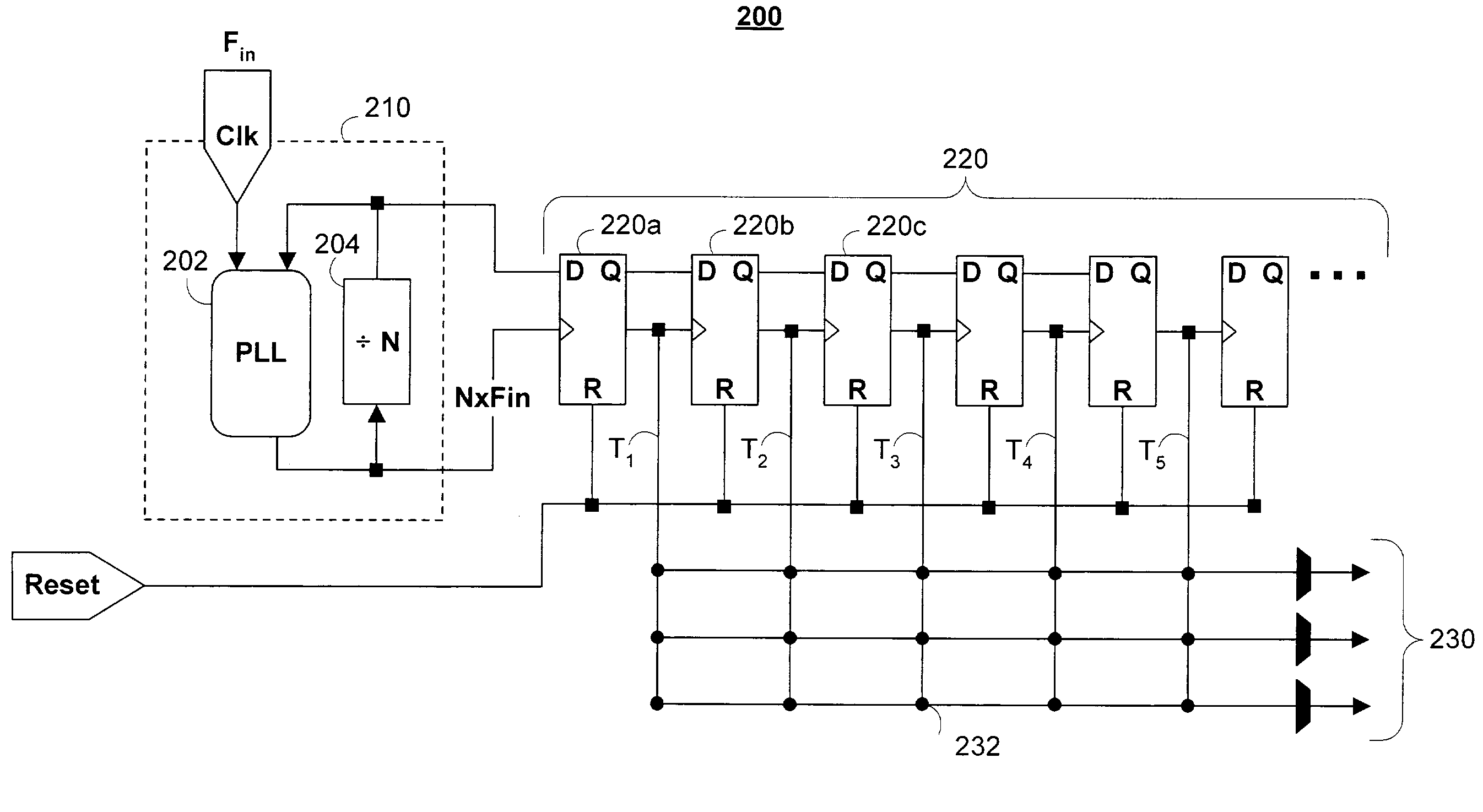

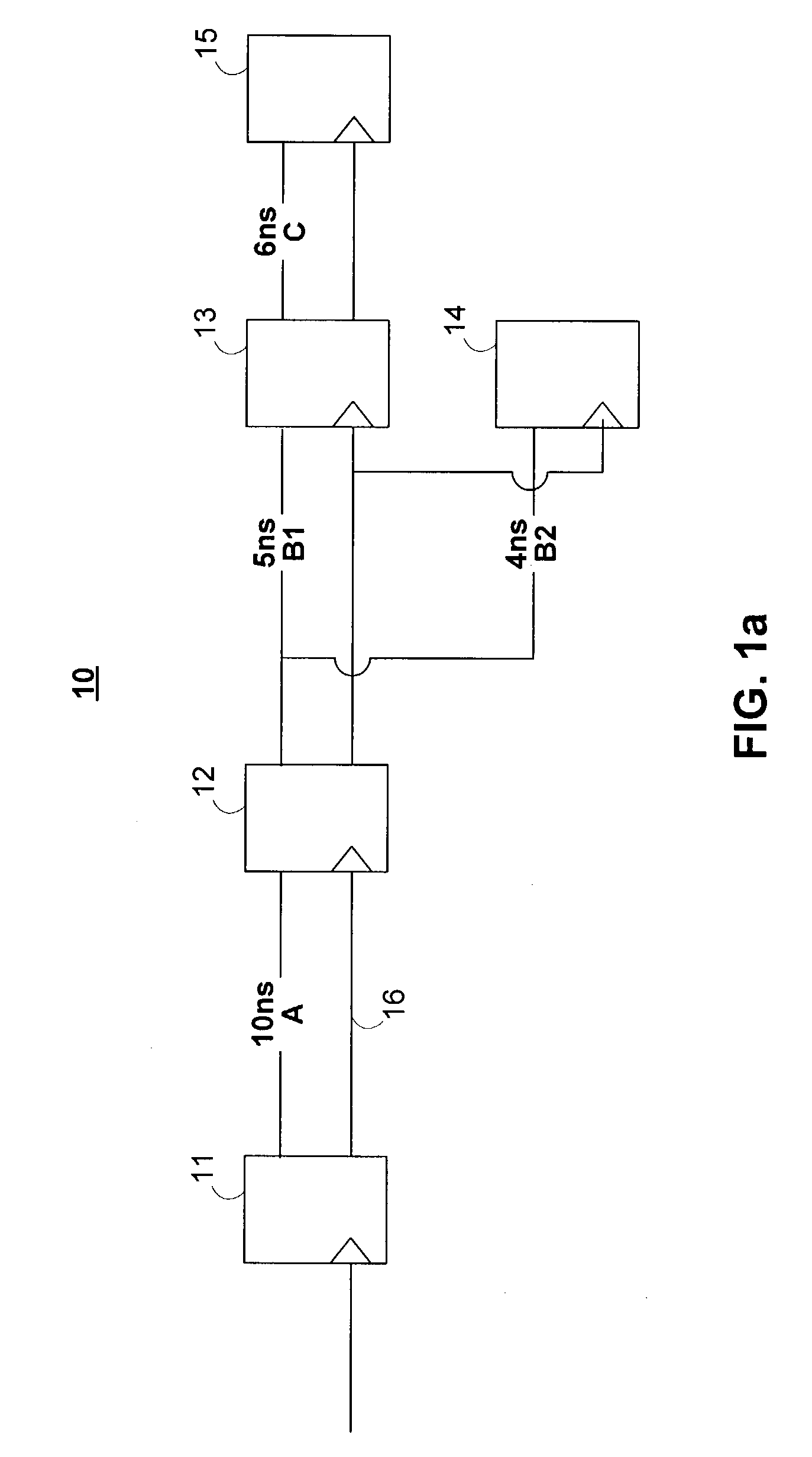

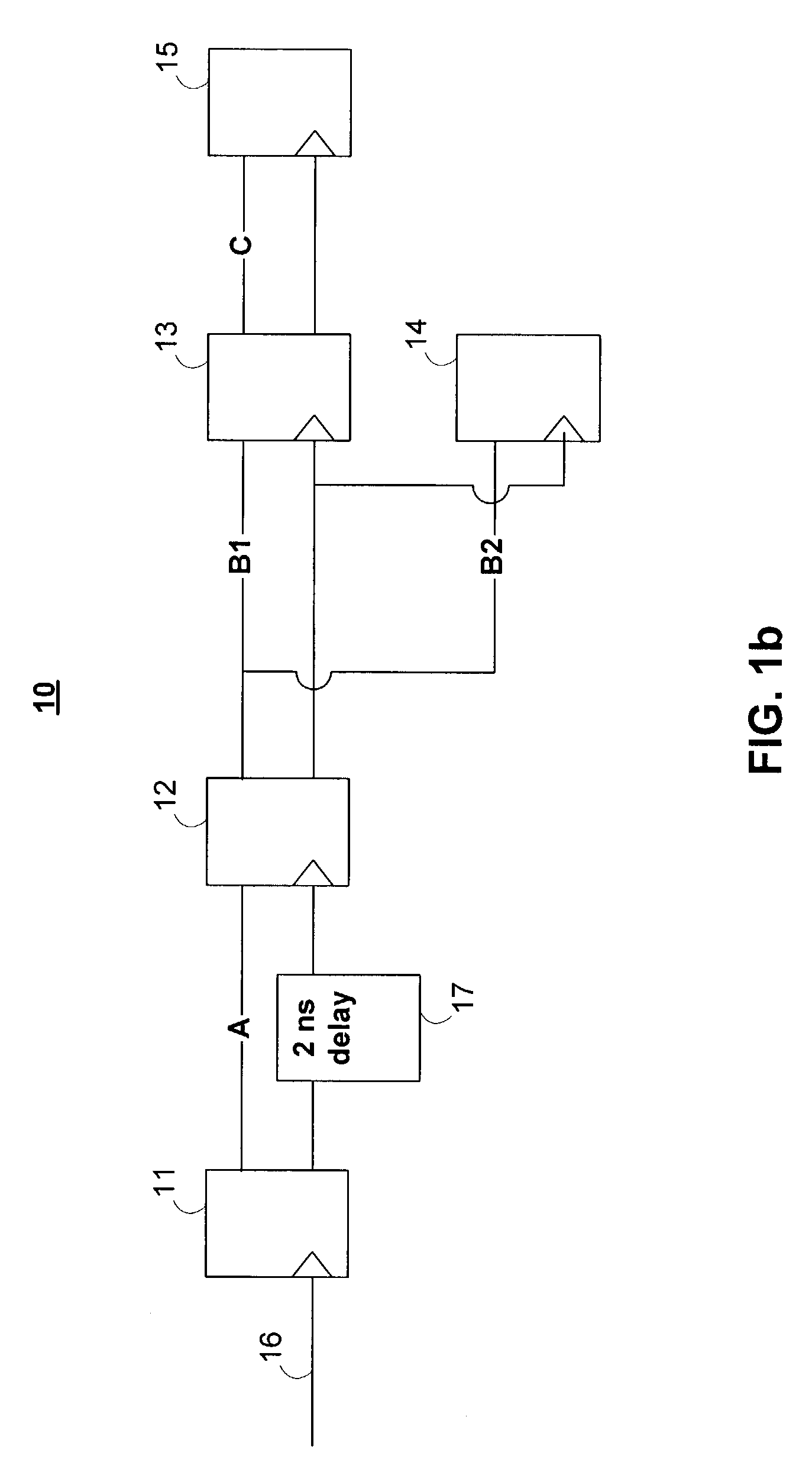

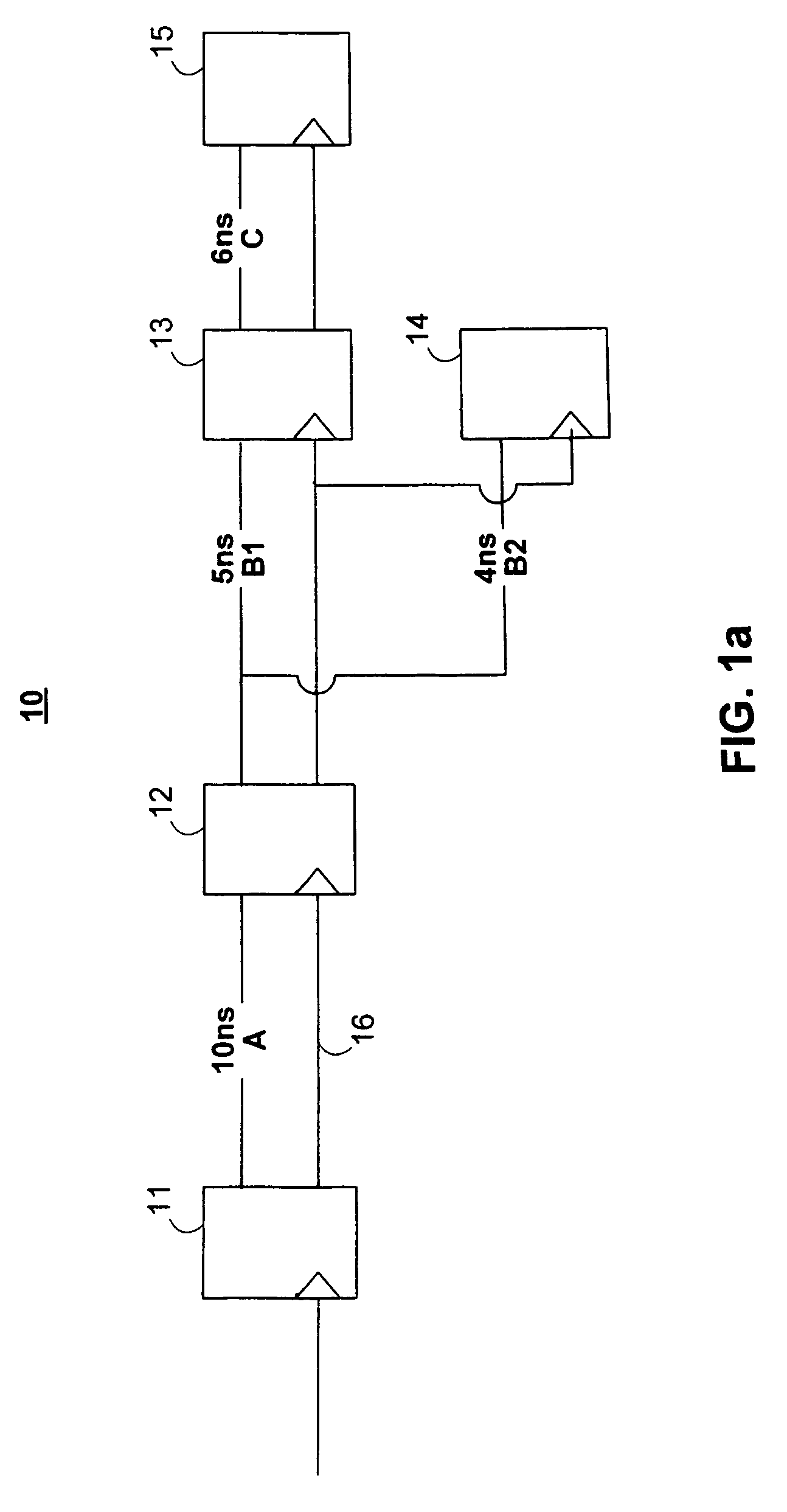

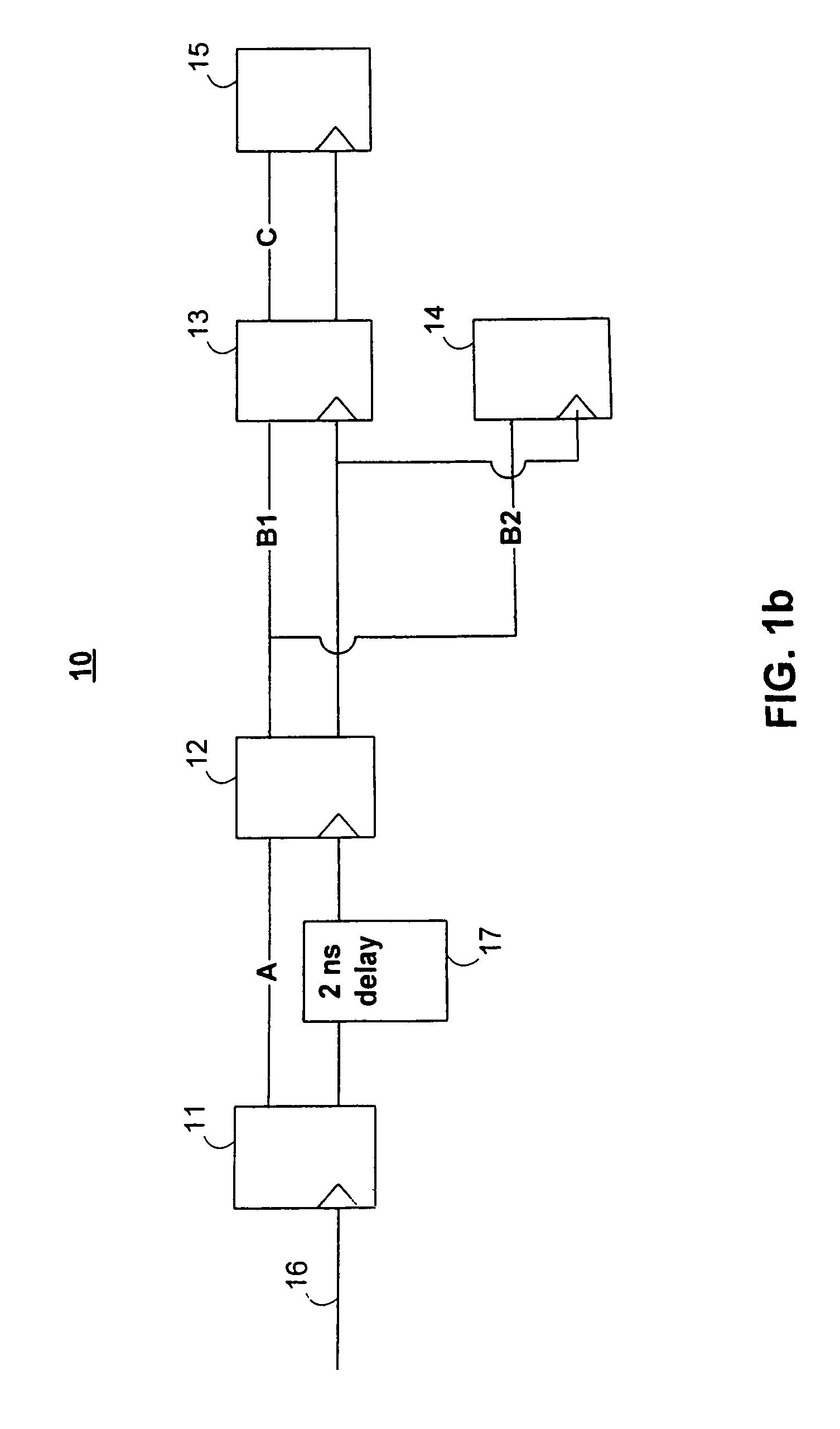

Programmable logic devices with skewed clocking signals

InactiveUS7107477B1Architecture be enhanceImprove performanceError detection/correctionData resettingProgrammable logic deviceCLOCK

A programmable logic device has programmable phase-shifting circuitry. The phase-shifting circuitry is used to generate a set of skewed clock signals that is used to adjust the relative timing of device elements in a circuit synthesized in the programmable logic device. By suitably adjusting the relative timing of the device elements, the circuit critical path lengths are effectively reduced leading to improved circuit frequency performance. Algorithms are provided for establishing clock skew values that lead to improved circuit performance. The algorithms are incorporated in computer aided design tools to enable automatic optimization of circuit designs.

Owner:ALTERA CORP

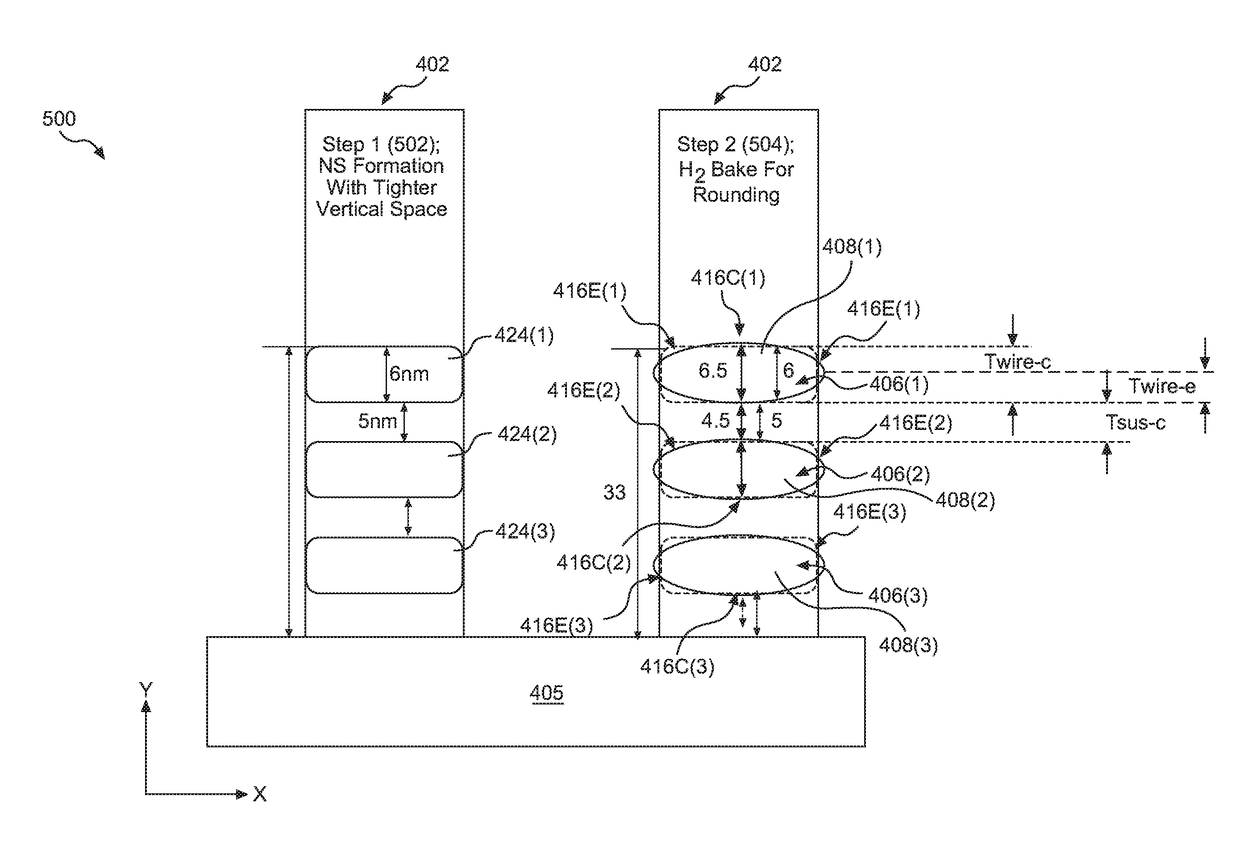

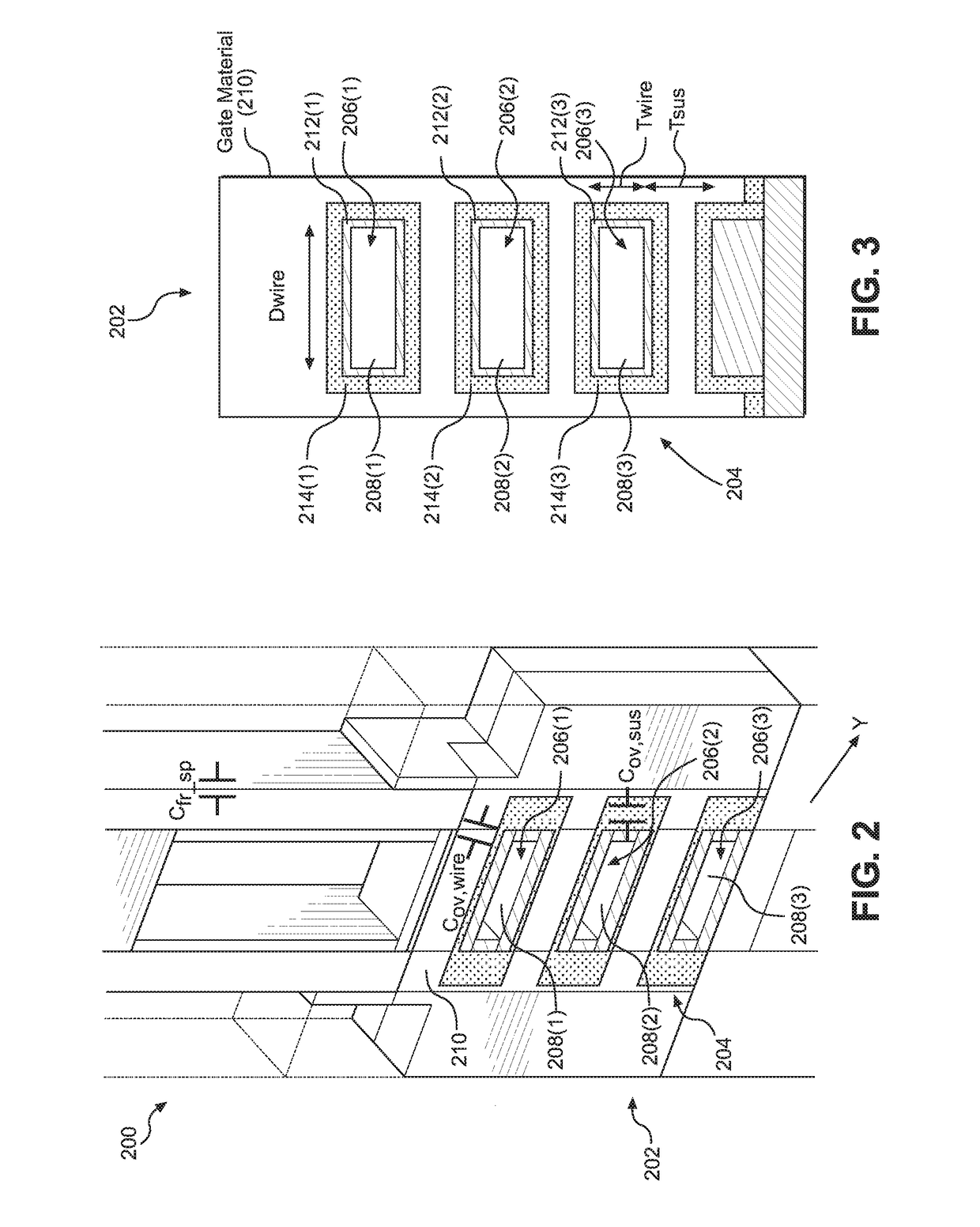

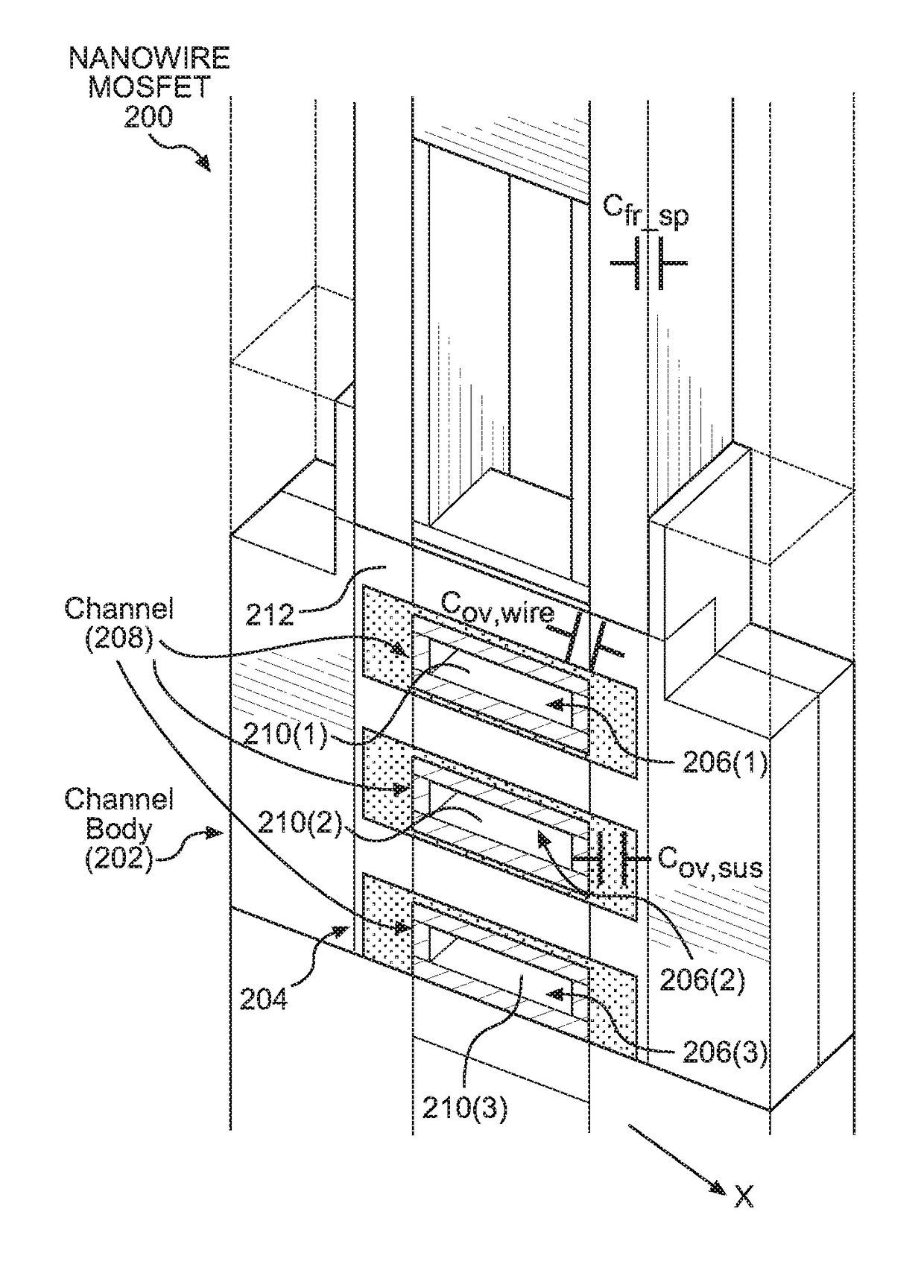

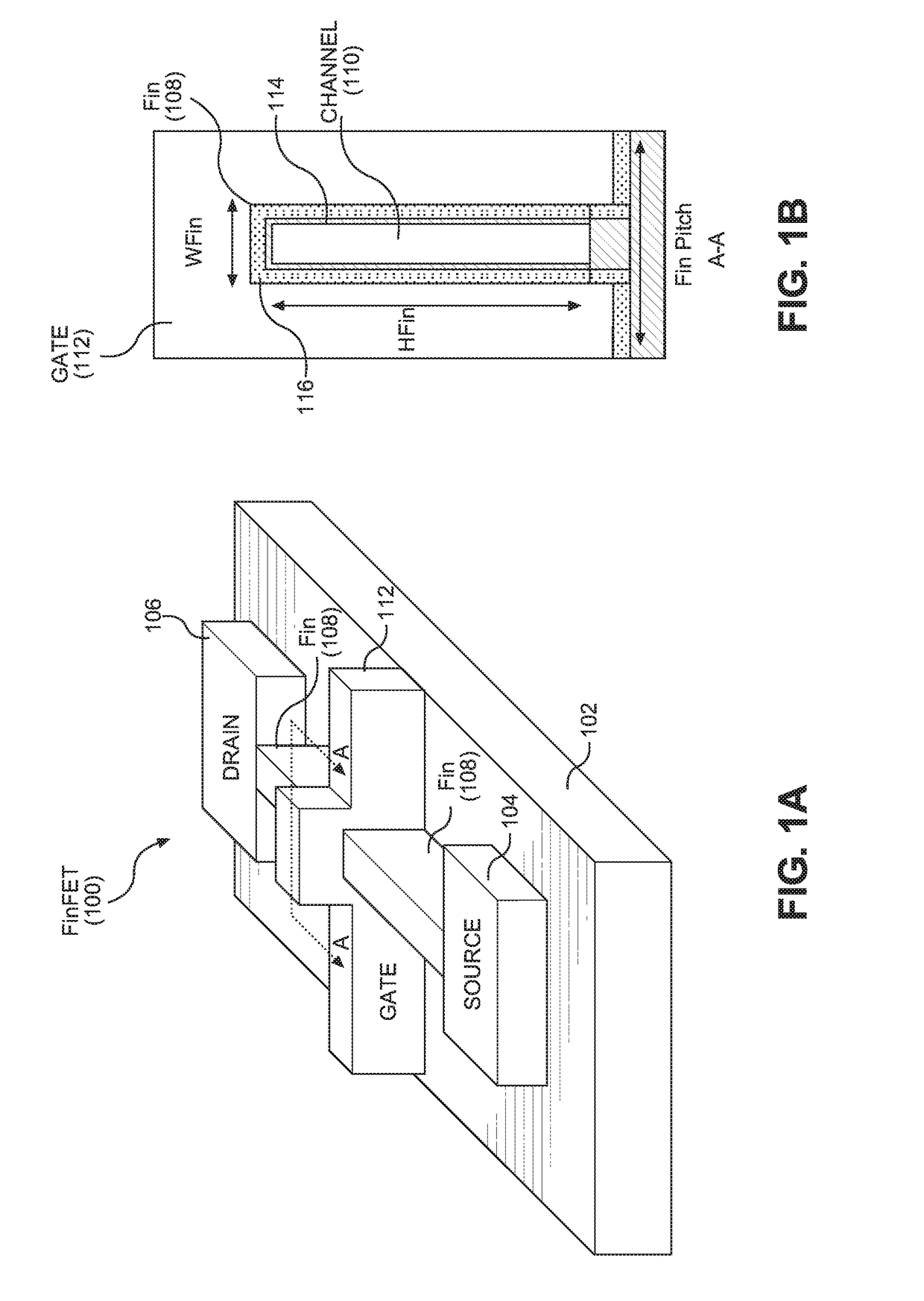

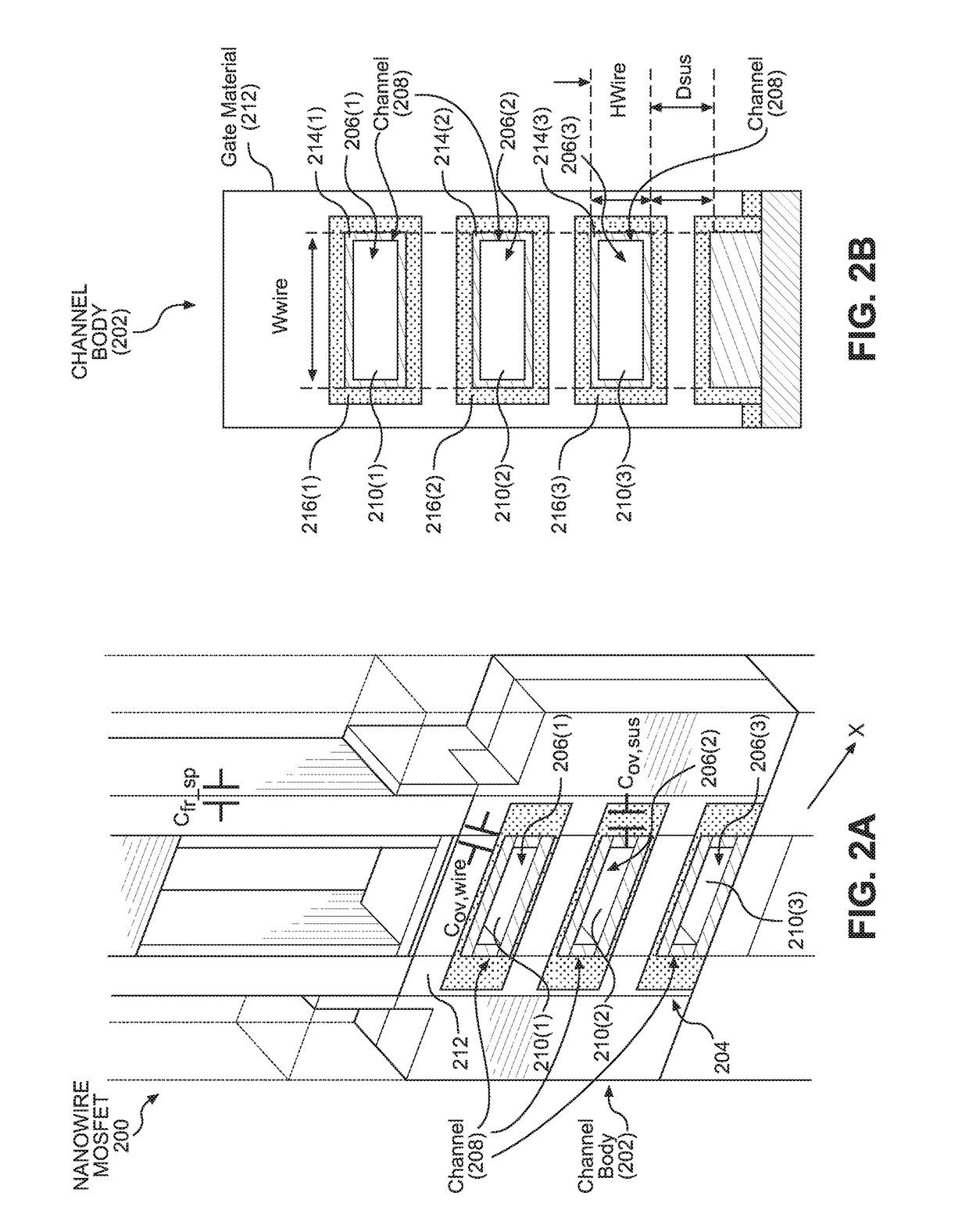

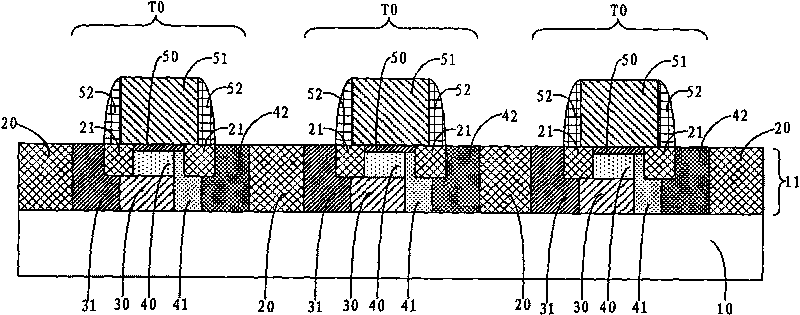

NANOWIRE METAL-OXIDE SEMICONDUCTOR (MOS) FIELD-EFFECT TRANSISTORS (FETs) (MOSFETs) EMPLOYING A NANOWIRE CHANNEL STRUCTURE HAVING ROUNDED NANOWIRE STRUCTURES

InactiveUS20170170268A1Reduce distanceSmall channel lengthTransistorSolid-state devicesMOSFETNanowire

Nanowire metal-oxide semiconductor (MOS) Field-Effect Transistors (FETs) (MOSFETs) employing a nanowire channel structure having rounded nanowire structures is disclosed. To reduce the distance between adjacent nanowire structures to reduce parasitic capacitance while providing sufficient gate control of the channel, the nanowire channel structure employs rounded nanowire structures. For example, the rounded nanowire structures provide for a decreased height from a center area of the rounded nanowire structures to end areas of the rounded nanowire structures. Gate material is disposed around rounded ends of the rounded nanowire structures to extend into a portion of separation areas between adjacent nanowire structures. The gate material extends in the separation areas between adjacent nanowire structures sufficient to create a fringing field to the channel where gate material is not adjacently disposed, to provide strong gate control of the channel even though gate material does not completely surround the rounded nanowire structures.

Owner:QUALCOMM INC

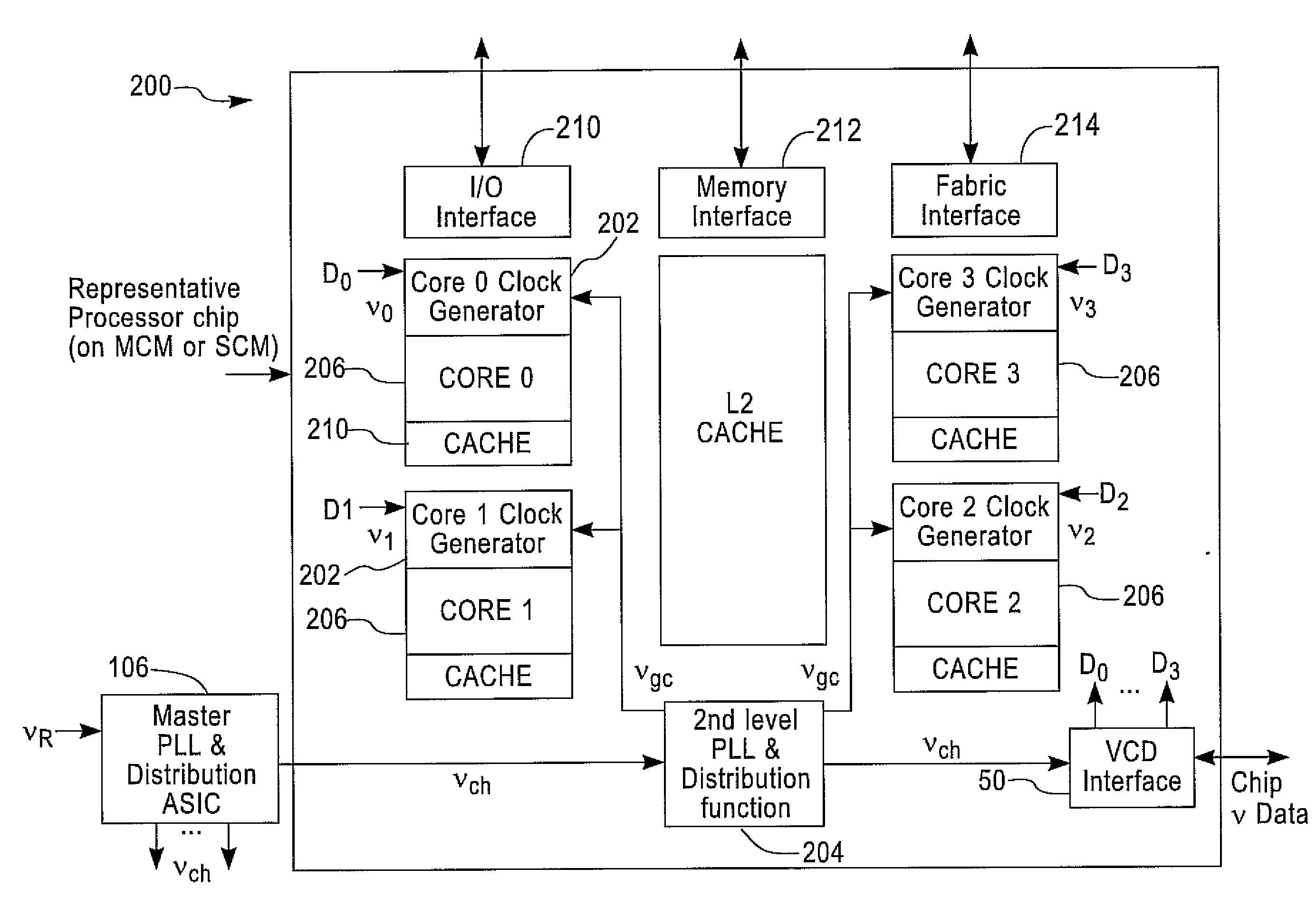

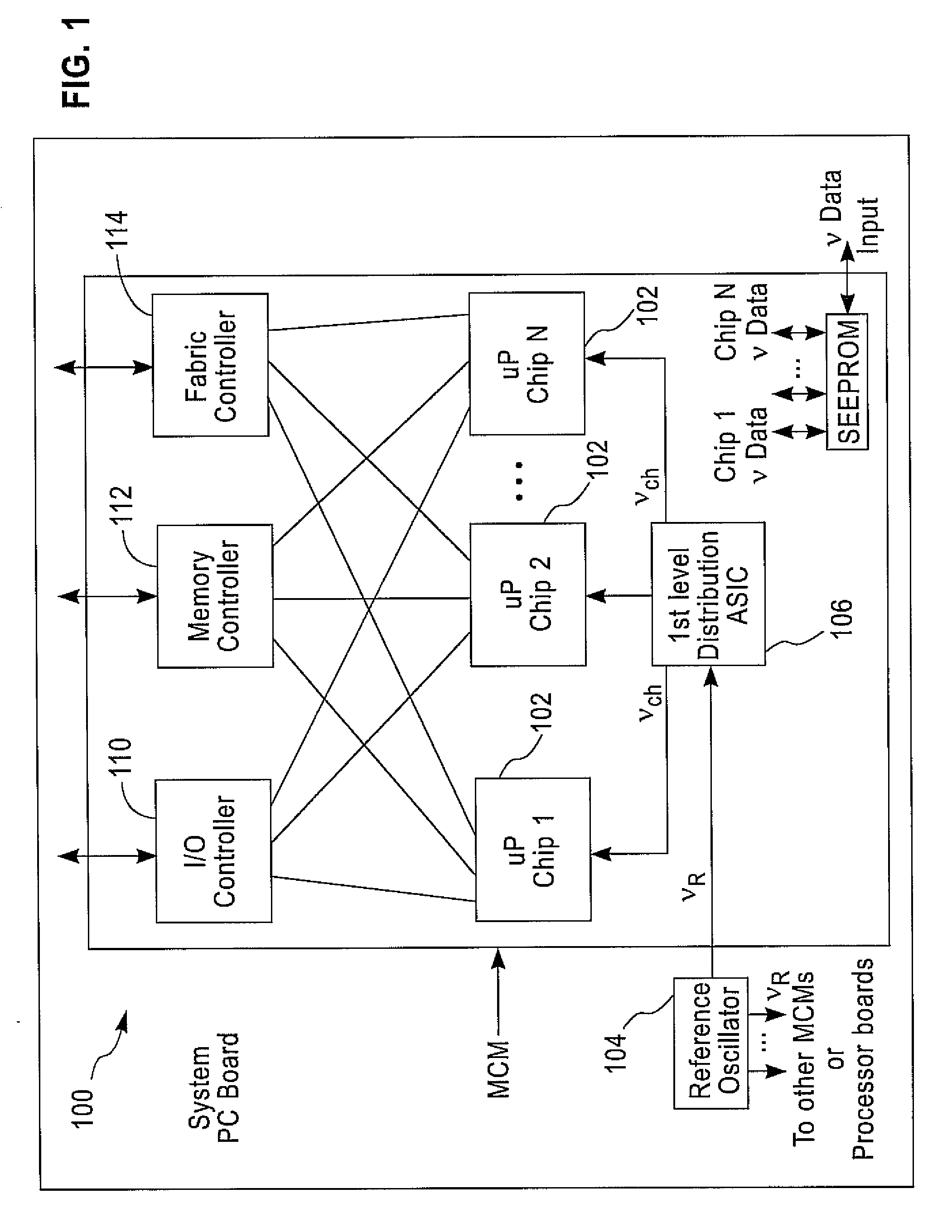

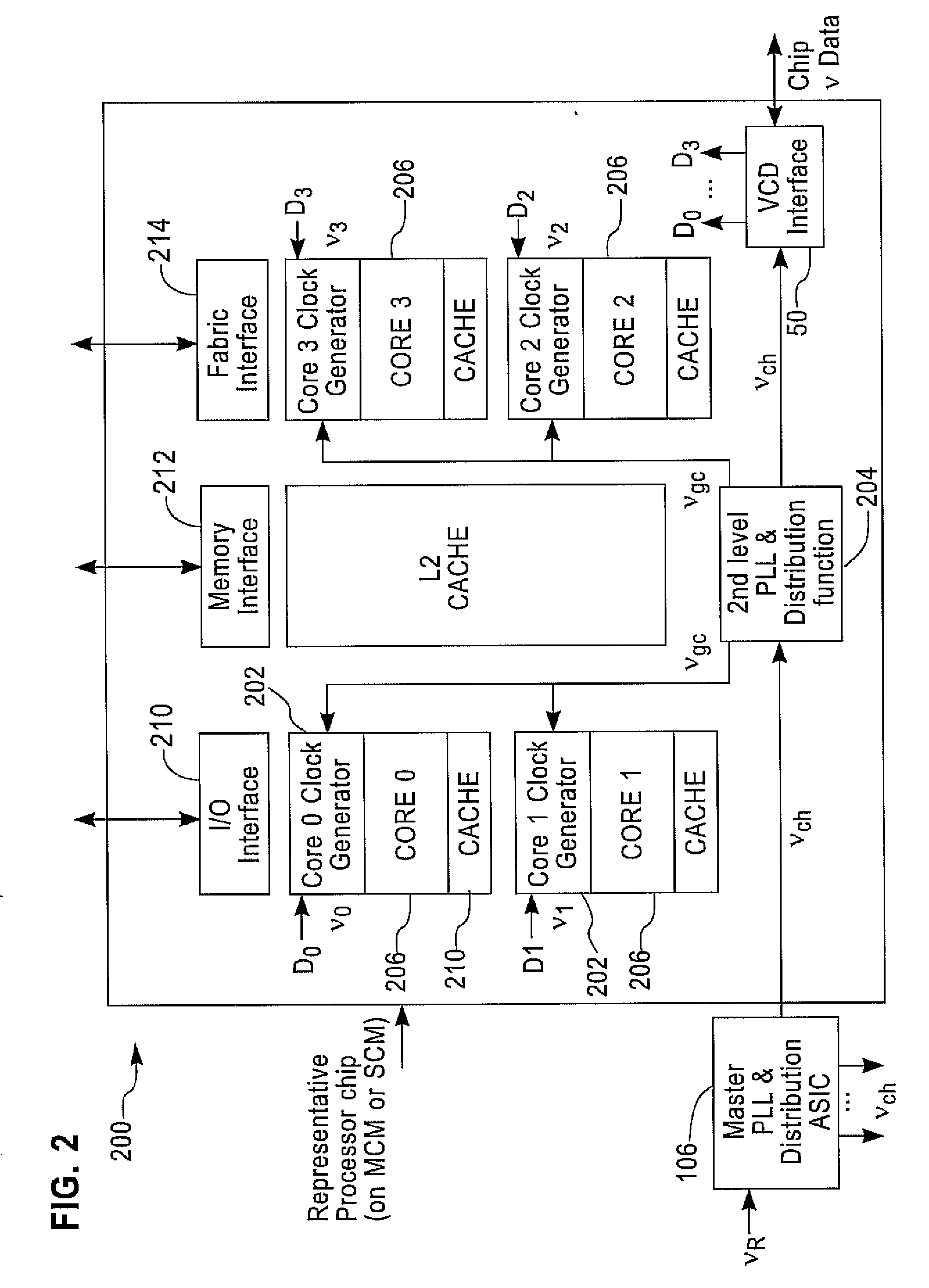

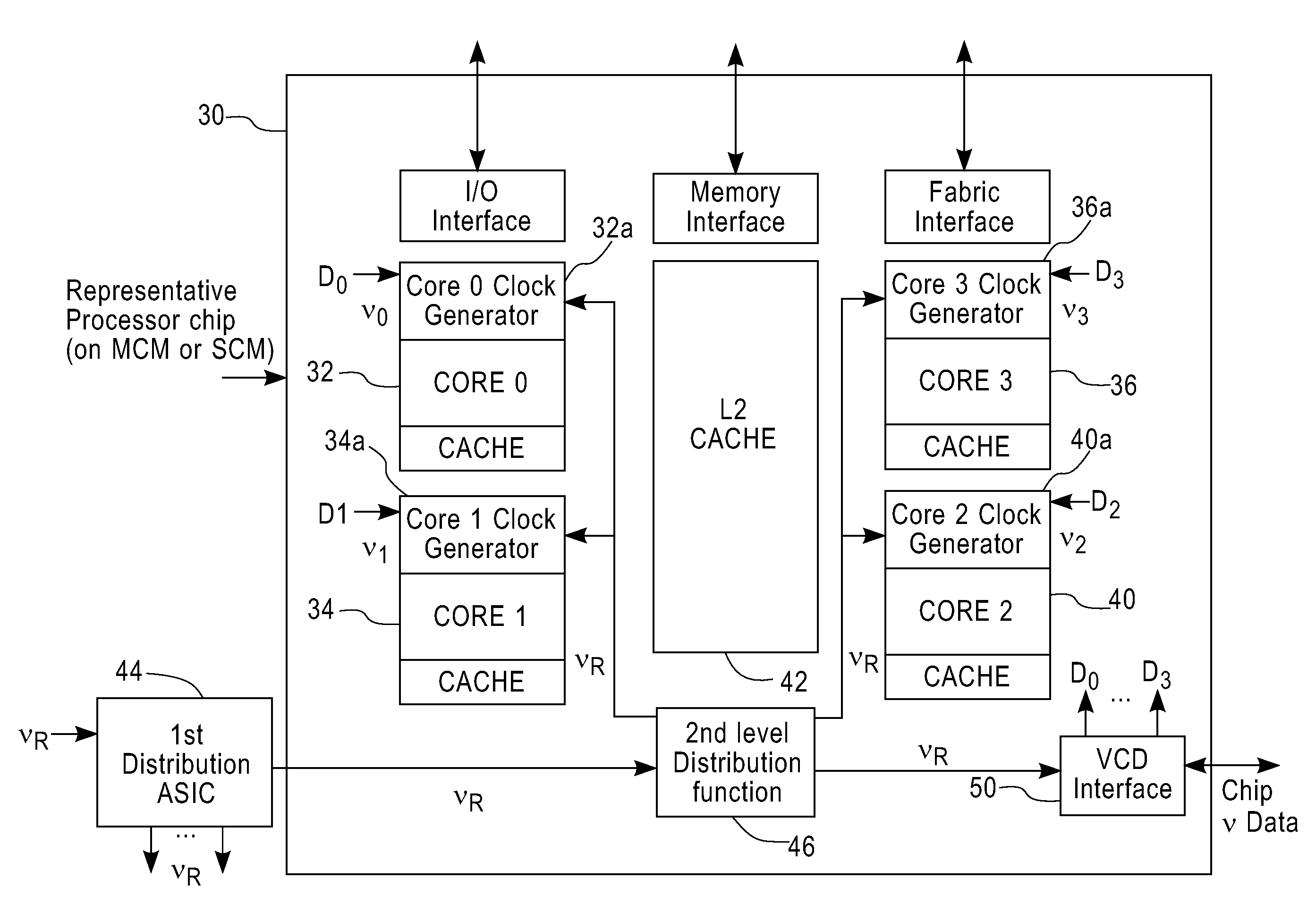

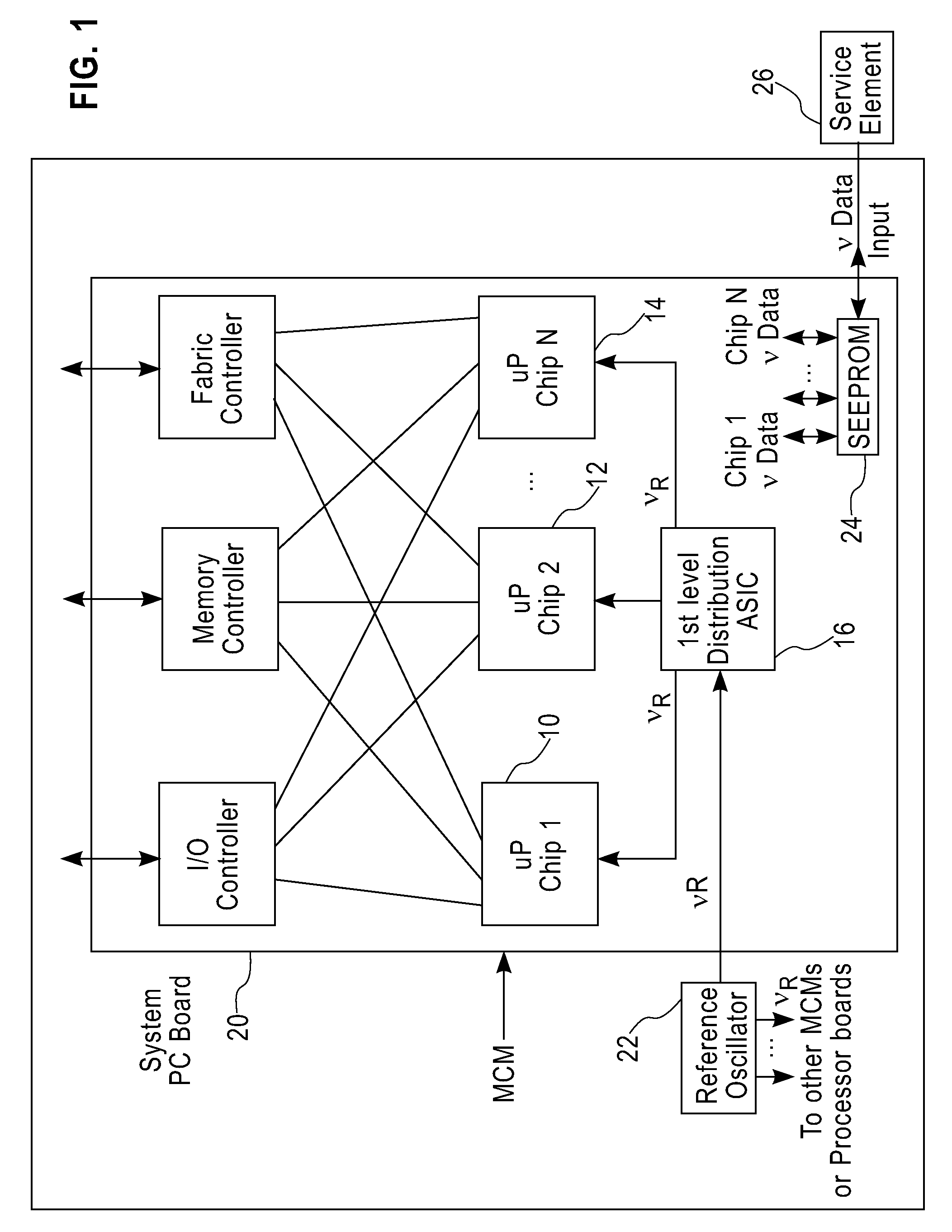

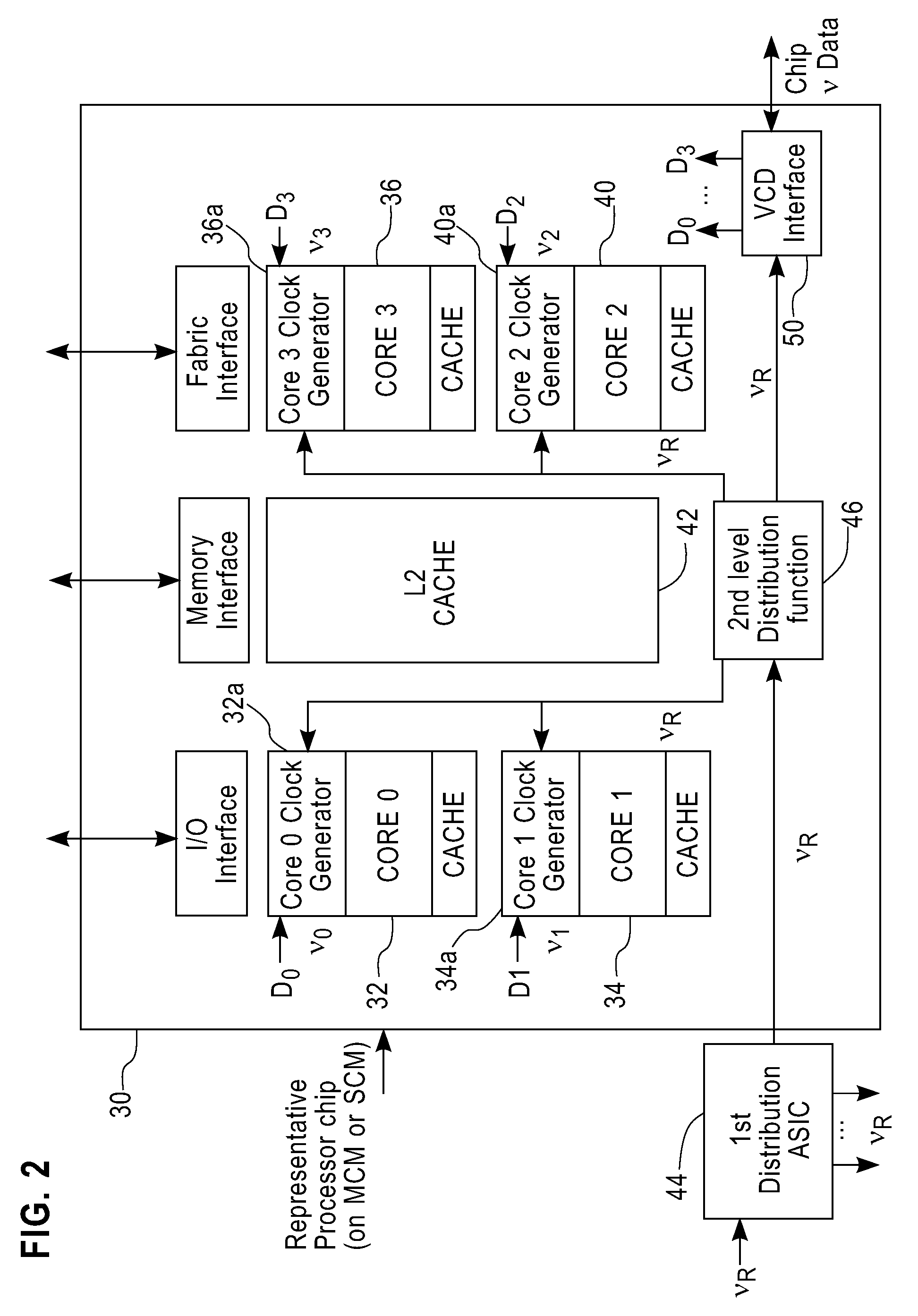

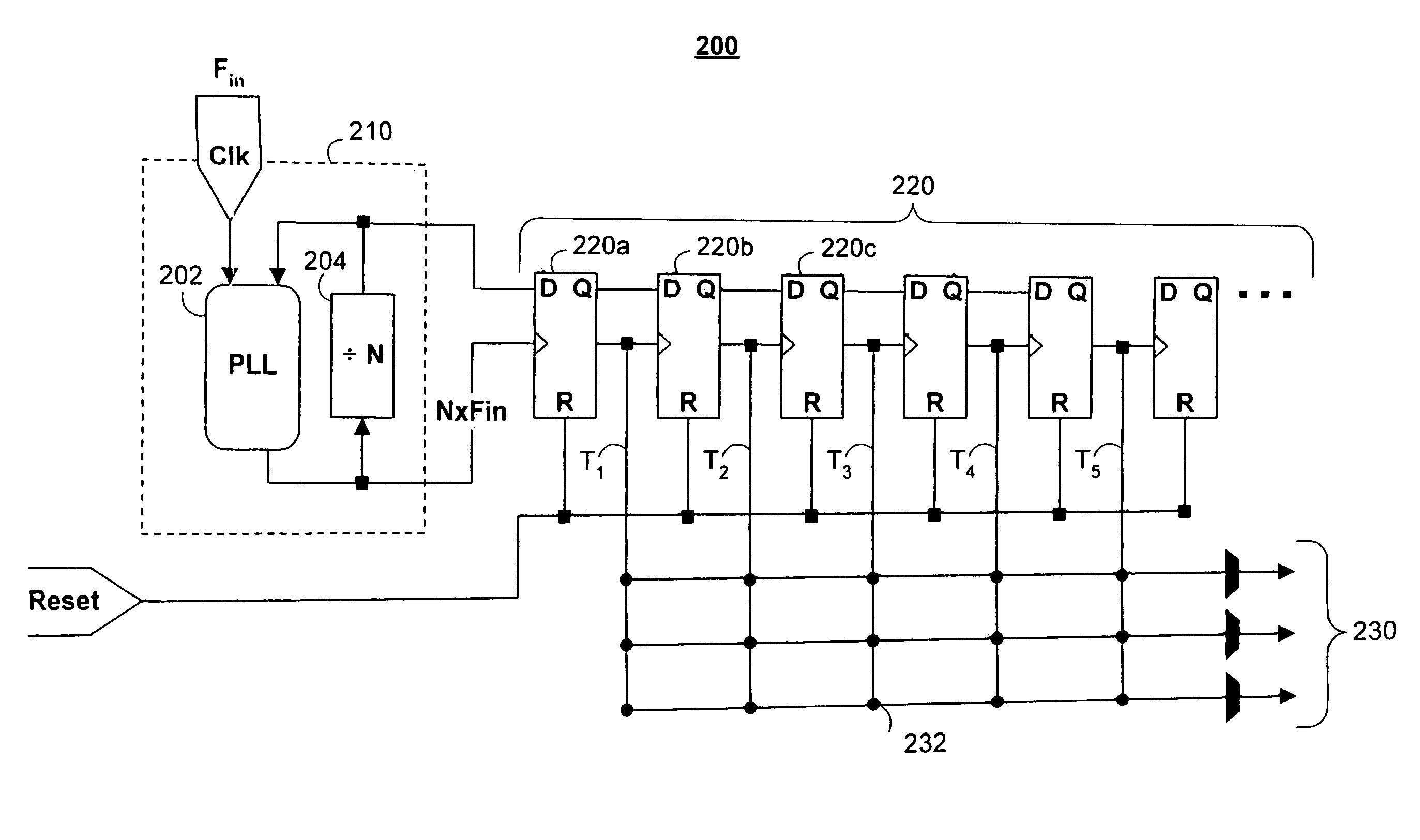

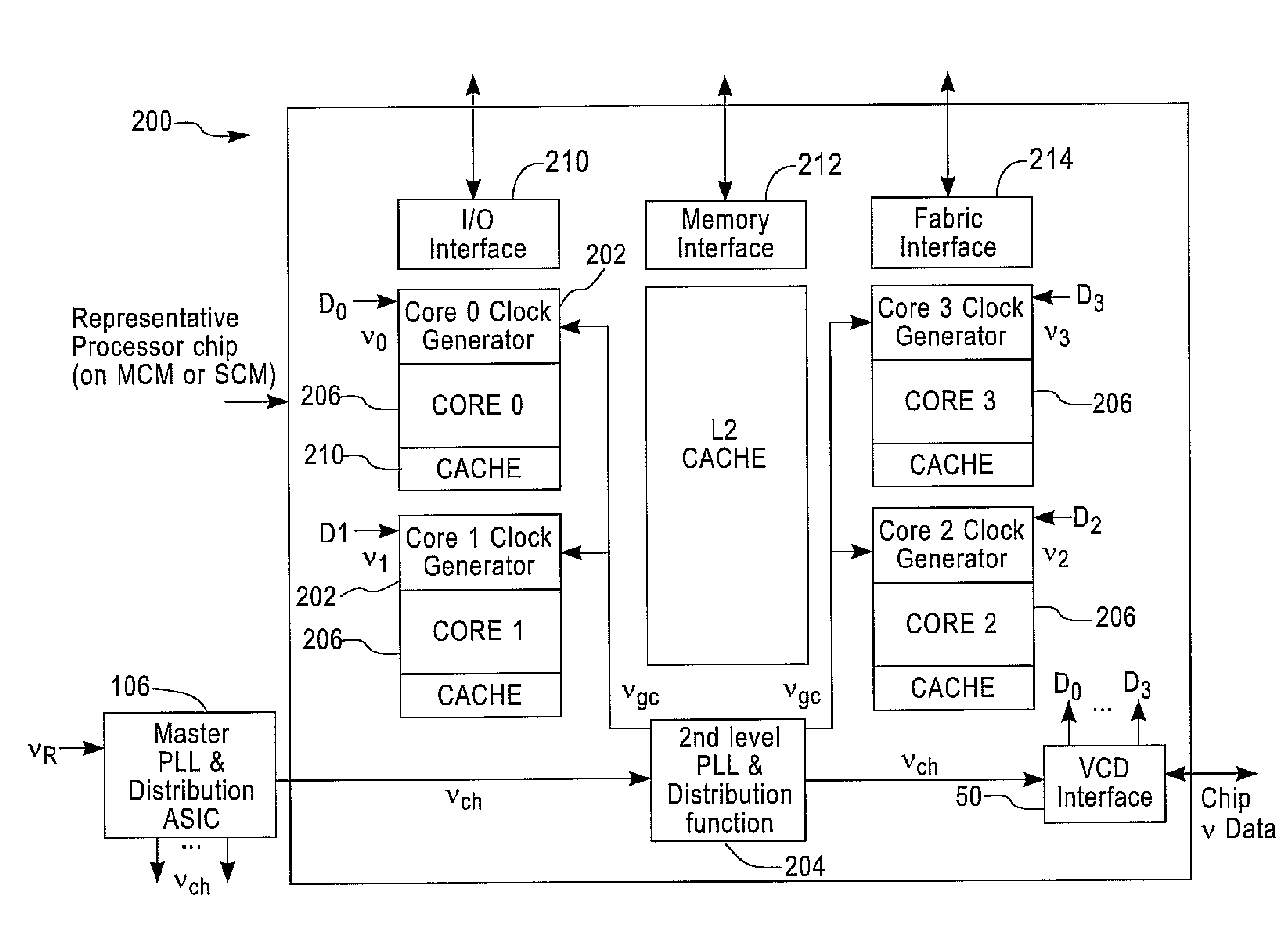

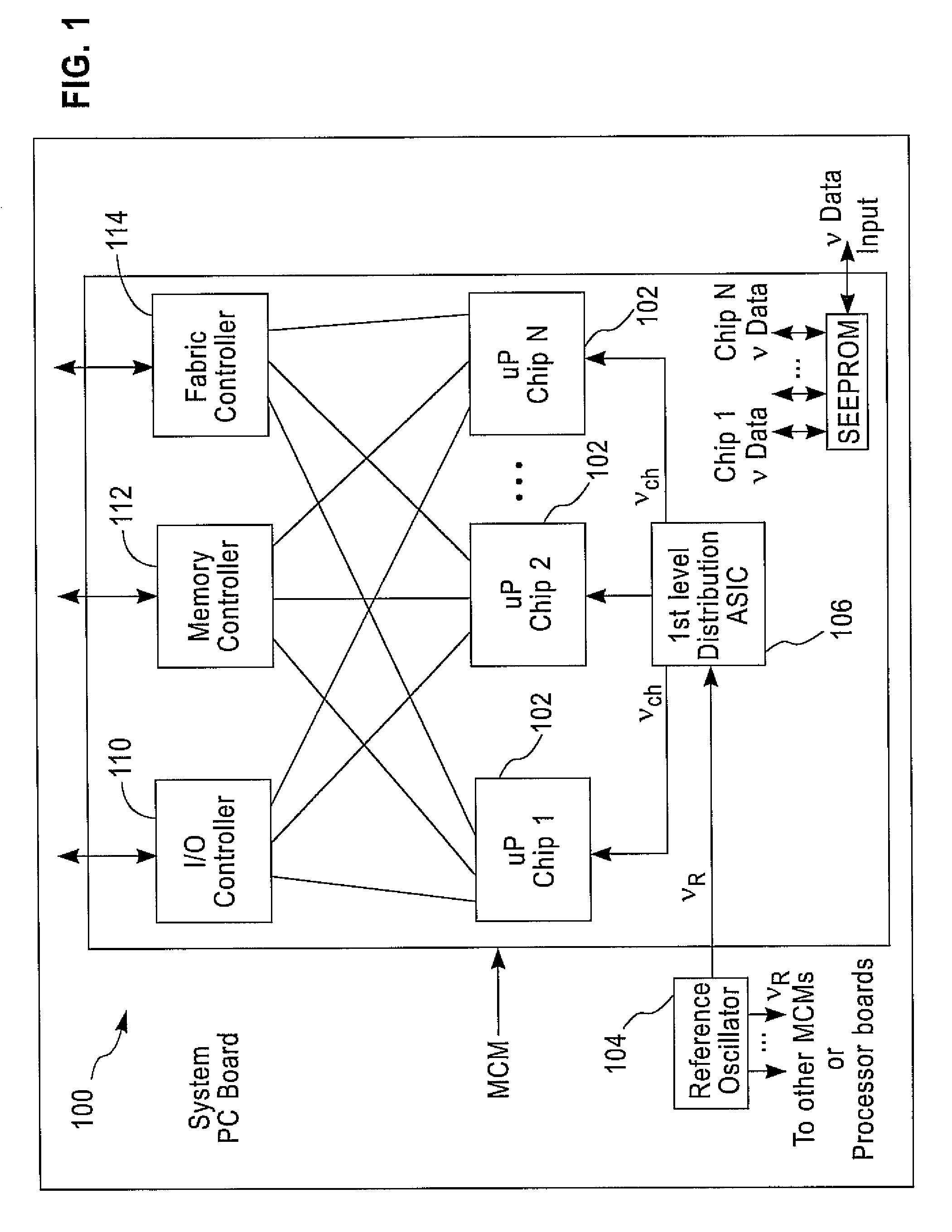

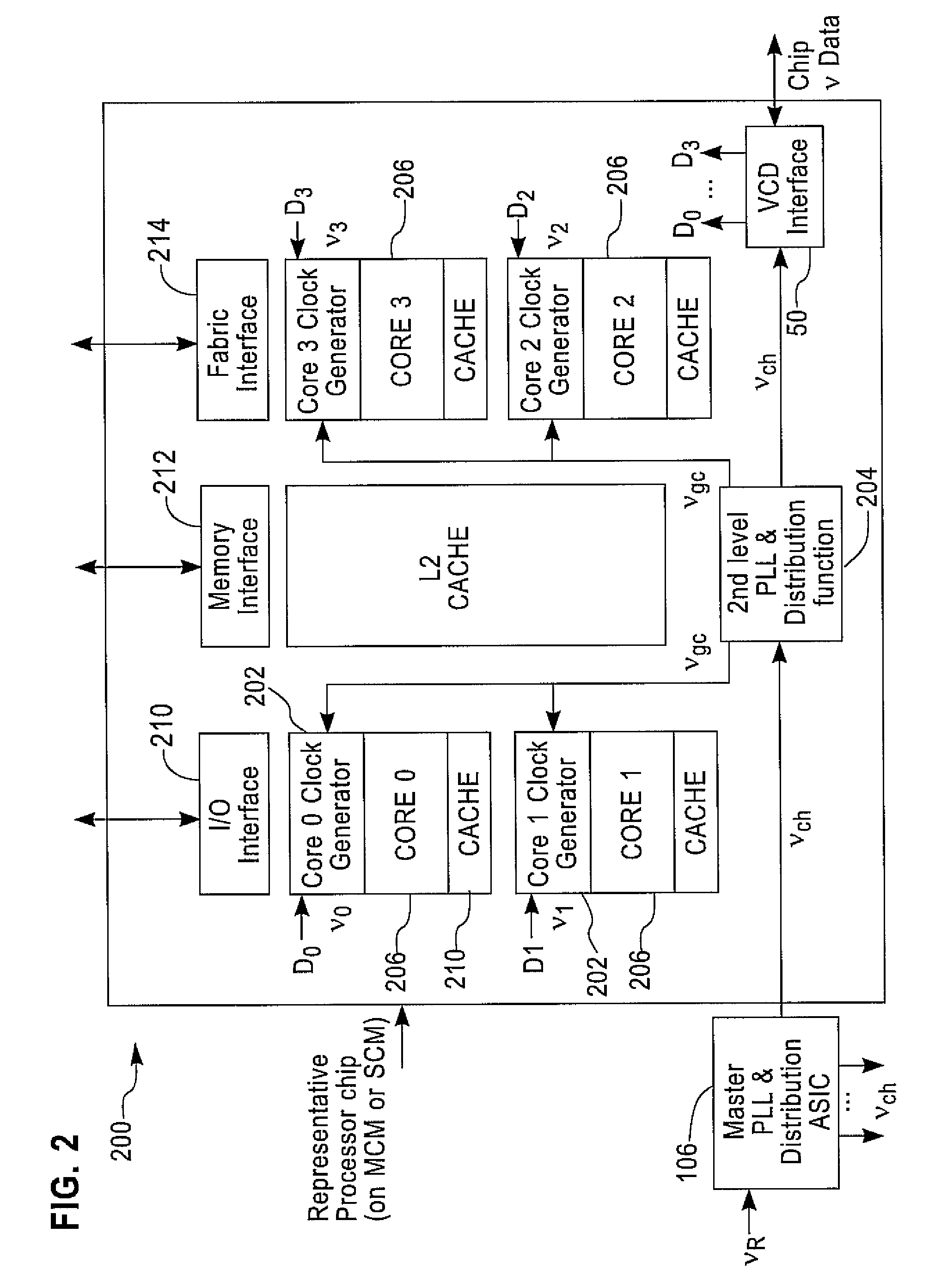

Method and system for analog frequency clocking in processor cores

ActiveUS20080256381A1Minimize latencyIncreased latencyPulse automatic controlGenerating/distributing signalsClock signalControl data

A method of and system for frequency clocking in a processor core are disclosed. In this system, at least one processor core is provided, and that at least one processor core has a clocking subsystem for generating an analog output clock signal at a variable frequency. Digital frequency control data and an analog signal are both transmitted to that at least one processor core; and that processor core uses the received analog signal and digital frequency control data to set the frequency of the output clock signal of the clocking subsystem. In a preferred implementation, multiple cores are asynchronously clocked and the core frequencies are independently set.

Owner:IBM CORP

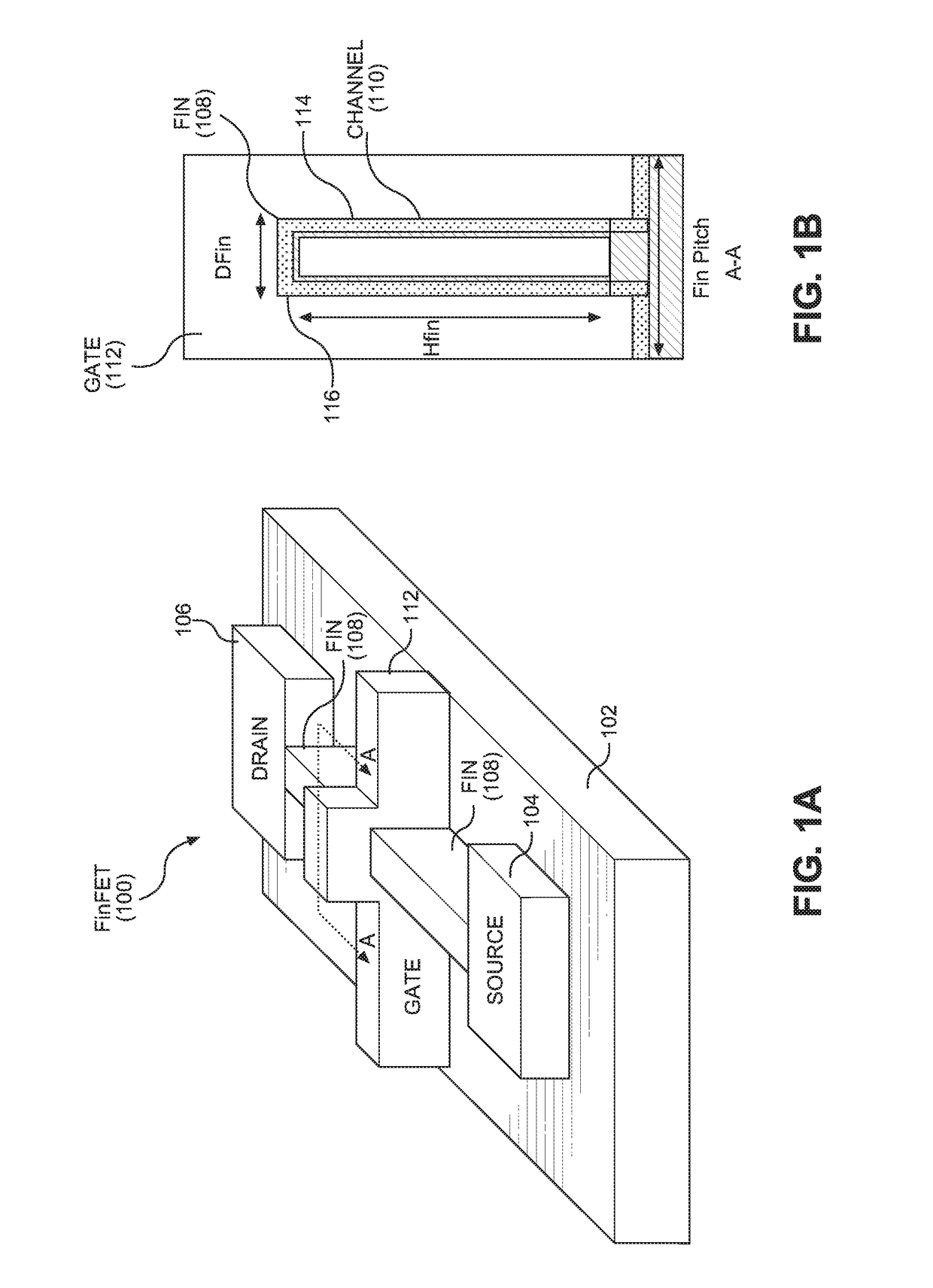

NANOWIRE METAL-OXIDE SEMICONDUCTOR (MOS) FIELD-EFFECT TRANSISTORS (FETs) (MOSFETs) EMPLOYING A NANOWIRE CHANNEL STRUCTURE EMPLOYING RECESSED CONDUCTIVE STRUCTURES FOR CONDUCTIVELY COUPLING NANOWIRE STRUCTURES

InactiveUS20170207313A1Increase widthIncrease channel current densitySemiconductor devicesMOSFETNanowire

Nanowire metal-oxide semiconductor (MOS) Field-Effect Transistors (FETs) (MOSFETs) employing a nanowire channel structure employing recessed conductive structures for conductively coupling nanowire structures are disclosed. Conductive structures are disposed between adjacent nanowire structures to conductively couple nanowire structures. Providing conductive structures in the nanowire channel structure increases the average cross-sectional area of nanowire structures, as compared to a similar nanowire channel structure not employing conductive structures, thus increasing effective channel width and drive strength for a given channel structure height. The precision of a gate material filling process is also eased, because gate material does not have to be disposed in areas between adjacent nanowire structures occupied by conductive structures. The conductive structure width can also be recessed with regard to width of nanowire structures in the nanowire channel structure to allow for a thicker metal gate to lower the gate resistance, while providing excellent electrostatic gate control of the channel.

Owner:QUALCOMM INC

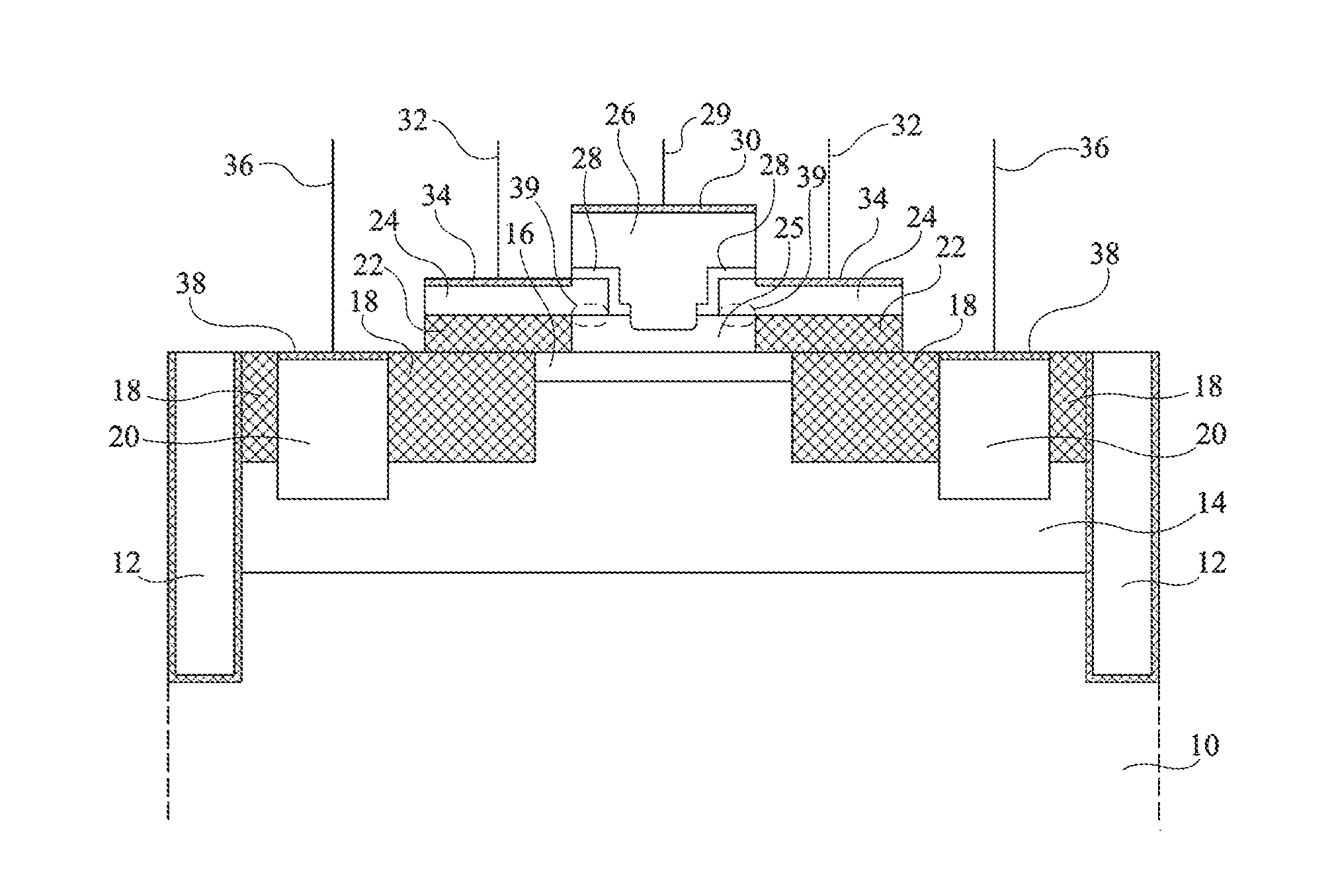

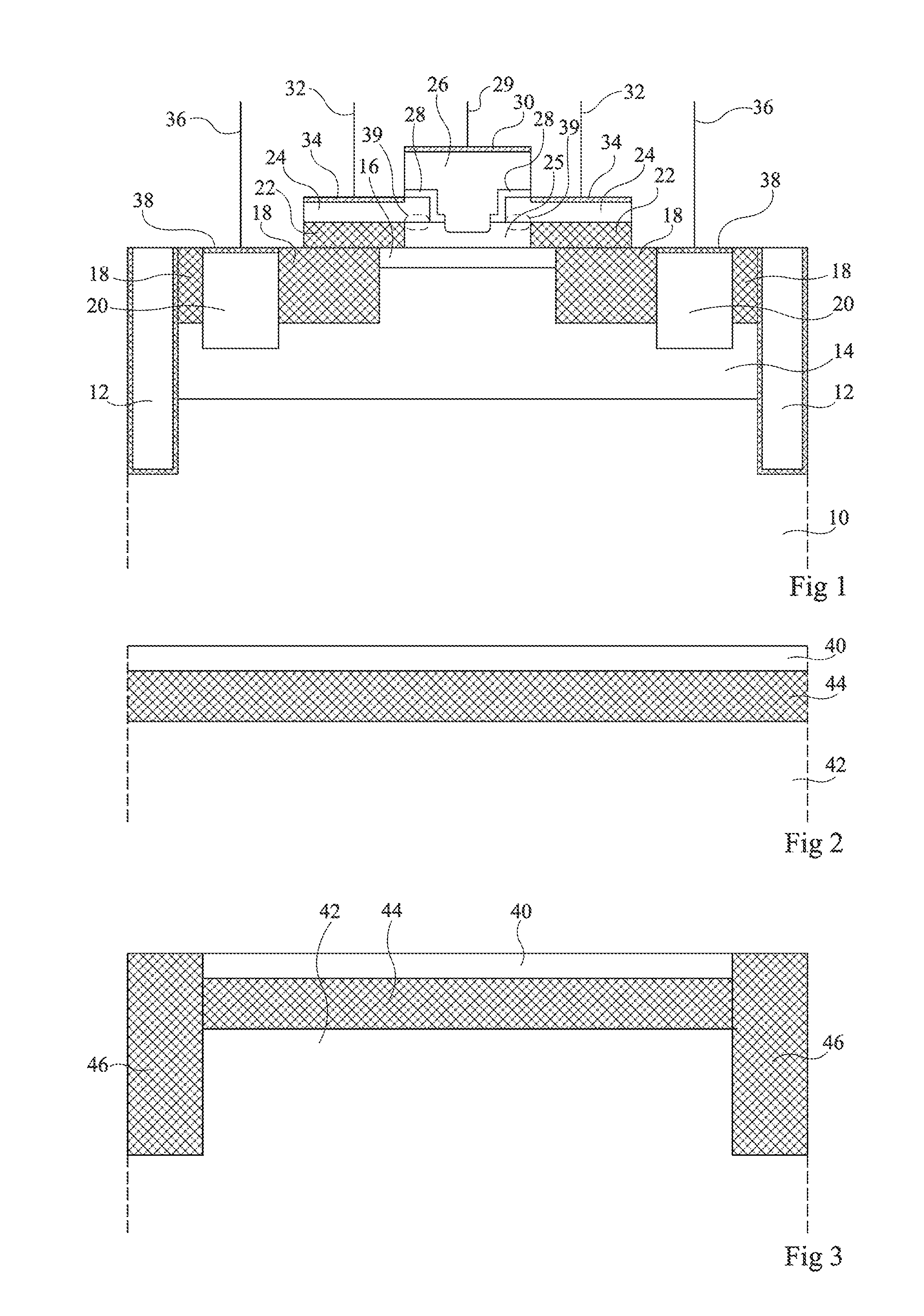

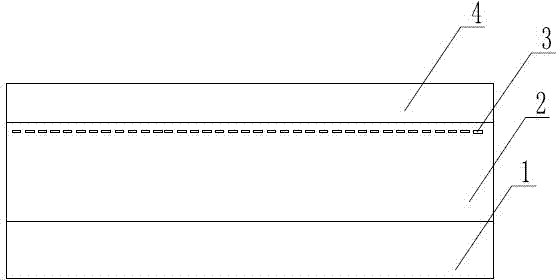

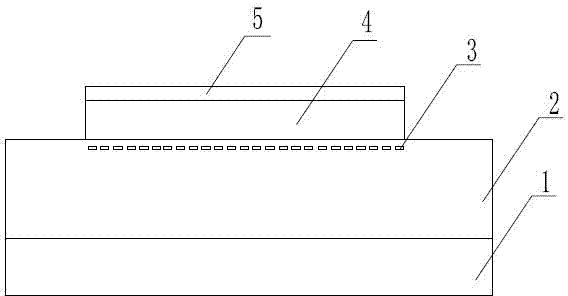

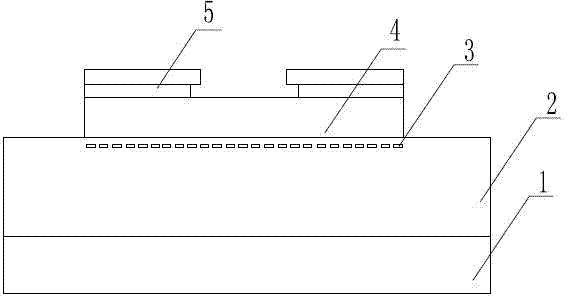

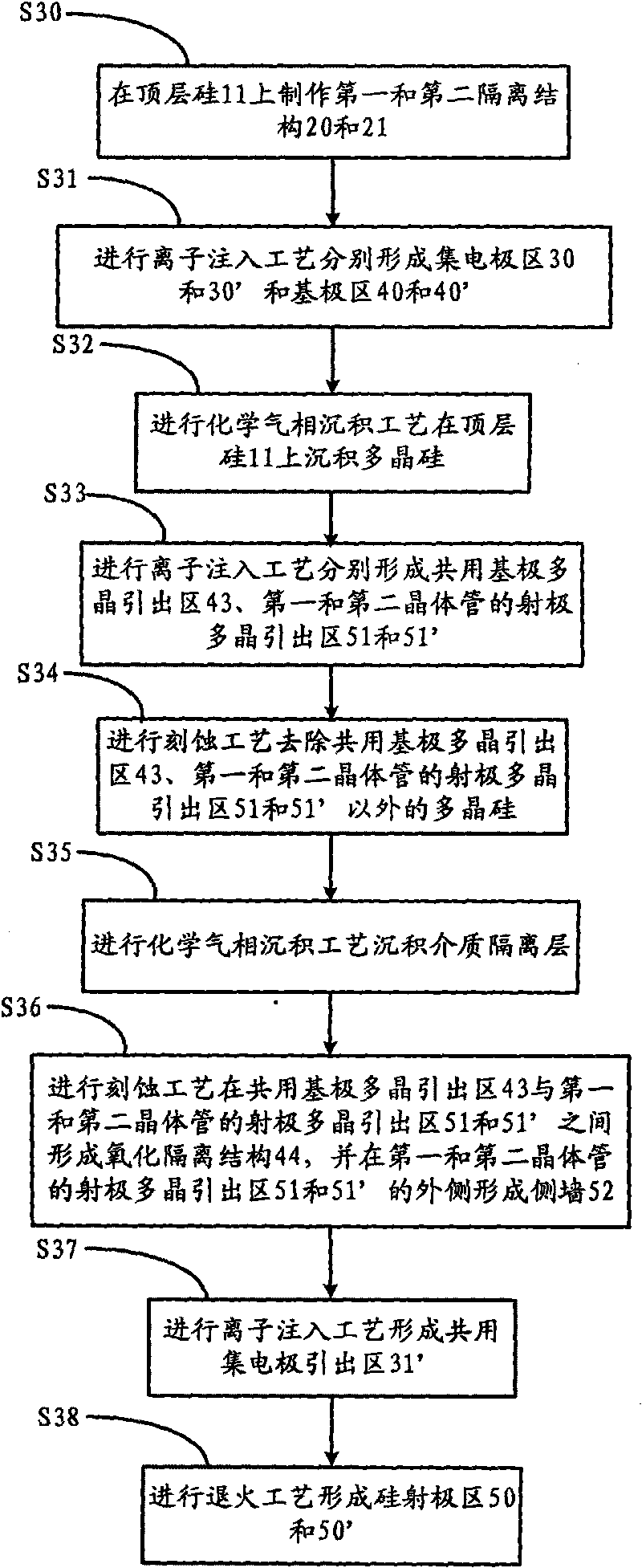

Bipolar transistor manufacturing method

InactiveUS20130270649A1Improve frequency performanceTransistorSolid-state devicesCondensed matter physicsSemiconductor

A method for manufacturing a bipolar transistor, including the steps of: forming a first surface-doped region of a semiconductor substrate having a semiconductor layer extending thereon with an interposed first insulating layer; forming, at the surface of the device, a stack of a silicon layer and of a second insulating layer; defining a trench crossing the stack and the semiconductor layer opposite to the first doped region, and then an opening in the exposed region of the first insulating layer; forming a single-crystal silicon region in the opening; forming a silicon-germanium region at the surface of single-crystal silicon region, in contact with the remaining regions of the semiconductor layer and of the silicon layer; and forming a second doped region at least in the remaining space of the trench.

Owner:STMICROELECTRONICS SRL

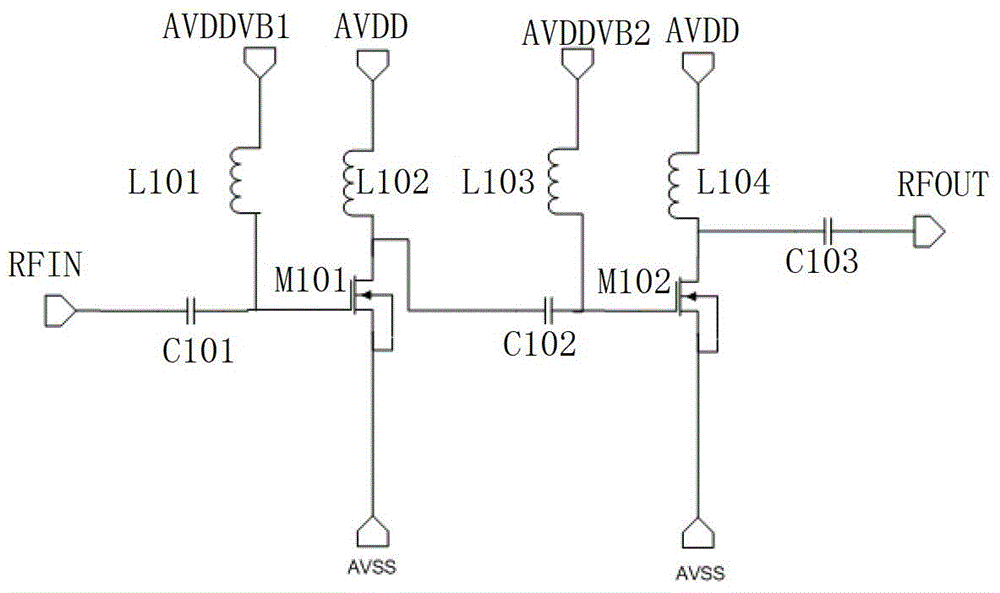

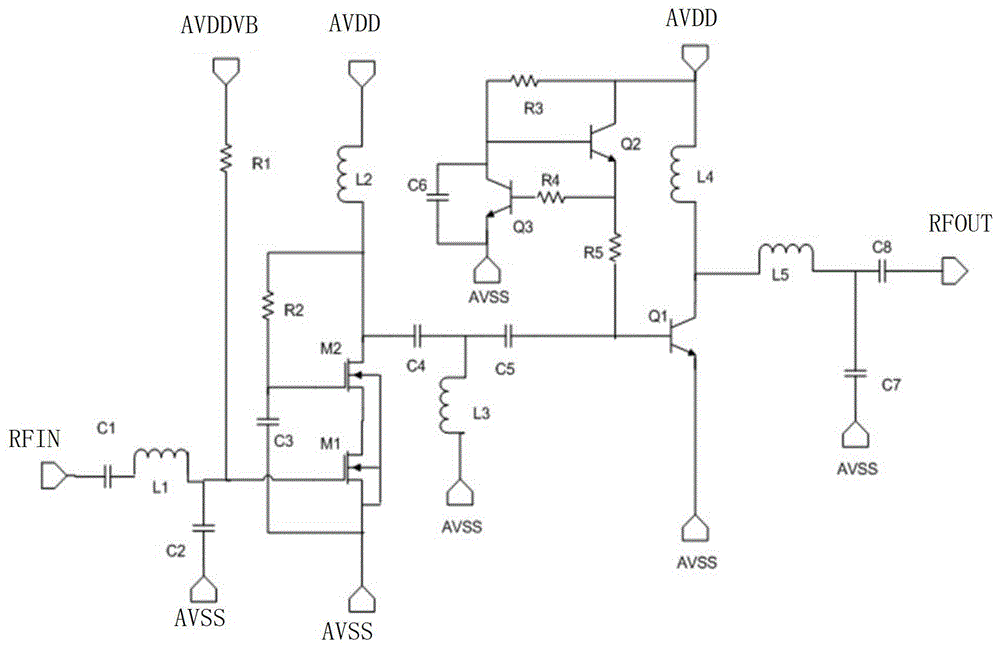

Radio frequency power amplifier

ActiveCN104158500AImprove pressure resistanceImprove isolationHigh frequency amplifiersAmplifier modifications to extend bandwidthCommon emitterAudio power amplifier

The invention discloses a radio frequency power amplifier integrated on a same chip. The radio frequency power amplifier comprises two stages of amplifying circuits. An automatic biasing cascode CMOS amplifier is adopted in the first-stage amplifying circuit, and a SiGe HBT connected through a common emitter is adopted in the second-stage amplifying circuit. According to the radio frequency power amplifier, the withstand voltage, the isolation and the bandwidth of the circuits can be improved, the voltage swing and working current of the circuits can be improved, the gain and the maximum output power of the circuits can be improved, the frequency performance of the power amplifier can be improved, full-chip integration can be achieved, and accordingly, the integration degree is improved, cost is reduced, and the application is simplified.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method and system for digital frequency clocking in processor cores

InactiveUS20080256382A1Improve noise immunityReduce signal distortionEnergy efficient ICTMultiple digital computer combinationsControl dataAnalog signal

Disclosed are a method of and system for digital frequency clocking in a processor core. At least one-processor core is provided, and that processor core has a clocking subsystem for generating an output clock signal, which may be an analog signal at a variable frequency. Digital frequency control data are transmitted or distributed to the processor core; and that one processor core receives the digital frequency control data transmitted to the core, and uses that received digital frequency control data to set the frequency of the output clock signal of the clocking subsystem of the processor core. Preferably, multiple cores are asynchronously clocked and the core frequencies are independently set, and, there is no phase relationship between the core clocks.

Owner:IBM CORP

Programmable logic devices with skewed clocking signals

InactiveUS7464286B1Improve frequency performanceImproves operating frequency characteristicError detection/correctionData resettingComputer Aided DesignPath length

A programmable logic device has programmable phase-shifting circuitry. The phase-shifting circuitry is used to generate a set of skewed clock signals that is used to adjust the relative timing of device elements in a circuit synthesized in the programmable logic device. By suitably adjusting the relative timing of the device elements, the circuit critical path lengths are effectively reduced leading to improved circuit frequency performance. Algorithms are provided for establishing clock skew values that lead to improved circuit performance. The algorithms are incorporated in computer aided design tools to enable automatic optimization of circuit designs.

Owner:ALTERA CORP

Method for preparing diamond base FET device with T-similar-type grid shelter autocollimation technology

ActiveCN103325686ALower on-resistanceImprove frequency performanceSemiconductor/solid-state device manufacturingSemiconductor devicesAutocollimationTemperature resistance

The invention discloses a method for preparing a diamond base FET device with the T-similar-type grid shelter autocollimation technology, and relates to the technical field of methods for manufacturing semiconductor devices. The method comprises the step of forming a high-resisting diamond layer on a high temperature resistance substrate, the step of forming a conducting channel in the high-resisting diamond layer, the step of covering the surface of the high-resisting diamond layer with a metal mask layer, the step of photoetching a table-board, the step of removing a metal mask outside the table-board area through corrosive liquid, the step of forming grids on the metal mask in a photoetching mode, the step of removing the metal mask in the middle of a source leaking area through the corrosive liquid and forming source leakage, the step of manufacturing the T-similar-type grids in the corrosion area, the step of oxidizing or nitriding the outer sides of metal grids and forming a dielectric layer, and the step of enabling the T-similar-type grids to serve as a shield. According to the method, the T-similar-type grid shelter autocollimation technology is adopted, the distance between a grid source position and a grid leakage position is effectively shortened and is basically equal to the grid length, and the grid source resistance and grid leak resistance are reduced.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

Hybrid frequency offset estimator

ActiveUS7590199B2Improve frequency performanceImprove performancePolarisation/directional diversityLine-faulsts/interference reductionPacket lossData aided

A hybrid carrier frequency offset estimator that uses data-aided and non-data-aided signal processing techniques to produce multiple candidates for the carrier frequency offset within a return channel receiver in a DVB-RCS system using turbo coding and quadrature phase shift keying (QPSK) data modulation. In this system, the invention is employed to estimate signal distortion caused by carrier frequency offset so that this particular source of signal distortion can be removed to improve the ability of the receiver to maintain synchronization in low signal-to-noise conditions. This, in turn, allows the receiver to meet the DVB-RCS performance target, measured in terms of packet loss ratio, in low signal-to-noise ratio conditions and in particular for burst-mode data transmission with a short data packet size.

Owner:ADVANTECH SATELLITE NETWORKS

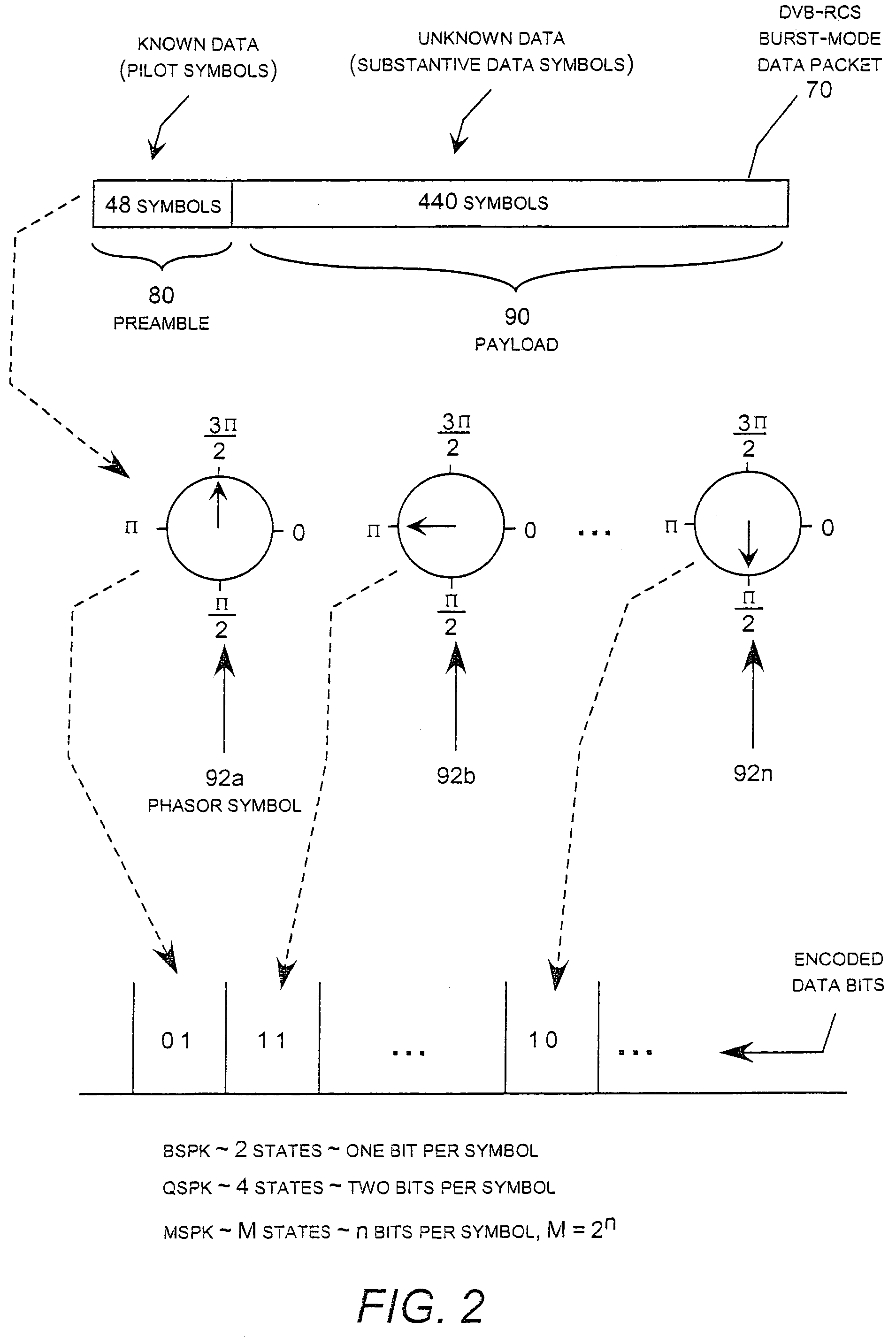

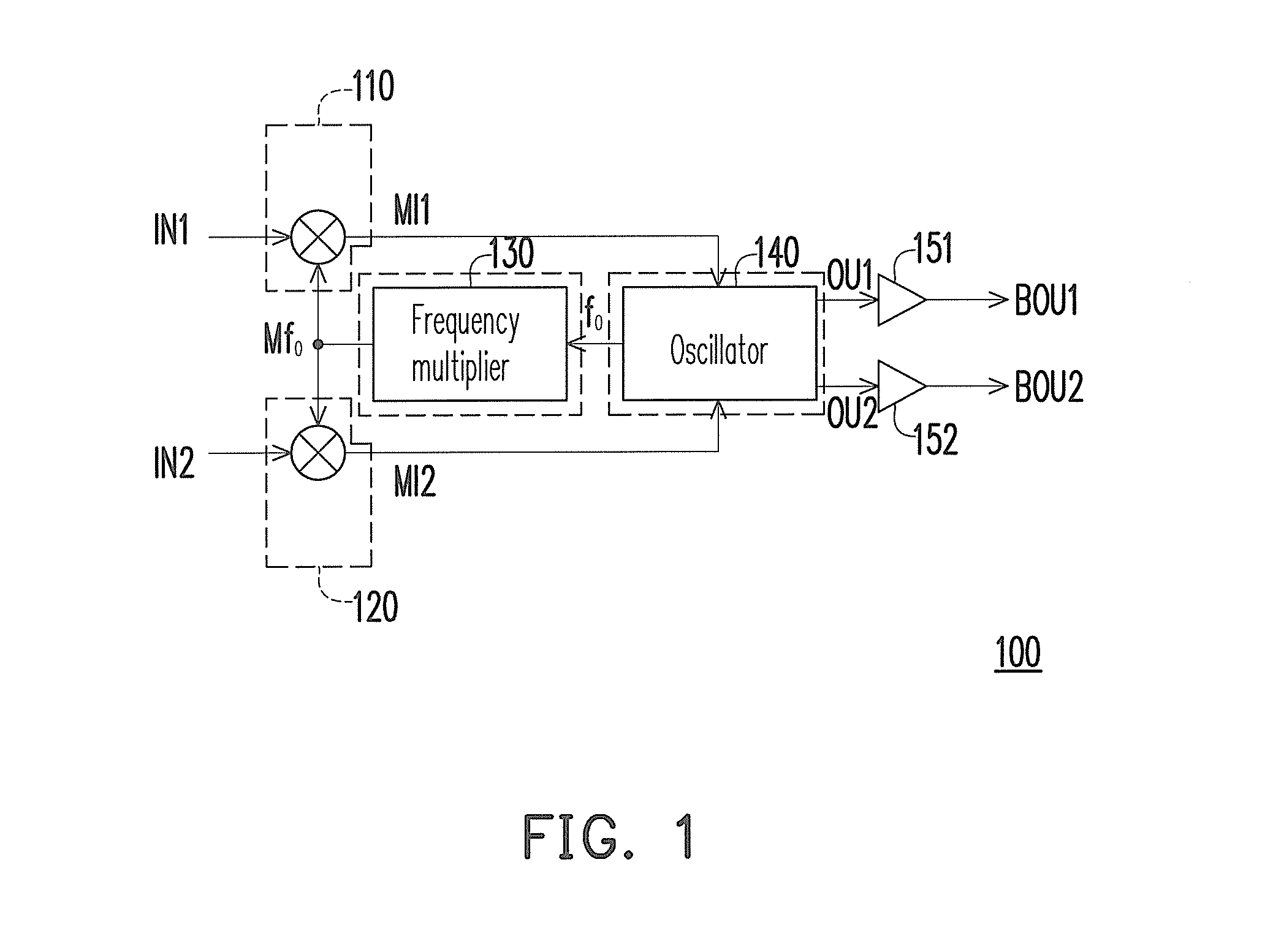

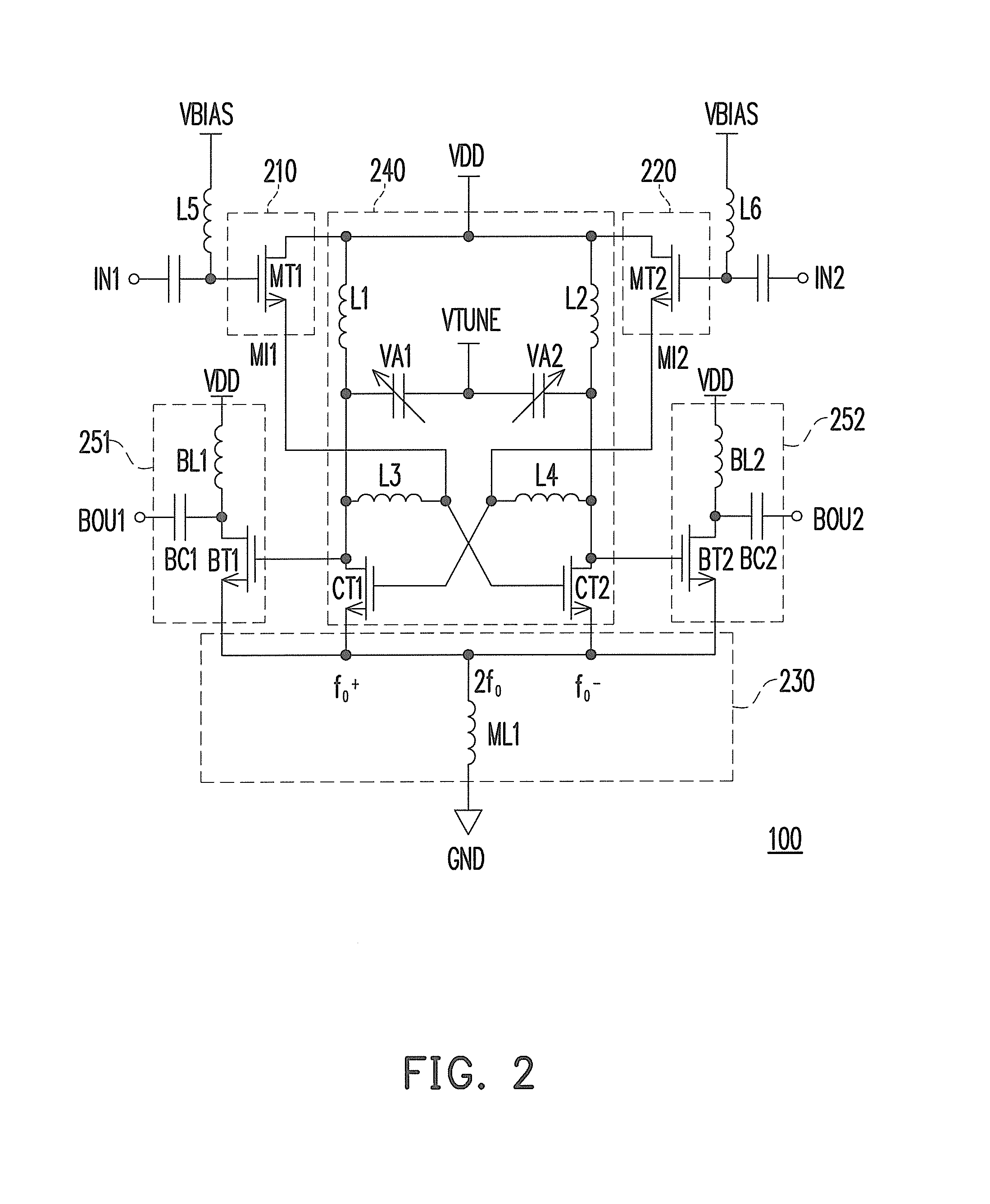

Injection-locked frequency dividing apparatus

InactiveUS8305116B2Easy to lockIncrease lock rangeCounting chain pulse countersPulse counters with static storageInjection lockedFrequency mixer

An injection-locked frequency dividing apparatus including a frequency multiplier, a first linear mixer, a second linear mixer, and an oscillator is disclosed. The frequency multiplier receives a frequency signal and generates a multiple-frequency signal accordingly. The first and the second linear mixer both receive the multiple-frequency signal and respectively receive a first input signal and a second input signal, wherein the phases of the first and the second input signal are complementary. The first and the second linear mixer respectively mix the multiple-frequency signal with the first and the second input signal to respectively generate a first mixed signal and a second mixed signal. The oscillator generates the frequency signal. The oscillator further receives the first and the second mixed signal and generates a first output signal and a second output signal accordingly, wherein the phases of the first and the second output signal are complementary.

Owner:NAT TAIWAN UNIV OF SCI & TECH

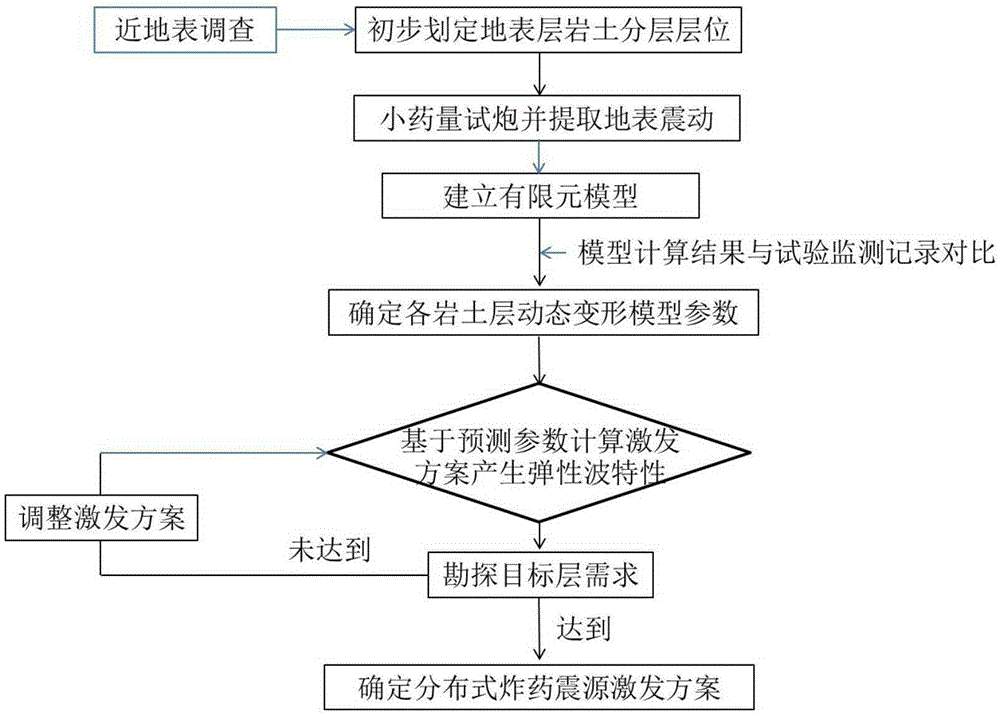

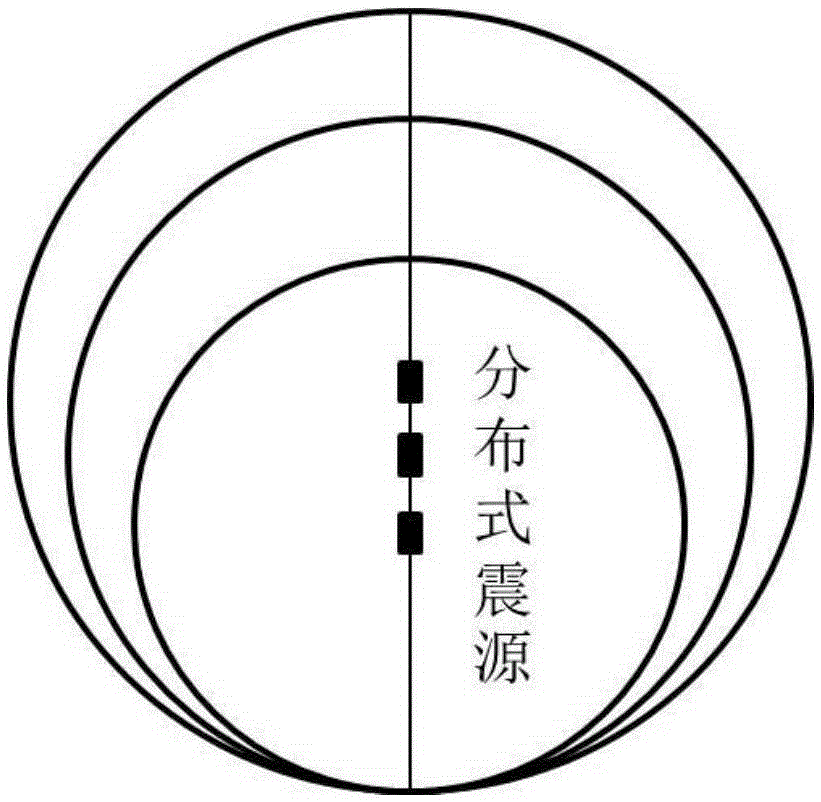

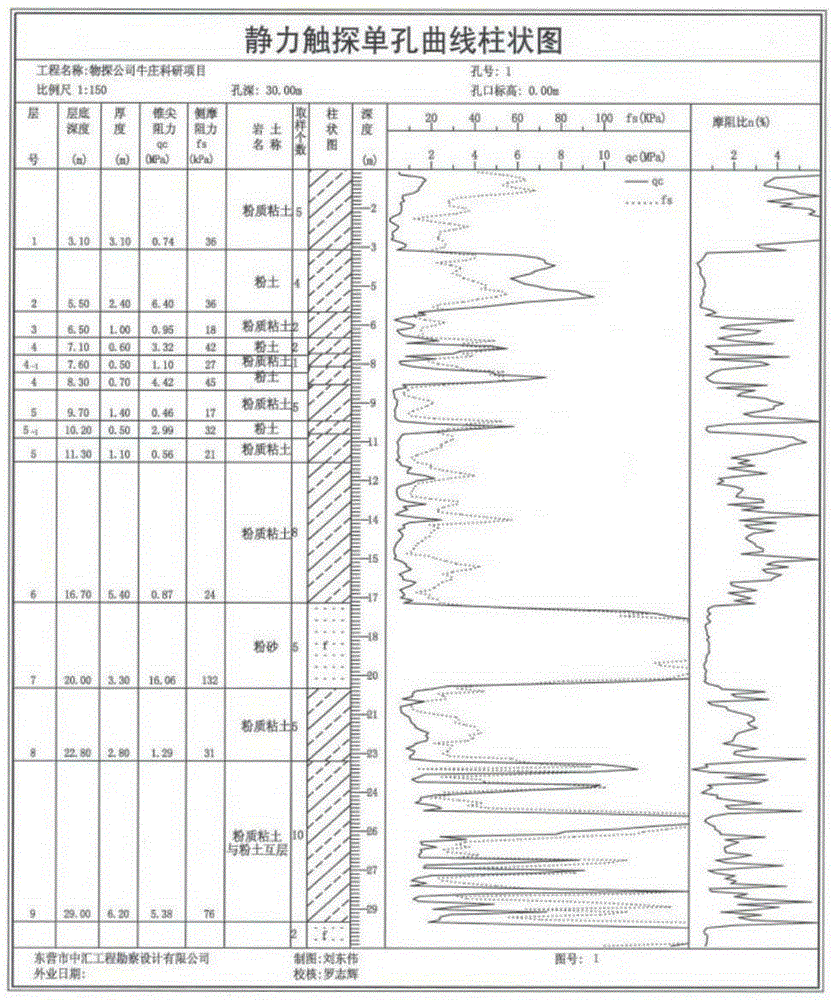

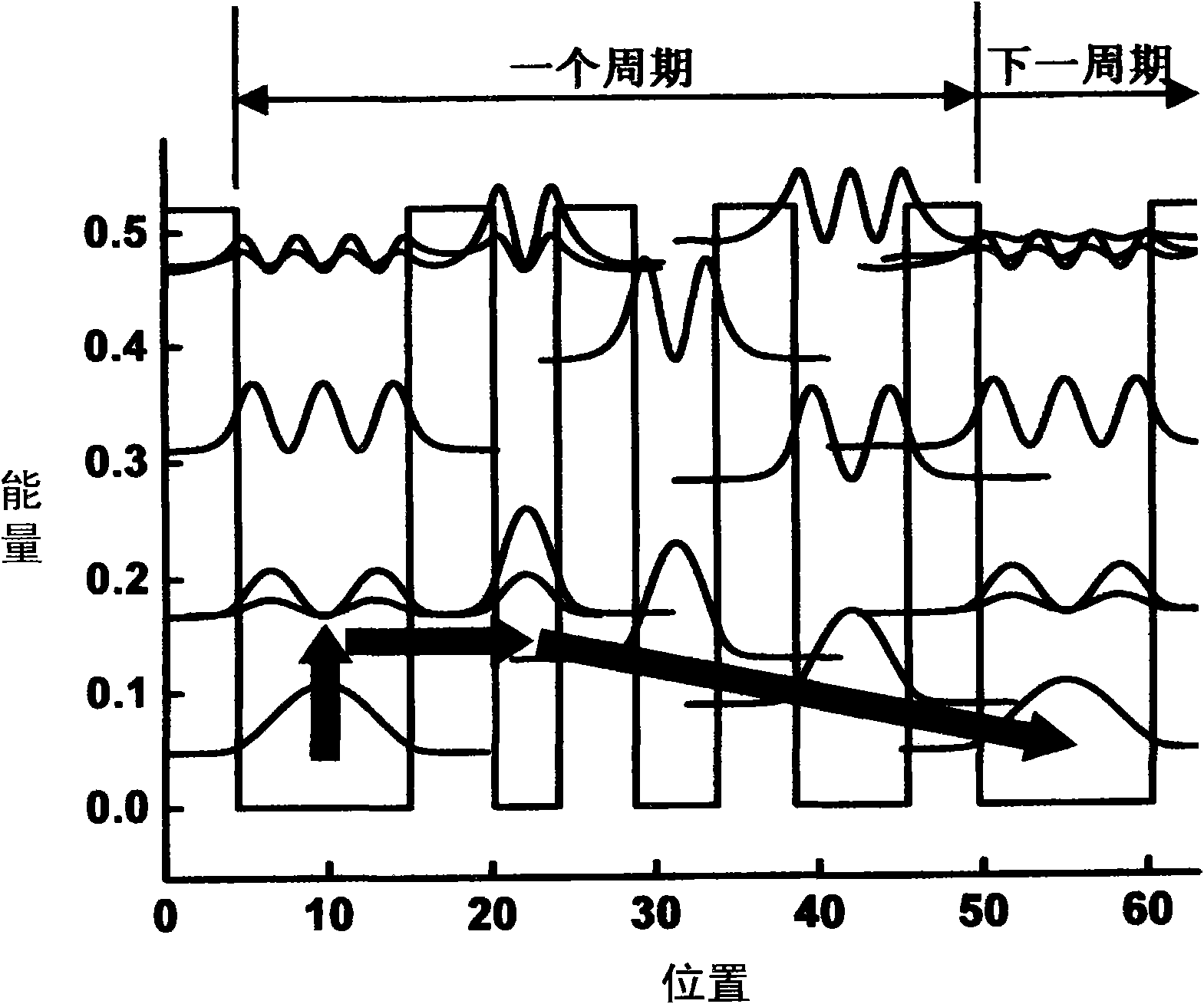

Method for determining distributed explosive source triggering parameters

The invention provides a method for determining distributed explosive source triggering parameters. The method comprises the steps of (a) adopting a near-surface survey method to delimit a rock-soil layer horizon of a surface layer and determining basic physical parameters; (b) performing gun testing and triggering, and monitoring and recording ground vibration; (c) according to gun testing arrangement and rock-soil layering of the earth surface, establishing a finite element model of explosion action in rock-soil of the explosive source; (d) performing comparing regression analysis by finite element model calculation and test monitoring records, and determining rock-soil dynamic deformation model parameters; (e) performing analysis comparison on initial elastic wave energy and frequency in multiple distributed explosive source triggering schemes on the basis of the established on-site rock-soil layer model, combining exploration target layer characteristics and requirements, and determining that the distribution satisfying the energy and resolution is explosive source triggering parameters. The method for determining the distributed explosive source triggering parameters, provided by the invention, is rapid in speed, wide in application scope, low in cost, simple and convenient, and easy to implement.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

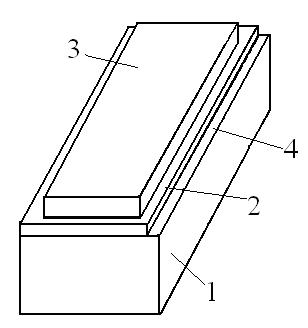

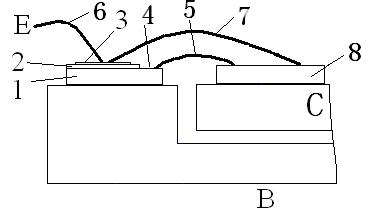

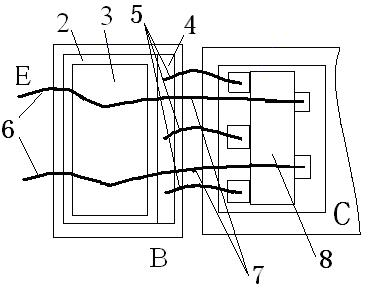

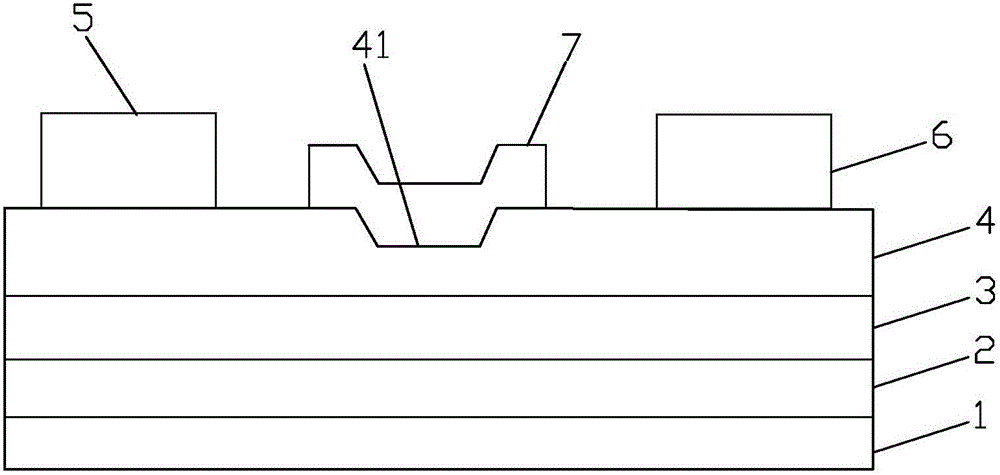

A microwave power transistor internal matching network and its manufacturing method

ActiveCN102280439AImprove performanceImprove frequency performanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceMicrowave

The invention discloses an internally matching network for a microwave power transistor and a manufacturing method of the internally matching network. The internally matching network comprises an internally matching mass optical memory (MOM) capacitor, a lower electrode outgoing line (5), a first upper electrode outgoing line (6) and a second upper electrode outgoing line (7), wherein the lower electrode outgoing line (5) of the MOM capacitor is led out of the upper surface (4), which is exposed by photoetching, of a lower electrode, and the other end of the lower electrode outgoing line is connected with a grounding pin of a tube core (8) transistor. The internally matching network has the advantages that the lengths of the electrode outgoing lines are shortened, the performance of the internally matching transistor is improved, a manufacturing process of the internally matching power transistor is simplified, the difficulty of the process is reduced, the utilization rate of a tube shell is improved, and the development period is shortened.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

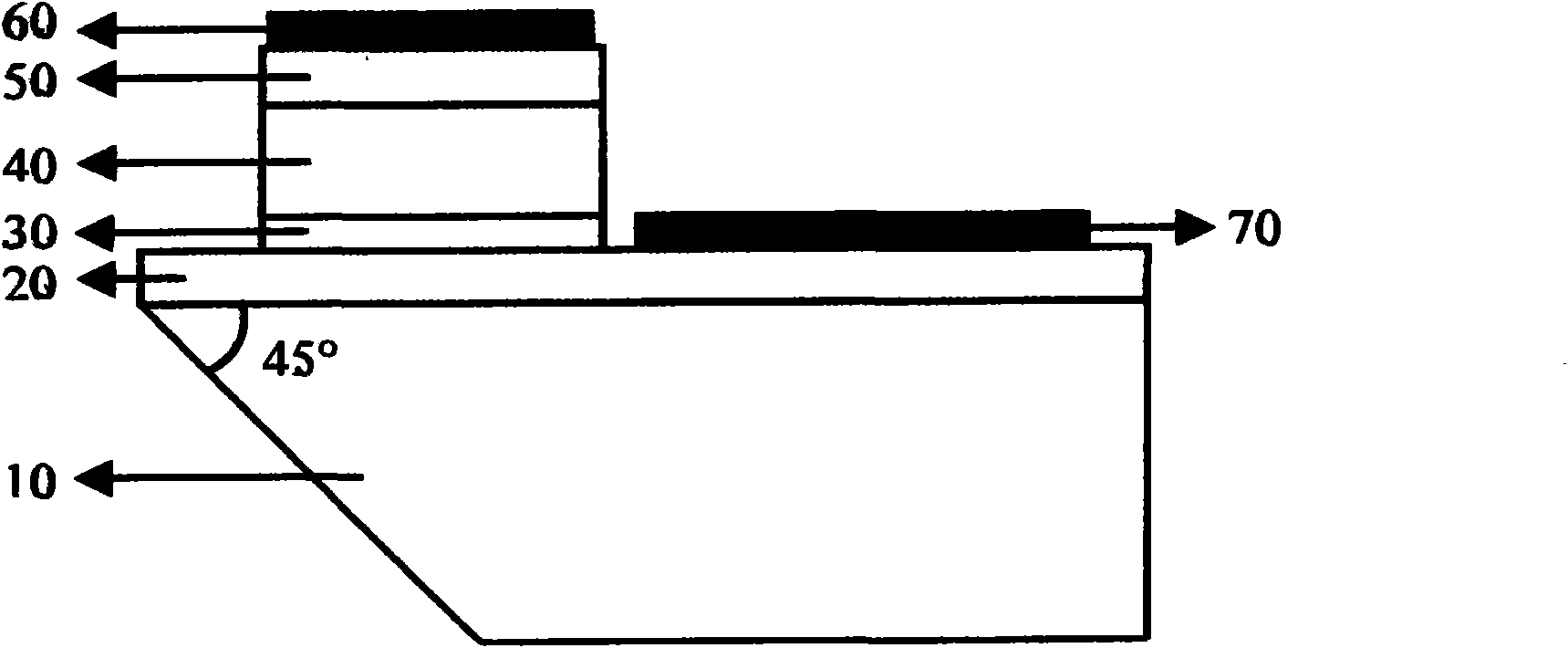

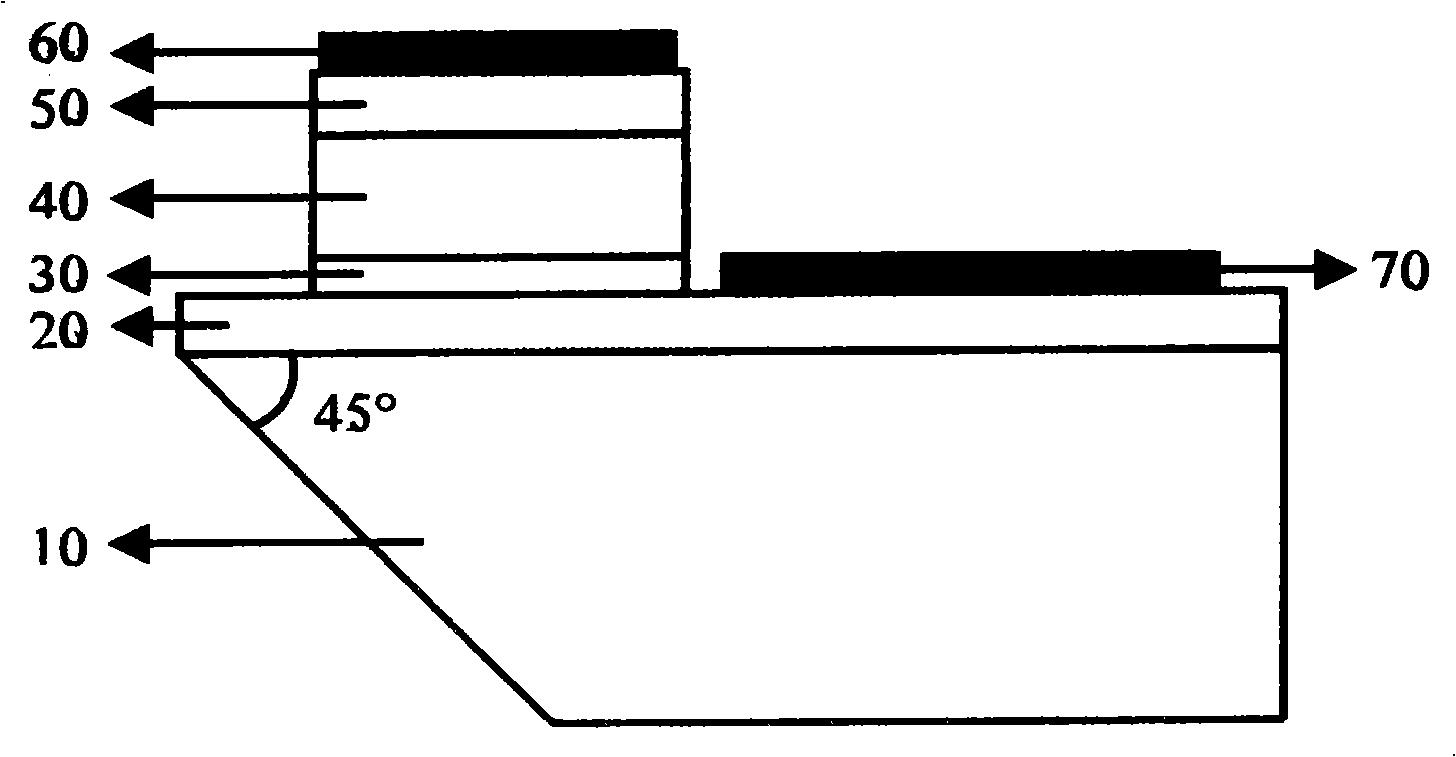

Structure of quantum cascade detector

InactiveCN101894876AIncrease resistanceShort relaxation timeSemiconductor devicesHigh concentrationOhmic contact

The invention provides the structure of a quantum cascade detector, which comprises a substrate, a lower ohmic contact layer, a barrier isolation layer, a multi-cycle active region structure layer, an upper ohmic contact layer, an upper electrode and a lower electrode, wherein the lower ohmic contact layer is arranged on the substrate and is used for carrying out the high-concentration doping process to achieve the ohmic contact with electrode materials; the barrier isolation layer is arranged at the middle part of the lower ohmic contact layer to form a table top all around the lower ohmic contact layer, wherein the barrier isolation layer is not doped; the multi-cycle active region structure layer is arranged on the barrier isolation layer and constitutes the core part of the detector for detecting light current; the upper ohmic contact layer is arranged on the multi-cycle active region structure layer and is used for carrying out the high-concentration doping process to achieve the ohmic contact with the electrode materials; the upper electrode is prepared on the upper ohmic contact layer; and the lower electrode is prepared on the table top all around the lower ohmic contact layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

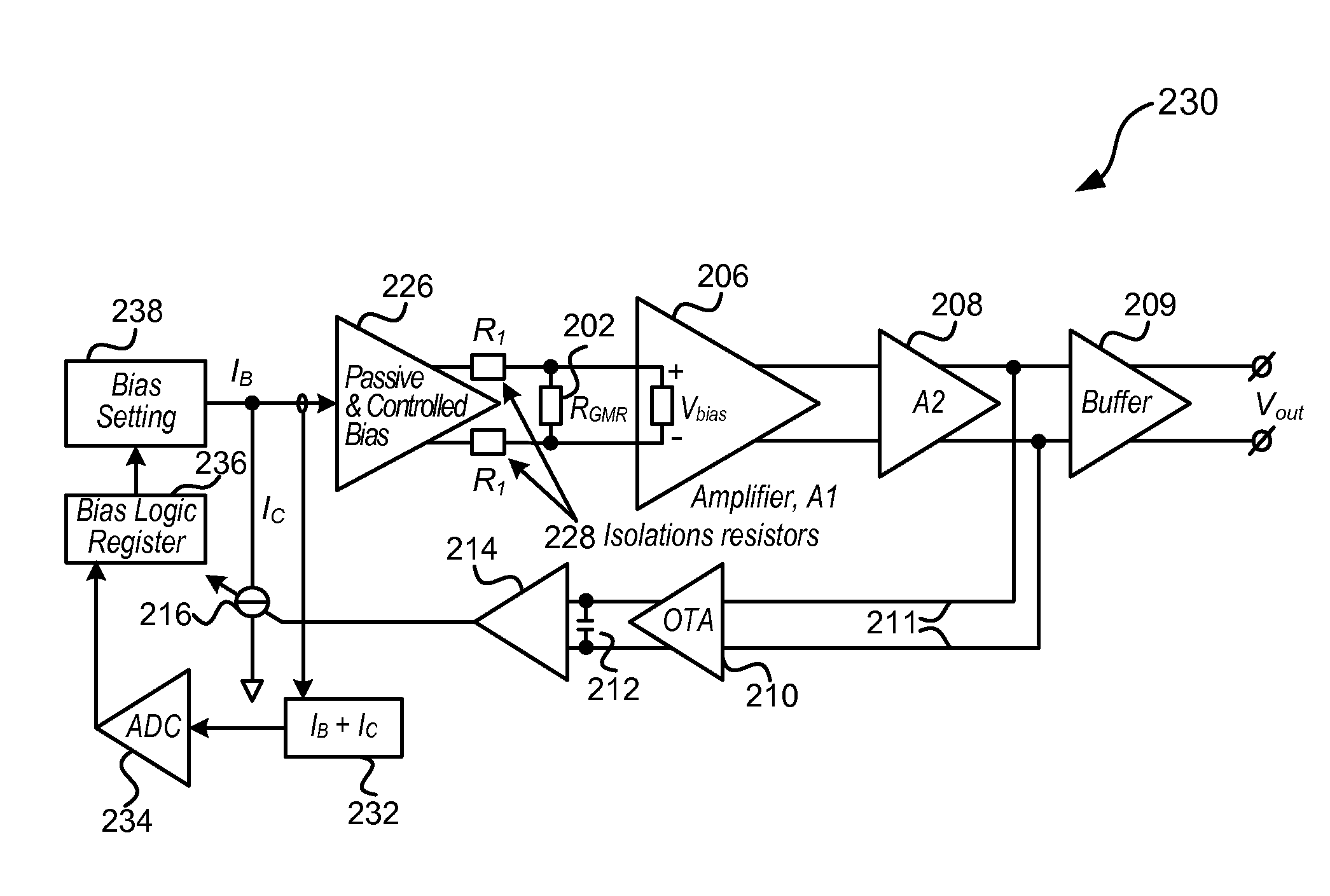

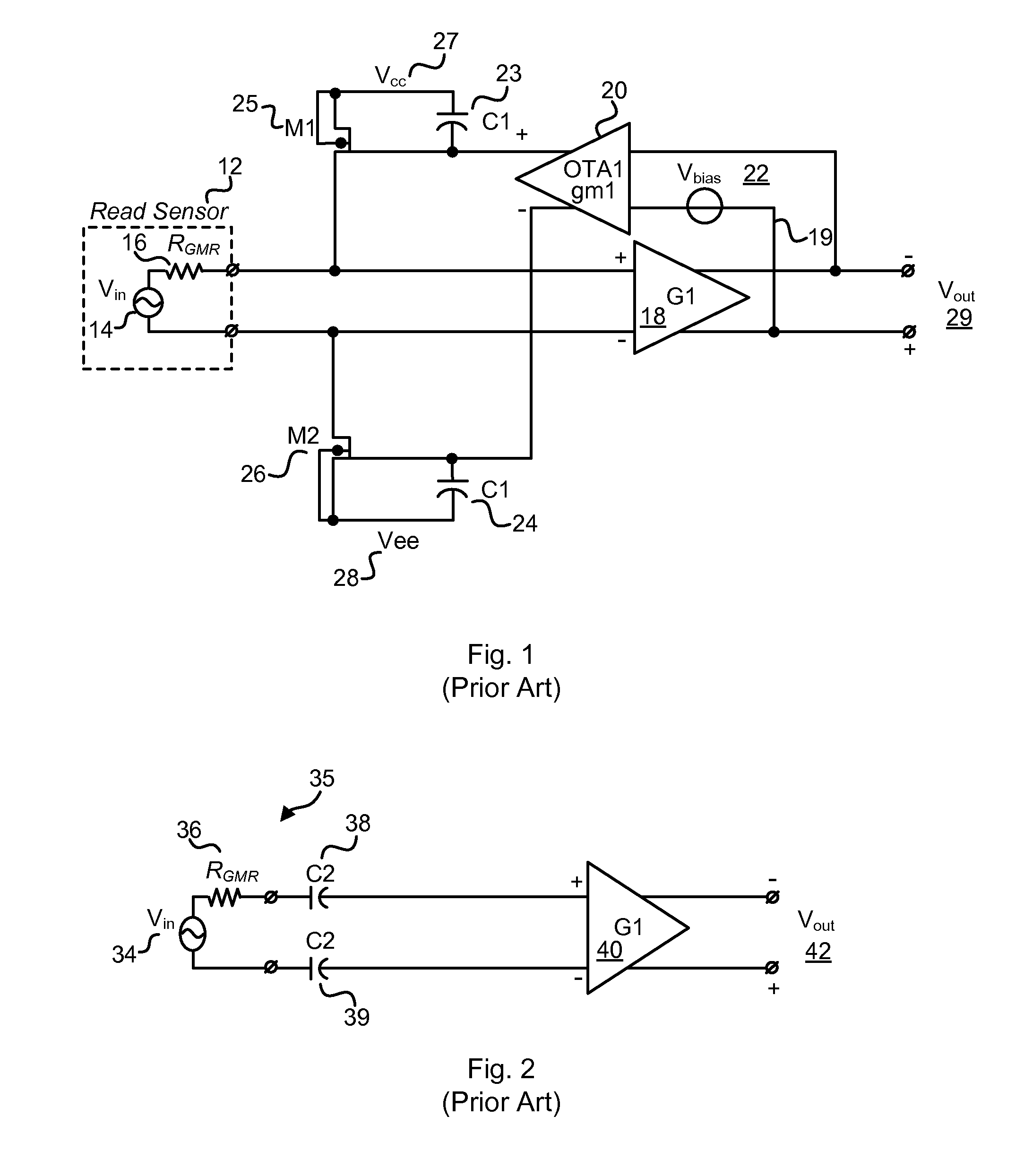

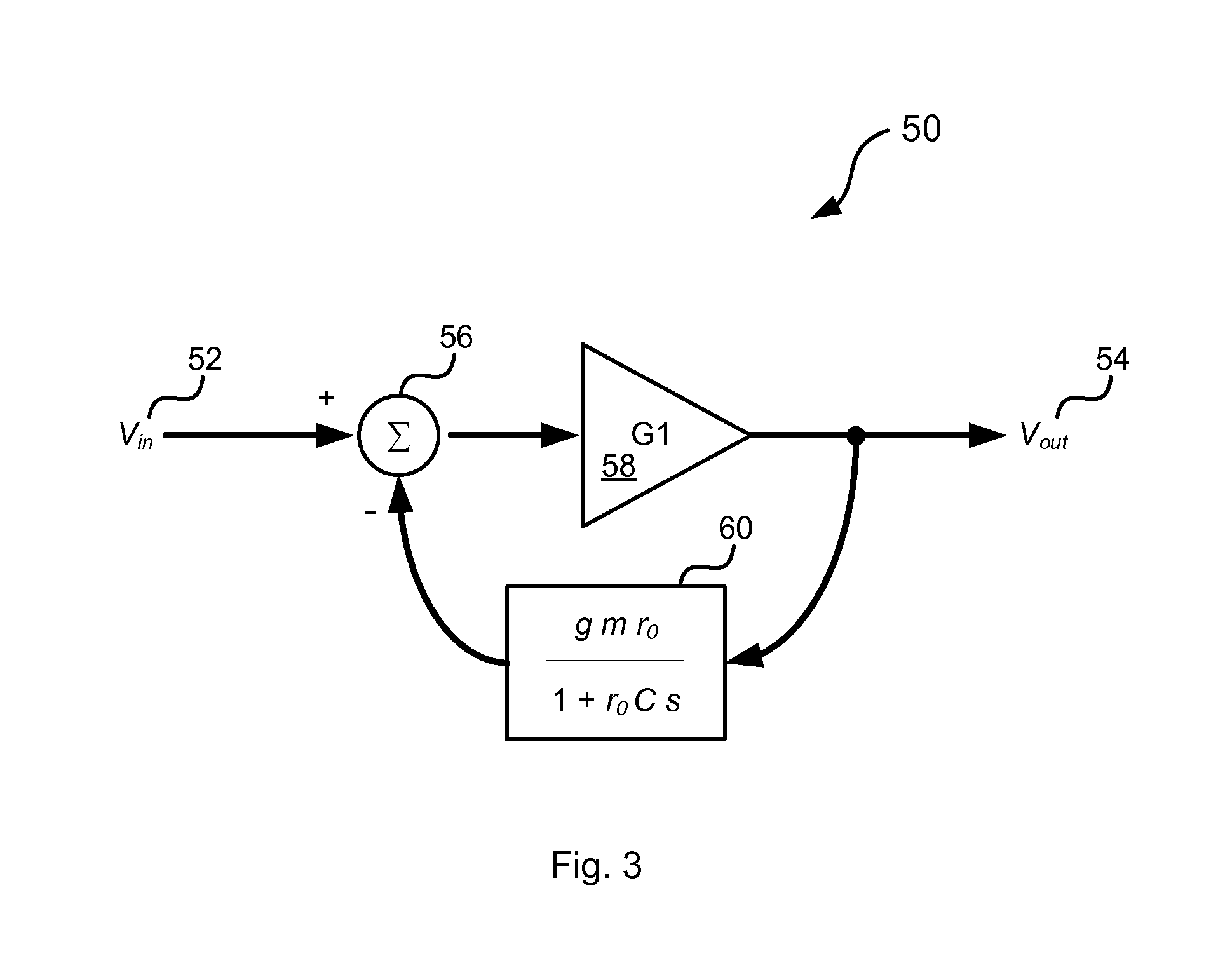

Direct coupled wide-bandwidth front-end with smart bias control amplifier

InactiveUS7667914B2High bandwidthReduce noiseRecord information storageAnalogue recordingHemt circuitsTransimpedance amplifier

Embodiments of the present invention provide a mixed-mode amplifier for amplifying signals in data storage devices such as disk drives. In one embodiments, a circuit for amplifying data signals comprises a magnetoresistive sensor having a bias voltage applied thereto; a signal amplifier which amplifies a signal detected by the magnetoresistive sensor having the bias voltage applied thereto; a feedback control block which is coupled to an output of the signal amplifier and outputs a feedback current used to vary a loop gain of the circuit; a bias setting circuit which outputs a bias setting current; and a transimpedance amplifier which receives the bias setting current from the bias setting block and the feedback current from the feedback control block and generates the bias voltage applied to the magnetoresistive sensor.

Owner:WESTERN DIGITAL TECH INC

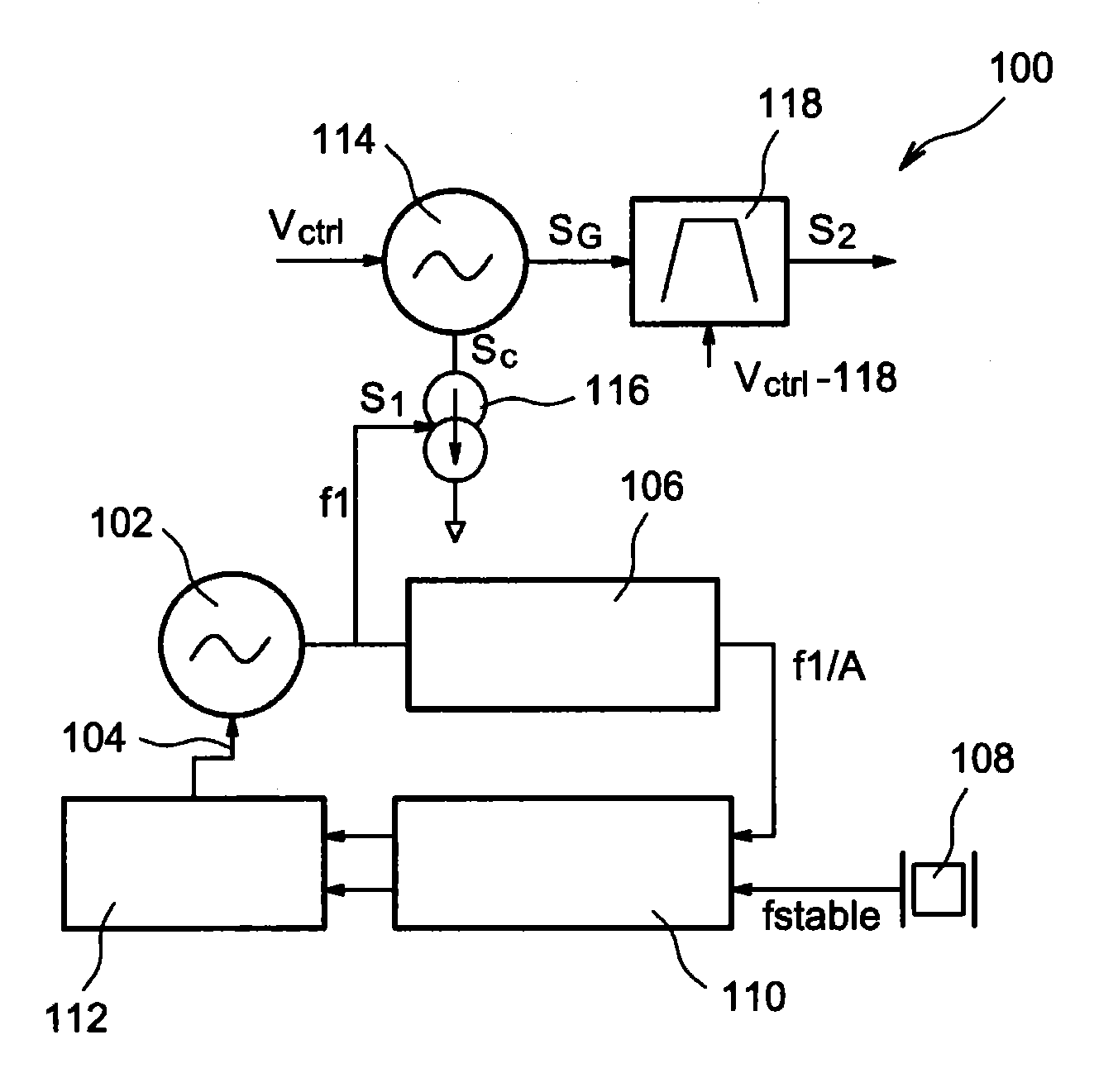

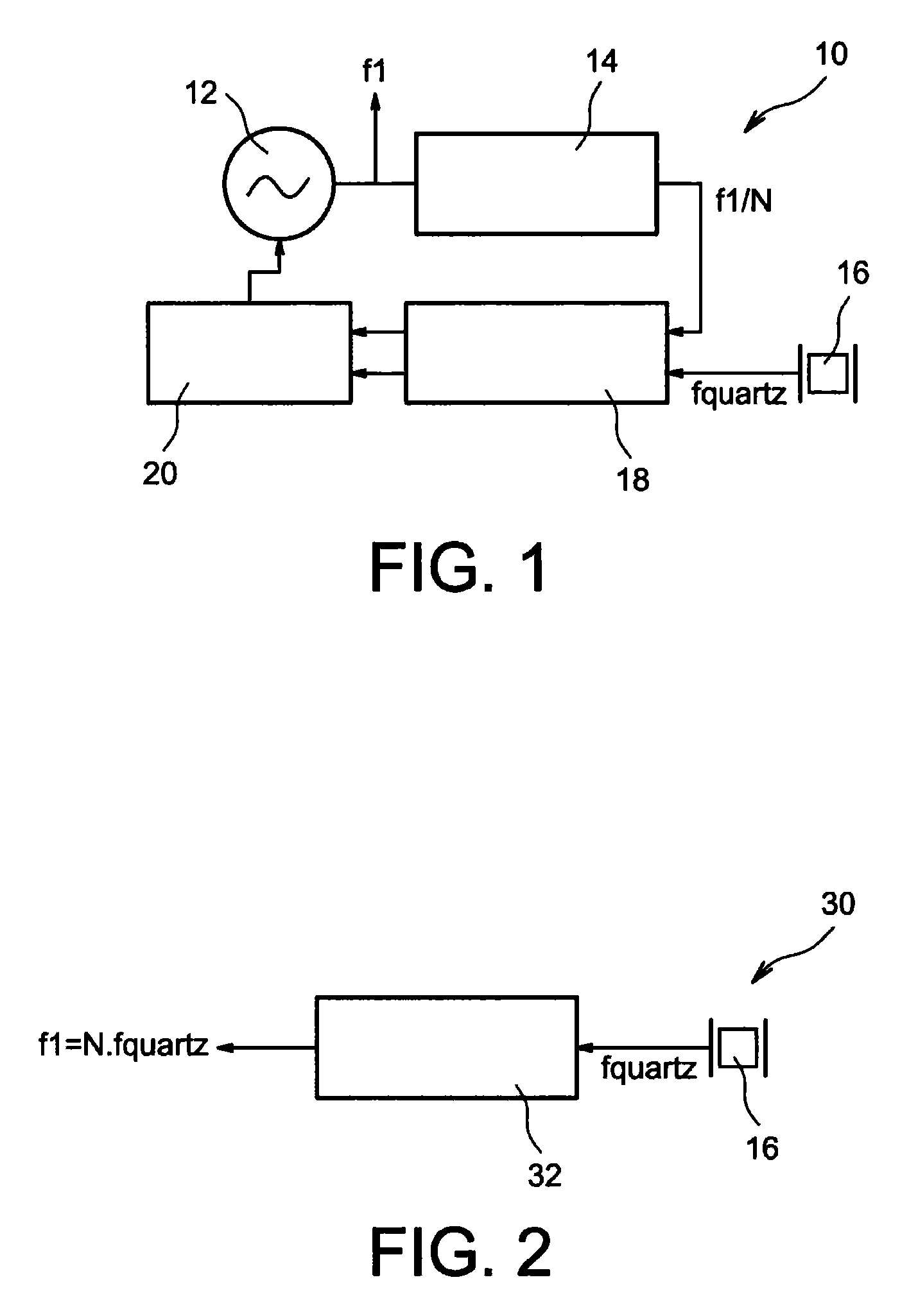

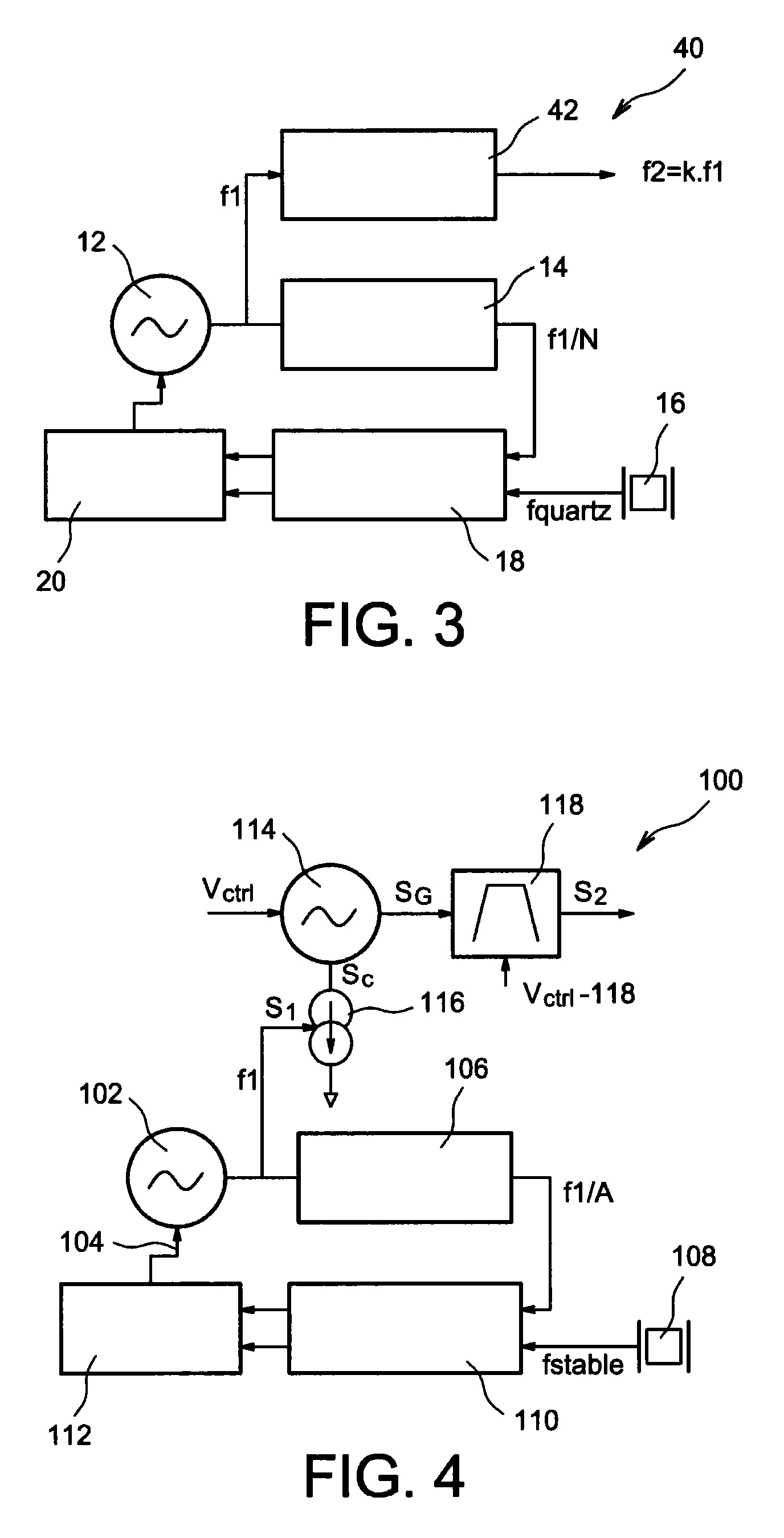

Frequency synthesis device and method

ActiveUS9209748B2Reducing consumption and sizeElectrical degradationPulse automatic controlOscillations generatorsFrequency spectrumEngineering

A frequency synthesis device including: a first generator configured to generate a periodic signal of frequency f1; a second and third generator, coupled with the first generator and configured to receive as an input the periodic signal of frequency f1 and to generate a signal SG corresponding to a train of oscillations of frequency substantially equal to N·f1, of a time less than T1=1 / f1 and repeated periodically at the frequency f1, where N is a whole number greater than 1; and a fourth generator configured to generate, from the signal SG, a periodic signal wherein a frequency spectrum includes a primary line of frequency f2=(N+i)·f1, where i is a whole number.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

Method and system for analog frequency clocking in processor cores

ActiveUS8161314B2Improve frequency performanceImprove noise immunityPulse automatic controlGenerating/distributing signalsControl dataAnalog signal

A method of and system for frequency clocking in a processor core are disclosed. In this system, at least one processor core is provided, and that at least one processor core has a clocking subsystem for generating an analog output clock signal at a variable frequency. Digital frequency control data and an analog signal are both transmitted to that at least one processor core; and that processor core uses the received analog signal and digital frequency control data to set the frequency of the output clock signal of the clocking subsystem. In a preferred implementation, multiple cores are asynchronously clocked and the core frequencies are independently set.

Owner:IBM CORP

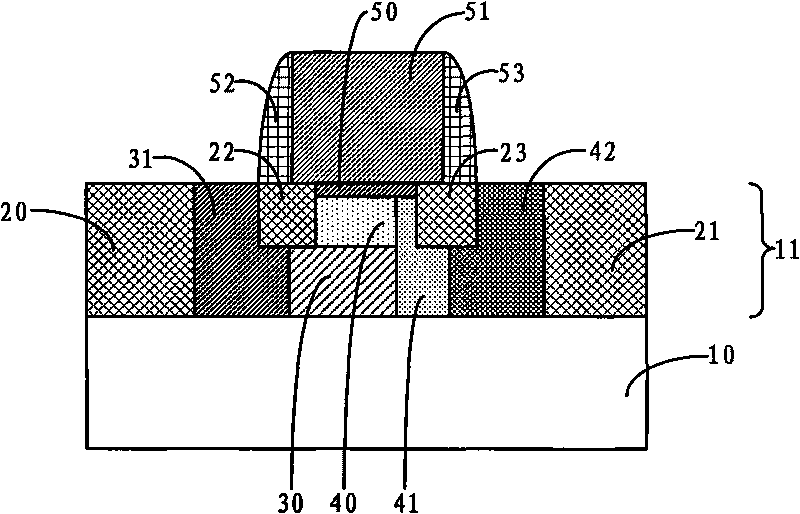

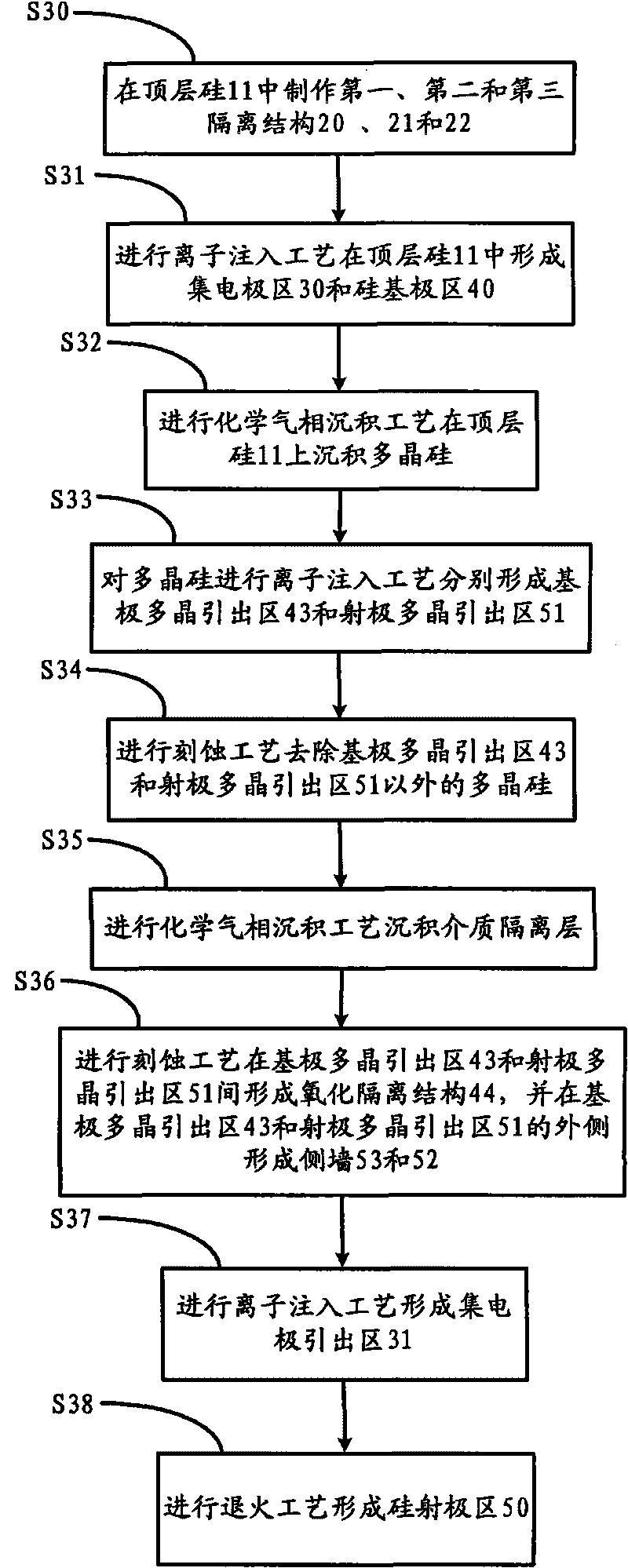

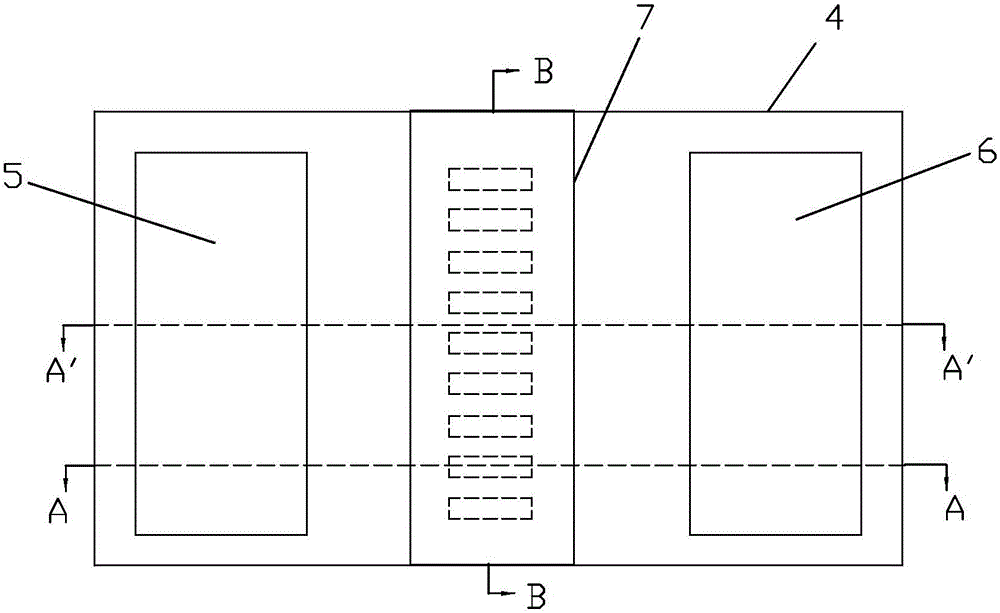

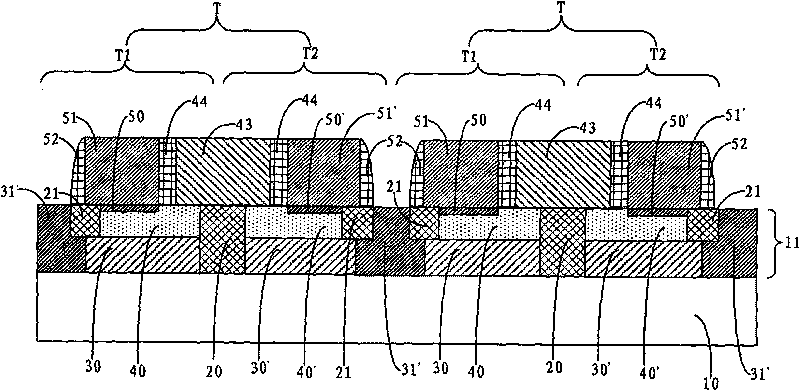

Thin SOI longitudinal bipolar transistor and manufacturing method thereof

ActiveCN101719508AOvercoming large input resistanceOvercome the problem of large inter-electrode capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The invention provides a thin SOI longitudinal bipolar transistor and a manufacturing method thereof. In the prior art, a base lead-out region is manufactured in top silicon and is connected with a silicon base region through a base connecting region, which causes the problems of complicated process, over-high base input resistance and interelectrode capacitance, and poor frequency performance ofthe transistor. The transistor of the invention, which is manufactured in the top silicon and is positioned between a first isolation structure and a second isolation structure, comprises a collectorregion, a silicon base region and a silicon emitter region which are sequentially stacked, wherein a collector lead-out region is arranged between the first isolation structure and a third isolation structure, is connected with the collector region, and is isolated from the silicon base region and the silicon emitter region through the third isolation structure; a polycrystalline base region and a polycrystalline emitter region are arranged on the top silicon in parallel; a medium isolation structure is arranged between the polycrystalline base region and the polycrystalline; the opposite outsides of the polycrystalline base region and the polycrystalline are provided with side walls; and the polycrystalline base region and the polycrystalline are connected with the silicon base region and the silicon emitter region respectively. The thin SOI longitudinal bipolar transistor and the manufacturing method thereof can reduce process complexity, effectively reduce the base input resistanceand the interelectrode capacitance, and effectively improve the frequency performance of the transistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

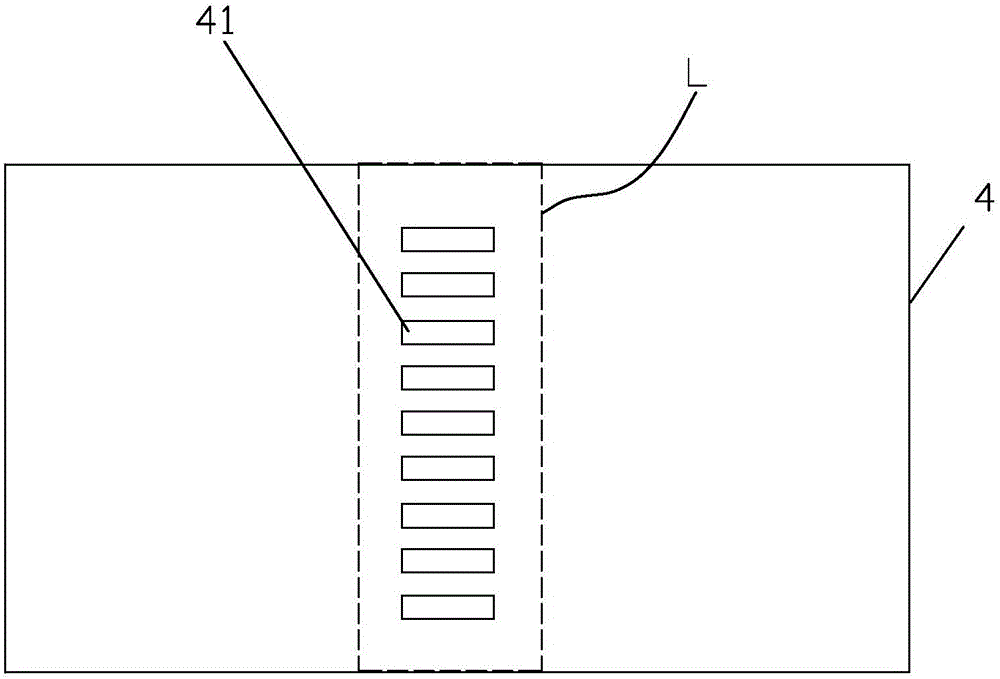

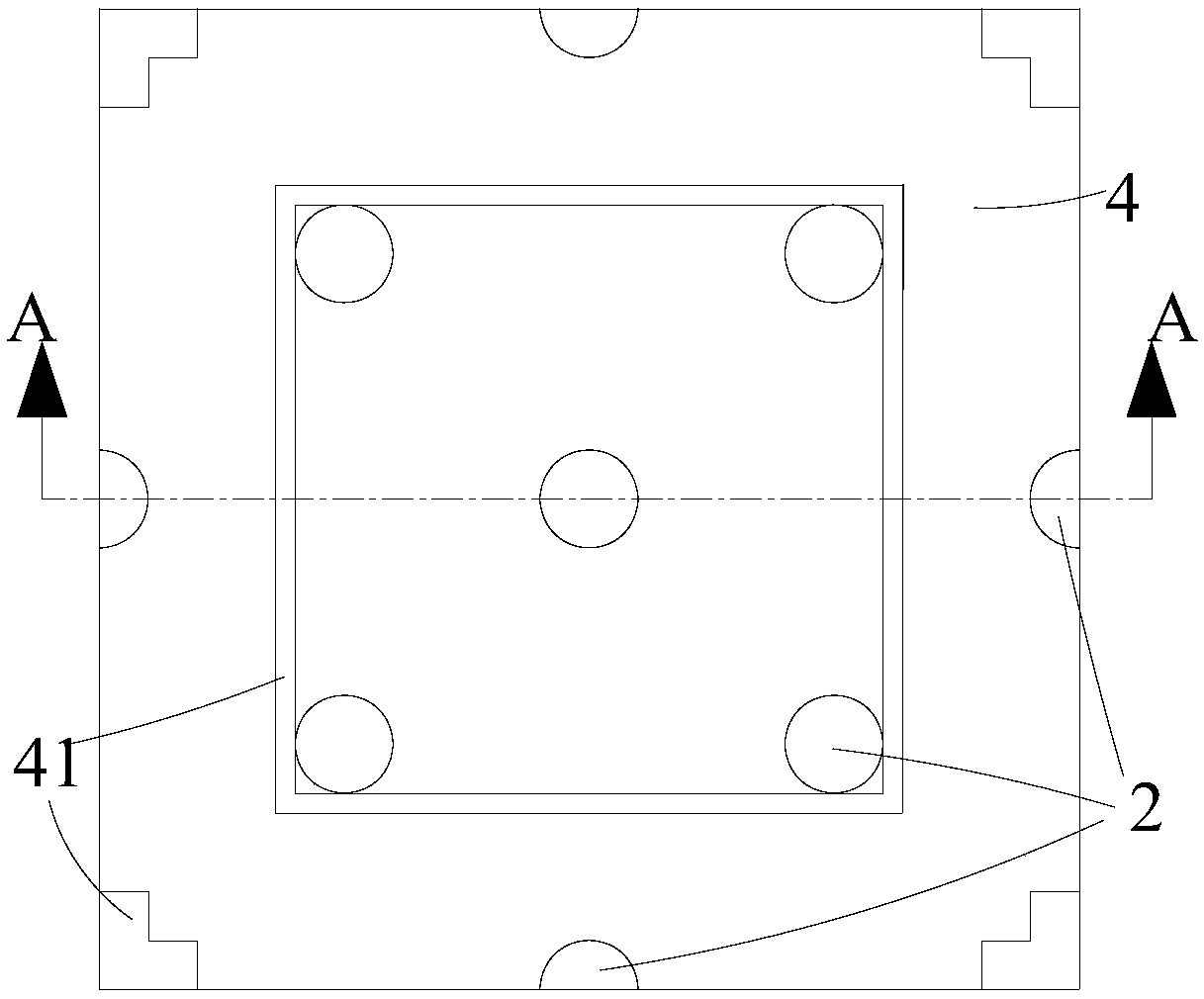

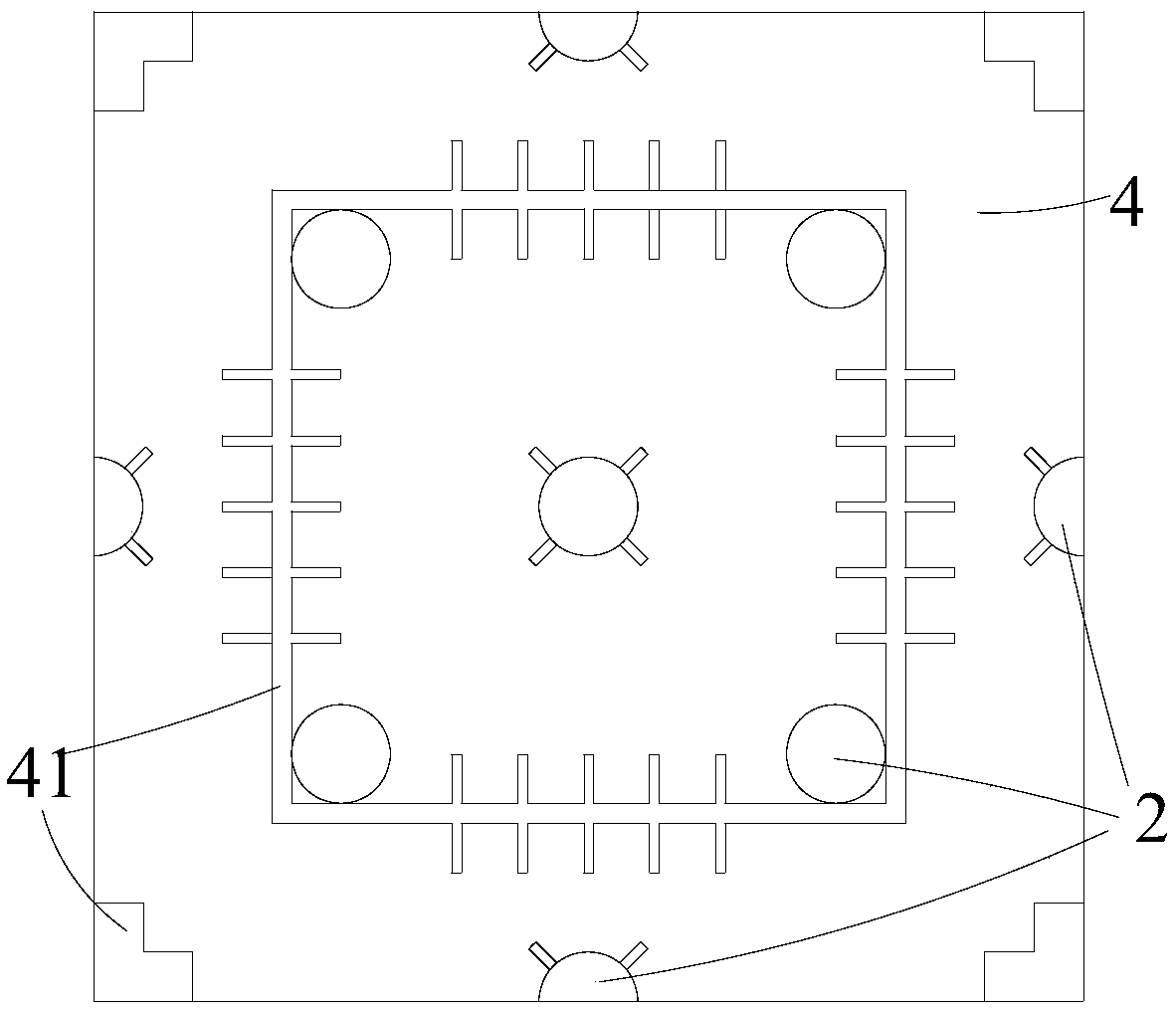

Microwave transistor of patterned grid structure and manufacturing method thereof

ActiveCN106024880AImprove gate control abilityGuaranteed current output capabilitySemiconductor/solid-state device detailsSolid-state devicesDensity reductionMicrowave

The invention discloses a microwave transistor of a patterned grid structure. The transistor is provided with a patterned region between the source electrode and the drain electrode of a barrier layer. Within the patterned region, the surface of the barrier layer partially concaves downwards along the thickness direction to form a plurality of grooves. A grid is arranged to cover the patterned region. The length of the grid is larger than the lengths of the grooves along the length direction of the grid, so that the grid can completely cover the grooves. On one hand, by means of the grooves, the grid control capability of a device is improved and the short-channel effect is suppressed. On the other hand, an original heterostructure below the grid is preserved. In this way, the reduction of the conductive capacity due to the density reduction of two-dimensional electron gas can be avoided. Therefore, the current output capability of the device is ensured while the short-channel effect is suppressed at the same time. The invention also discloses a manufacturing method of the above microwave transistor.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

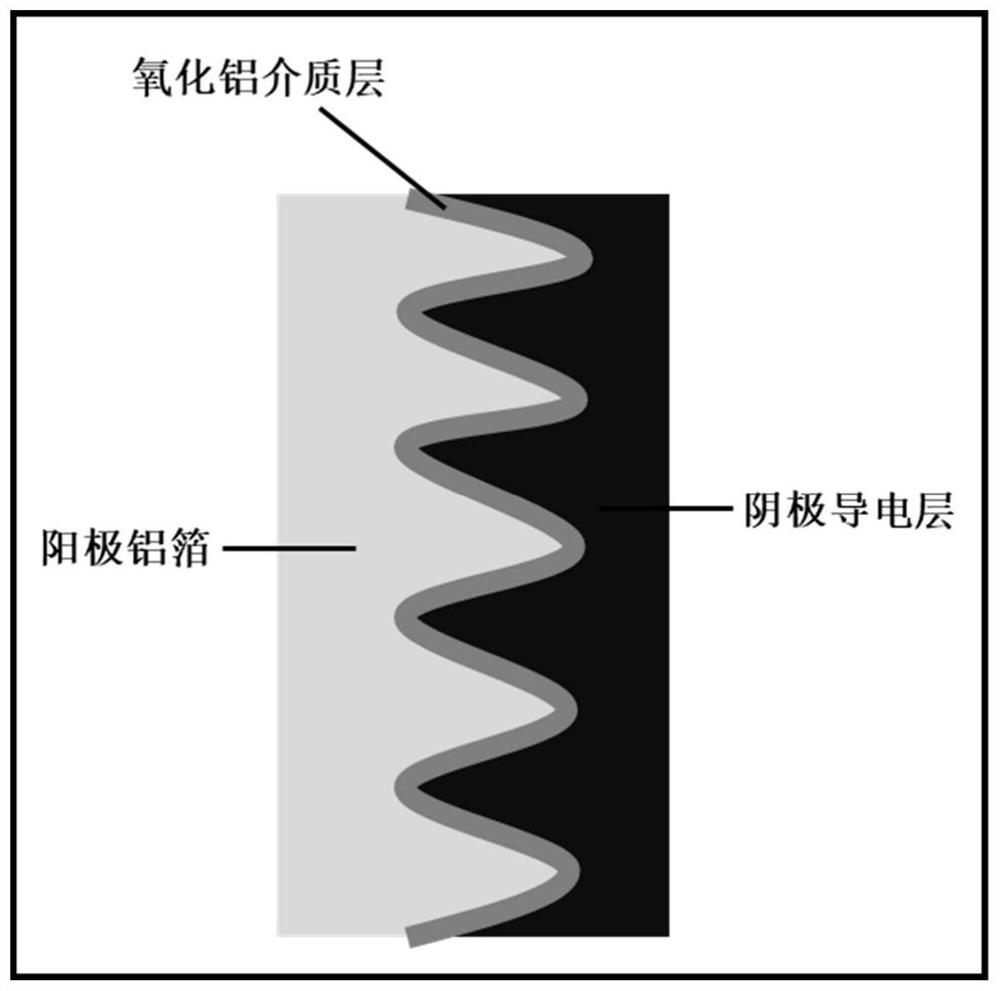

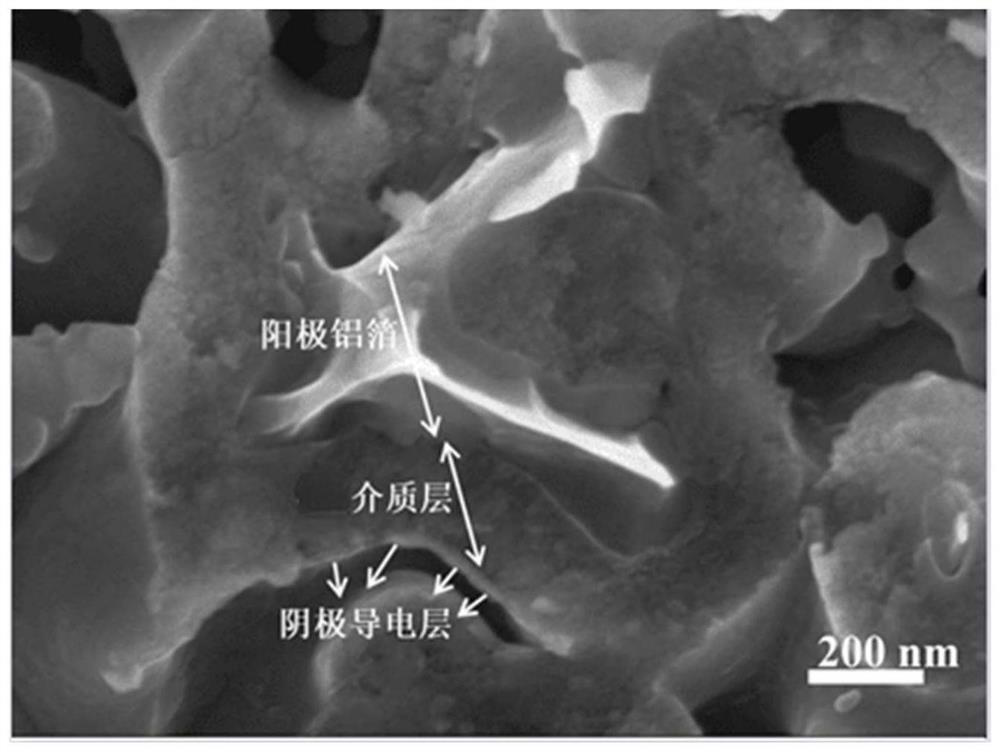

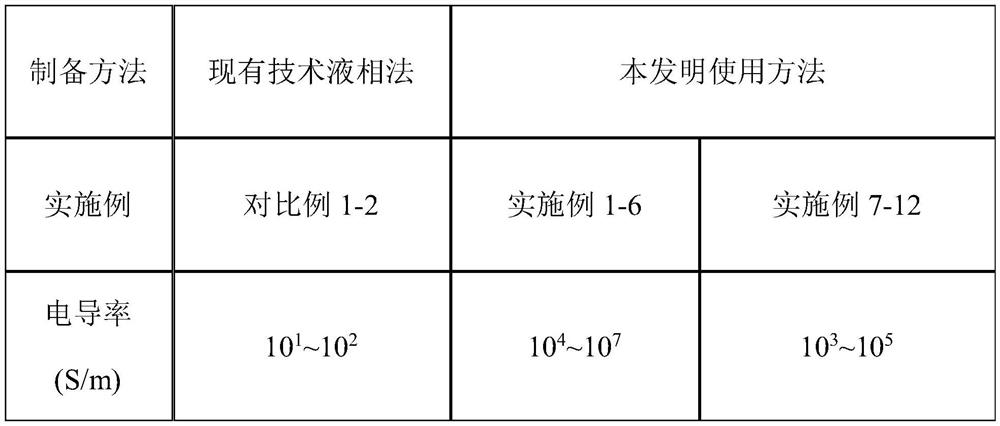

Solid aluminum electrolytic capacitor cathode conductive film and preparation method and application thereof

PendingCN113436889AIncrease capacity extraction rateImprove adhesionCapacitor electrodesMicro nanoAluminum foil

The invention discloses a solid aluminum electrolytic capacitor cathode conductive film and a preparation method and application thereof, and belongs to the field of aluminum electrolytic capacitors. The method comprises the following steps: depositing a conductive metal film on the surface of an anode foil dielectric layer of the aluminum electrolytic capacitor by using a vapor deposition method; and leading out a cathode electrode from the deposited conductive layer, namely preparing the conductive film on the surface of the anode foil dielectric layer of the aluminum electrolytic capacitor. According to the gas phase chemical method, the problem that solution molecules are difficult to enter micro holes in the surface of the anode aluminum foil in a liquid phase method is solved, so that the conductive film has high step coverage rate in the micro-nano holes, and the capacity extraction rate of the capacitor is improved. The conductive thin film prepared by adopting the gas phase chemical method has the advantages of compact structure, few impurities, good uniformity and the like.

Owner:XI AN JIAOTONG UNIV

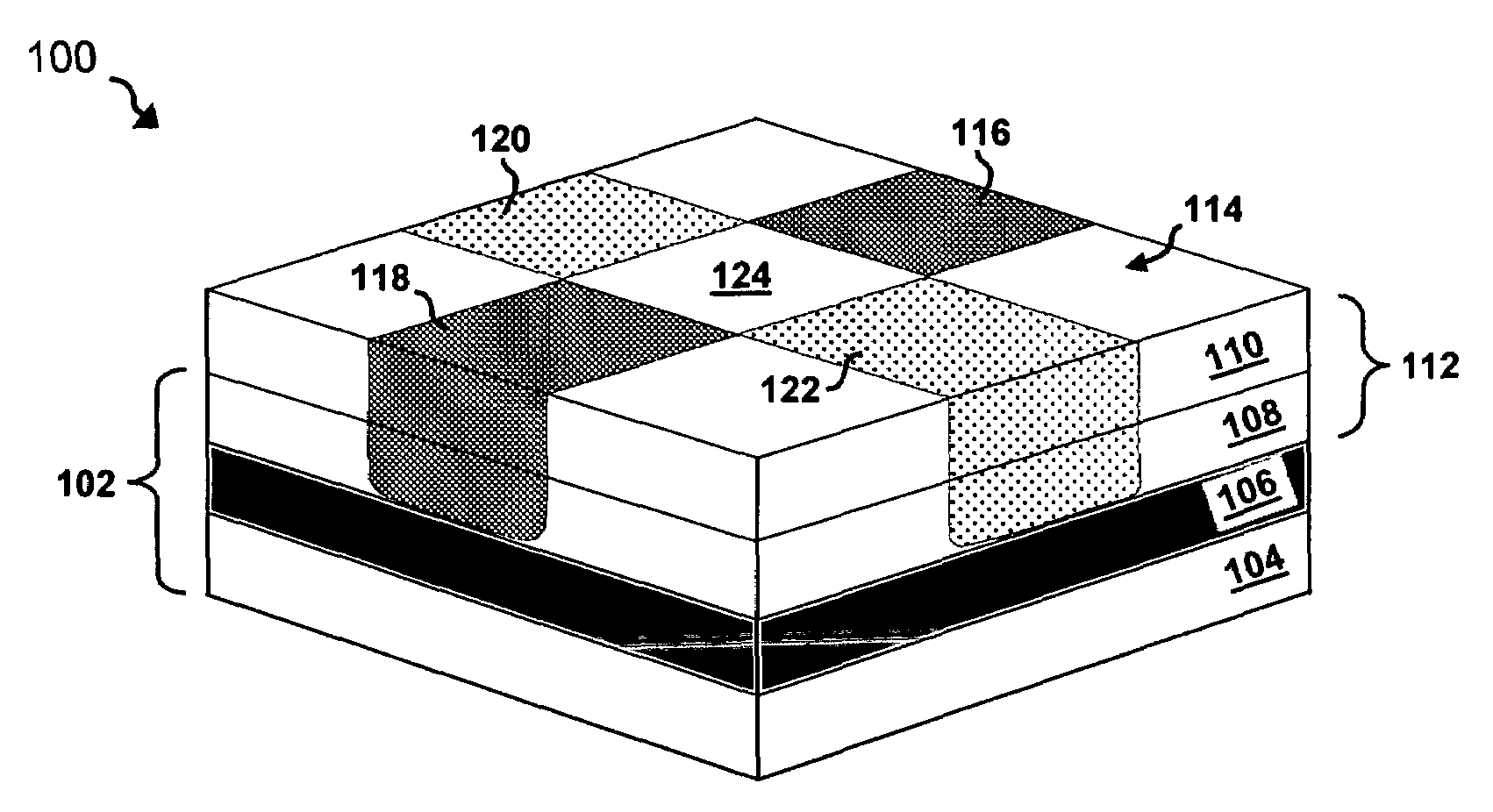

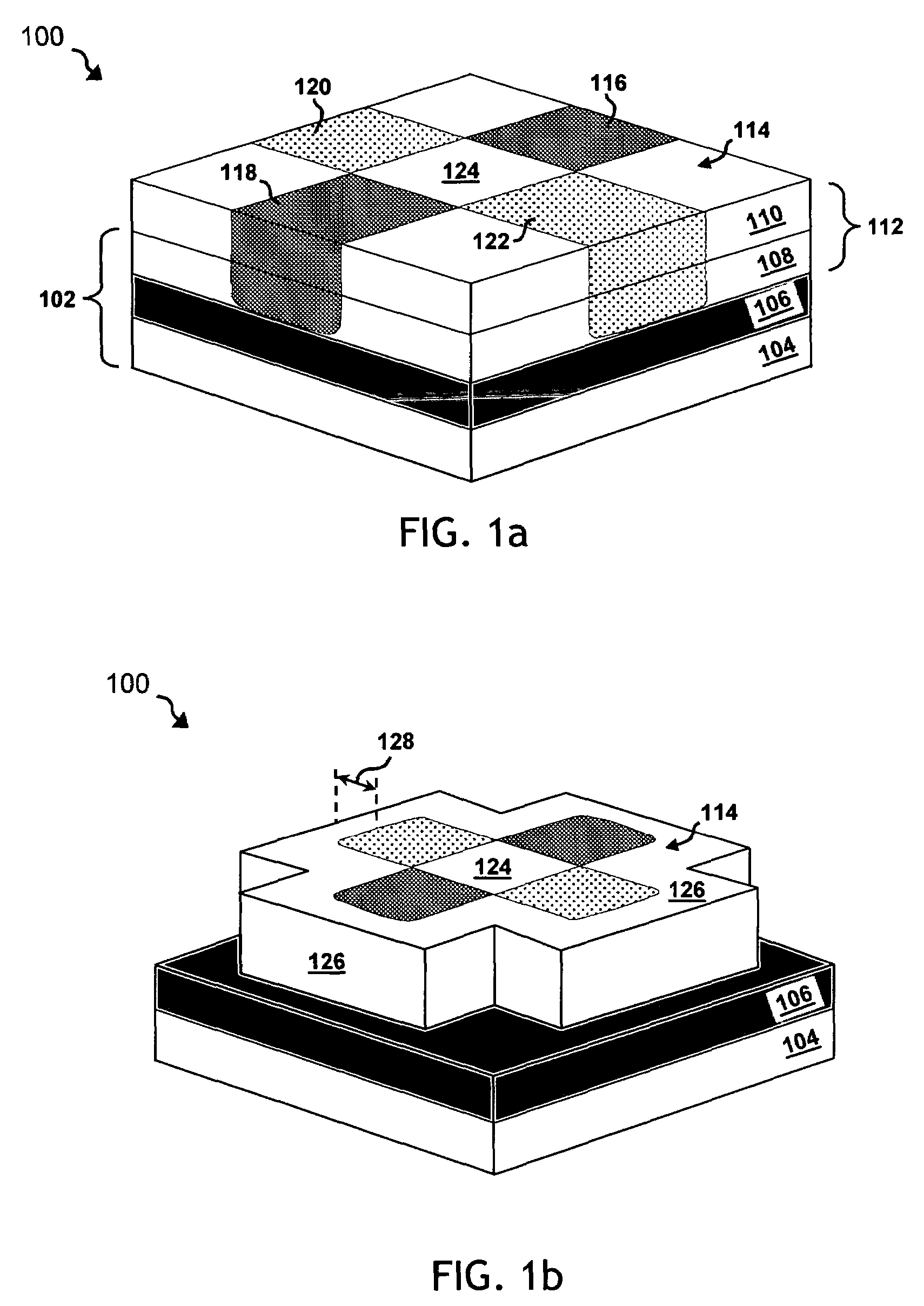

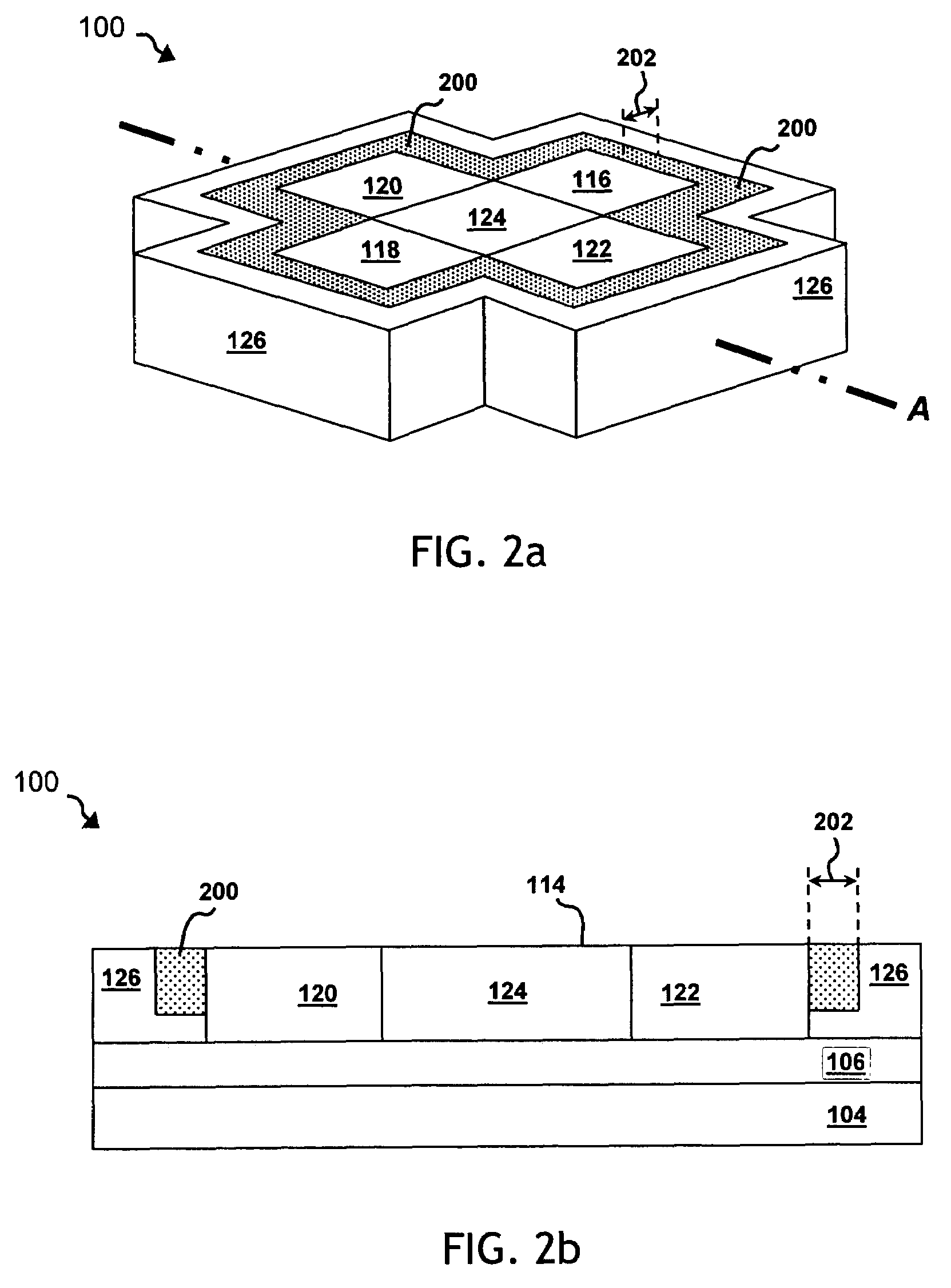

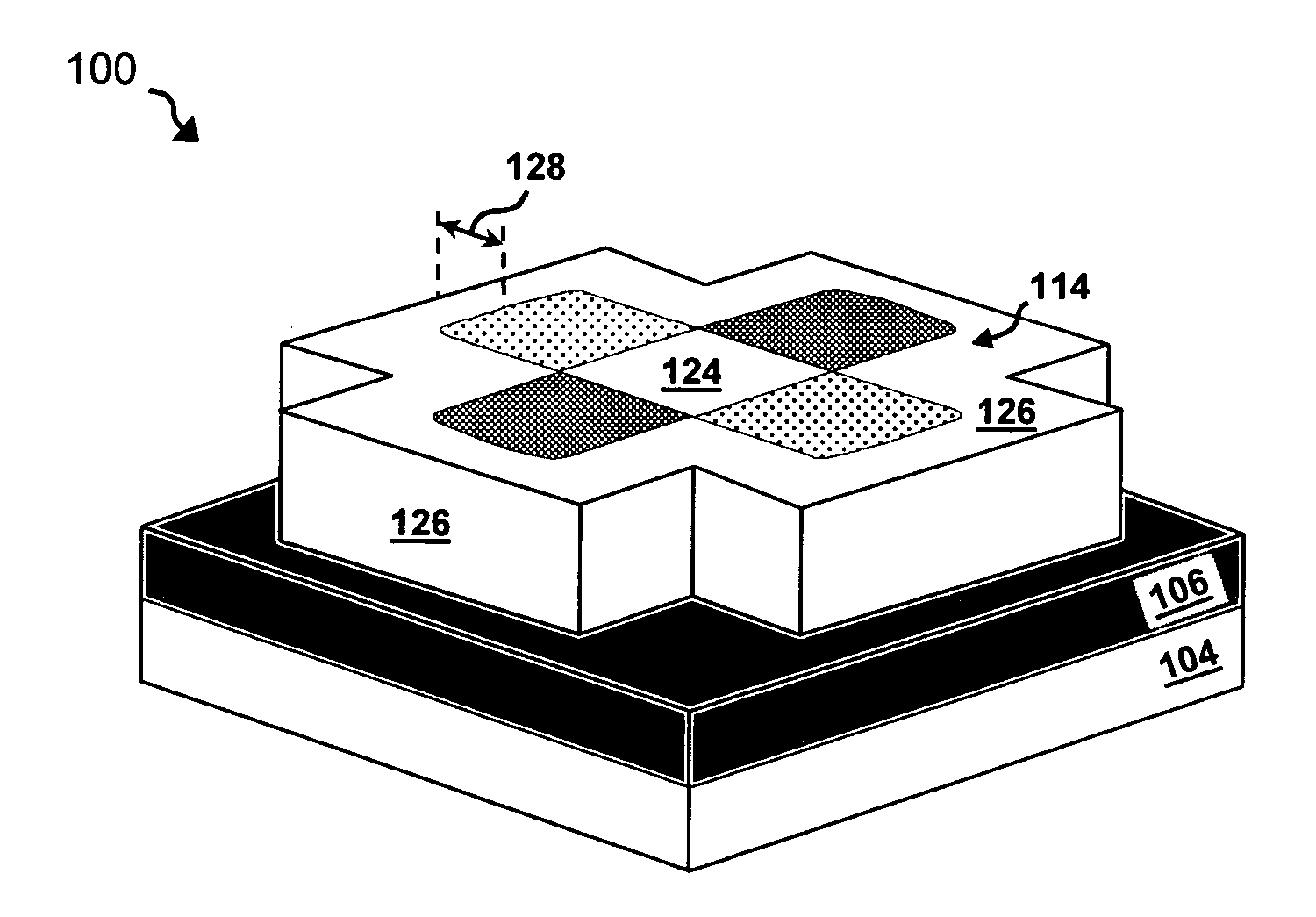

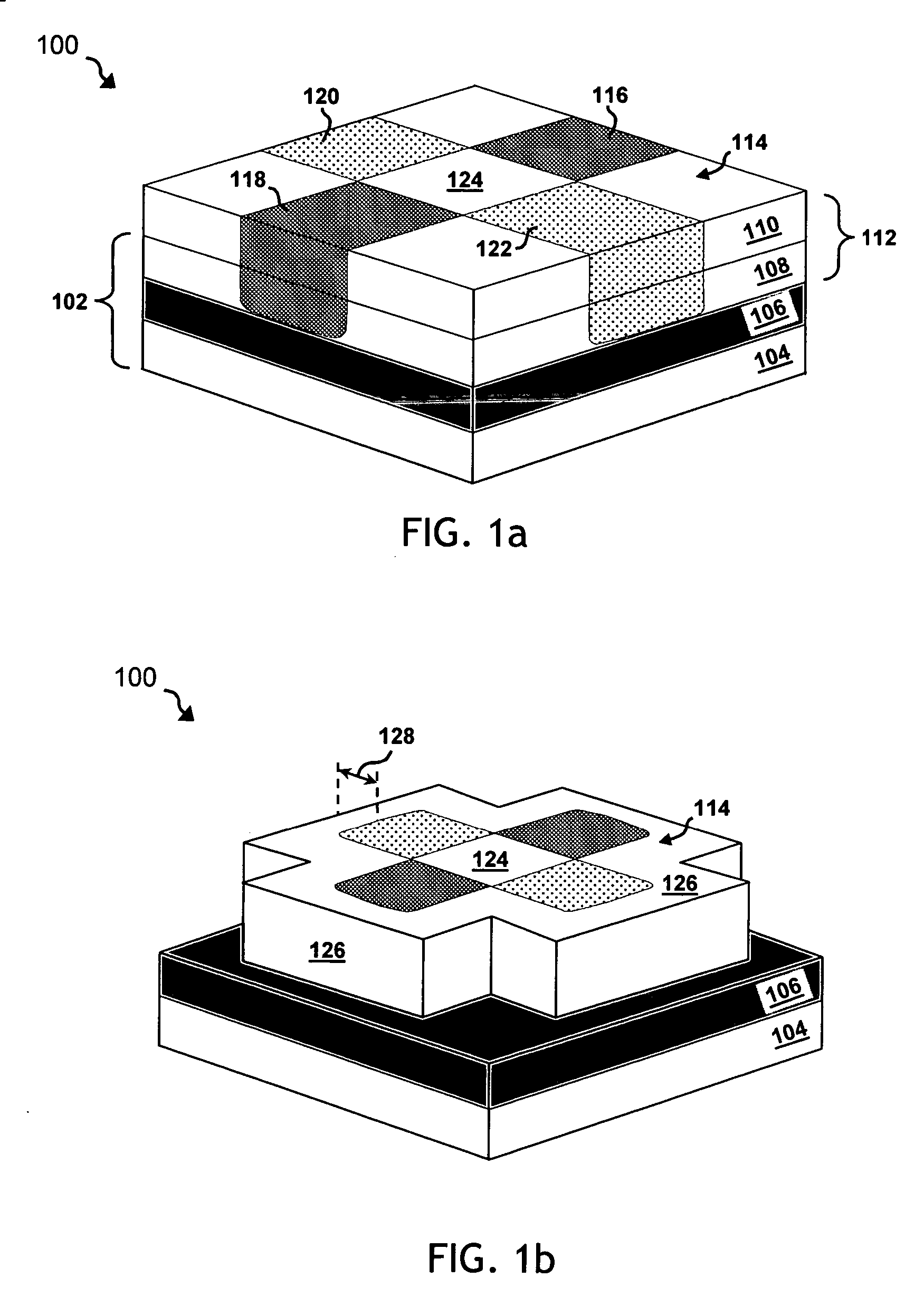

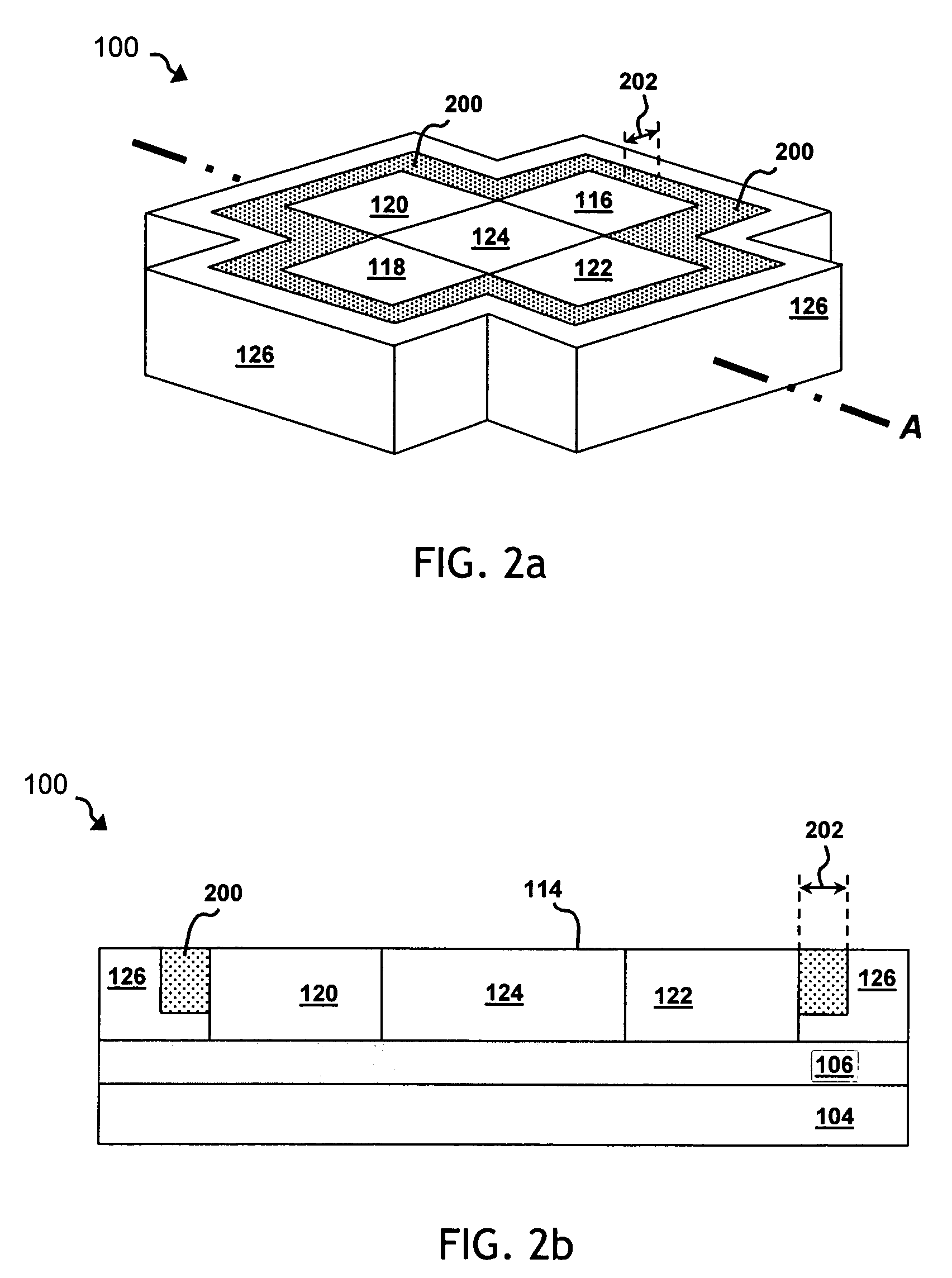

Versatile system for cross-lateral junction field effect transistor

ActiveUS7288800B2Easy to adaptEasy to produceThyristorSolid-state devicesField-effect transistorSemiconductor

The present invention provides a system for providing a cross-lateral junction field effect transistor (114) having desired high-performance desired voltage, frequency or current characteristics. The cross-lateral transistor is formed on a commercial semiconductor substrate (102). A channel structure (124) is formed along the substrate, having source (120) and drain (122) structures laterally formed on opposites sides thereof. A first gate structure (116) is formed along the substrate, laterally adjoining the channel structure orthogonal to the source and drain structures. A second gate structure (118) is formed along the substrate, laterally adjoining the channel structure, orthogonal to the source and drain structures and opposite the first gate structure.

Owner:TEXAS INSTR INC

Conversion of an antenna to multiband using current probes

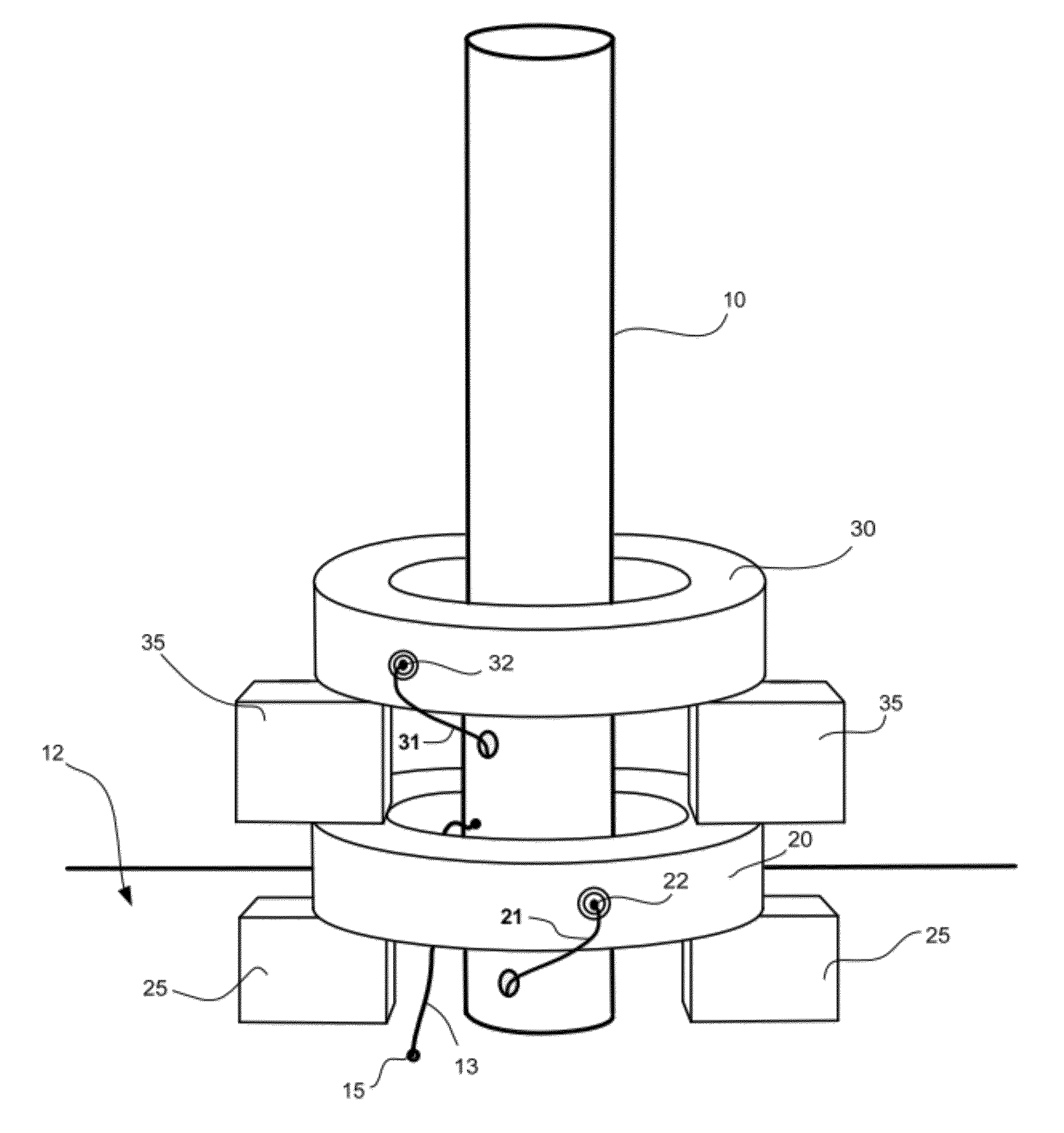

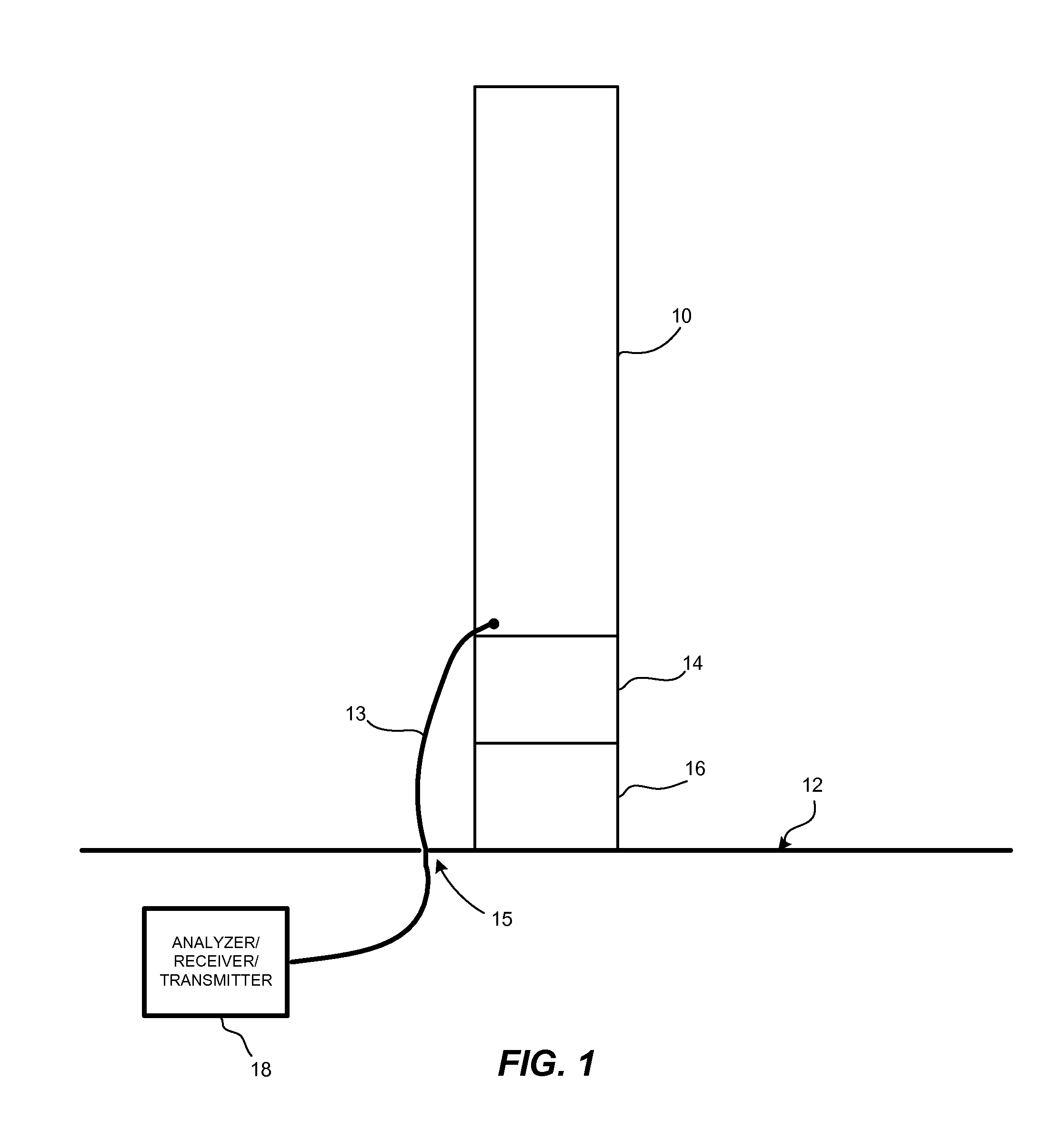

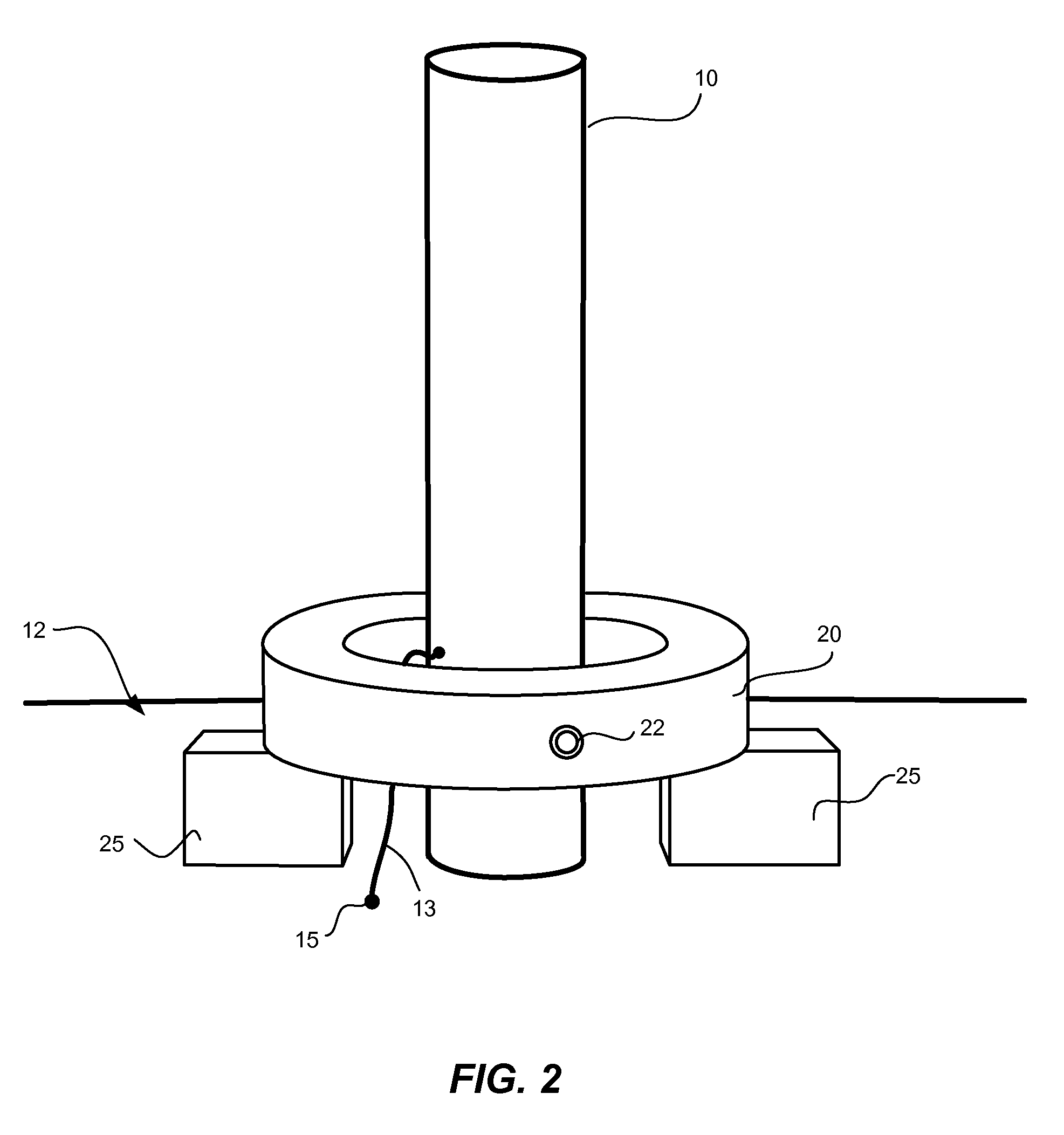

InactiveUS8164534B1Enhancing voltage standing wave ratioImprove frequency performanceSimultaneous aerial operationsAntenna adaptation in movable bodiesMulti bandPower flow

A multi-band antenna comprising a conductive structure and a plurality of current probes coupled around the conductive structure is disclosed. An existing antenna capable of generating H fields having a first signal line is converted into a multi-signal line antenna with increased frequency capabilities, by mounting a first current probe having a designated frequency range about a periphery of the existing antenna; coupling a second signal line to the first current probe; and performing at least one of transmitting and receiving via at least one of the first and second signal lines, wherein the mounting of the first current probe to the existing antenna improves a voltage standing wave ratio (VSWR) of the existing antenna and the second signal line operates as an independent signal line for signal reception / transmission within the designated frequency range.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

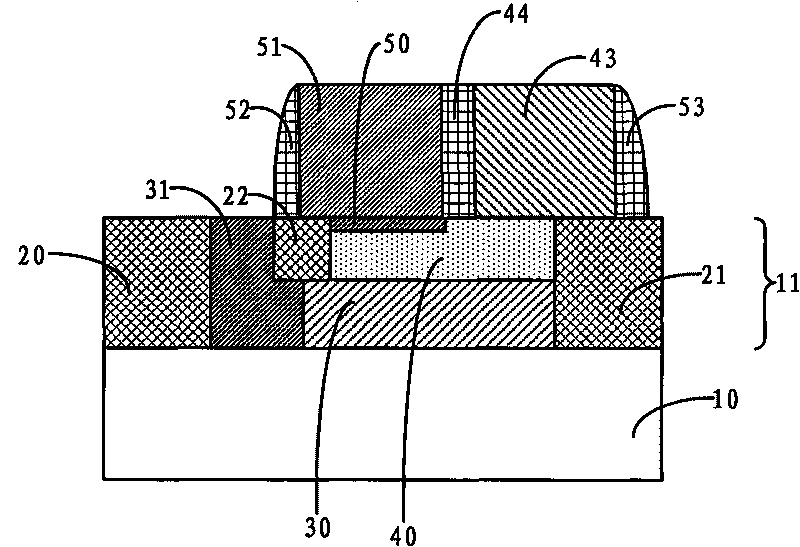

Co-electrode thin SOI longitudinal bipolar transistor device and manufacturing method thereof

ActiveCN101719503AHighly integratedIncrease working currentSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceEngineering

The invention provides a co-electrode thin SOI longitudinal bipolar transistor device and a manufacturing method thereof. In the prior art, the transistors does not share an electrode so as to cause incompact device structure and low integration degree, and in addition, the base leading-out area is connected with the silicon base area through the base connecting area so as to cause complex process, high base input resistance and poor frequency performance. The device of the invention comprises a plurality of transistor units provided with first and second transistors; both the first and second transistors have a collector area, a silicon base area and a silicon emitter area which are overlapped in the top silicon in turn and a polycrystalline emitter area arranged on the top silicon; a shared polycrystalline base area is connected with the silicon base areas of the first and second transistors, arranged between the polycrystalline emitter areas of the first and second transistors, and isolated with the polycrystalline emitter areas through a medium isolation structure; and a shared collector leading-out area is arranged between two adjacent transistor units, and two ends of the shared collector leading-out area are connected with the collector areas at two sides respectively. The device has the advantages of compact structure, high integration degree, low base input resistance and good frequency performance.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

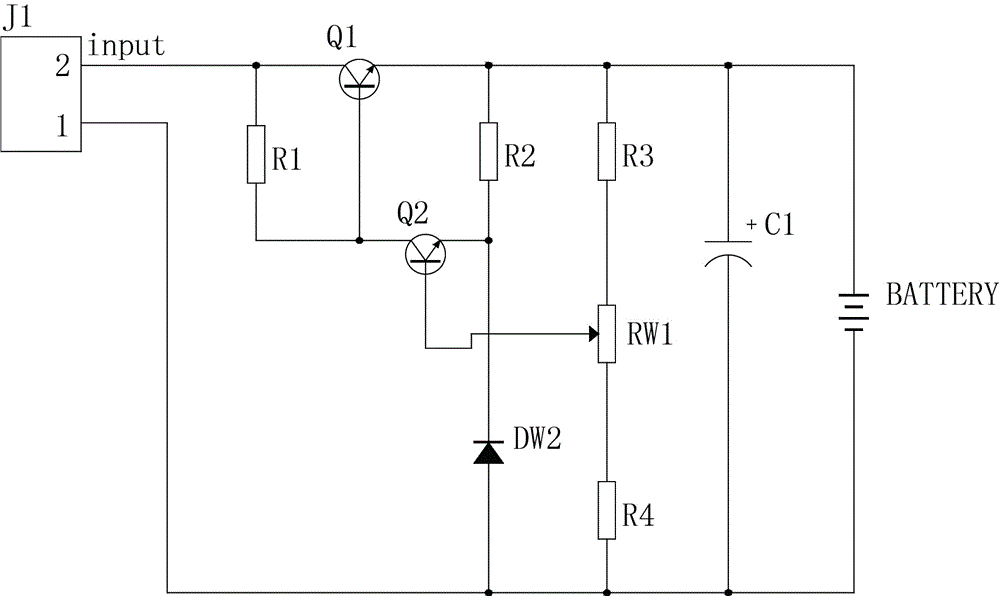

Battery charging circuit

InactiveCN105553008AProtection lifeReduce input currentBatteries circuit arrangementsElectric powerBattery chargePower flow

The invention discloses a battery charging circuit. An input current can be reduced at a high voltage by comparing a group of bleeder circuits with a fixed voltage through a triode and controlling an input by a high-current triode, so that the role in protecting the lifetime of a battery is put into play.

Owner:NINGBO AMBON EMERGENCY PROD

Versatile system for cross-lateral junction field effect transisor

ActiveUS20060151804A1Easy to adaptHighly versatileSolid-state devicesSemiconductor devicesEngineeringField-effect transistor

The present invention provides a system for providing a cross-lateral junction field effect transistor (114) having desired high-performance desired voltage, frequency or current characteristics. The cross-lateral transistor is formed on a commercial semiconductor substrate (102). A channel structure (124) is formed along the substrate, having source (120) and drain (122) structures laterally formed on opposites sides thereof. A first gate structure (116) is formed along the substrate, laterally adjoining the channel structure orthogonal to the source and drain structures. A second gate structure (118) is formed along the substrate, laterally adjoining the channel structure, orthogonal to the source and drain structures and opposite the first gate structure.

Owner:TEXAS INSTR INC

Board-to-board connector

InactiveUS7086868B2Improve performanceLow costPrinted circuit assemblingCross-talk/noise/interference reductionBoard-to-board connectorConductive materials

The disclosed connector and method transfers high frequency signals from one circuit board to another circuit board, while maintaining good electrical and mechanical performance, at a significantly reduced cost. The connector includes a body member and a conductive pin extending through a center portion of the body member to opposing planar surfaces. An arcuate contact member is positioned within the body member and circumferential to at least a portion of the conductive pin. A flexible conductive material is positioned on an opposing surface and engages the arcuate contact member such that the connector can be positioned between cooperating circuit boards, allowing the conductive pin and arcuate contact member to operatively engage the circuit boards for passing signals therebetween.

Owner:REVEAL IMAGING

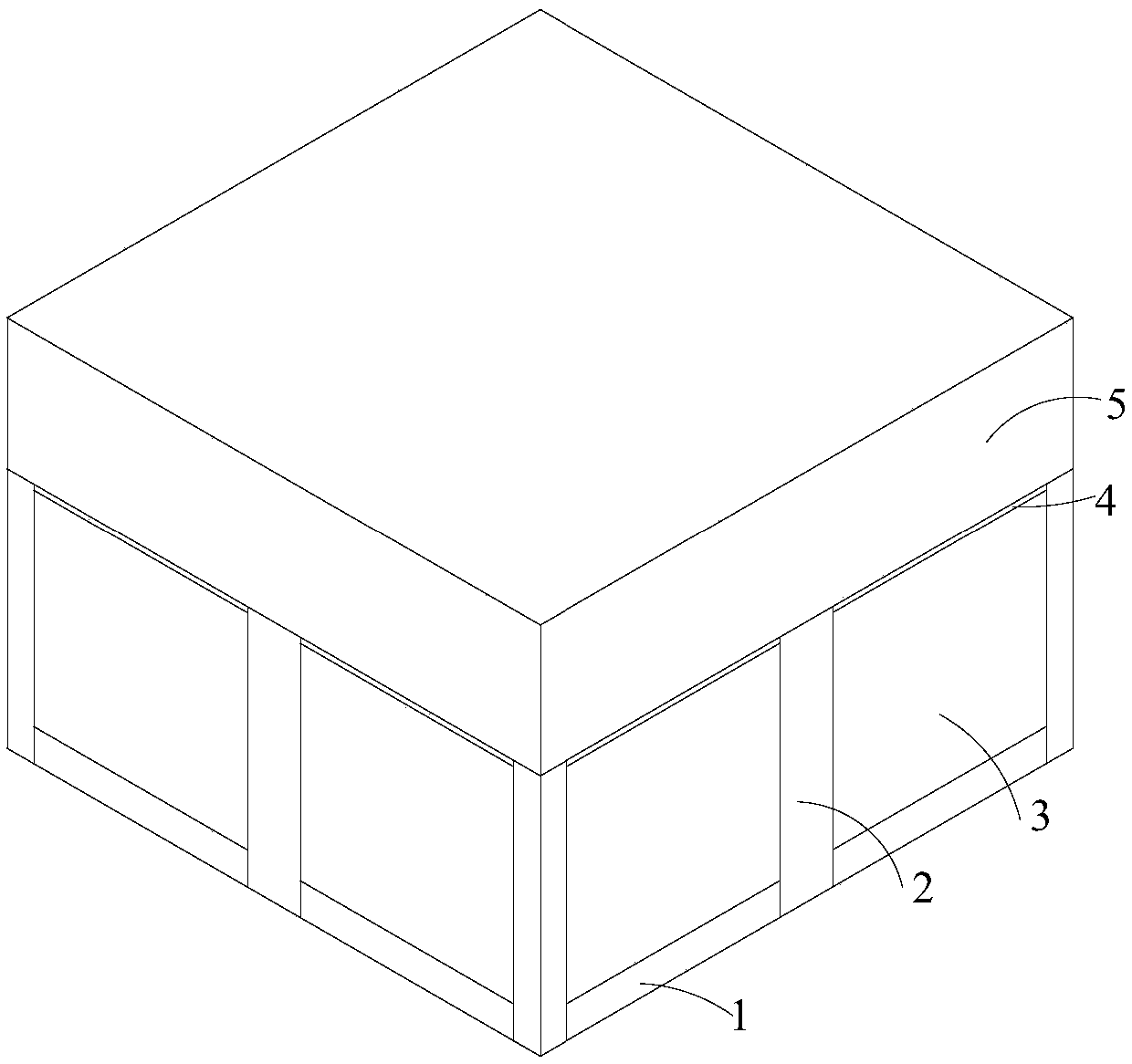

Enhanced wave absorbing material structure body

PendingCN109586041AEfficient removalSolve the problem of insufficient reflectivityAntennasEngineeringStructural unit

The invention relates to the technical field of wave absorbing materials and particularly provides an enhanced wave absorbing material structure body. The enhanced wave absorbing material structure body is formed by periodically splicing a plurality of identical structural units, each of the structural units comprises a heat dissipating bottom plate, a first wave absorbing material stacked on theheat dissipating bottom plate, a carrier plate stacked on the surface of the first wave absorbing material, a plurality of heat transfer bodies which pass through the first wave absorbing material from the heat dissipating bottom plate and is in contact with the carrier contact, a reflection enhancement layer which is stacked on the surface of the carrier in a patterned way and is in contact withthe heat transfer bodies, and a second wave absorbing material which is stacked on the reflection enhancement layer and a surface of the carrier which is not covered by the reflection enhancement layer. The enhanced wave absorbing material structure body of the invention has good heat dissipating performance and good wave absorbing performance, and the problem that a flat wave absorbing material has insufficient reflectance at a low frequency is solved.

Owner:深圳唯创微波技术有限公司

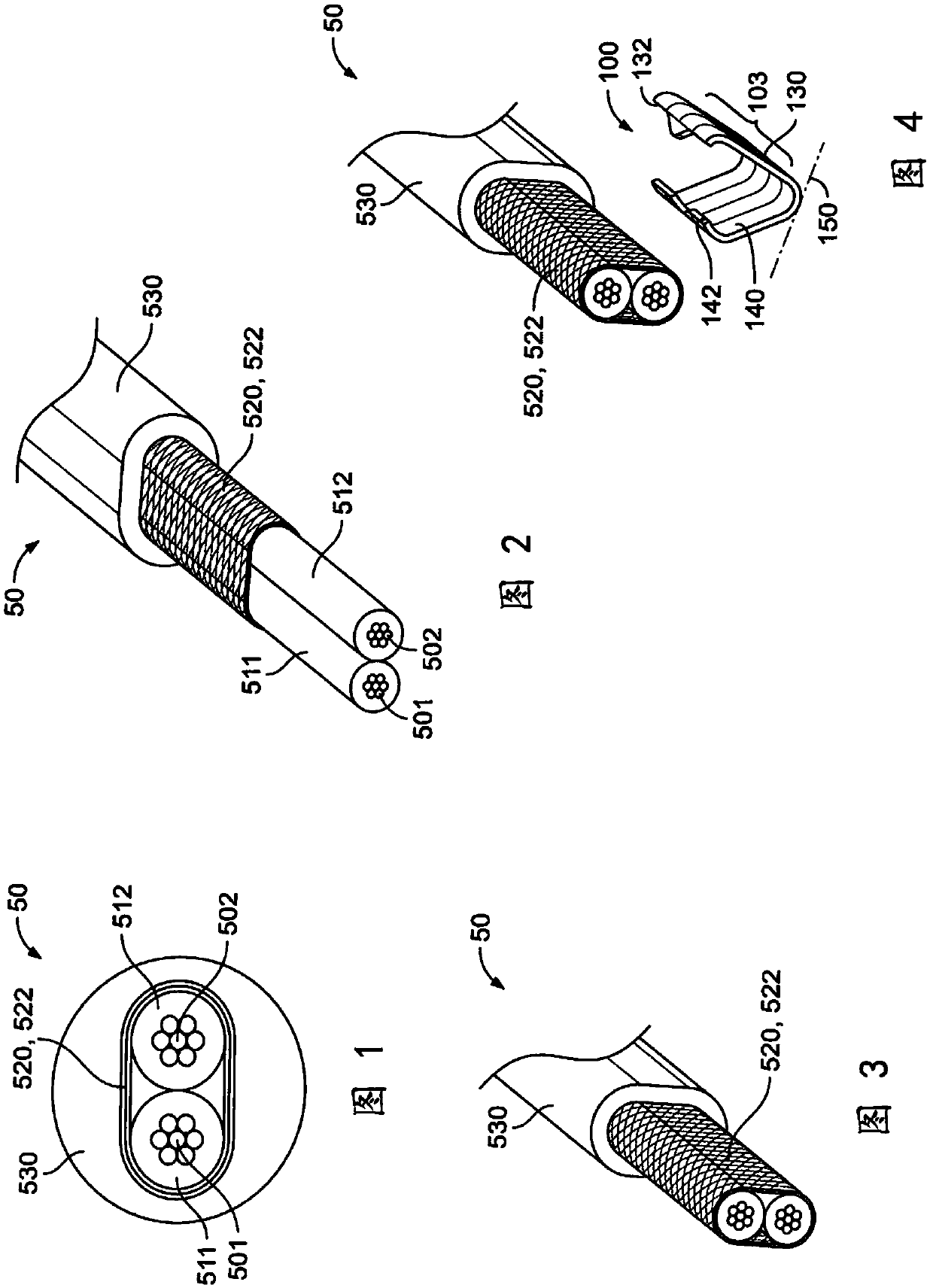

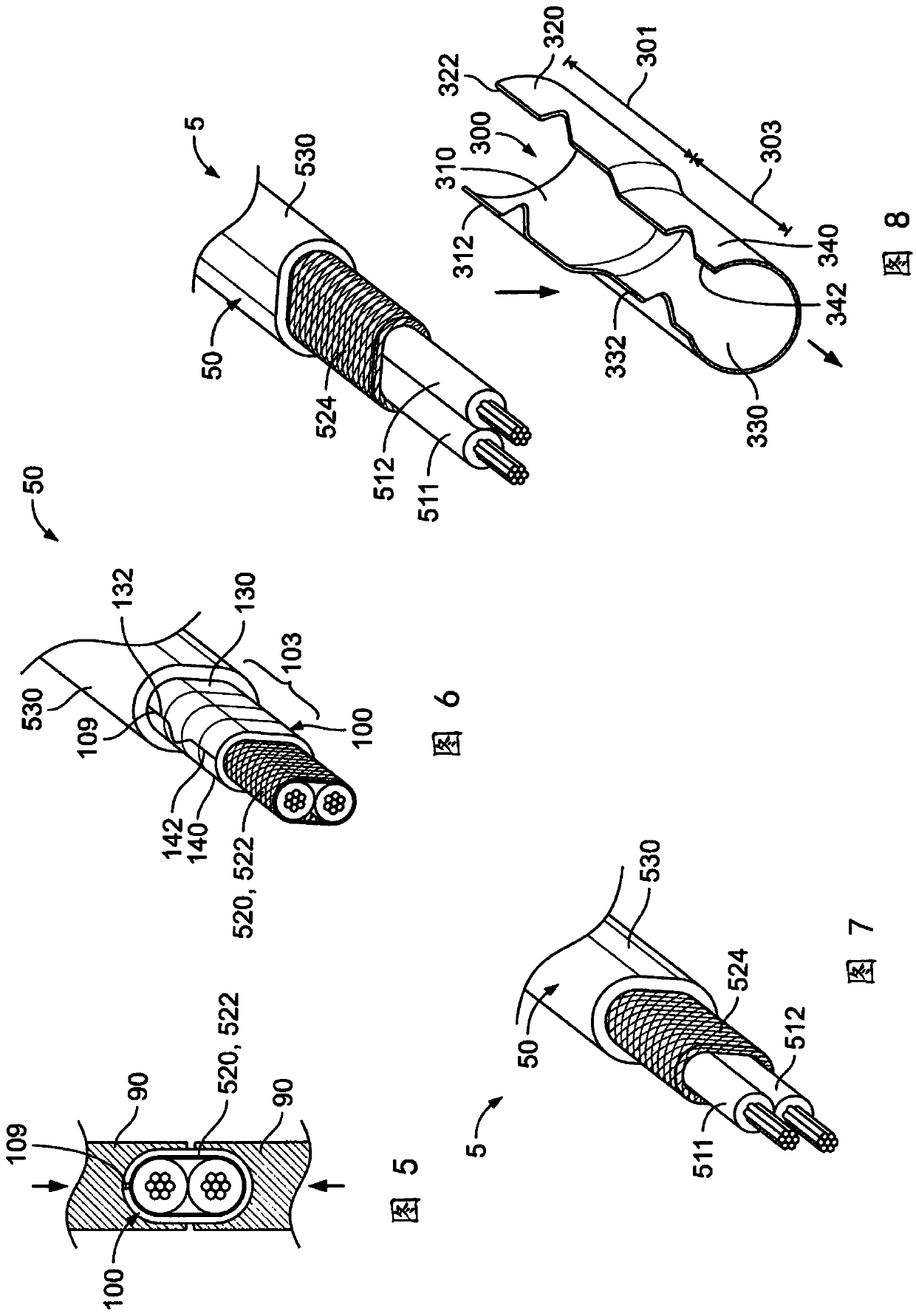

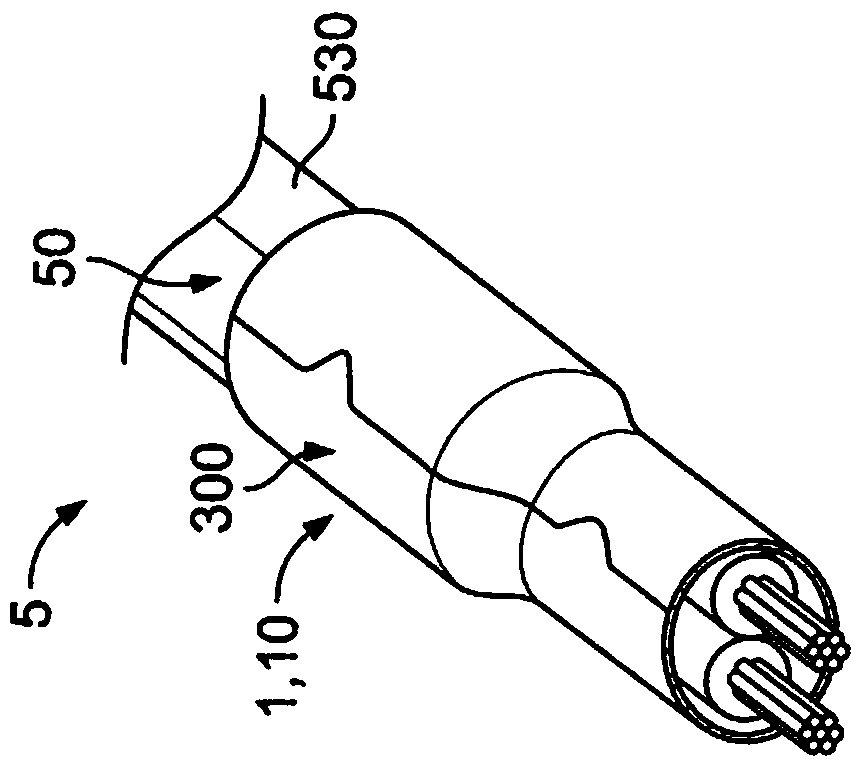

Electrical contact device, electrical connecting unit and method for assembling electrical cable

ActiveCN109546361AImprove frequency performanceSave installation spaceCoupling device detailsInsulated cablesAutomotive industryElectrical contacts

The invention relates to an electrical contact device (300), in particular to a twin-axial contact device, preferably a ferrule or a shield contact sleeve, for an electrical cable (50) , in particulara twin-axial cable for the automotive industry which comprises crimping sections (301, 303) with openings, in a crimped state of the contact device at / on the cable, the crimping sections (301, 303) which are closed and oval in crimping sections are installed at / on the cable by means of the crimping sections. The invention further relates to a method for assembling an electrical cable, in particular a twin-axial cable, for the automotive industry, wherein when assembling the cable (50), an open crimping section (301, 303) of an electrical contact device or an electrical connecting unit (10) at / on the cable is transformed into a closed crimping section at / on the cable, when transforming the open crimping sections into the closed crimping section, a crimping section which is oval in cross-sections and closed is installed at / on the cable.

Owner:TE CONNECTIVITY GERMANY GMBH