Co-electrode thin SOI longitudinal bipolar transistor device and manufacturing method thereof

A technology of bipolar transistors and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as low integration, low operating current, and large inter-electrode capacitance, and reduce process complexity degree, increase the working current, improve the effect of frequency performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The common electrode thin SOI vertical bipolar transistor device and its manufacturing method of the present invention will be further described in detail below.

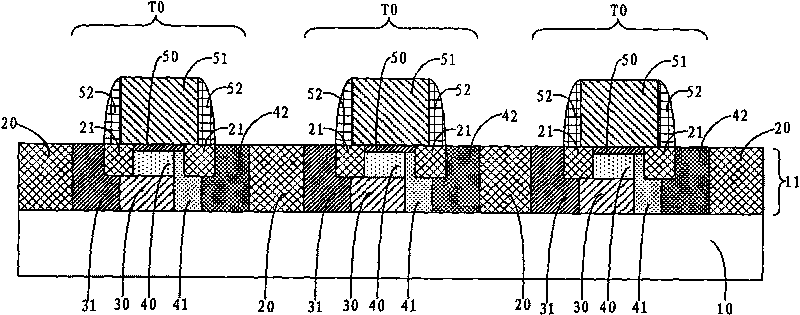

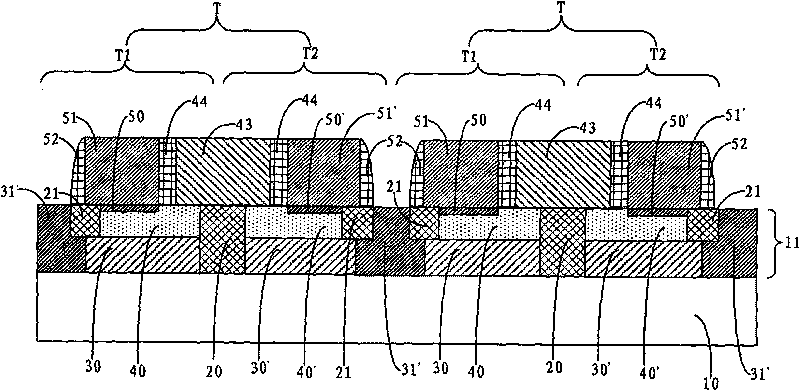

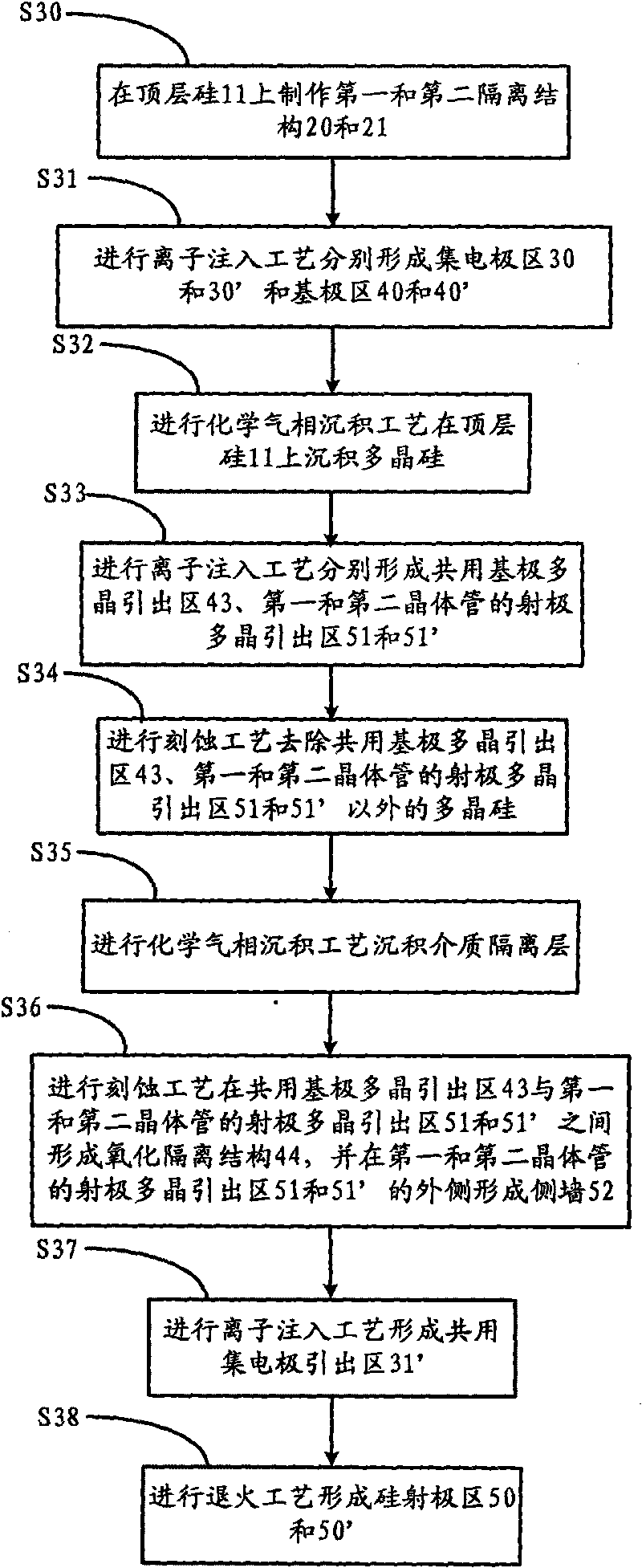

[0028] see figure 2 , which shows the composition structure of the common electrode thin SOI vertical bipolar transistor device of the present invention, as shown in the figure, the common electrode thin SOI vertical bipolar transistor device is fabricated in the top layer silicon 11, including a plurality of transistor units T , each transistor unit T includes first and second transistors T1 and T2 of the same type, the top layer silicon 11 is fabricated on the insulating buried layer 10, the top layer silicon 11 has first and second isolation structures 20 and 21, the insulating buried layer Below 10 is a silicon substrate (not shown), and the insulating buried layer 10 is usually silicon oxide. The first isolation structure 20 is a shallow trench isolation structure (STI), and the second isolation struct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More