Bipolar transistor manufacturing method

a manufacturing method and technology of bipolar transistor, applied in the direction of transistors, electrical devices, semiconductor devices, etc., can solve the problems of mos transistor manufacturing methods, 1 is its bulk, and the depth is not compatible with the latest methods for manufacturing mos transistors, and achieves high frequency performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

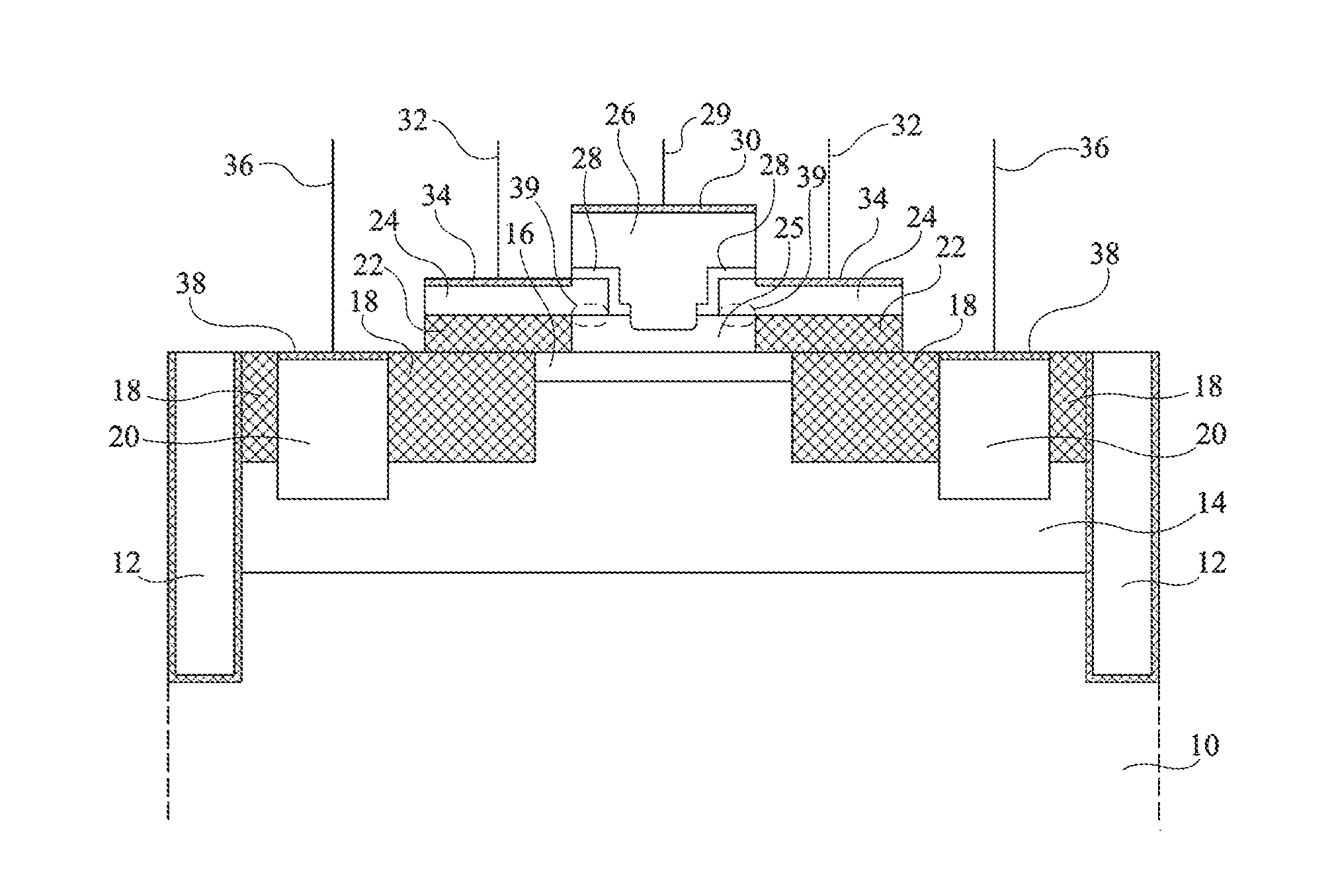

[0044]A method for manufacturing a bipolar transistor on a FD-SOI-type substrate is here provided. FIGS. 2 to 18 illustrate results of steps of such a method.

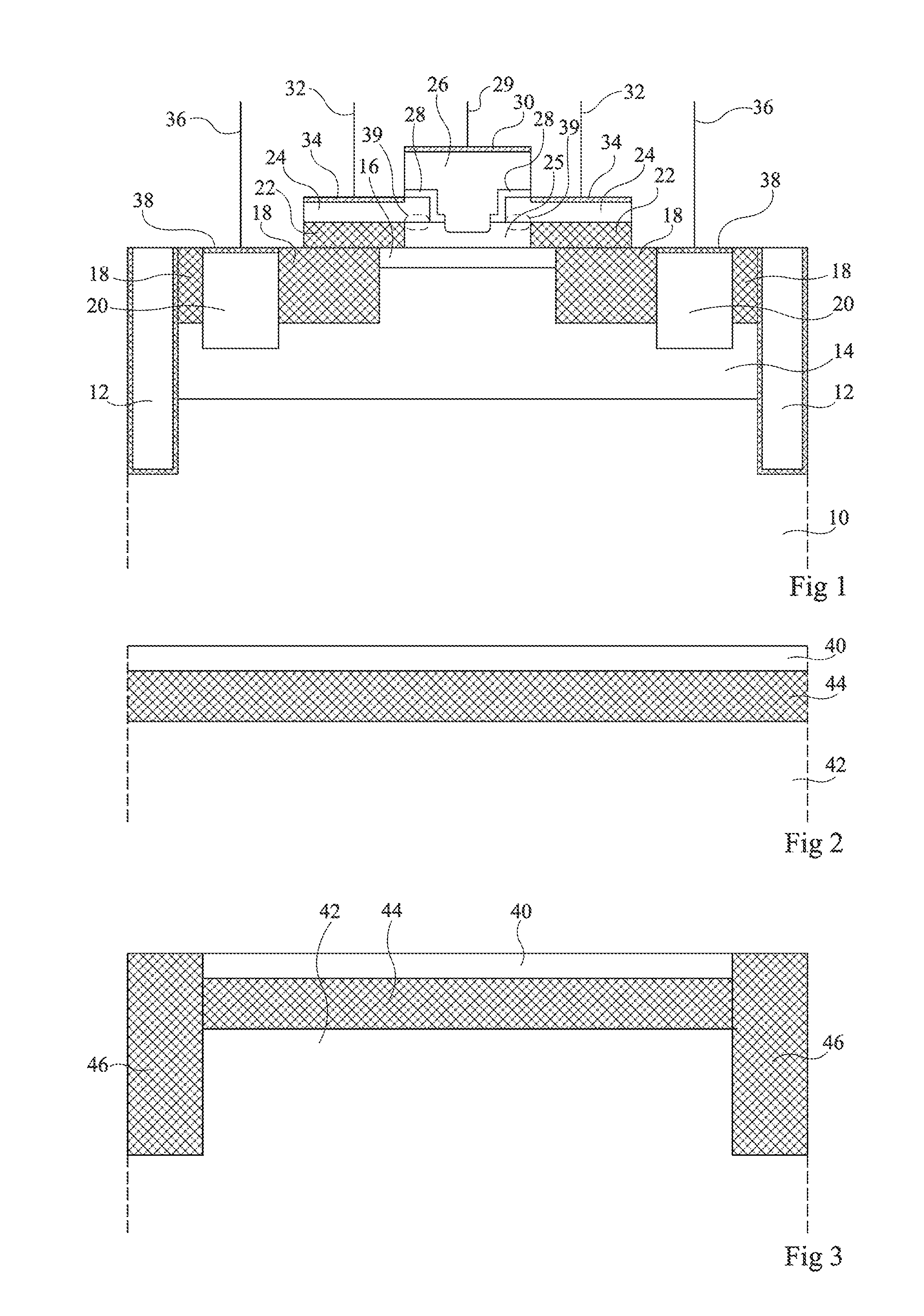

[0045]At a step illustrated in FIG. 2, it is started from a structure of FD-SOI type comprising an upper semiconductor layer 40 which extends on a semiconductor substrate 42 with an interposed insulating layer 44. Conventionally, such structures have an insulating layer 44 with a thickness ranging between 10 and 50 nm, for example, 25 nm, and a fully-depleted upper layer 40 with a thickness ranging between 5 and 15 nm, for example, 10 nm.

[0046]At a step illustrated in FIG. 3, shallow insulating trenches 46 (STI trenches) which cross semiconductor layer 40, insulating layer 44, and which penetrate in depth into semiconductor substrate 42 are formed. Trenches 46 extend down to a total depth ranging between 150 and 350 nm, for example, a depth equal to 250 nm.

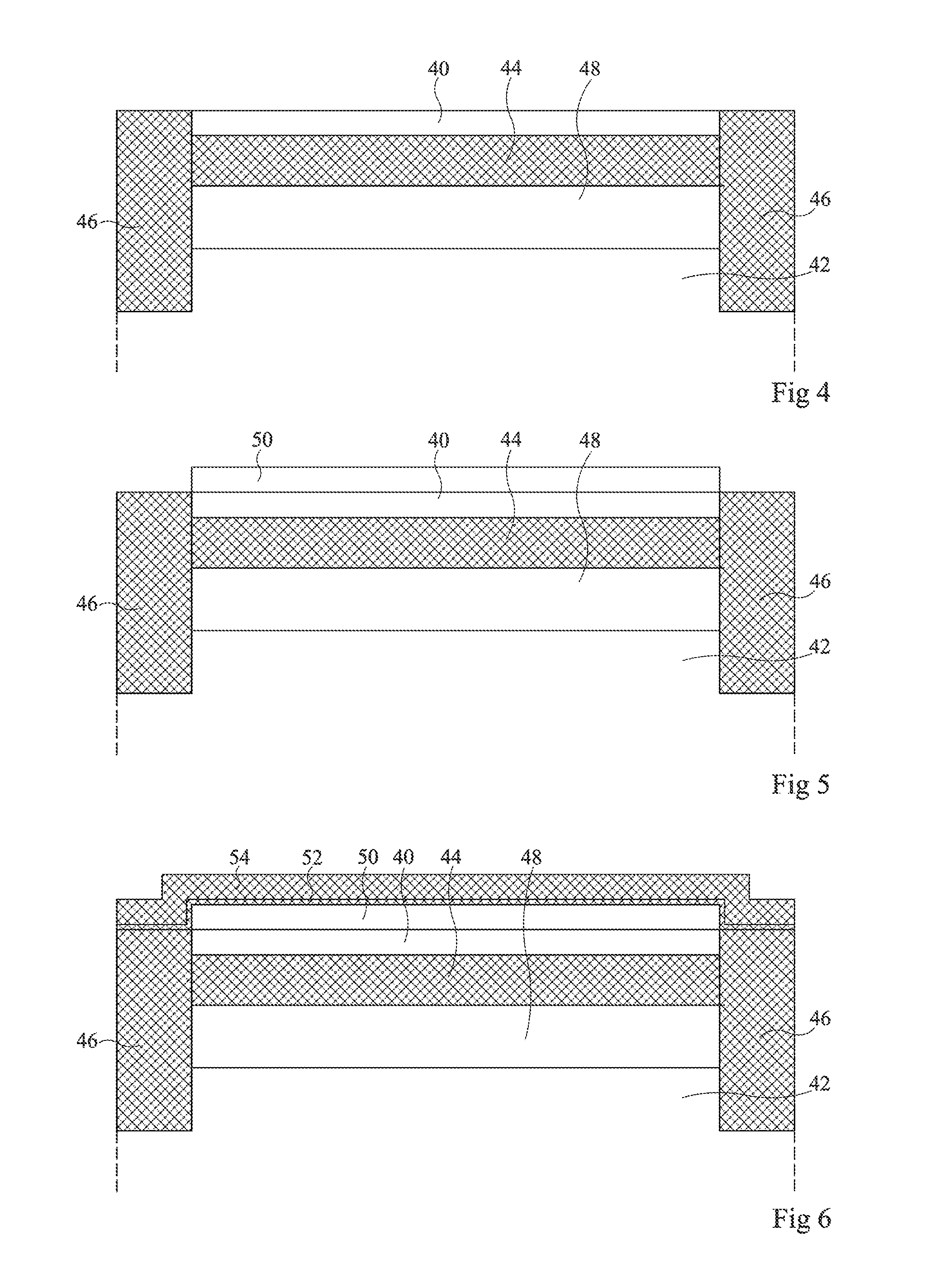

[0047]At a step illustrated in FIG. 4, a dopant implantation has been pe...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More