Image encryption and decryption system and method based on FPGA platform and evolutionary hardware

An evolutionary hardware, encryption and decryption technology, applied in the field of information encryption and decryption, can solve the problems of poor flexibility and achieve the effects of fast encryption speed, enlarged key space, and enhanced security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention is described in detail below in conjunction with accompanying drawing and embodiment:

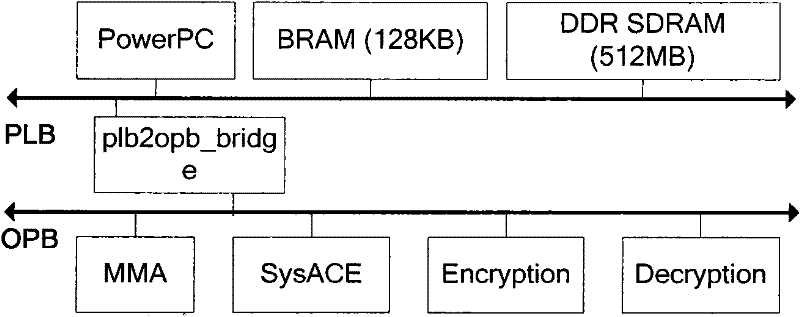

[0045] This example is implemented on the XC2VP30 FPGA development board, using PowerPC as the processor, using the on-chip memory BRAM (128KB capacity in the embodiment) and the off-chip memory DDR SDRAM (512MB capacity in the embodiment) as the memory, and using the CF card as the non-volatile memory The volatile memory stores image data. The image data before and after encryption and decryption are all stored in the CF card. Due to the limited on-chip memory BRAM of the FPGA platform, a 512MB memory stick DDRSDRAM can be added to store the stack of software projects.

[0046] figure 1 Shown is the overall structure diagram of the system, because PowerPC is used as the processor, the system has two buses, PLB (Processor Local Bus, processor local bus) and OPB (On-Chip Peripheral Bus, on-chip peripheral bus). The OPB bus connects some low-speed and low-perfo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More