Method for making packaging substrate with recess structure

A technology for packaging substrates and manufacturing methods, which is applied in the manufacture of semiconductor/solid-state devices, assembling printed circuits with electrical components, and electrical components, etc., can solve the problem of small packaging process margins, the difficulty of increasing the number of output and input pins of 40' of solder balls, Problems such as the first substrate 22' and the second substrate 32' are additionally performed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

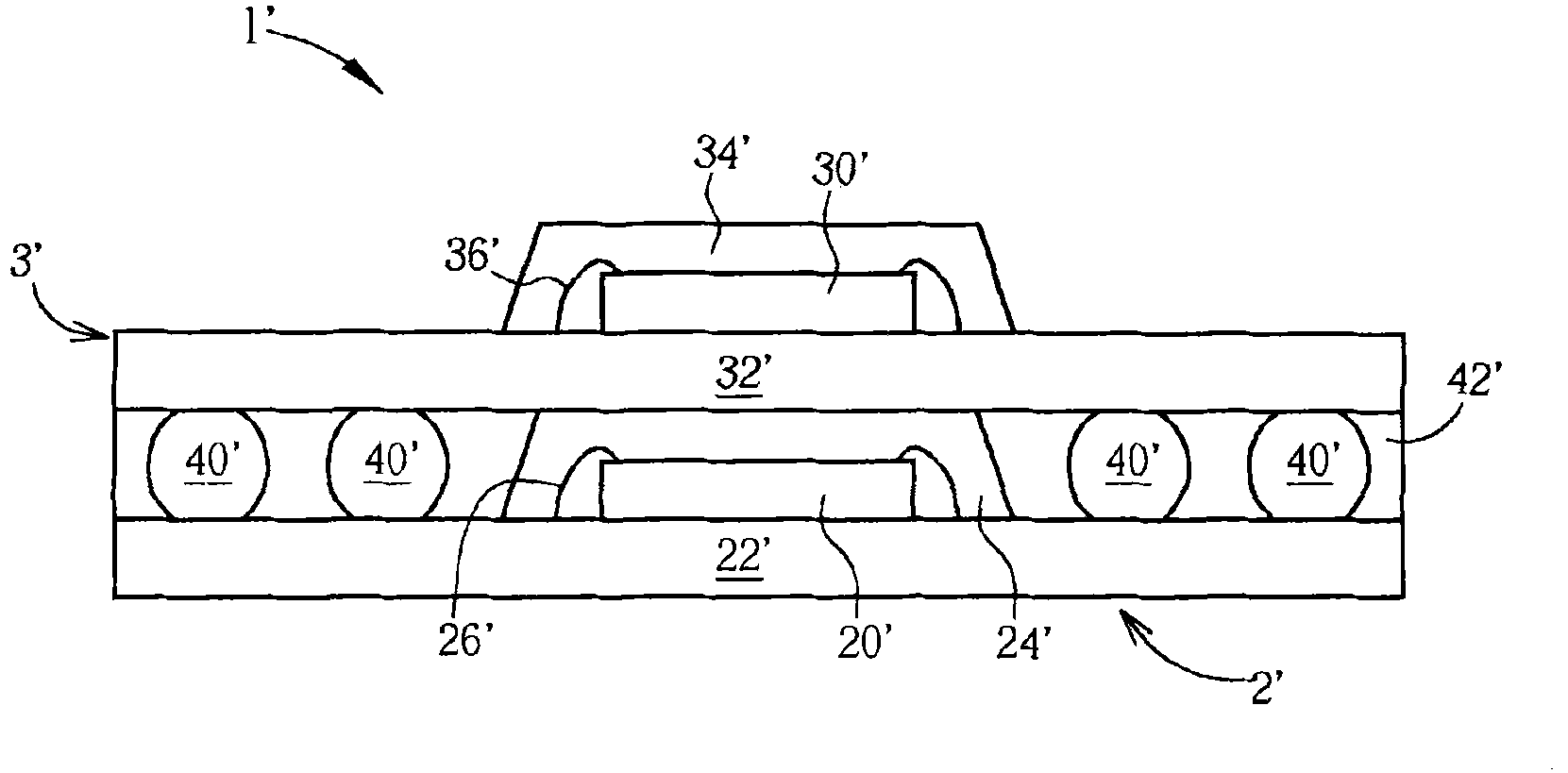

[0045] The invention relates to a manufacturing method of a packaging substrate with a cavity structure, which is used as a solution for integrating high-density integrated circuit components. The invention utilizes a pressing process of a composite circuit board to combine the circuit board with reserved openings with the main body circuit board to complete the packaging substrate with a cavity structure.

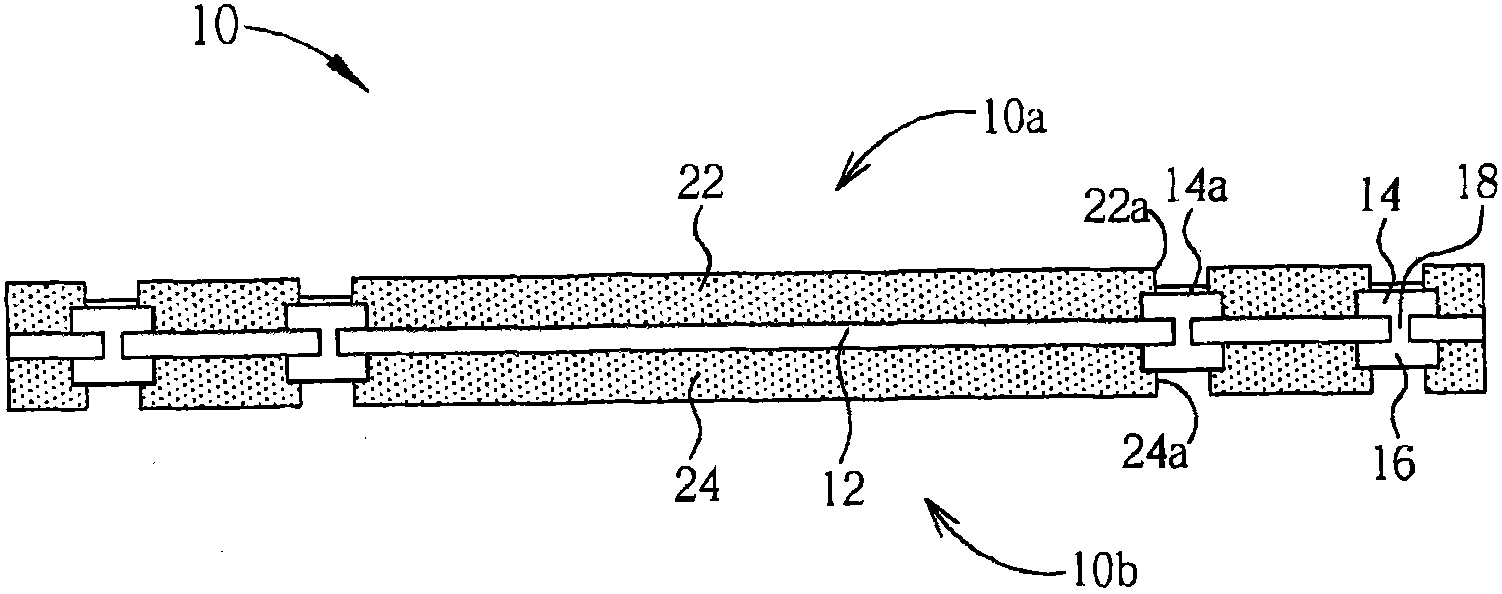

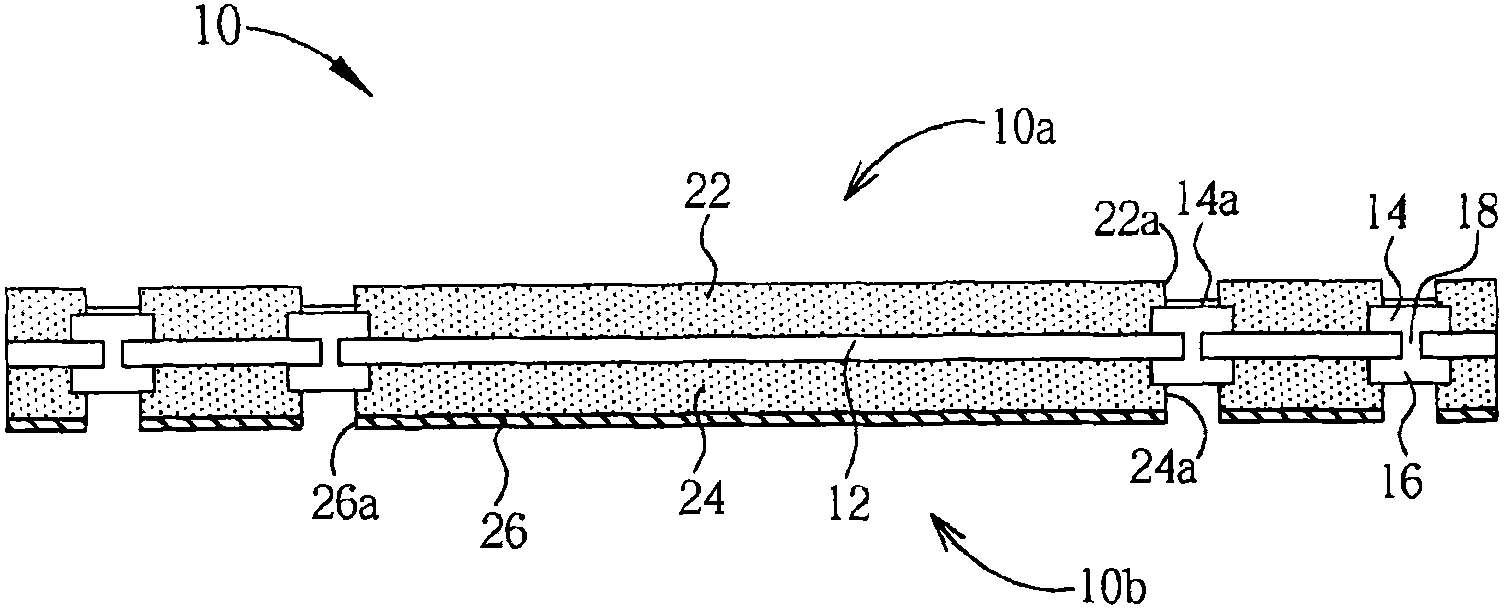

[0046] The manufacturing method of the packaging substrate with cavity structure of the present invention can be mainly divided into three parts, wherein the first part is to form the connection board with reserved openings, the second part is to form the main circuit board, and the third part is to form the connection board Press fit with the main circuit board. Below, that is, through Figure 1a to Figure 1c Explain the first part, by Figure 2a and Figure 2b Explain the second part, by image 3 Describe the third part.

[0047]see Figure 1a to Figure 1c , which ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com