Sigma-delta fraction N frequency comprehensive device behavior level modeling method

A technology of frequency synthesizer and modeling method, applied in the direction of instrument, automatic control of power, electrical digital data processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

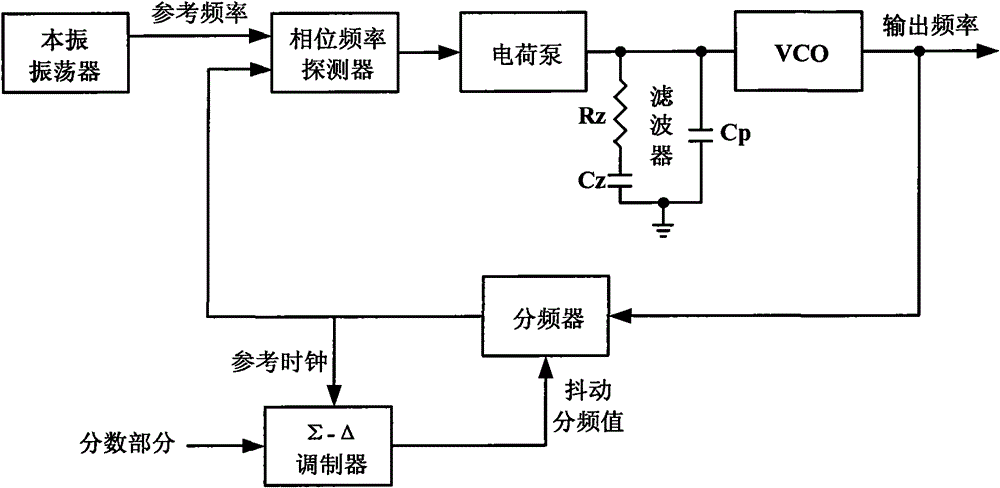

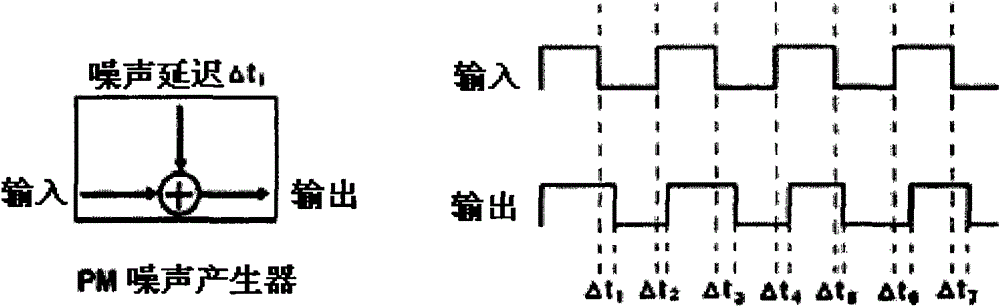

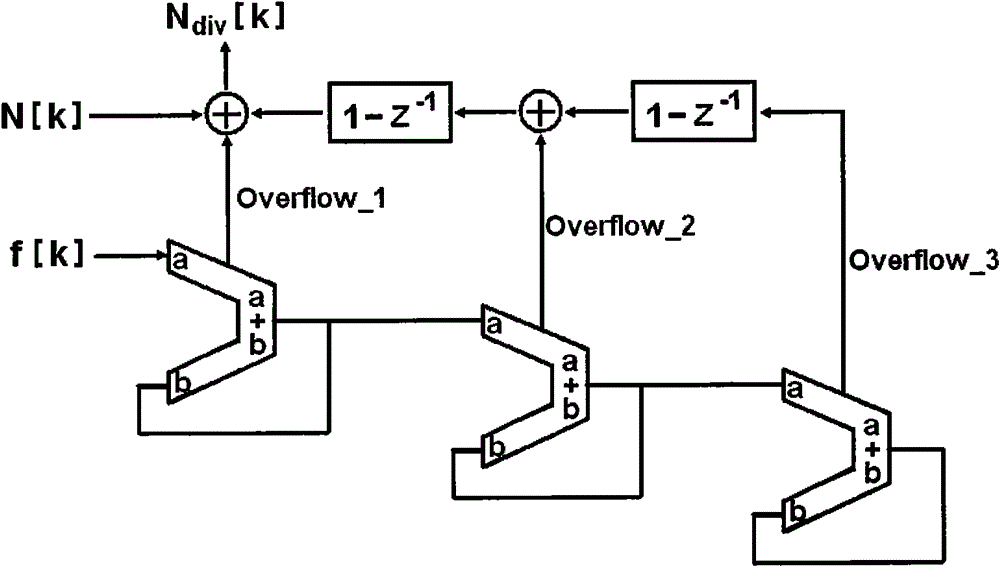

[0075] In this embodiment, a Σ-Δ fractional-N frequency synthesizer is modeled using VHDL-AMS language, and its performance is simulated by the simulator ADMS. In this embodiment, the modules including the oscillator, phase-frequency detector, charge pump, VCO, filter, frequency divider, and Σ-Δ modulator included in the frequency synthesizer are modeled at the behavioral level, where the local oscillator Phase-frequency detectors, charge pumps, VCOs, filters, and frequency dividers are phase-locked loop systems. Some nonlinear effects, such as charge pump asymmetry, dead zone effects, and jitter noise are modeled. Of all the key performance metrics for a PLL system, phase noise is the most critical because it increases the noise floor and degrades the system's sensitivity, and it is also a more difficult part to model. In order to model the PLL system more accurately, different jitter noise sources are modeled, and the Σ-Δ modulator, which mainly affects the phase noise of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More