Low-complexity and extensible fault-tolerant routing algorithm specific to network on chip

A low-complexity, network-on-chip technology, applied in data exchange networks, error prevention, digital transmission systems, etc., to achieve good scalability, overcome large area overhead, and ultra-low hardware complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

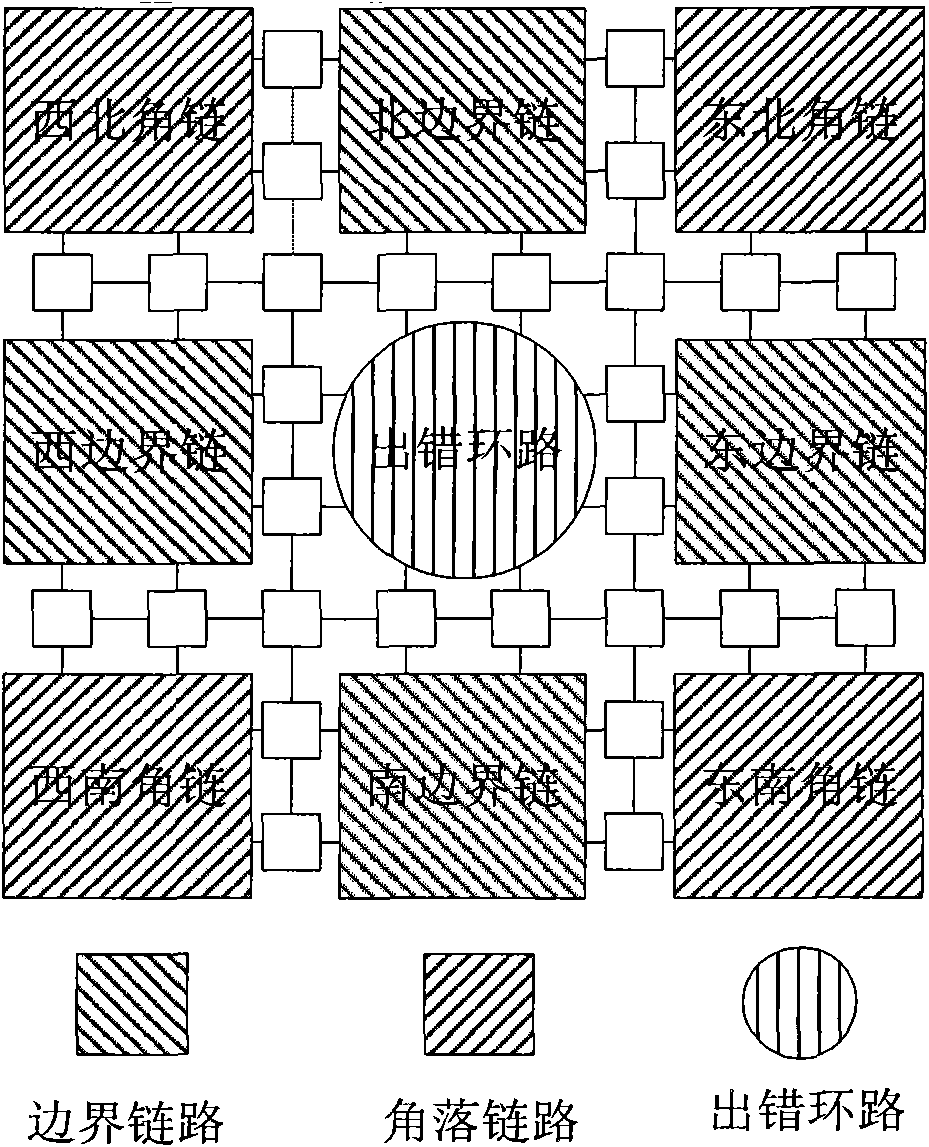

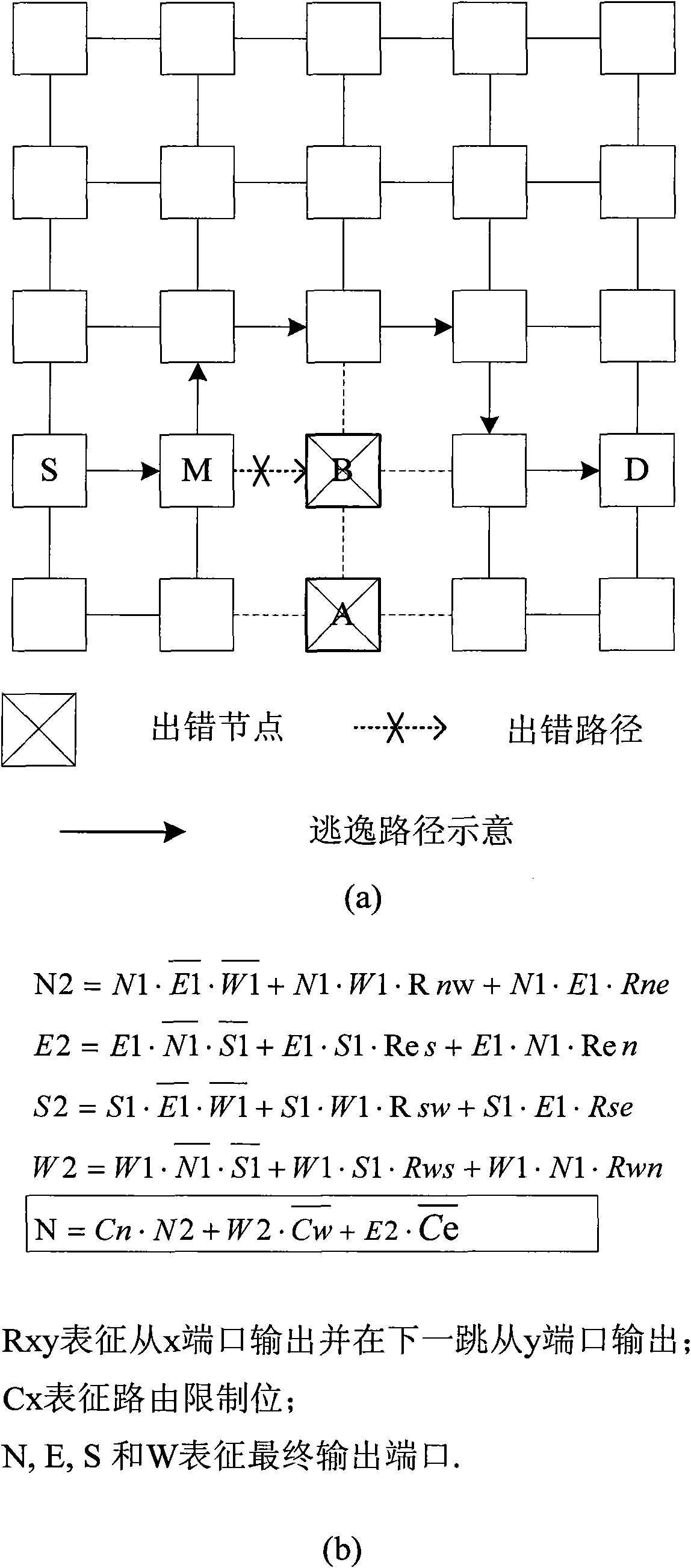

[0044] When the error node occurs in the four corner areas or the four border areas or any single area in the center area, the algorithm can use the above three-step strategy to divide and conquer each one. The error situation in the southern border area is as follows: image 3 As shown in , when a node in the corner area or central area is wrong, we can adopt a similar method to achieve the purpose of bypassing the wrong node to ensure the communication between normal node pairs.

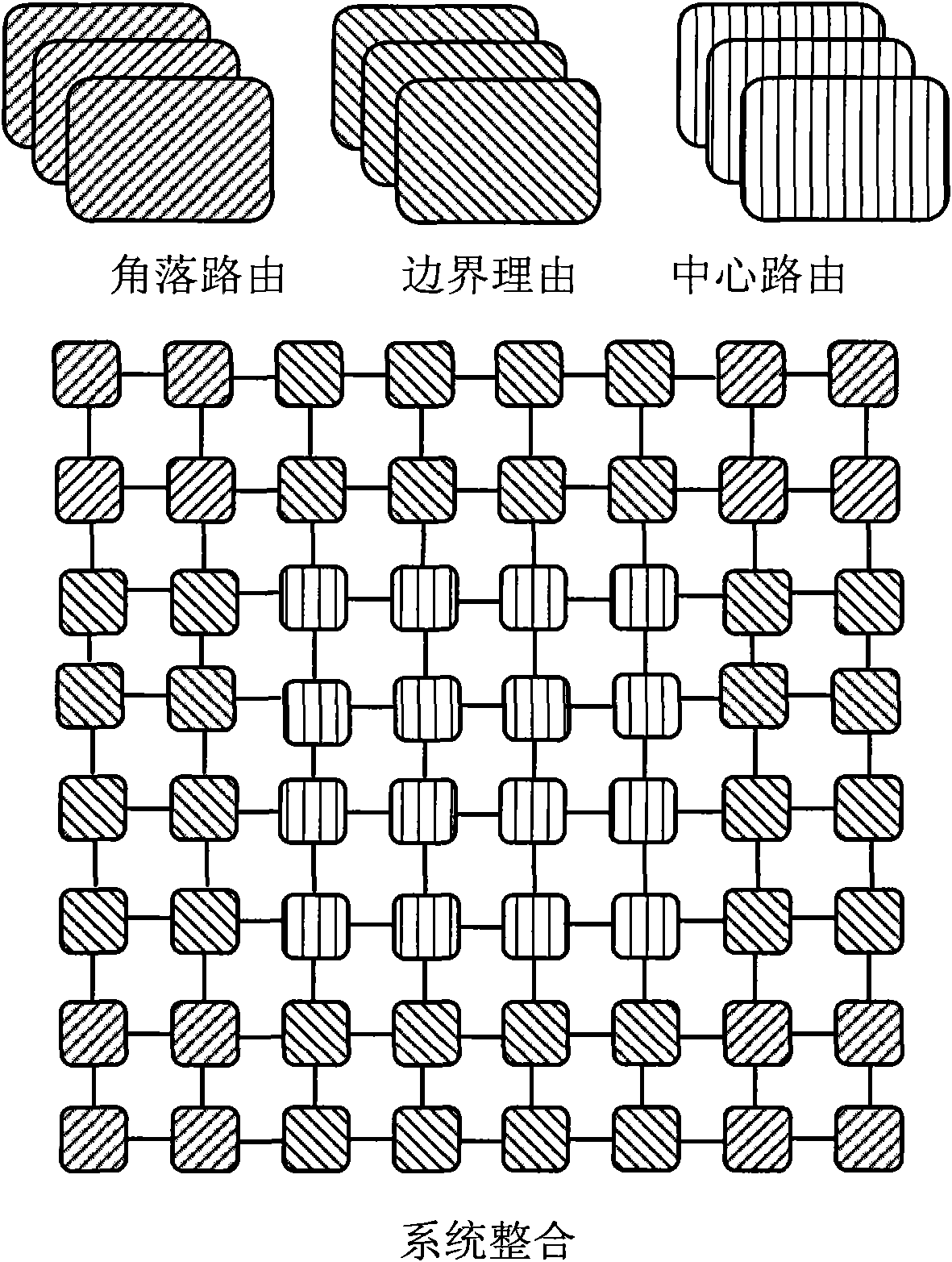

[0045] In order to simplify the configuration of the system, the algorithm can adopt the method of merging and absorbing. In general, two principles are grasped, and the adjacent scattered error nodes are absorbed as much as possible to form a rectangular fault area and approach the corner area as much as possible. , the specific implementation is as Figure 4 shown.

[0046] When the area formed after merging and absorbing wrong nodes spans several different areas, the routers on both sides of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More