Method for realizing decoding, software decoder and decoding device

An implementation method and technology of a hardware decoder, applied in the field of software decoders and decoding equipment, can solve the problems of disadvantageous decoding efficiency, waiting for hardware decoders, waiting for software decoders, etc., and achieve the effect of improving decoding efficiency and realizing parallel processing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] This embodiment will be described from the perspective of a software decoder. The software decoder is used to implement functions such as software decoding and software driving the hardware decoder, while the hardware decoder implements the hardware decoding function.

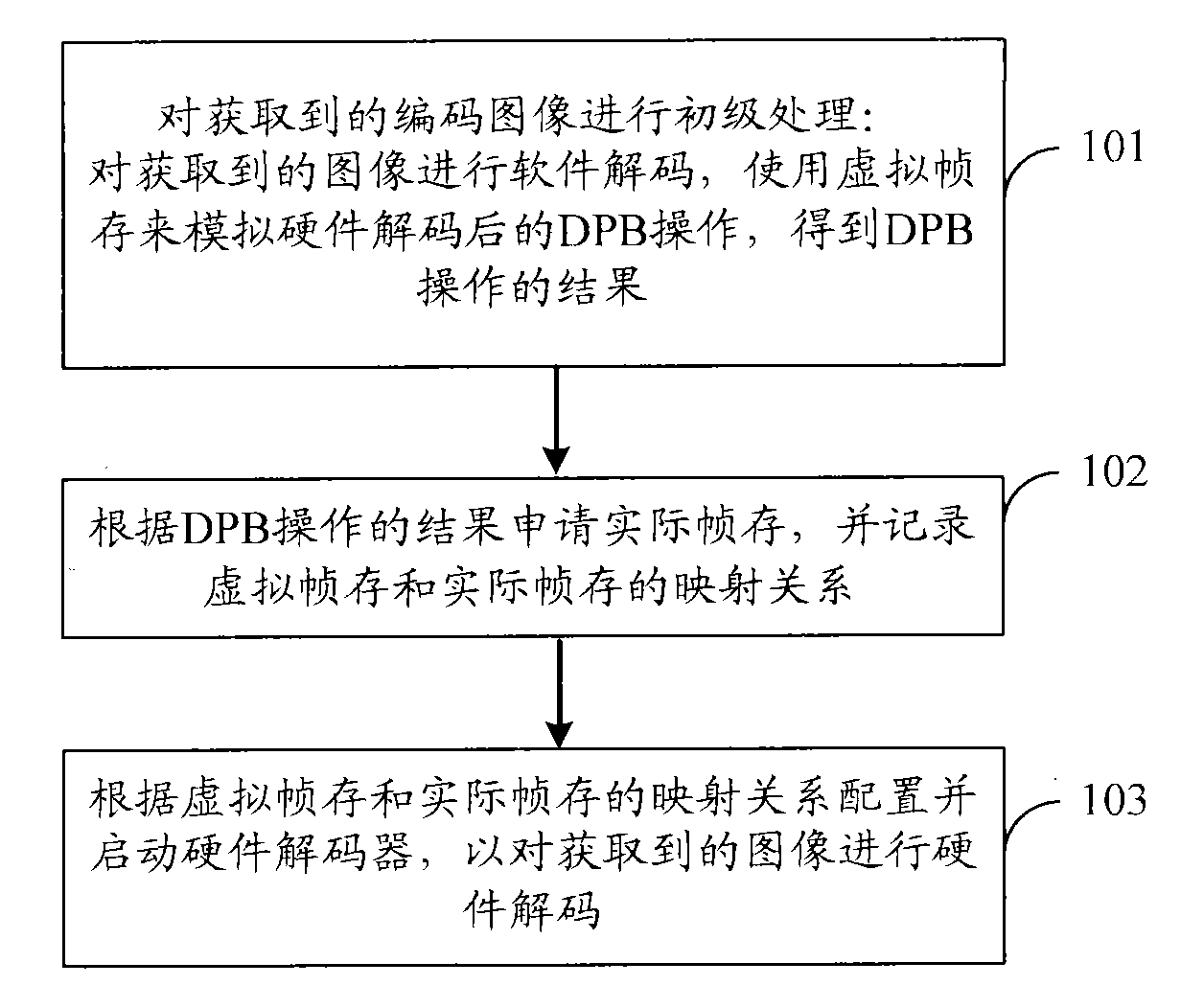

[0030] A decoding implementation method, such as figure 1 As shown, the specific process can be as follows:

[0031] 101. Perform primary processing on the acquired coded image frame; the primary processing specifically includes: performing software decoding on the acquired encoded image, using a virtual frame memory to simulate a DPB operation after hardware decoding, and obtaining a result of the DPB operation.

[0032] For example, in order to make the division of labor between software decoding and hardware decoding more reasonable, the slice header (slice header) that requires a lot of logical operations can be handed over to the software decoder for decoding, and the data-intensive slice data (sli...

Embodiment 2

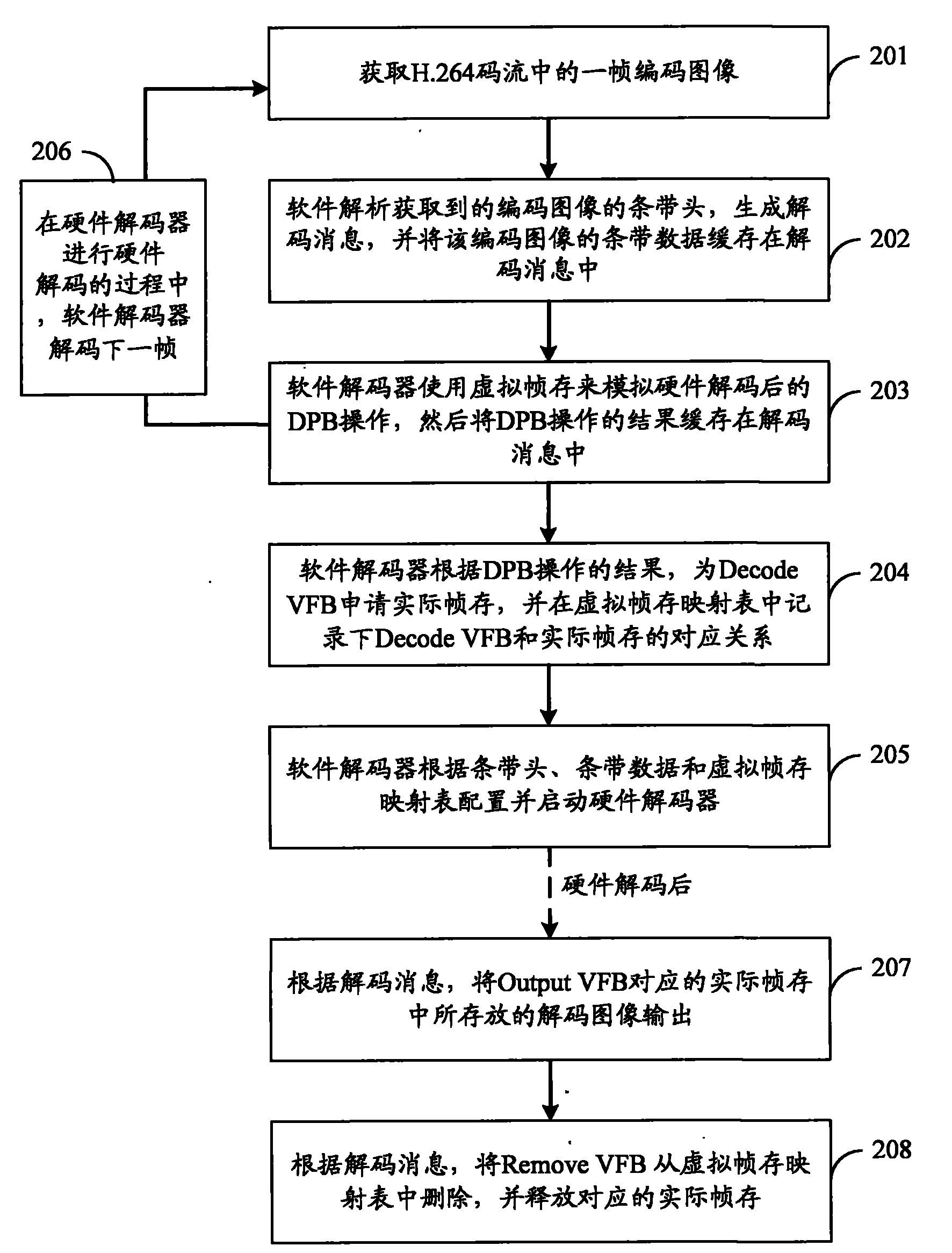

[0051] According to the method described in the first embodiment, this embodiment will take the software decoder to parse the slice header, the hardware decoder to decode the slice data, and the code stream to be an H.264 code stream as an example for further description.

[0052] After parsing the slice header, the software decoder generates a decoded message, then buffers the slice data into the decoded message, uses the virtual frame memory to simulate the DPB operation after a frame ends, and caches the result of the DPB operation in the decoded message. Before starting the hardware decoder to decode each frame of encoded image, the software decoder applies for the actual frame memory according to the decoding message, and updates the virtual frame memory mapping table that records the mapping relationship between the virtual frame memory and the actual frame memory, and then Configure and start the hardware decoder with data and virtual frame memory mapping table to perfor...

Embodiment 3

[0070] According to the method described in the second embodiment, a specific example will be used to describe in detail below.

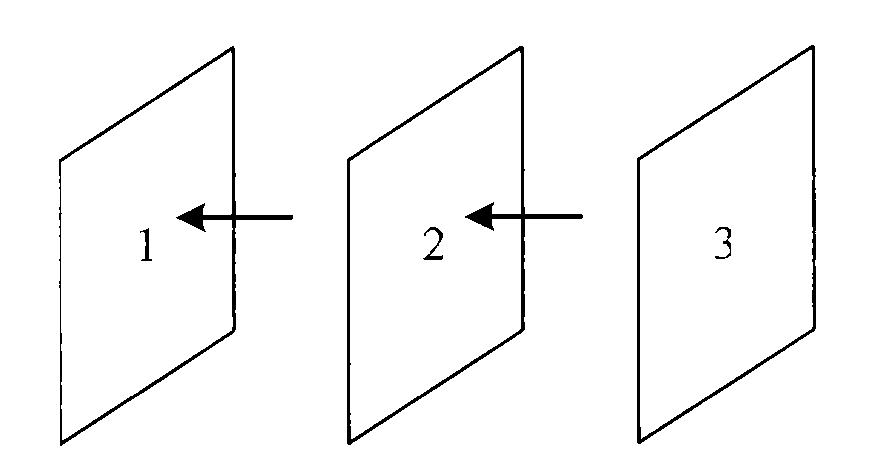

[0071] see Figure 3a , Figure 3a is a schematic diagram of the code stream. Generally, in the code stream, the image of the next frame refers to the image of the previous frame, and the number of reference frames is 1. For example, Figure 3a Include three frames of images: 1, 2 and 3, then 1 has no reference frame, 1 is the reference frame of 2, 2 is the reference frame of 3, and so on if there are other frames later.

[0072] In this embodiment, the recording of the mapping relationship between the virtual frame memory and the actual frame memory in the virtual frame memory mapping table is taken as an example for description. Wherein, the structure of the virtual frame memory mapping table may be specifically shown in Table 1;

[0073] Table I:

[0074] VFB

RFB

Remark

0

Actual frame memory information (address,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com