Multi-CPU (Central Processing Unit)system starting method and module based on PCI/PCIe (Peripheral Component Interconnect/Peripheral Component Interconnect Express) bus

A technology for starting modules and buses, applied in the direction of program loading/starting, program starting/switching, multi-programming device, etc., can solve problems such as affecting system performance, and achieve the effects of improving initialization speed, saving costs, and improving start-up speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

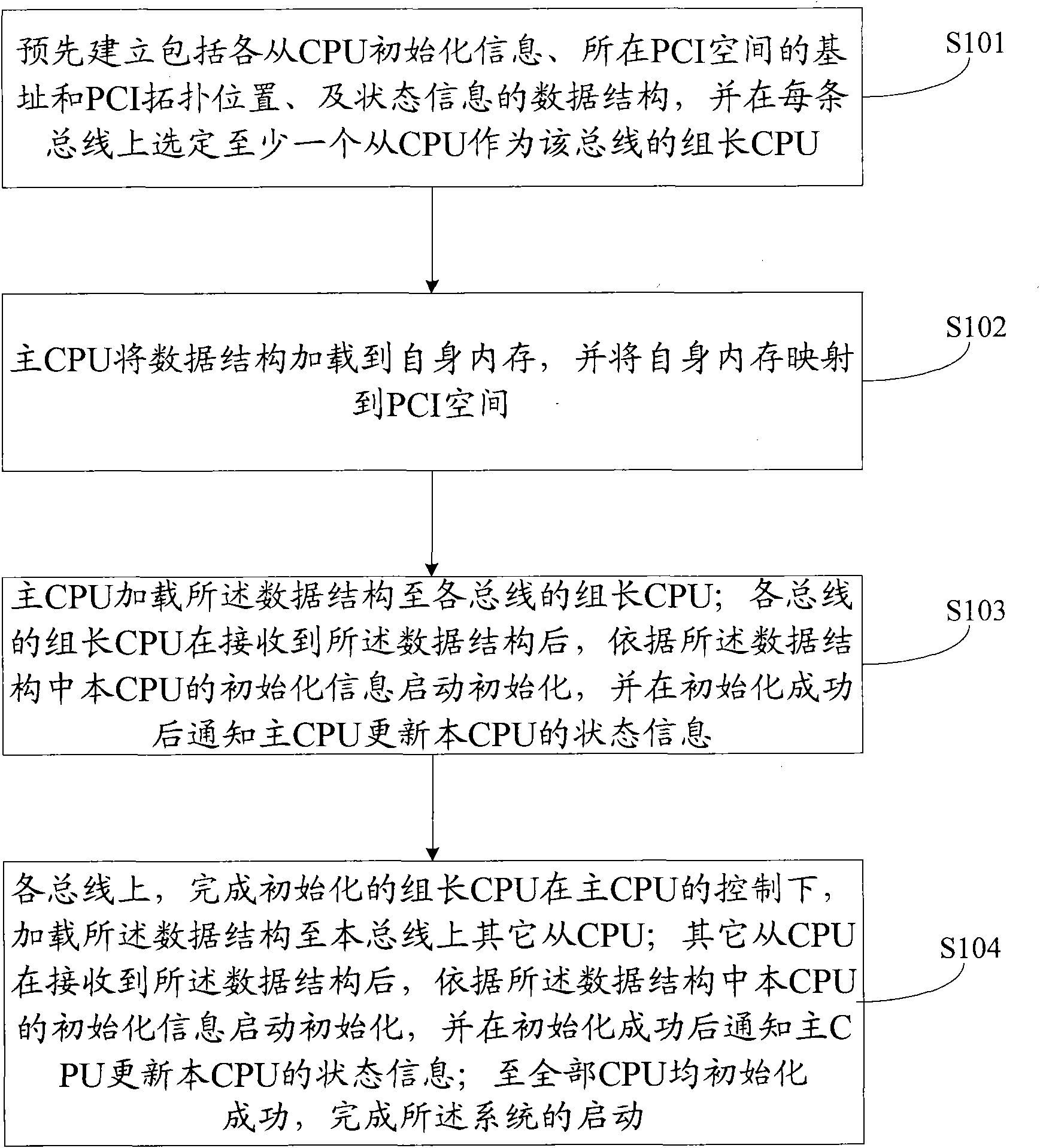

[0045] see figure 1 , a method for starting a multi-CPU system based on the PCI / PCIe bus provided by the embodiment of the present invention:

[0046] Step S101: Pre-establish a data structure including the initialization information of each slave CPU, the base address of the PCI space, the PCI topological position, and status information, and select at least one slave CPU on each bus as the group leader CPU of the bus.

[0047] Usually, pre-established data structures are stored in the FLASH of the main CPU.

[0048] Wherein, on each bus, select at least one slave CPU as the group leader CPU of the bus, preferably, select the slave CPU whose device number is 0 on each bus, that is, CPU (BUSn, DEV0) as the CPU (BUSn, DEV0) The leader CPU of the bus.

[0049] The method that this multi-CPU system starts comprises the steps:

[0050] Step S102: the main CPU loads the data structure into its own memory, and maps its own memory to the PCI space.

[0051] Here, after the main C...

Embodiment 2

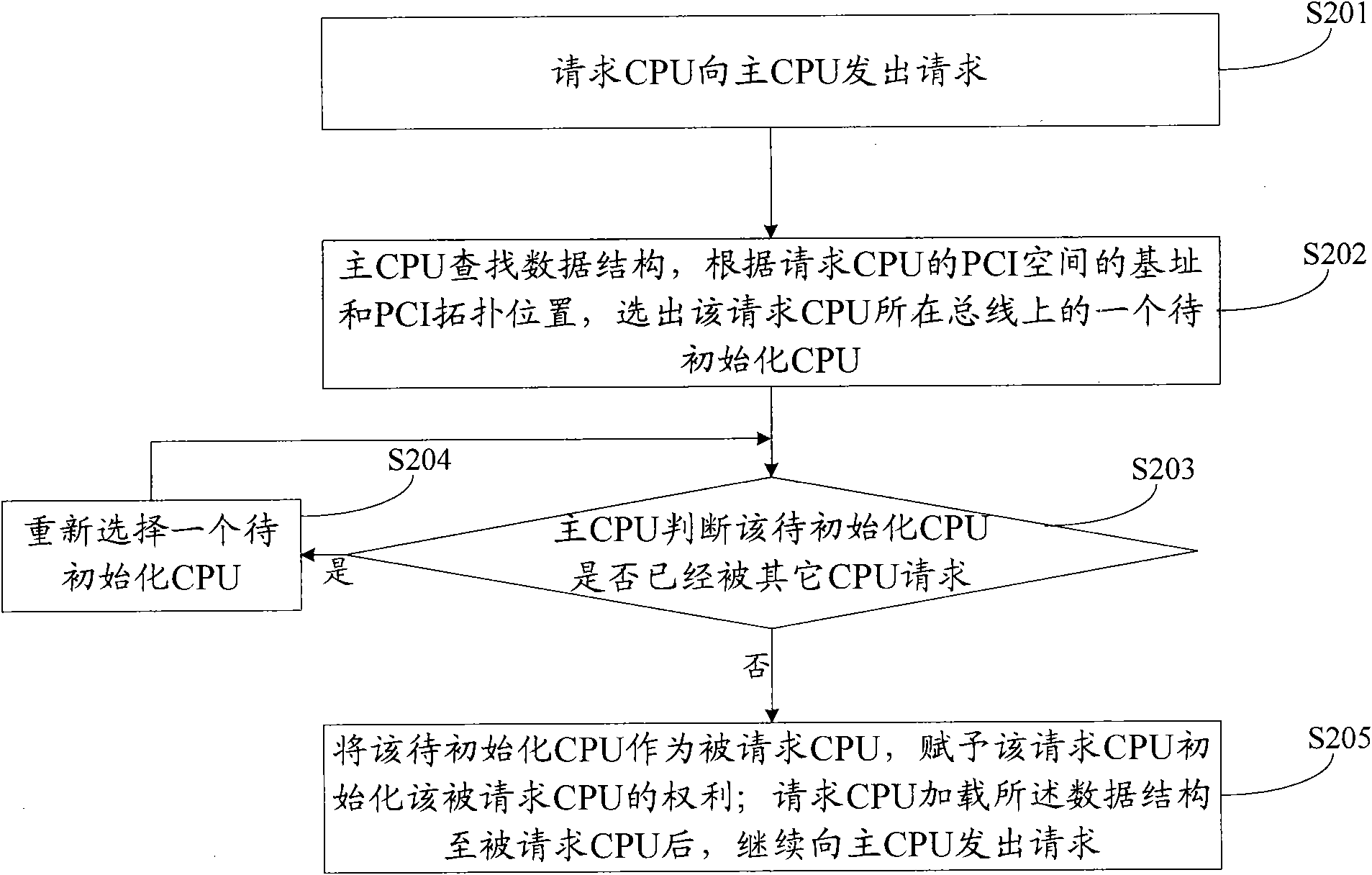

[0073] see image 3 , a preferred PCI / PCIe bus-based multi-CPU system startup method provided by the embodiment of the present invention:

[0074] Step S301: Pre-establish a data structure including the initialization information of each slave CPU, the base address of the PCI space, the PCI topology position, and the state information, and select at least one slave CPU on each bus as the group leader CPU of the bus.

[0075] Usually, pre-established data structures are stored in the FLASH of the main CPU.

[0076] Wherein, on each bus, select at least one slave CPU as the group leader CPU of the bus, preferably, select the slave CPU whose device number is 0 on each bus, that is, CPU (BUSn, DEV0) as the CPU (BUSn, DEV0) The leader CPU of the bus.

[0077] The method that this multi-CPU system starts comprises the steps:

[0078] Step S302: the main CPU loads the data structure into its own memory, and maps its own memory to the PCI space.

[0079] Here, after the main CPU s...

Embodiment 3

[0104] see Figure 5 , the embodiment of the present invention provides a kind of multi-CPU system startup module based on PCI / PCIe bus, comprising:

[0105] A data structure establishment unit 501, configured to establish a data structure including each slave CPU initialization information, the base address of the PCI space where it resides, the PCI topology position, and state information;

[0106] The group leader CPU selection unit 502 is used to select at least one slave CPU as the group leader CPU of the bus on each bus;

[0107] The main CPU initialization unit 503 is used for the main CPU to load the data structure into its own memory, and map its own memory to the PCI space;

[0108] The group leader CPU initialization unit 504 is used for the main CPU to load the data structure to the group leader CPU of each bus; after the group leader CPU of each bus receives the data structure, according to the initialization information of the CPU in the data structure Start th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More