SOC (System on a Chip) debugging and verifying device and method

A system-on-chip and verification device technology, applied in the field of system-on-chip, can solve problems such as reducing the efficiency of development, hindering the progress of development, and increasing the development cost of SOC chips, so as to achieve the effect of improving development efficiency and reducing development cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

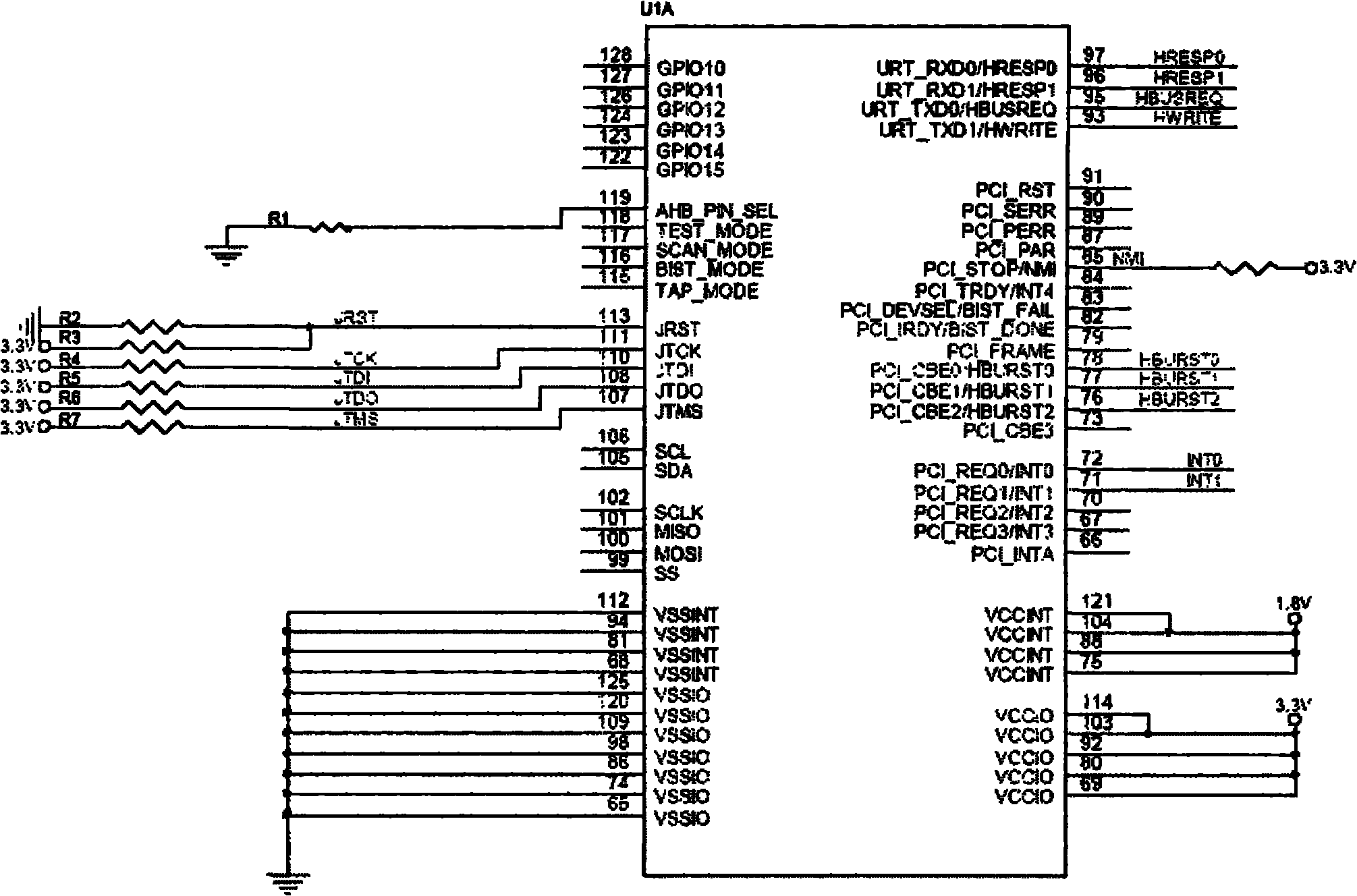

[0035] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0036] Embodiments of the present invention provide a system-on-chip debugging and verification device and method, which can fully verify the IP hard core and SOC system, greatly improve the development efficiency of SOC products, and reduce the development cost.

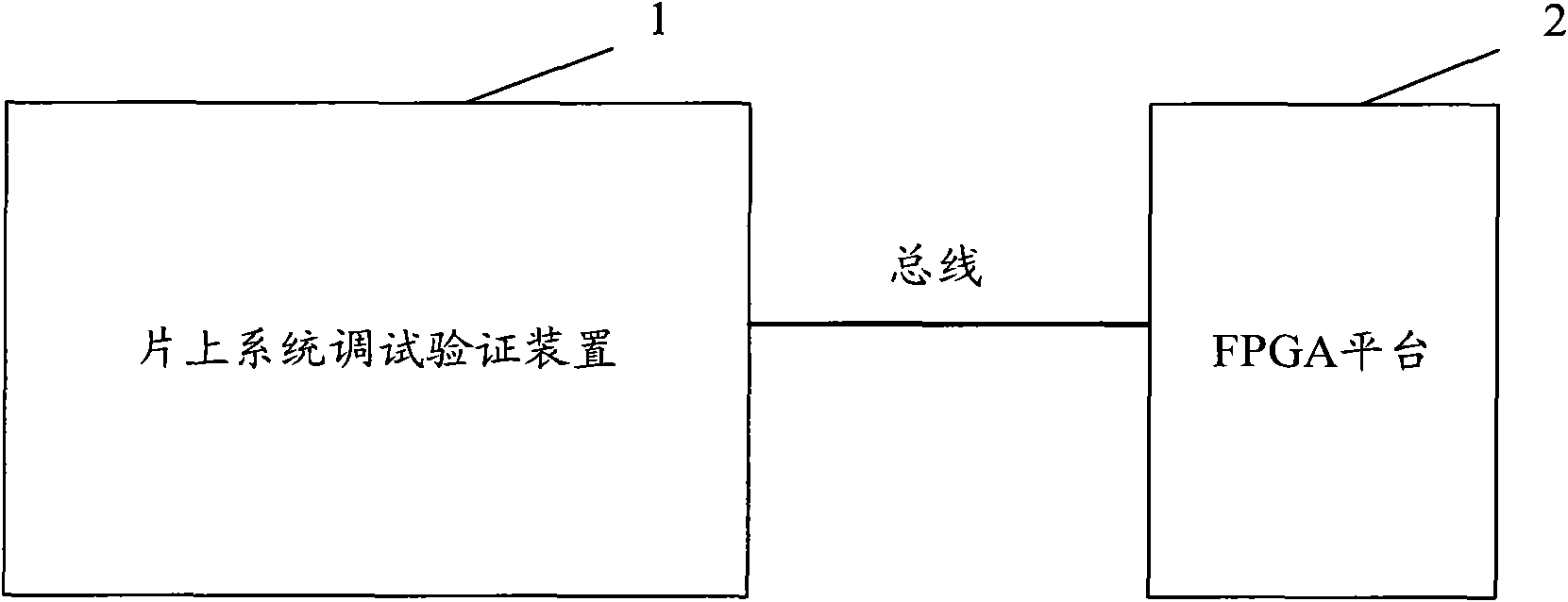

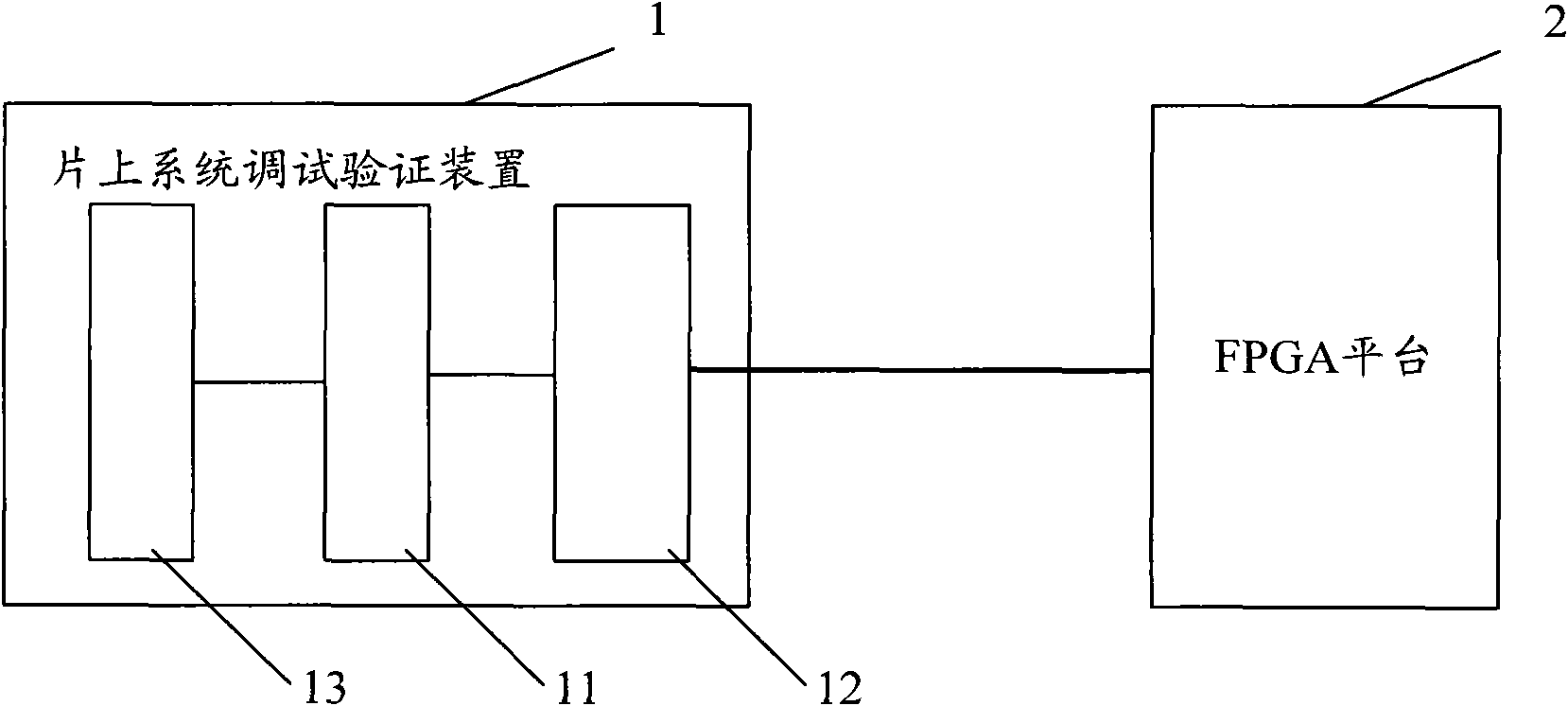

[0037] An embodiment of the present invention provides a system-on-chip debugging verification device, such as figure 1 As shown, the system-on-chip debugging and verification device 1 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More