Register transport level N-modular redundancy verifying method

A register transfer level, N-mode redundancy technology, applied in instrumentation, functional testing, electrical digital data processing, etc., can solve the problems of low automation level, uncontrollable fault injection, high verification cost, and achieve strong observability, The effect of high level of automation and simple operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to make the purpose, content, and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

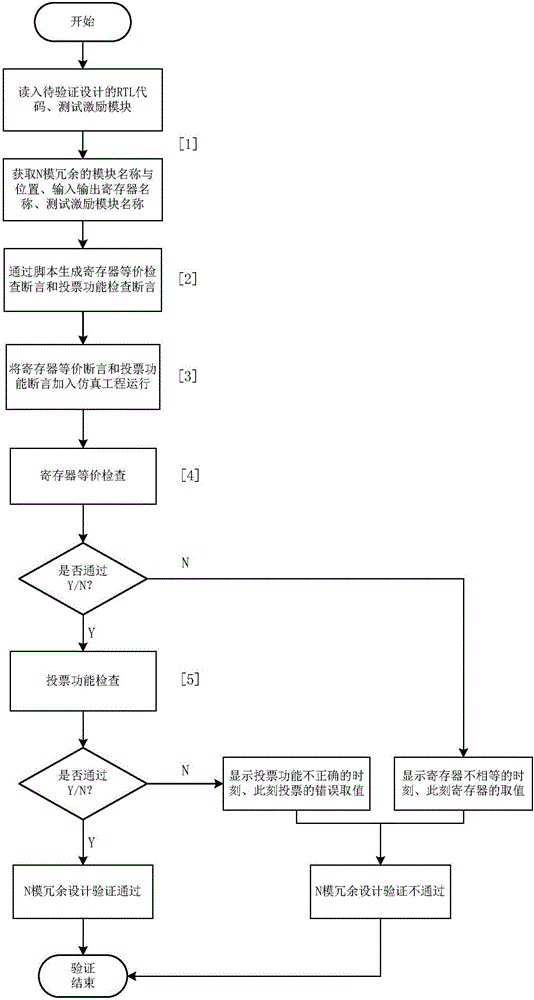

[0020] figure 1 Shown is a flow chart of a register transfer level N-mode redundancy verification method of the present invention, as figure 1 Shown, the specific steps of the semi-automatic verification method of a kind of register transfer level N module redundant design of the present invention are as follows:

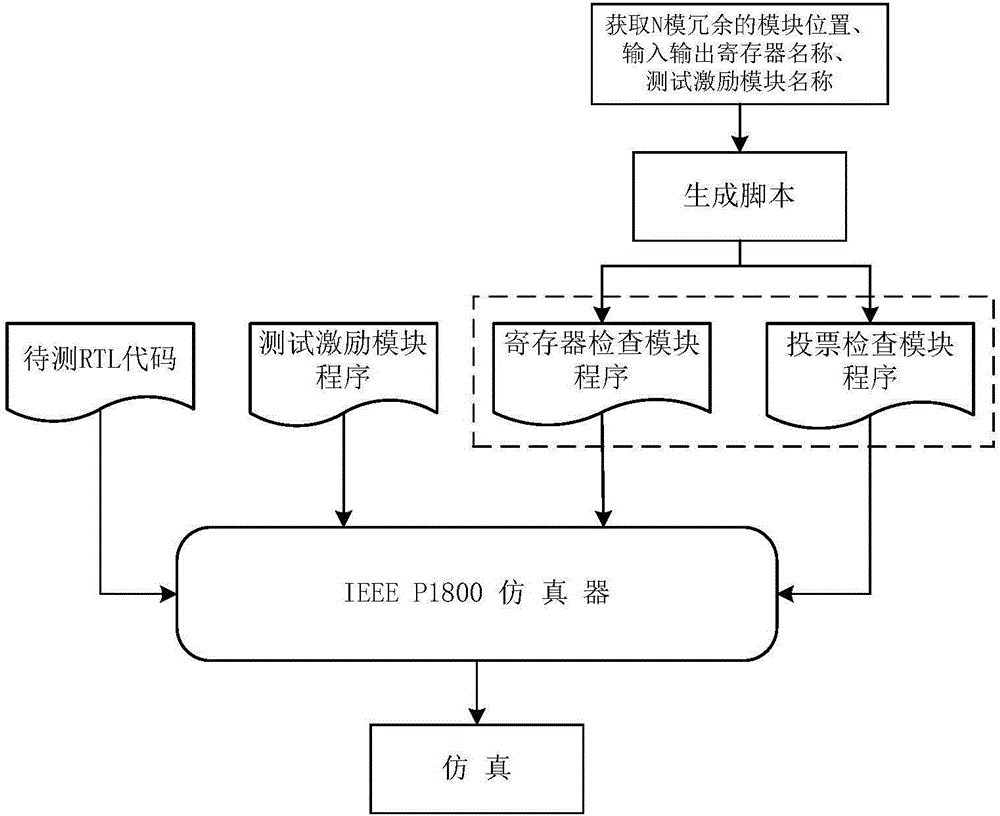

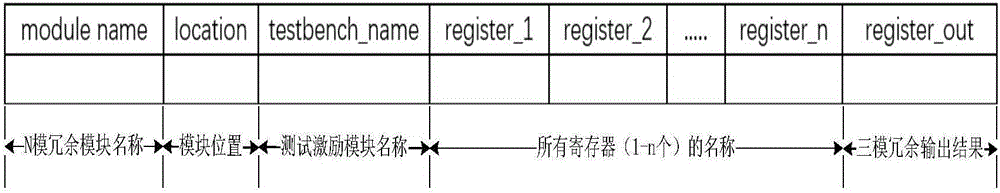

[0021] (1) Generation of test modules. Input the N-mode redundant module position, input and output register name, and testbench module name of the register transfer level design to be tested into the platform generation script, and the script replaces the N-mode redundant module position, input and output register name , generate a register equivalence check module and a voting function check module that ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More