Patents

Literature

68results about How to "Fully verified" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Secure and confidential custodial transaction system, method and device using zero-knowledge protocol

PendingUS20190034923A1Rule out the possibilityPrevent leakageEncryption apparatus with shift registers/memoriesAnonymous user systemsZero-knowledge proofKnowledge level

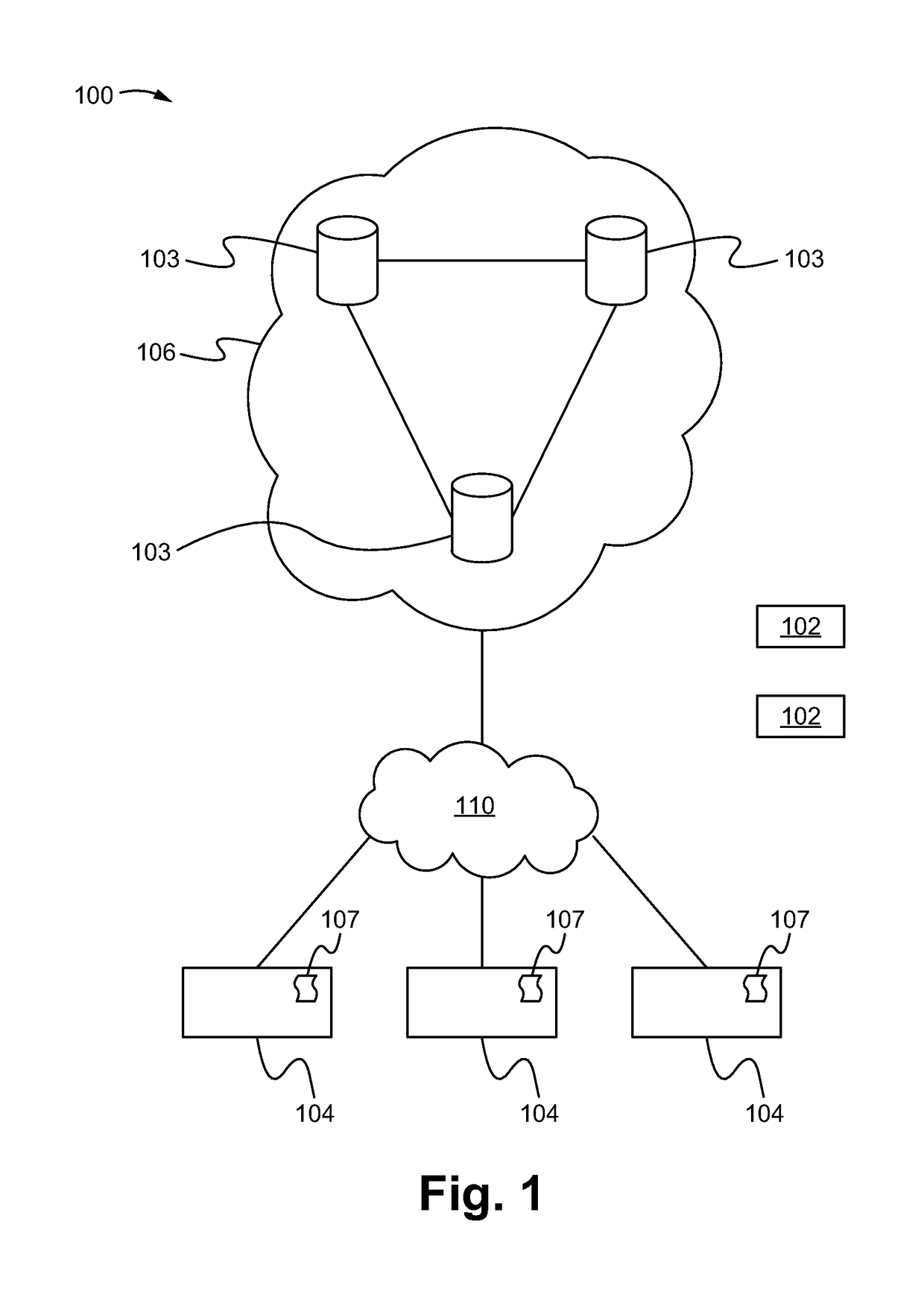

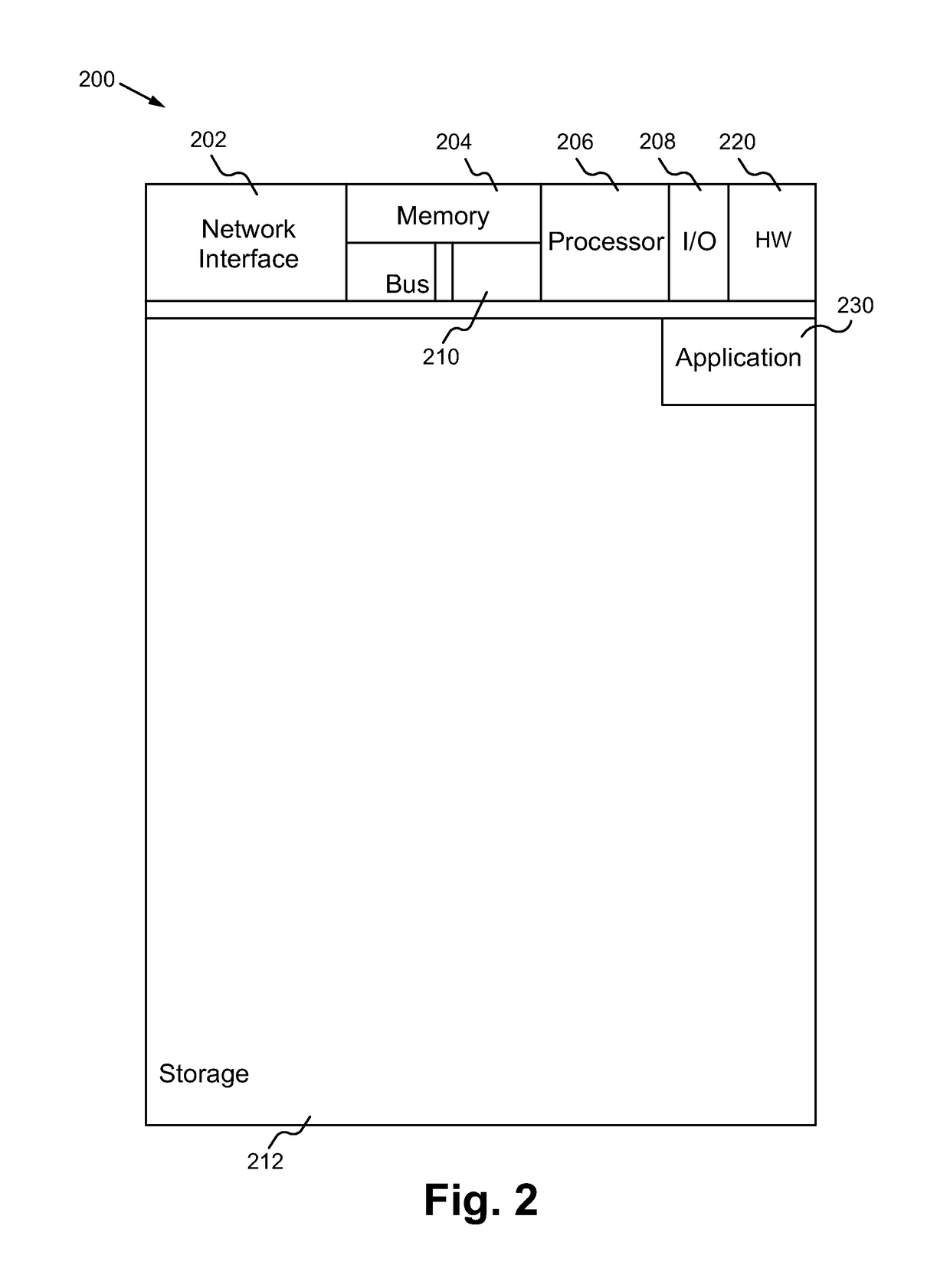

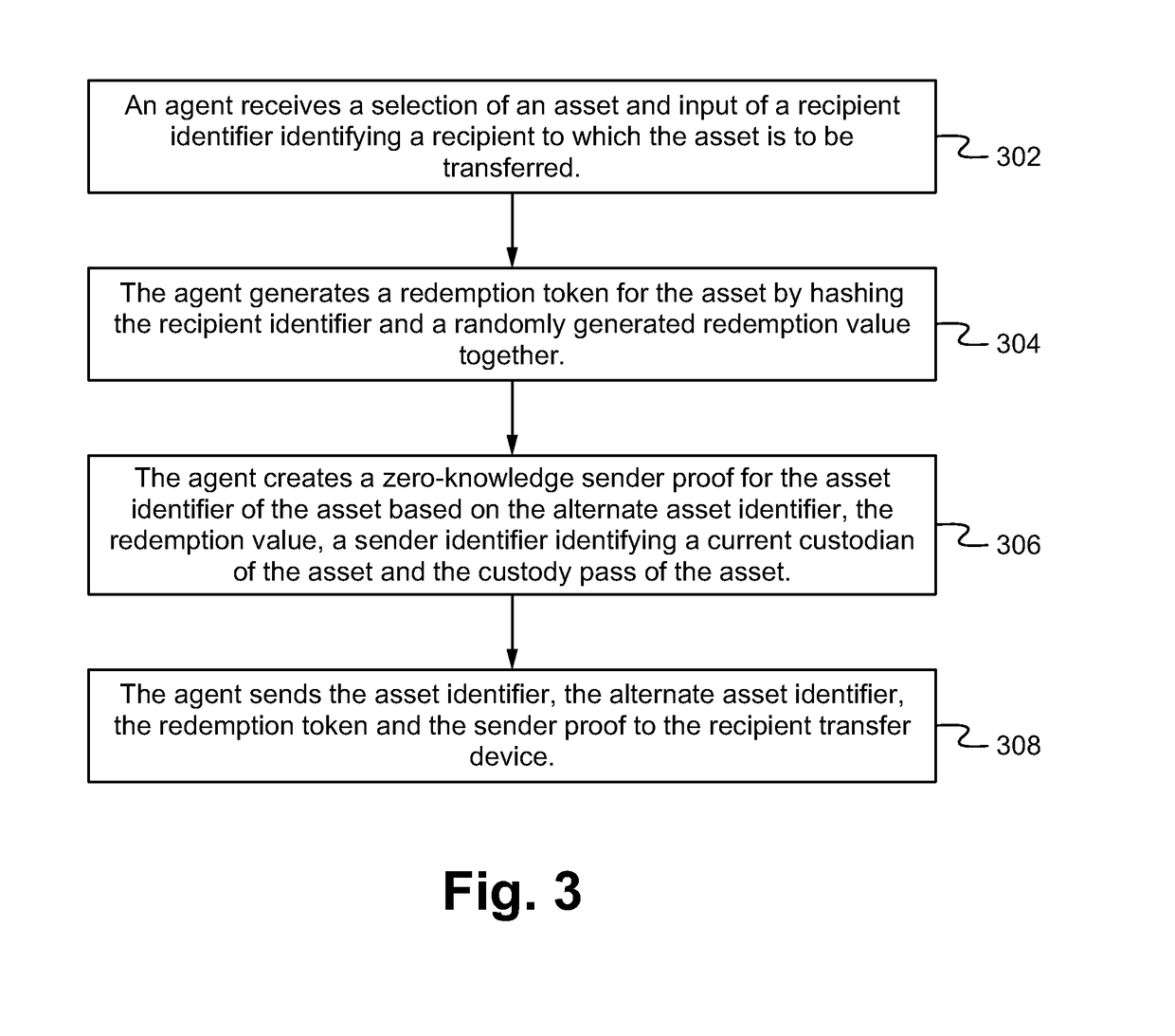

A system, device and method of confidential secure custodial transfers of asset between entities utilizing transaction agents implemented via a distributed ledger (e.g. a blockchain). In particular, the transaction agents securely record each of the transactions on the ledger utilizing obfuscated or proxy data state such that information about the transactions cannot be gleaned from the ledger. In particular, the transaction agents are able to enforce business rules of the system by requesting zero-knowledge proofs from participants to the transaction (e.g. sender and recipient) in place of actual data for the transaction. The zero-knowledge proofs are able to be designed to prevent an observer of the distributed ledger from determining any information of the transaction that is taking place.

Owner:CHRONICLED INC

Real business-based financial transaction test system and method

InactiveCN108614777ARealize simulationEffectively detect defectsFinanceSoftware testing/debuggingFinancial transactionFinancial trading

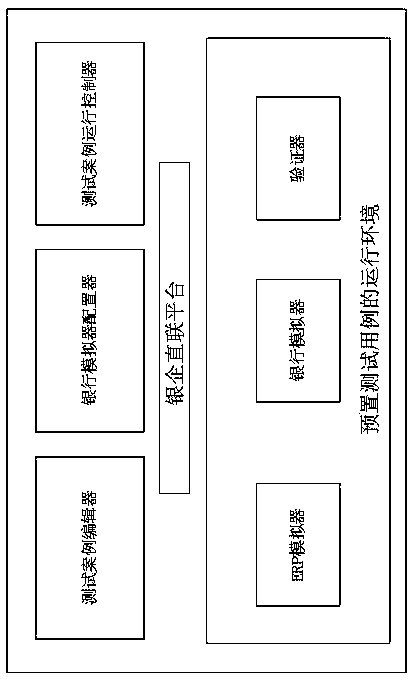

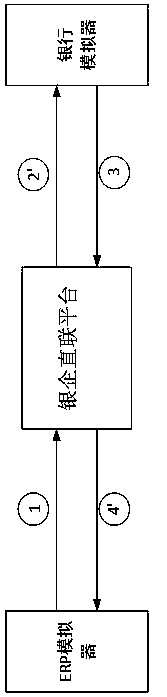

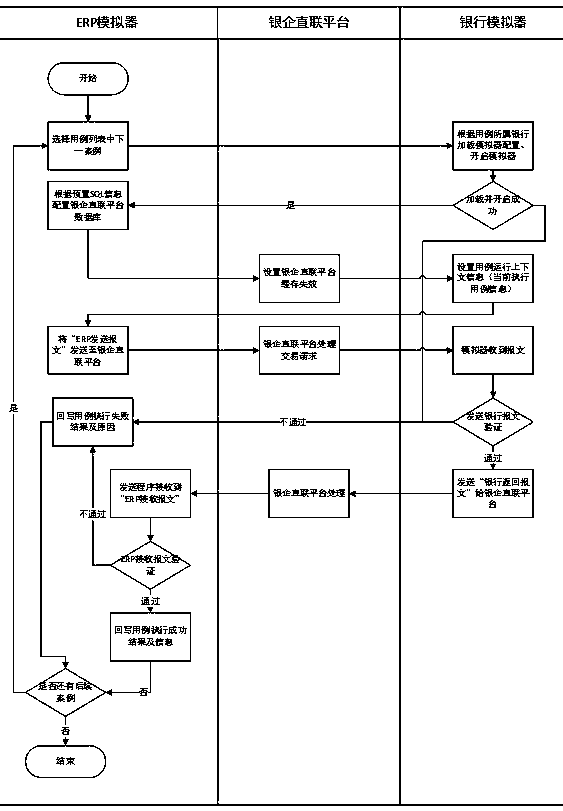

The invention discloses a real business-based financial transaction test system and method, belongs to the field of financial transaction simulation and test, and aims at carrying out modification byusing systems of ERP manufacturers so as to obtain effective and sufficient verification without influencing fund security of enterprise users. An adopted technical scheme is the real business-based financial transaction test system which comprises an ERP simulator, a bank simulator, a bank-enterprise direct connection platform, a verifier, a test case editor, a bank simulation configuration unitand a test case operation controller. The invention furthermore discloses the real business-based financial transaction test method.

Owner:SHANDONG INSPUR GENESOFT INFORMATION TECH CO LTD

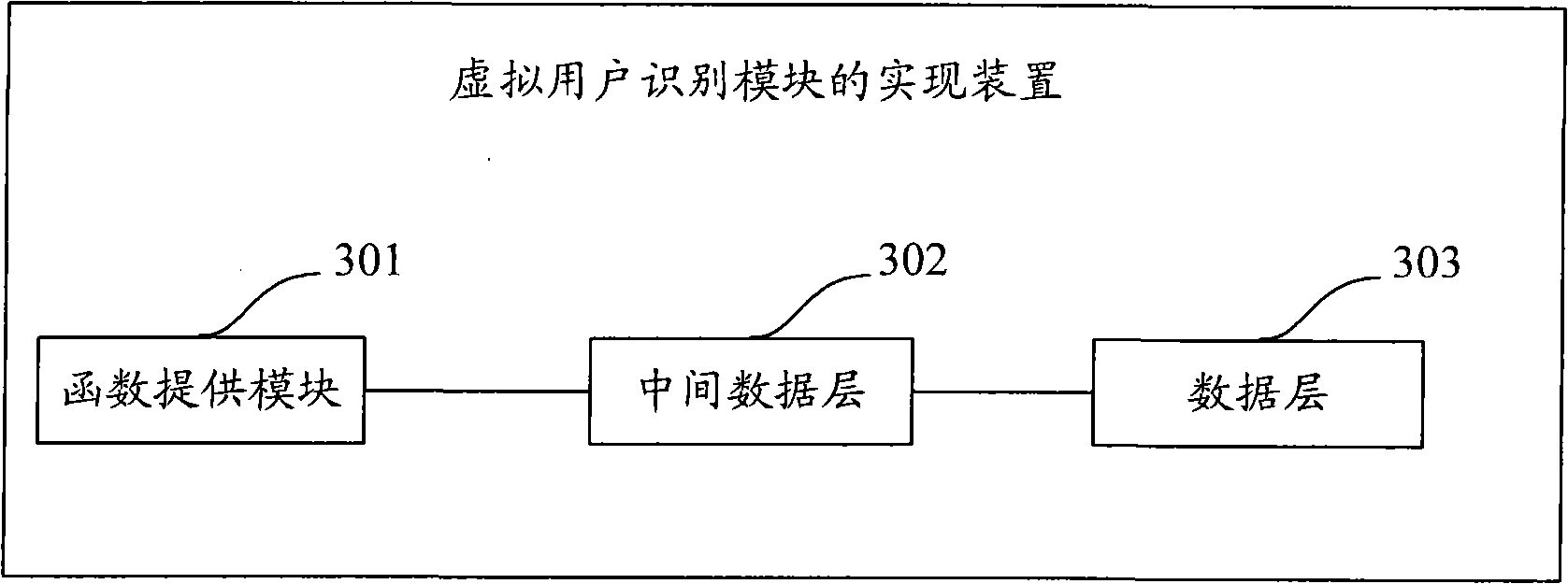

Realization method, device and testing system for virtual user identification module

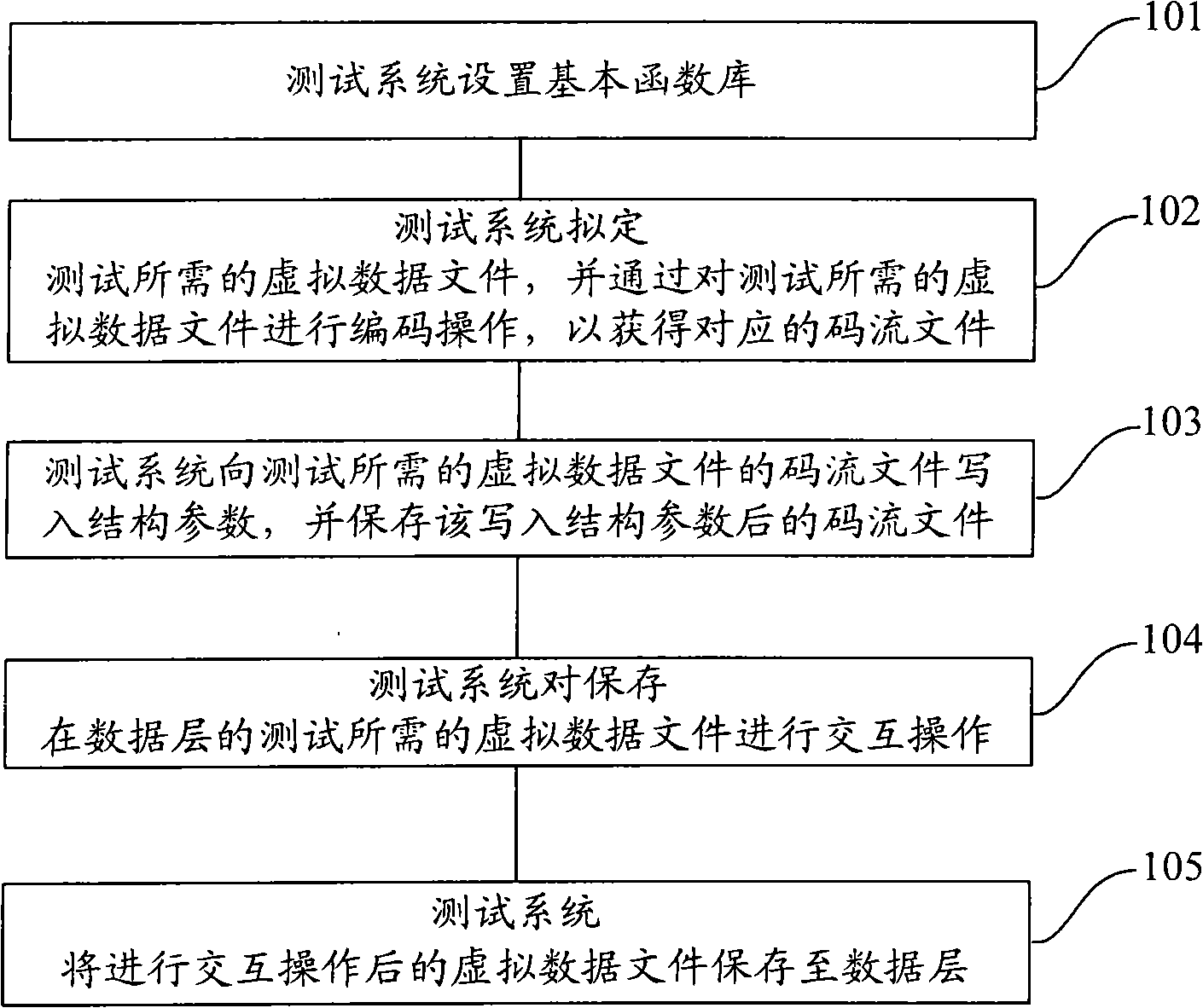

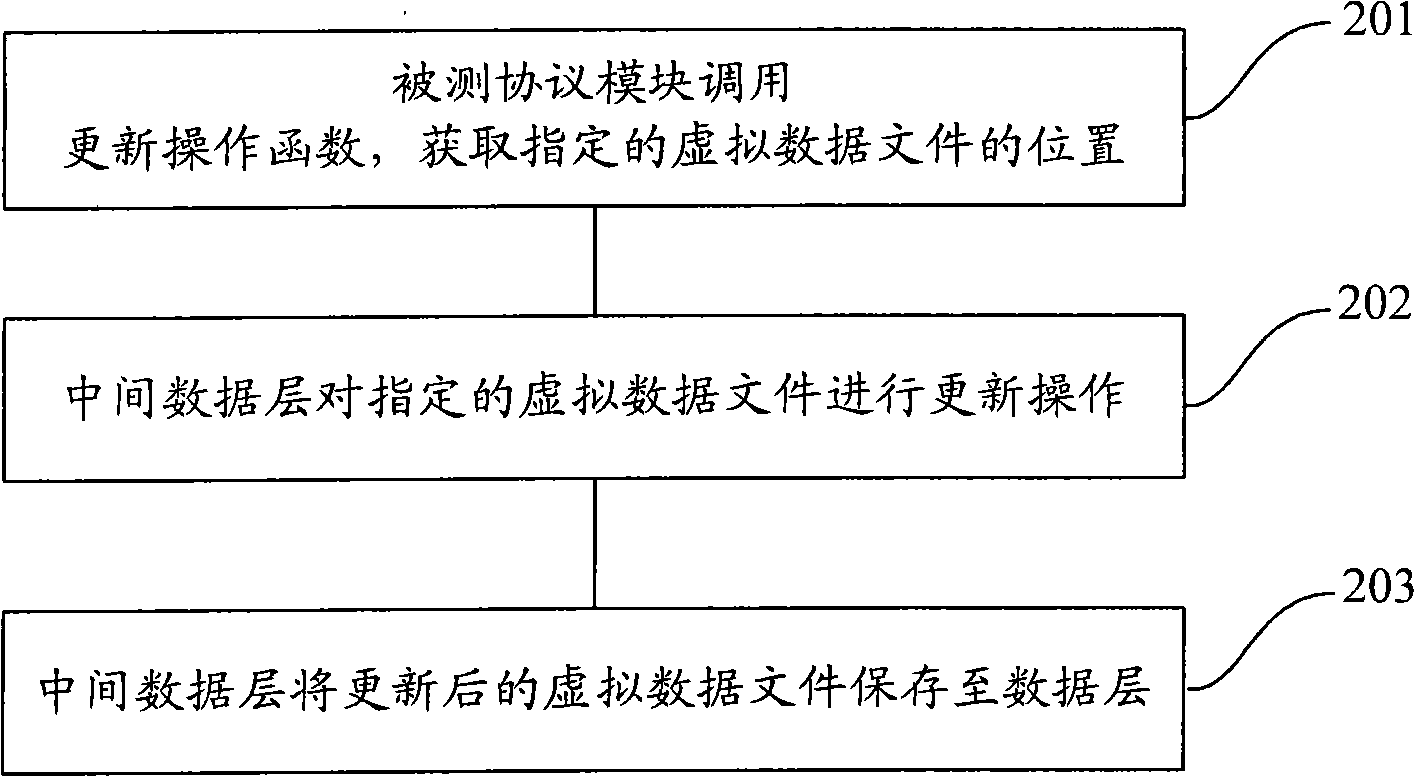

The invention discloses a realization method for a virtual user identification module, comprising the following steps of: arranging a basic function library, initiating virtual data files, invoking the operation function in the arranged basic function library by a tested protocol module; and utilizing a middle data layer in the virtual user identification module to carry out an interactive operation with the virtual data file stored in the data layer of the virtual user identification module. In order to realize the method, the invention provides a realization device for the virtual user identification module, comprising a function providing module, the middle data layer and the data layer. Correspondingly, the invention also provides a testing system that comprises the virtual user identification module and the tested protocol module. Therefore, the method, the device and the system can simulate the real general user identification module / user identification module, thus carrying out complete test and verification on the protocol module further.

Owner:ZTE CORP

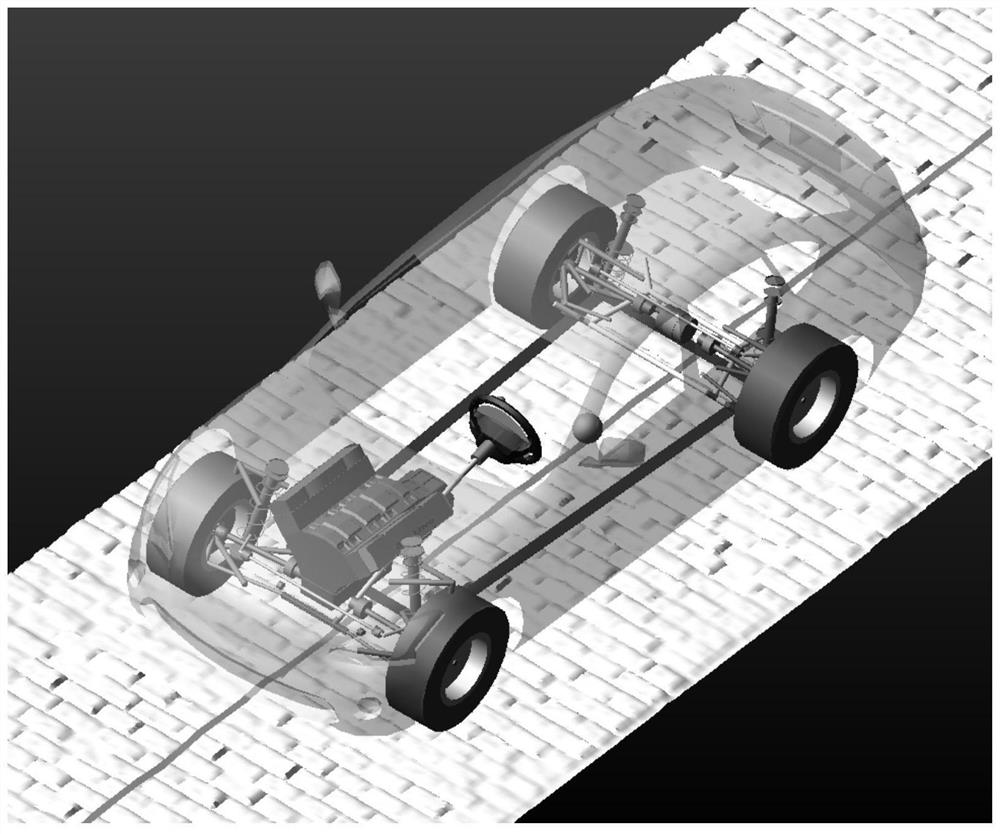

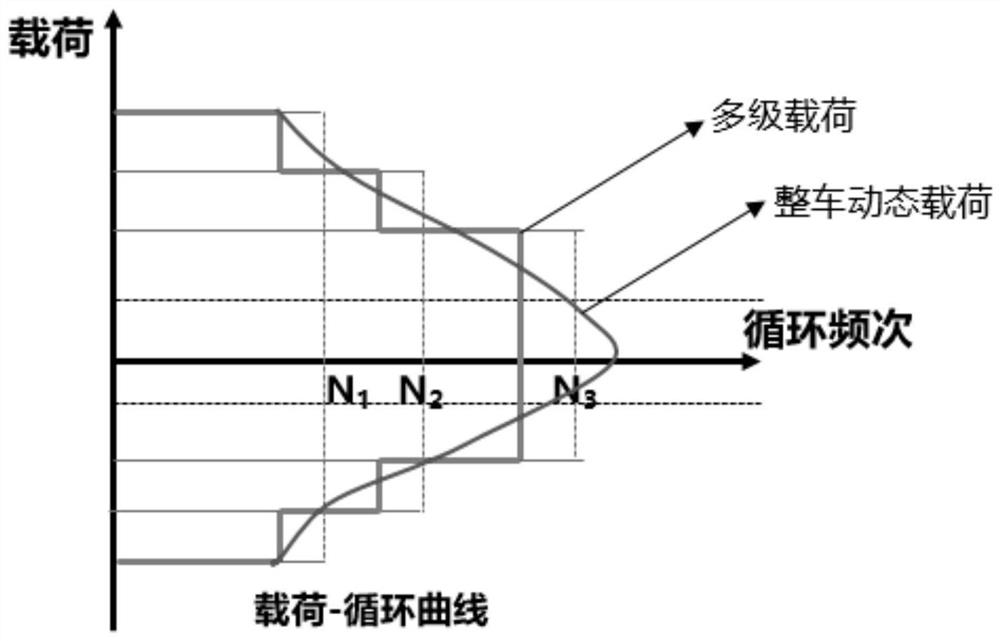

Vehicle bench test load spectrum analysis method based on virtual test field

PendingCN113010964AFully verifiedImprove molding qualityGeometric CADDesign optimisation/simulationBench testRoad surface

The invention discloses a vehicle bench test load spectrum analysis method based on a virtual test field. The method comprises the following steps: establishing a digital test field durable pavement model; establishing a digital tire model; establishing a vehicle multi-body dynamic model, and performing calibration; simulating a virtual test field, and extracting a virtual load signal; preprocessing and counting the dynamic load; and carrying out test bed load spectrum conversion based on amplitude cumulative frequency. According to the method, dynamic load data of key parts such as a vehicle body and a chassis suspension can be obtained through virtual test field simulation in the early stage of vehicle development, the dynamic load is preprocessed, then compression and pseudo damage evaluation are performed on the load, and finally, a multi-stage constant-amplitude load spectrum is equivalently converted, so the standard load spectrum for the fatigue durability test of the rack test bed is manufactured, full verification of fatigue durability analysis of the vehicle rack is ensured, and the product forming quality is improved.

Owner:慧勒智行汽车技术(昆山)有限公司

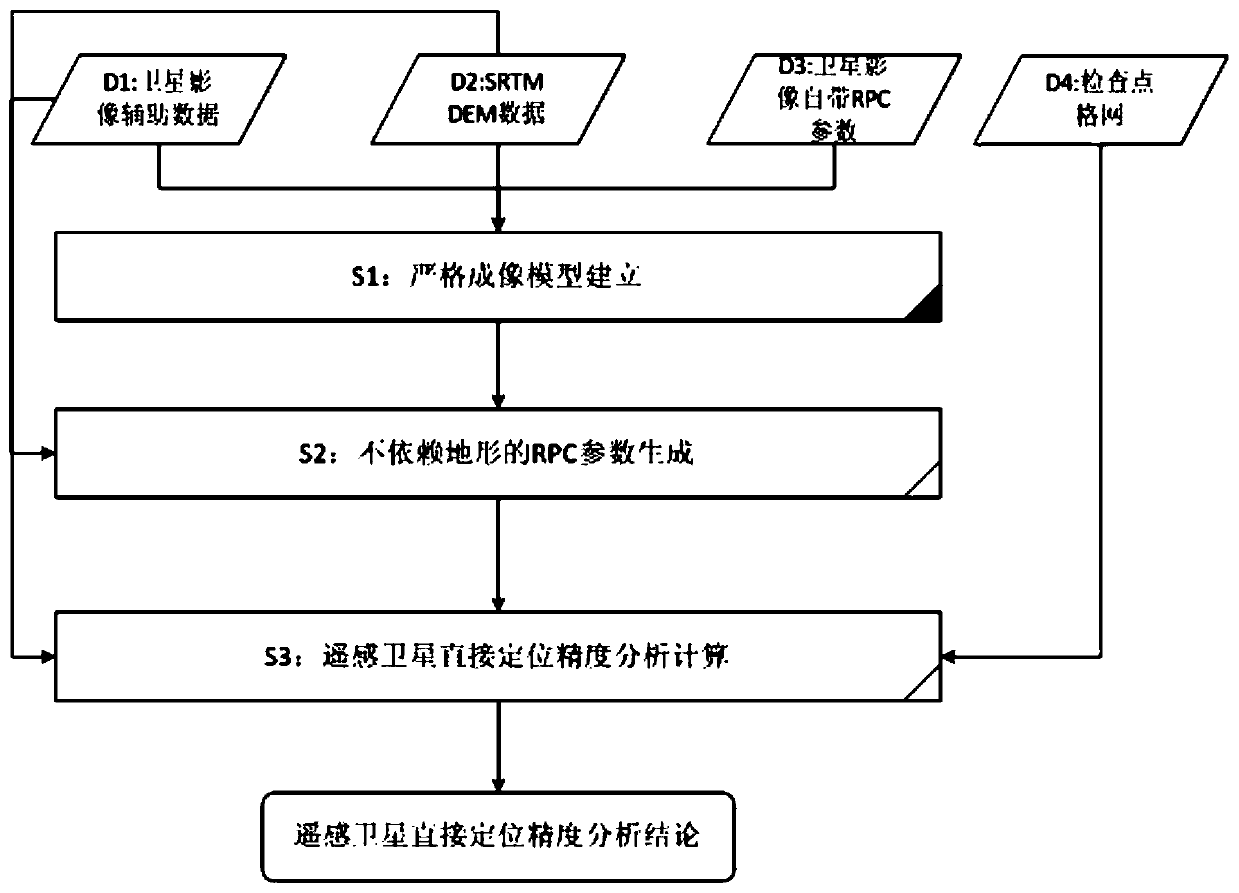

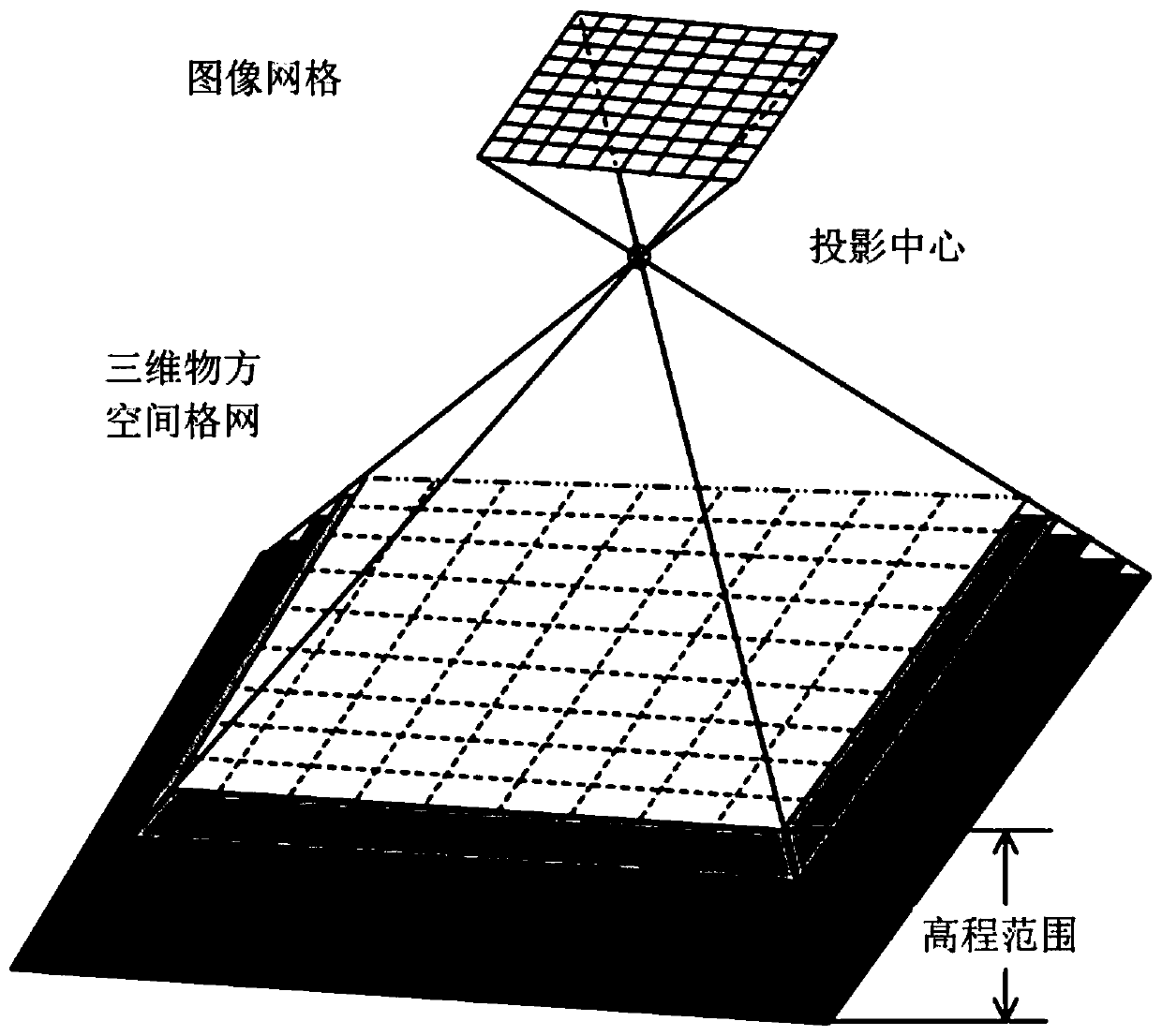

Geometric positioning precision analysis method for remote sensing satellite without ground control point

ActiveCN110378001AFully verifiedHigh precisionDesign optimisation/simulationSpecial data processing applicationsTerrainBaseline data

A geometric positioning precision analysis method for a remote sensing satellite without a ground control point comprises the following steps: S1, establishing a strict imaging model, and rewriting the strict imaging model to obtain a strict model geometric positioning equation; S2, generating RPC parameters independent of terrains; S3, checking the absolute geometric positioning precision of theRPC coefficient of the image product according to an image angular point method, and judging whether the RPC coefficient of the image product can be used as the reference data of geometric precision analysis and checking or not; verifying the internal coincidence precision of the RPC coefficient generated without depending on a terrain method according to a check point method, and eliminating errors possibly introduced by RPC coefficient calculation; according to a cross validation method, obtaining the relative precision of the RPC coefficient generated without depending on a terrain method and the RPC coefficient of the image data product; and obtaining a direct geometric positioning precision analysis conclusion of the on-orbit optical remote sensing satellite. According to the method,the analysis and calculation of the geometric positioning precision of the remote sensing satellite are realized.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

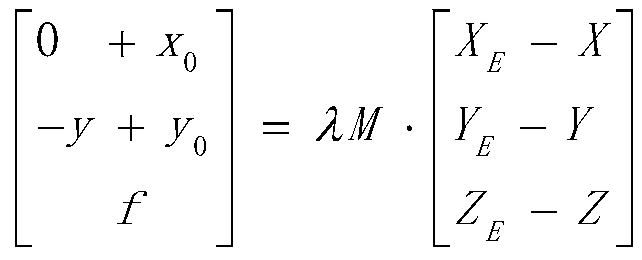

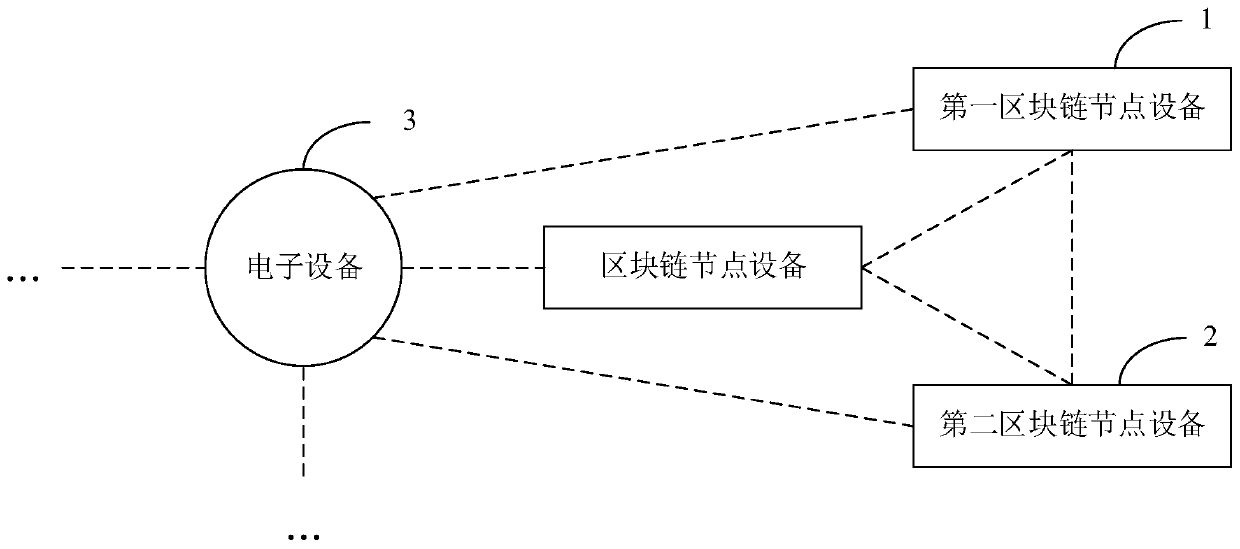

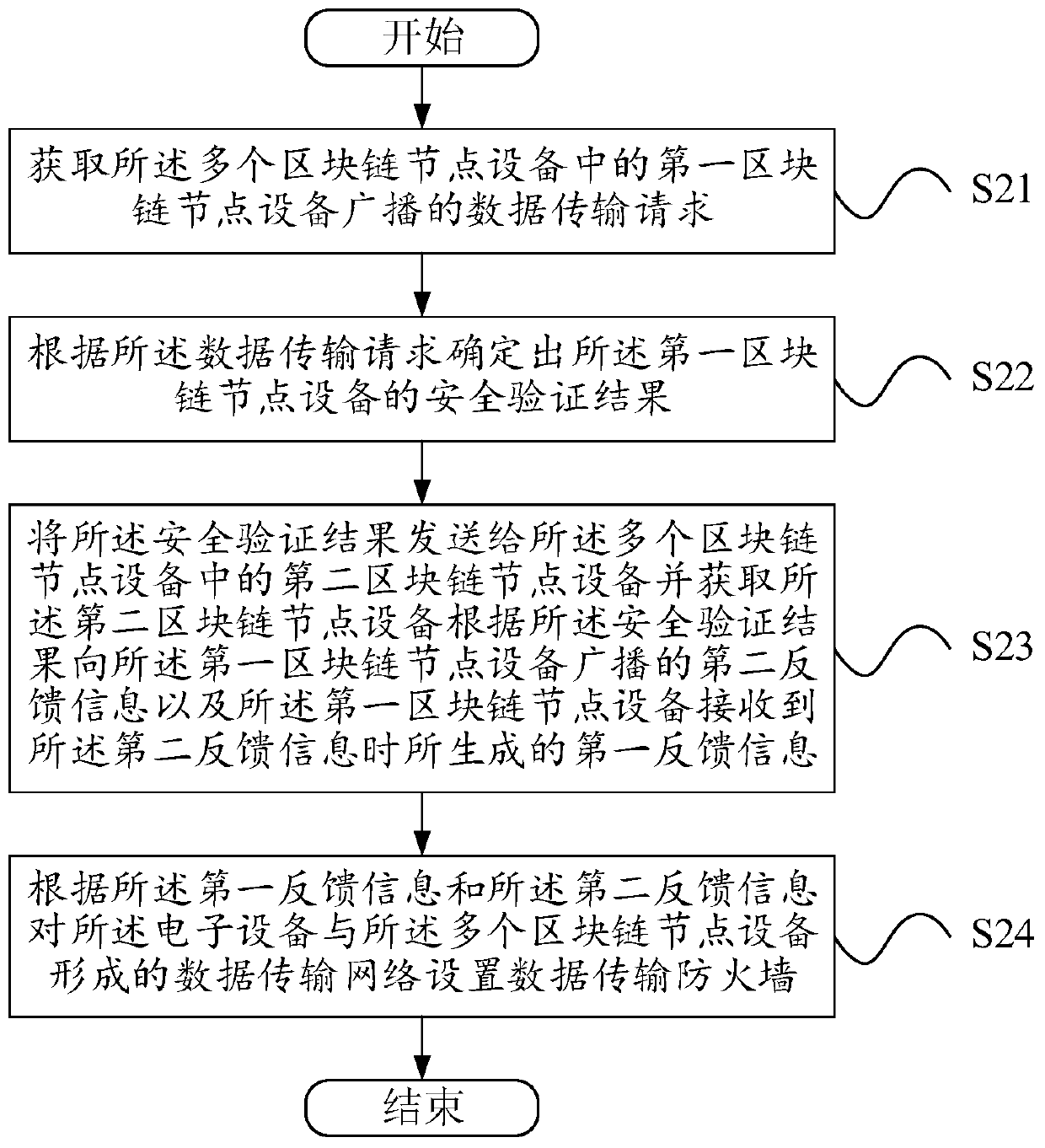

Data transmission method and device based on block chain and electronic equipment

ActiveCN110933072AImprove timelinessEnsure data transmission securityDatabase distribution/replicationDigital data protectionData transmissionSecurity validation

The embodiment of the invention discloses a data transmission method based on a block chain. In this method, the second blockchain node device is prevented from carrying out security verification on the data transmission request, so that the second blockchain node device is prevented from allocating time slice resources for security verification and encryption algorithm processing; the second blockchain node device can directly respond according to the security verification result sent by the electronic device, and the timeliness of data transmission interaction between the second blockchain node device and the first blockchain node device is improved. The electronic equipment can fully and comprehensively verify the data transmission request, thereby ensuring the data transmission security between the second blockchain node device and the first blockchain node device. By setting the data transmission firewall, the data transmission potential safety hazard between the second blockchainnode device and the first blockchain node device can be eliminated, and thus the data transmission security of the whole data transmission network is ensured.

Owner:宁波平辅寅保险科技有限公司

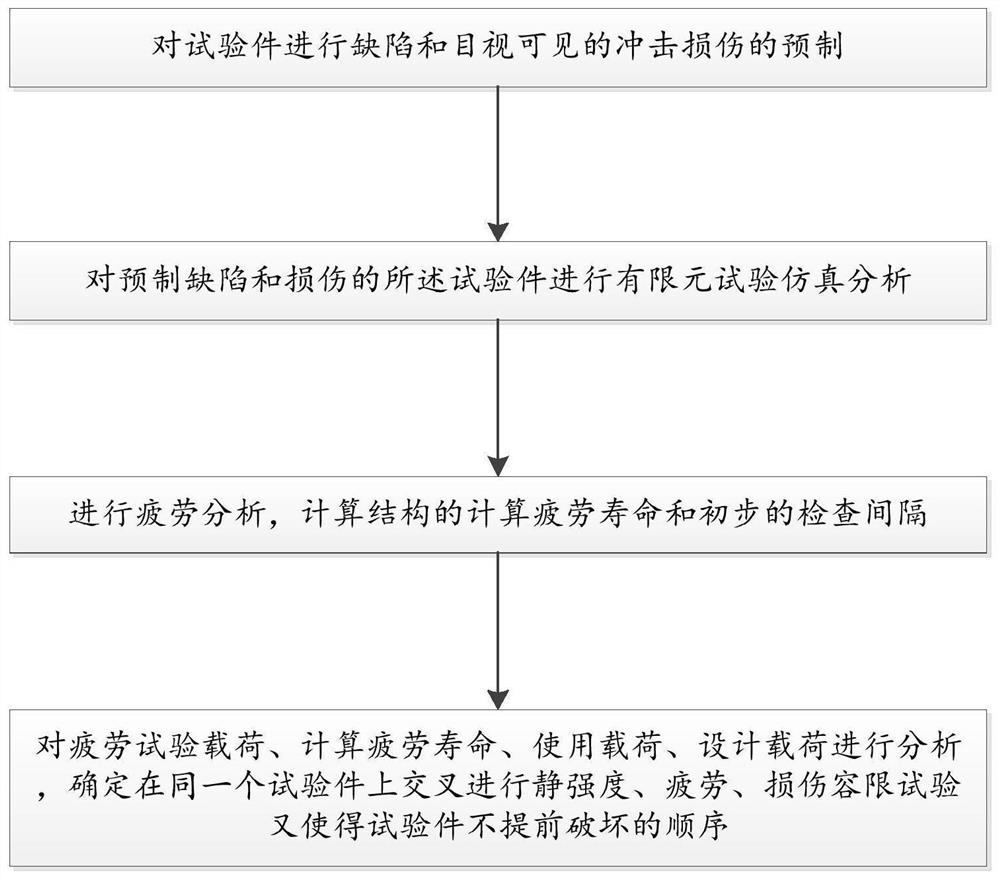

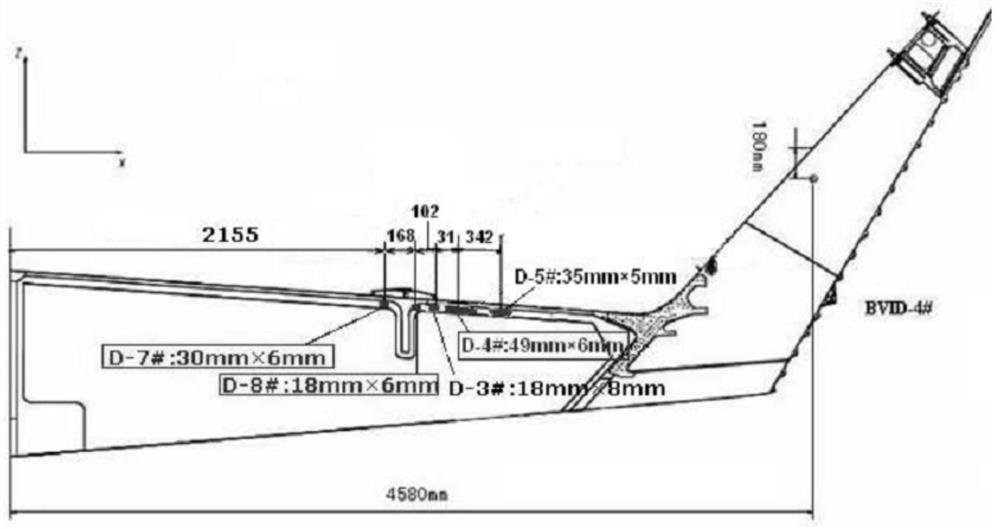

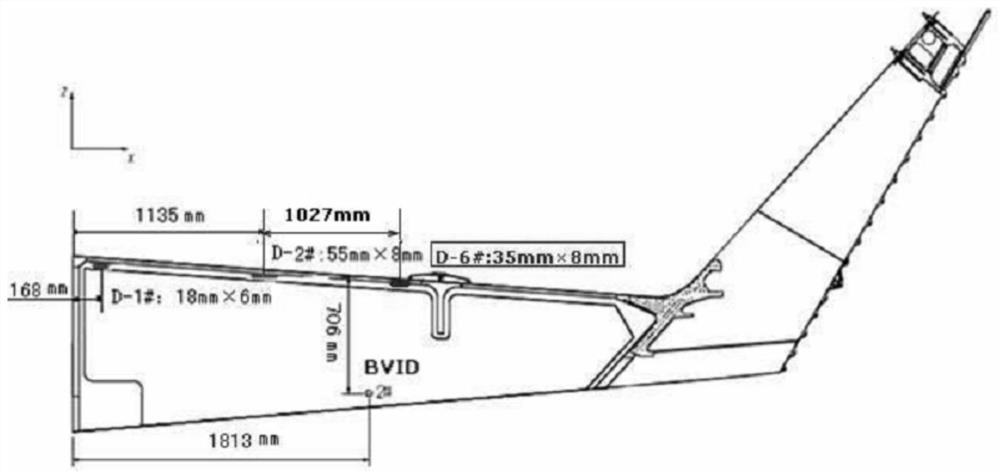

Composite material structure static strength and fatigue strength integrated test verification method

ActiveCN112268799AShorten the development cycleReduce in quantityMachine part testingSustainable transportationStatic strengthFlight safety

The invention discloses a composite material structure static strength and fatigue strength integrated test verification method. According to the method aiming at material characteristics and structure of a composite material, the requirements that cyclic load needs to be considered in composite material static strength verification, residual bearing capacity needs to be considered after the cyclic load, and residual strength evaluation needs to be carried out after fatigue verification are met, actual experience is combined, the method for verifying the static and fatigue test of the composite material structural component on the same test piece is provided, the technical bottleneck of verification of the composite material structural component is solved, a structural static strength andfatigue strength integrated verification chain of a composite material structural component 'limited load static-fatigue-limit load static-fatigue (damage tolerance)-limited (limit) load static force'is formed, so that the composite material structural component is fully verified, the development period can be shortened, the number of test pieces is reduced, the cost is reduced, and the flight safety level of an aircraft is further improved.

Owner:CHINA HELICOPTER RES & DEV INST

Chinese classical garden knowledge graph completion and cognitive reasoning method

PendingCN112463987AImplement extractionIncrease profitNeural architecturesText database queryingMachine learningInformation extraction

The invention provides a Chinese classical garden knowledge graph completion and cognitive reasoning method, which comprises the following steps of: 1, executing the function of a system 1, namely a perception system, in a recognition science double-channel theory, and realizing information extraction of entities and relationships; and 2, executing the system 2 in the acknowledged scientific double-channel theory, namely analyzing the function of the system, performing reasoning, firstly judging whether knowledge graph completion is continuously performed or not, and if completion is completed, stopping the algorithm flow. The method of the invention mainly has the following technical advantages: 1, the method has the capability of third-generation artificial intelligence cognitive reasoning; 2, the utilization rate and the execution efficiency of information are improved; and 3, the method can be widely applied to national classical gardens.

Owner:中国园林博物馆北京筹备办公室 +1

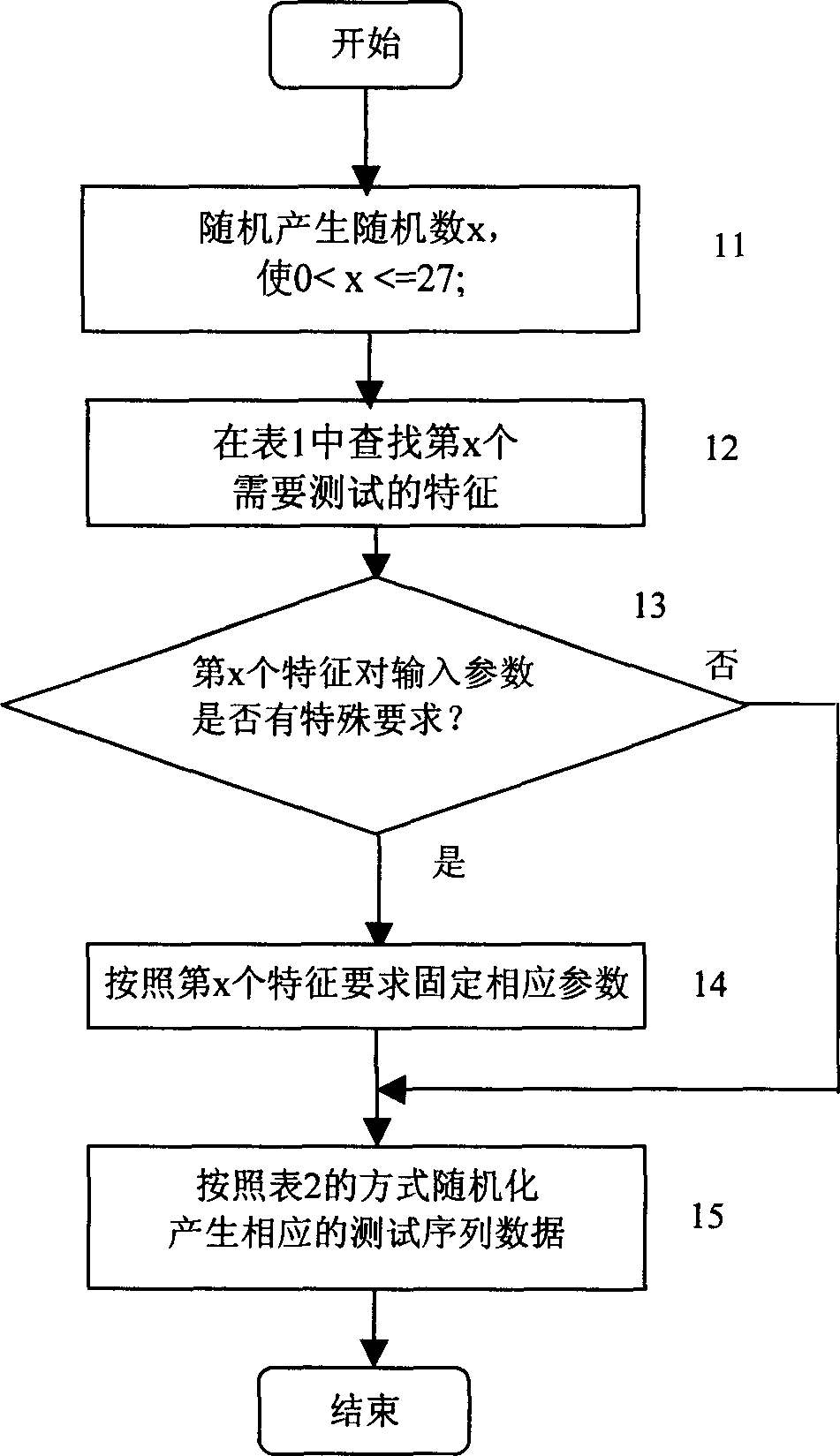

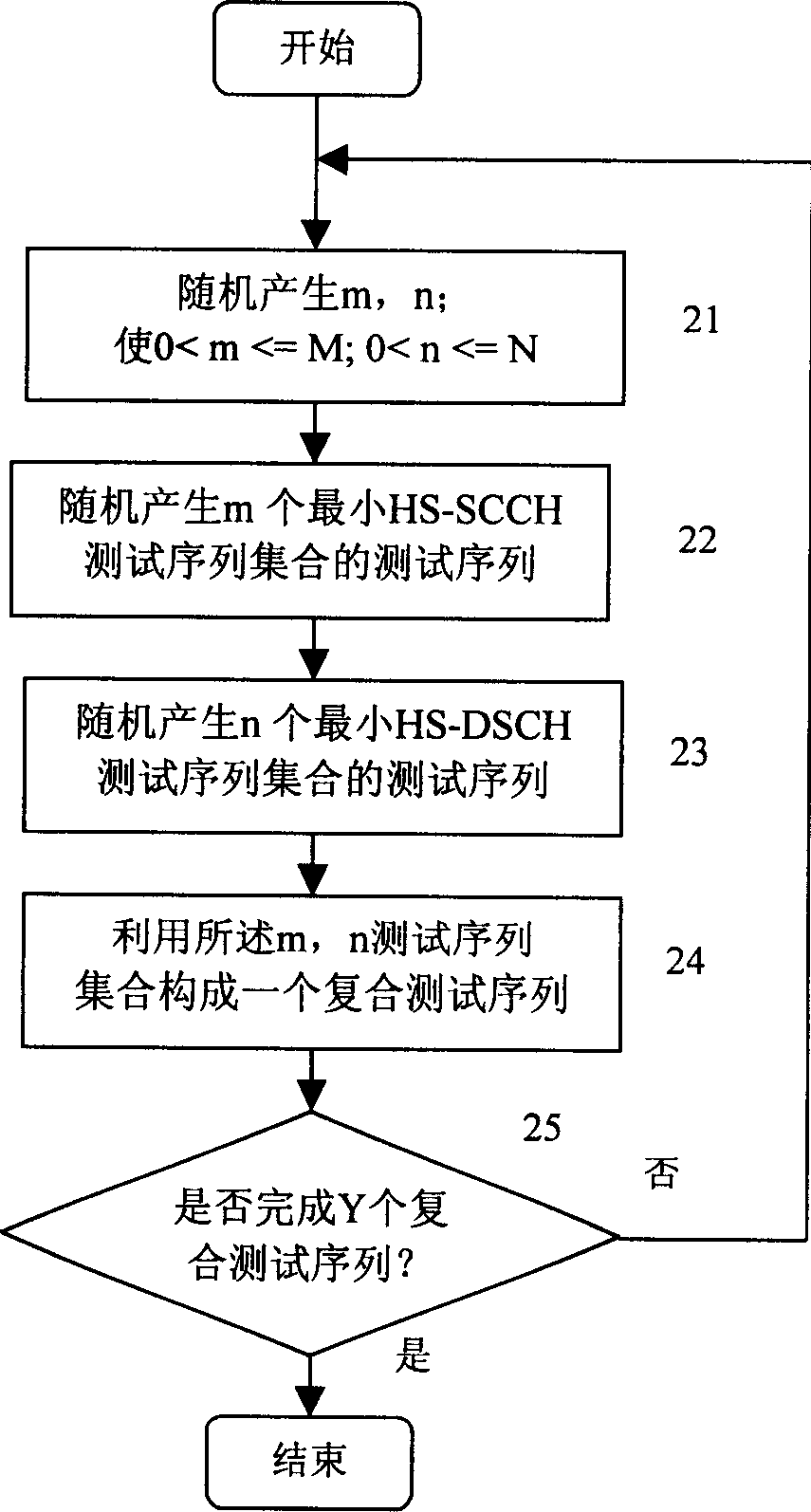

Method of testing transmission performance of HSDPA channel

InactiveCN1809001AImprove accuracyGuarantee sufficiencyData switching networksEngineeringTest sequence

This invention relates to method to test HSDPA signal channel transmission property, which adopts One random generation HSDPA transmission and physical signal channel testing sequence method to generate test sequence and testing the transmission property based on the said test sequence; testing sequence generation through divided HSDPA transmission and physical signal channel each process phase to give one test sequence minimum set and then on the base forming abundant test sequence set through overlapping.

Owner:HUAWEI TECH CO LTD

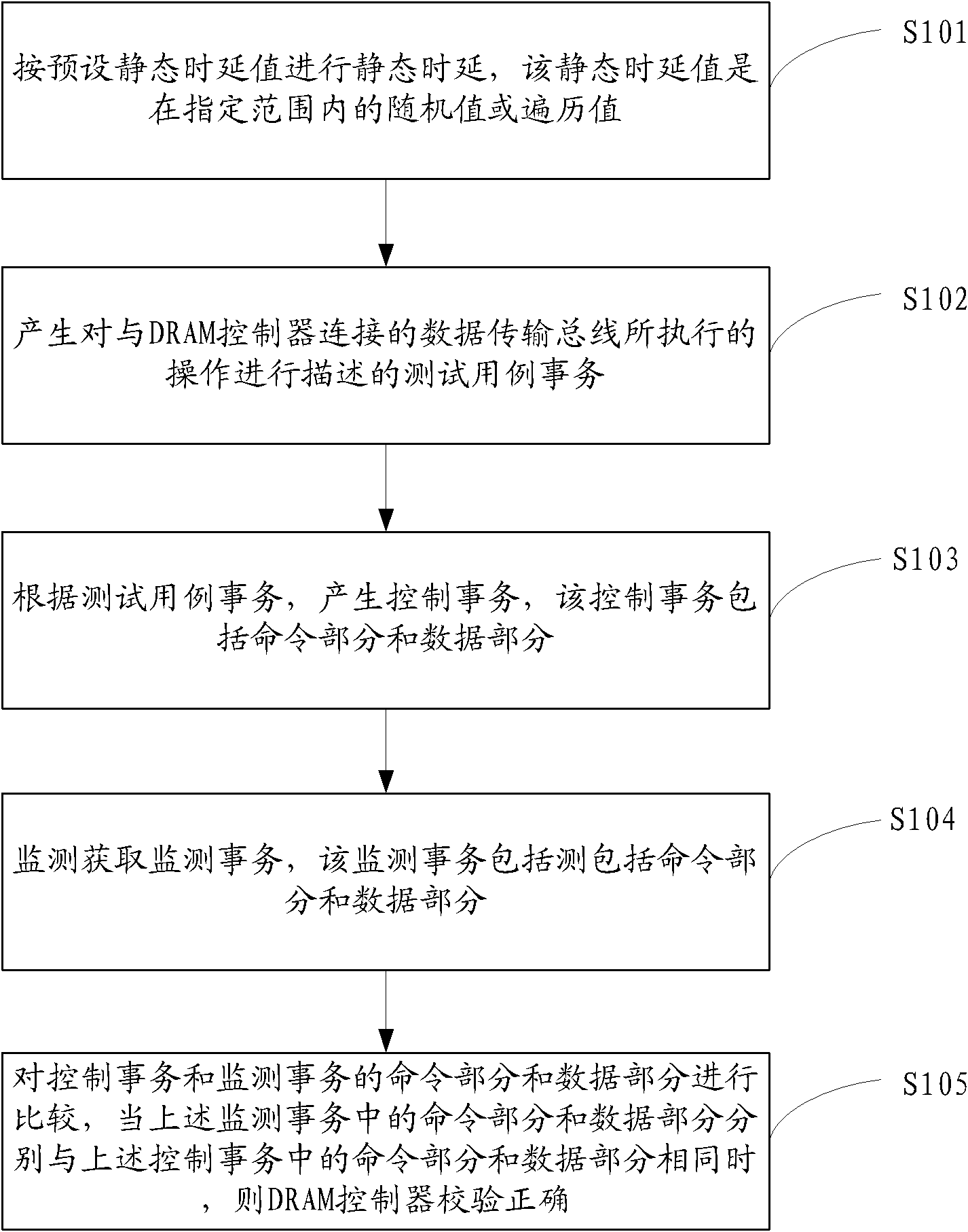

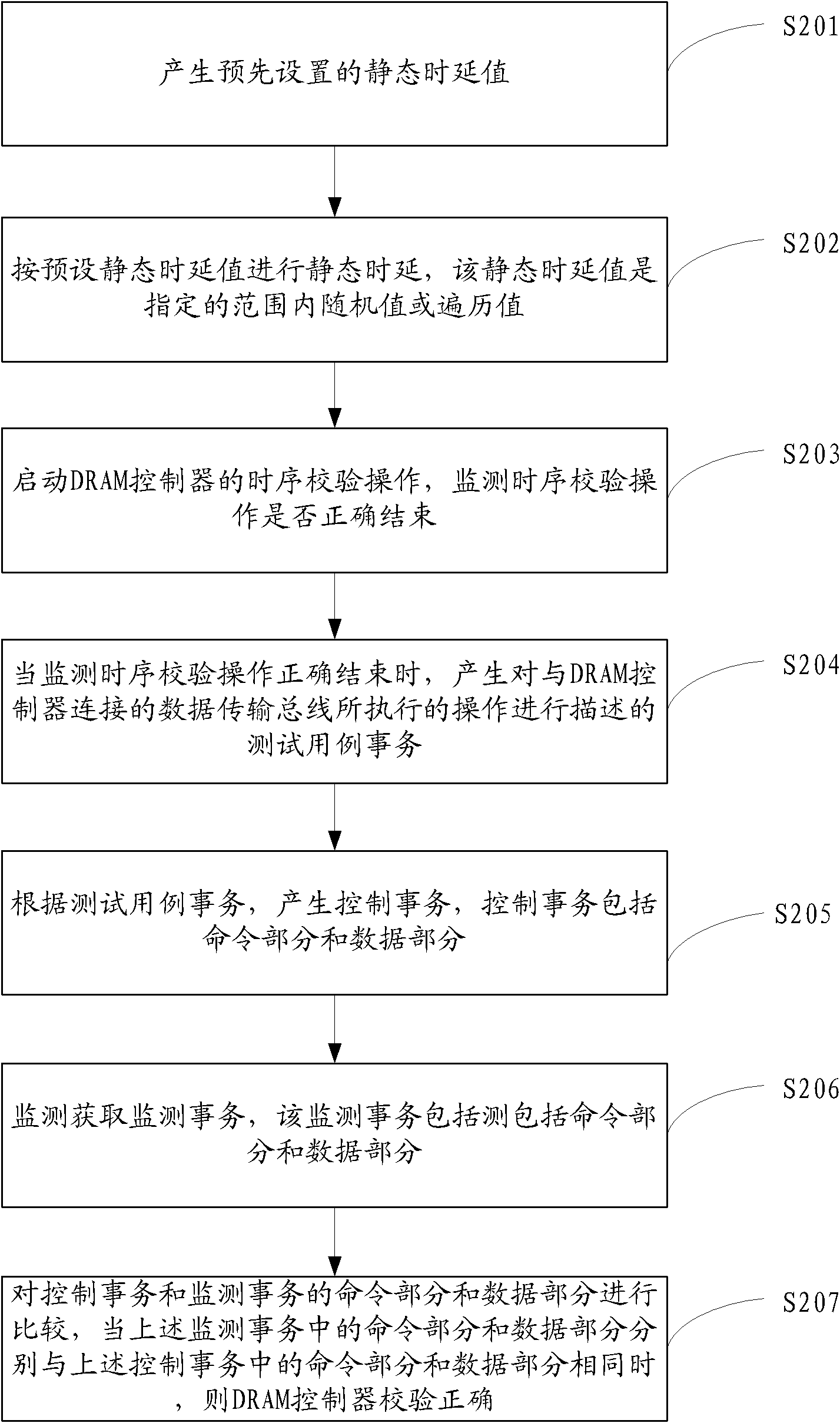

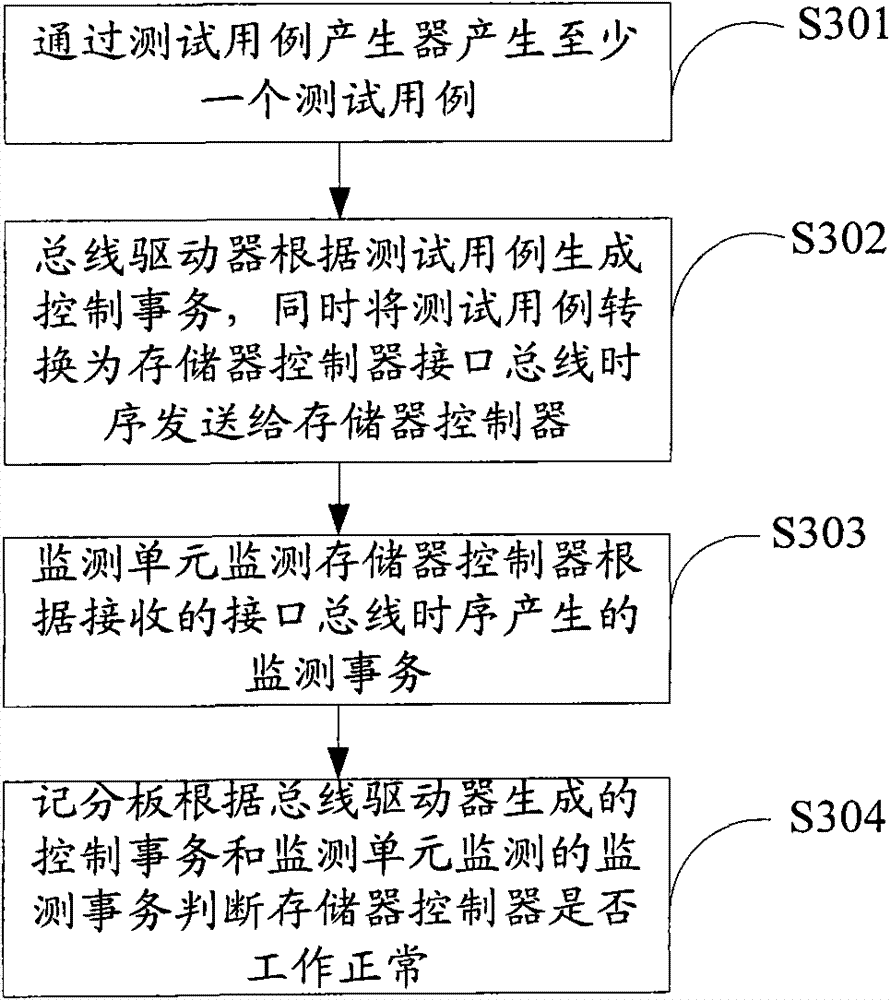

Method and system for verifying timing sequence calibration function of dynamic random access memory (DRAM) controller

ActiveCN102385547AFull verification of the calibration functionThe checksum function is verified for fullFunctional testingStatic random-access memoryRandom access memory

The invention is applied to the technical field of electronics, which provides a method and a system for verifying a timing sequence calibration function of a dynamic random access memory (DRAM) controller. The method comprises steps of performing static delay according to preset static delay value which is random value or traverse value in designated range; generating a test case event describing operations executed by a data transmission bus connected with the DRAM controller; generating a control event according to the test case event; monitoring and obtaining a monitoring event which includes an order part and a data part; and obtaining accurate timing sequence calibration of the DRAM controller when the order part and the data part in the monitoring event are respectively identical with an order part and a data part in the control event. By means of the preset static delay value generated in random or traversal mode in the designated range, the timing sequence calibration function of the DRAM controller is verified, thereby achieving the purpose of verifying the timing sequence calibration function as comprehensive as possible and obtaining complete verification.

Owner:ANYKA (GUANGZHOU) MICROELECTRONICS TECH CO LTD

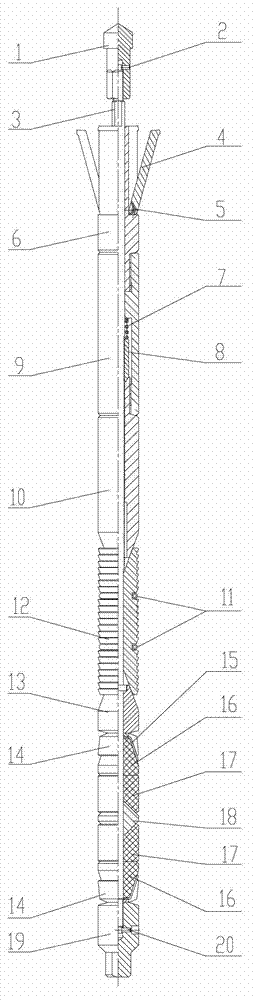

Over chuck distance steel wire operation slip plug

The invention relates to an over chuck distance steel wire operation slip plug special for snubbing operation of a water injection well during oil extraction. The plug comprises a fishing cap and a fixed supporting seat, wherein the fishing cap is connected with a center rod; the outer wall of the center rod is sequentially sleeved on a positioning supporting seat, a locking ring outer cylinder, a slip upper seat, a slip and a slip lower seat; the lower side of the slip lower seat is provided with two rubber cylinder sheaths and a supporting seat; an outer rubber cylinder and an inner rubber cylinder are arranged between the two rubber cylinder sheaths. According to the plug, the outer diameter of the plug is smaller than the inner diameter of an eccentric water distributor for the water injection well, so that a tail pipe can be plugged at a chuck distance section under the conditions that the original well pipe column scales severely, and the drift diameter is reduced; and the interior of a part below a tubing coupling at assigned depth can be plugged by mechanically shocking the plug through a steel wire operation tool ring under the well.

Owner:PETROCHINA CO LTD +1

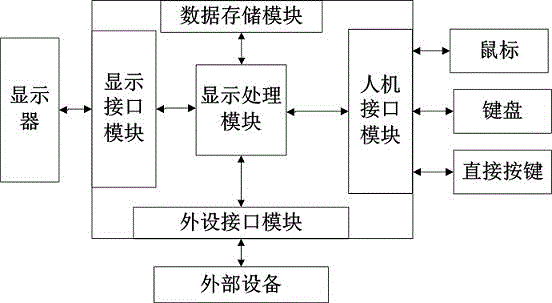

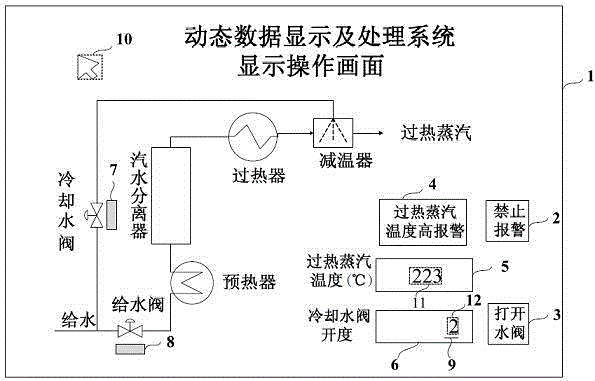

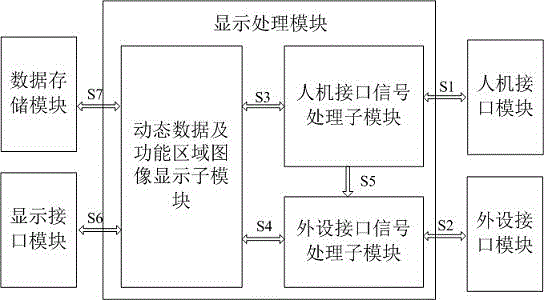

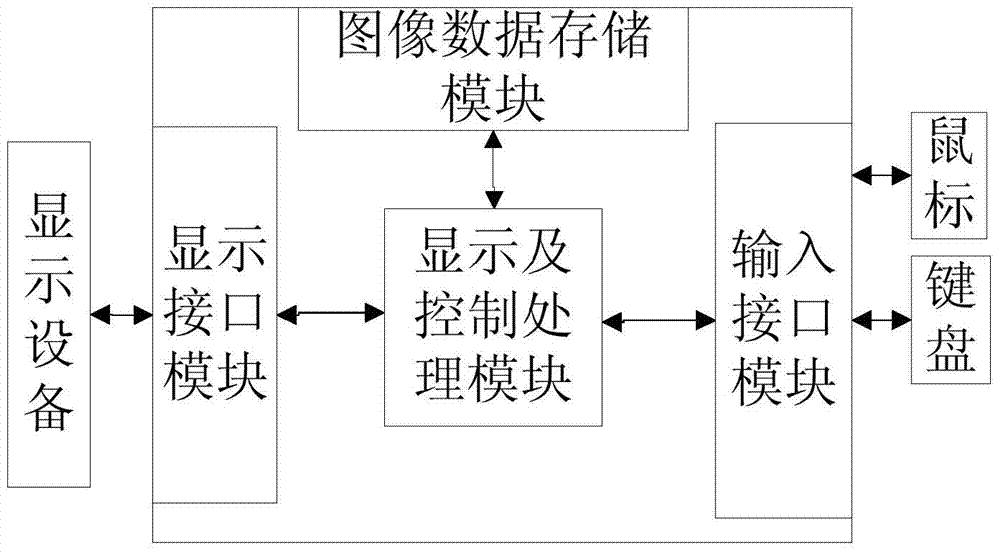

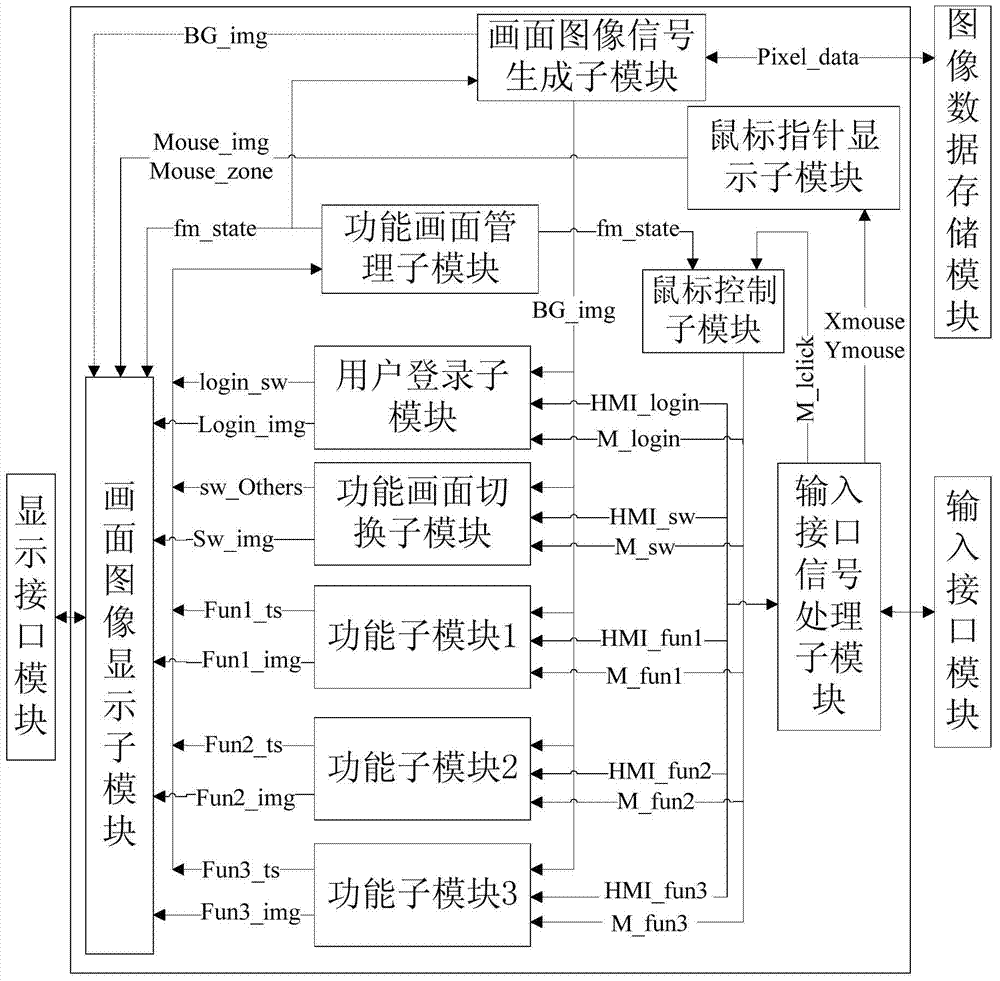

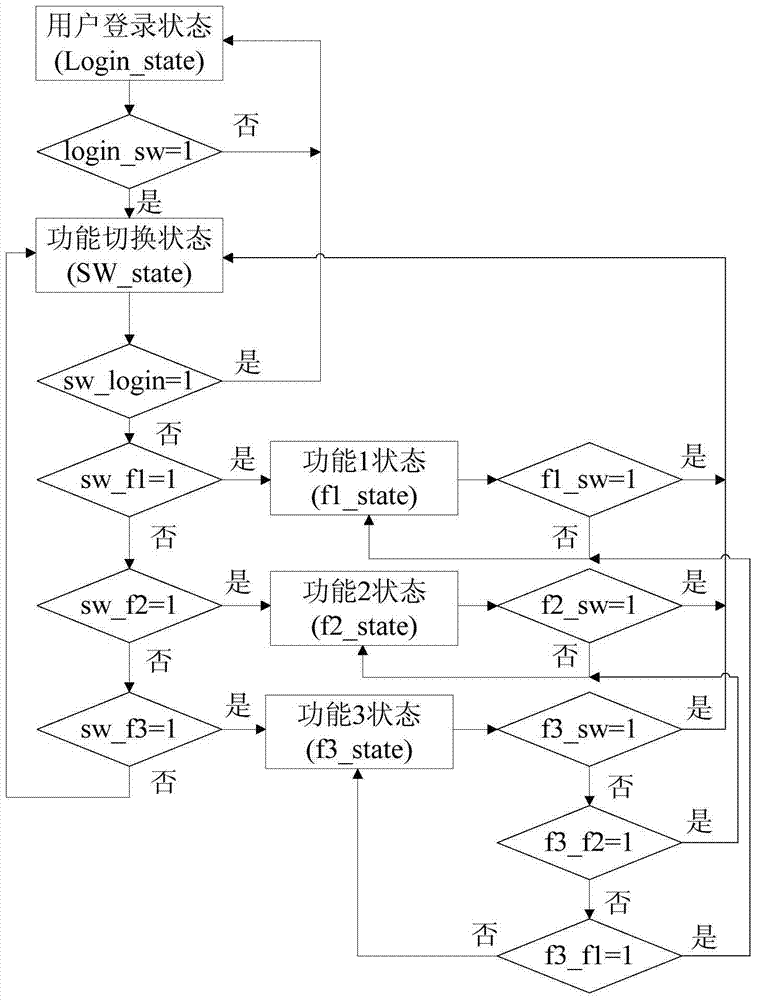

Dynamic data displaying and processing system and method

InactiveCN105045547AImprove information securityImprove reliabilityDigital output to display deviceData displayOperational system

The invention discloses a dynamic data displaying and processing system. The system comprises an input device, a displaying and processing module, a display interface module, an external interface module, a man-machine interface module, a display and data storage module. Operation frame displayed on a screen of the display comprises a background frame area, an alarm flicker area, a mouse control area, a dynamic data display area, a dynamic data background area, a user input data display area, a user input data background area, a user input active line area, an external device state area and a mouse image area. The invention further relates to a dynamic data displaying and processing method. No CPU chip, no soft core / hard core are adopted by the dynamic data displaying and processing system and method, and no operation system and application software are contained, so fully test and verification can be conveniently implemented, so excellent reliability and information safety can be achieved.

Owner:闫明霞

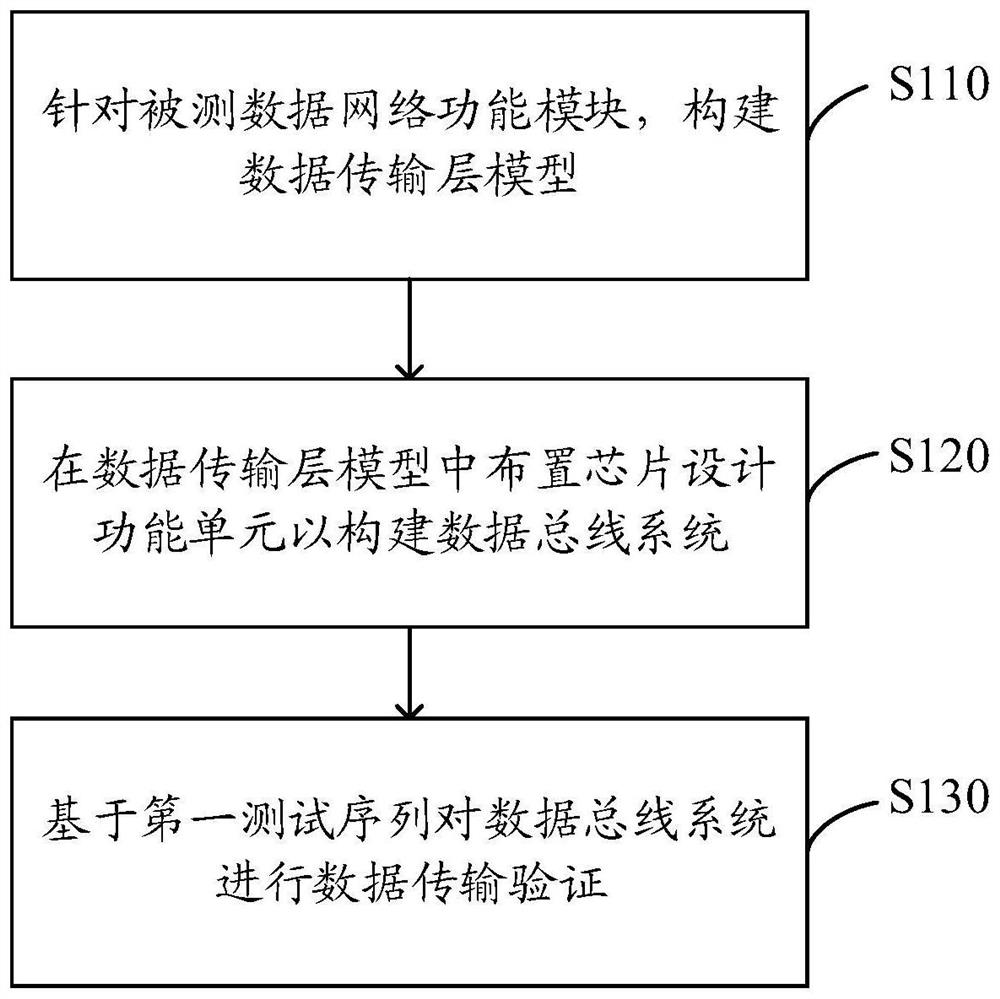

Data network design verification method and device and verification equipment

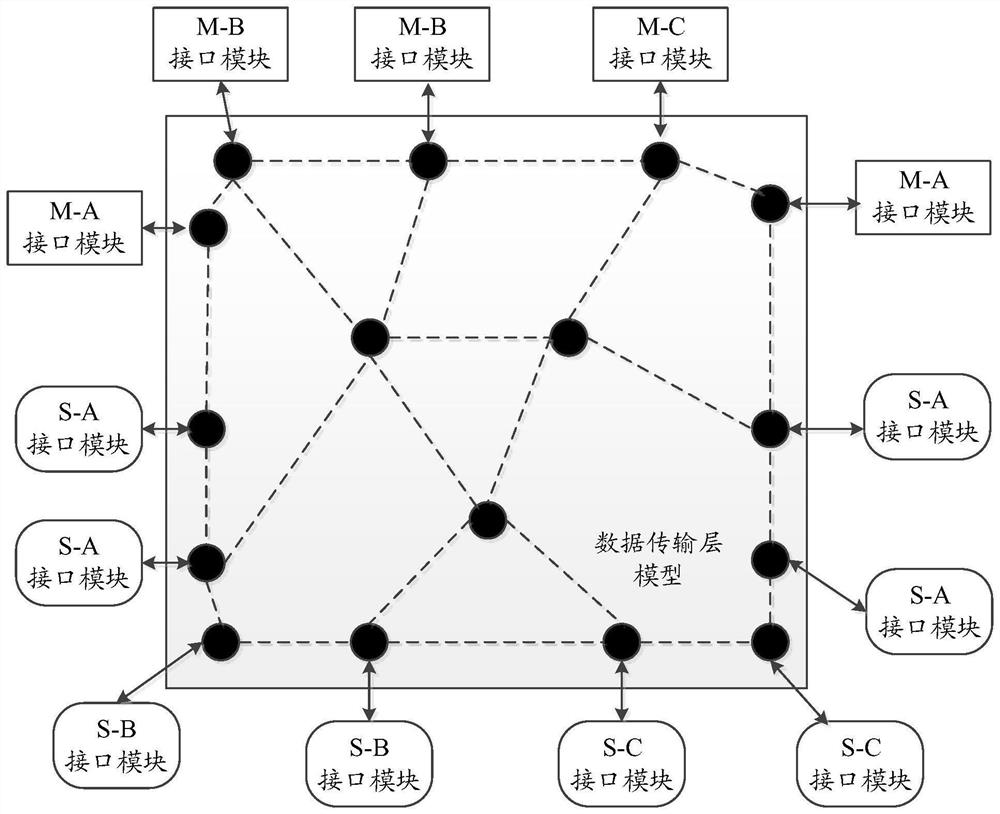

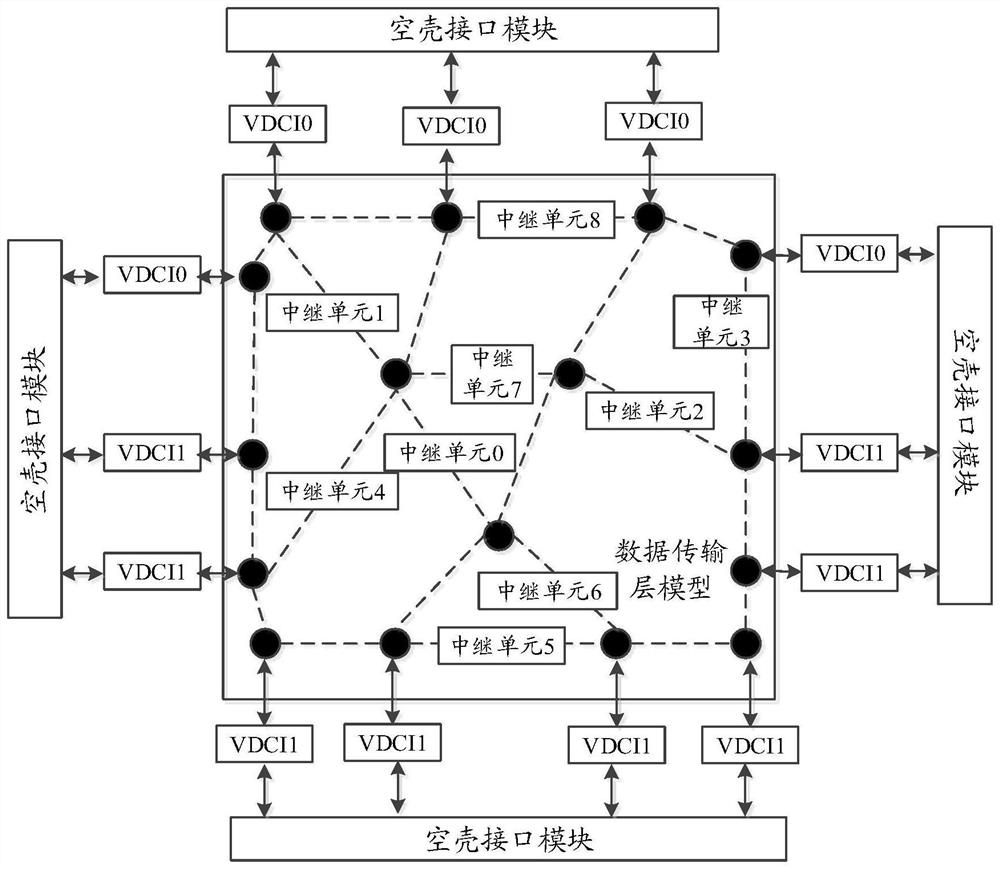

PendingCN112597719AFully verifiedComprehensive Data ValidationCAD circuit designSpecial data processing applicationsComputer hardwareTrunking

The invention provides a data network design verification method and device and verification equipment. The data network design verification method comprises the following steps: constructing a data transmission layer model for a tested data network function module; arranging a chip design function unit in the data transmission layer model to construct a data bus system; and performing data transmission verification on the data bus system based on the first test sequence. The chip design function unit comprises a clock domain crossing interface module, a voltage domain crossing interface module or a relay unit.

Owner:HYGON INFORMATION TECH CO LTD

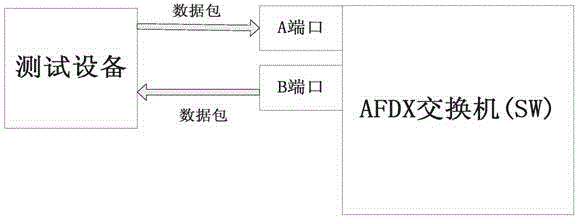

Test method for transmission performance of AFDX switch

ActiveCN105376118AMeet functional testing requirementsFully verifiedData switching networksTest requirementsFunctional requirement

The invention provides a test method of the transmission performance of an AFDX switch. According to the test method, transmission virtual links (VL) are reasonably allocated, and port full-flow transmission can be realized, and function test requirements of the transmission ports of the AFDX switch under a limit (full-flow transmission) condition can be satisfied. With the test method adopted, transmission performance test can be performed on 24 ports of the AFDX switch fast and effectively, and therefore, the requirements of protocols can be satisfied.

Owner:西安翔腾微电子科技有限公司

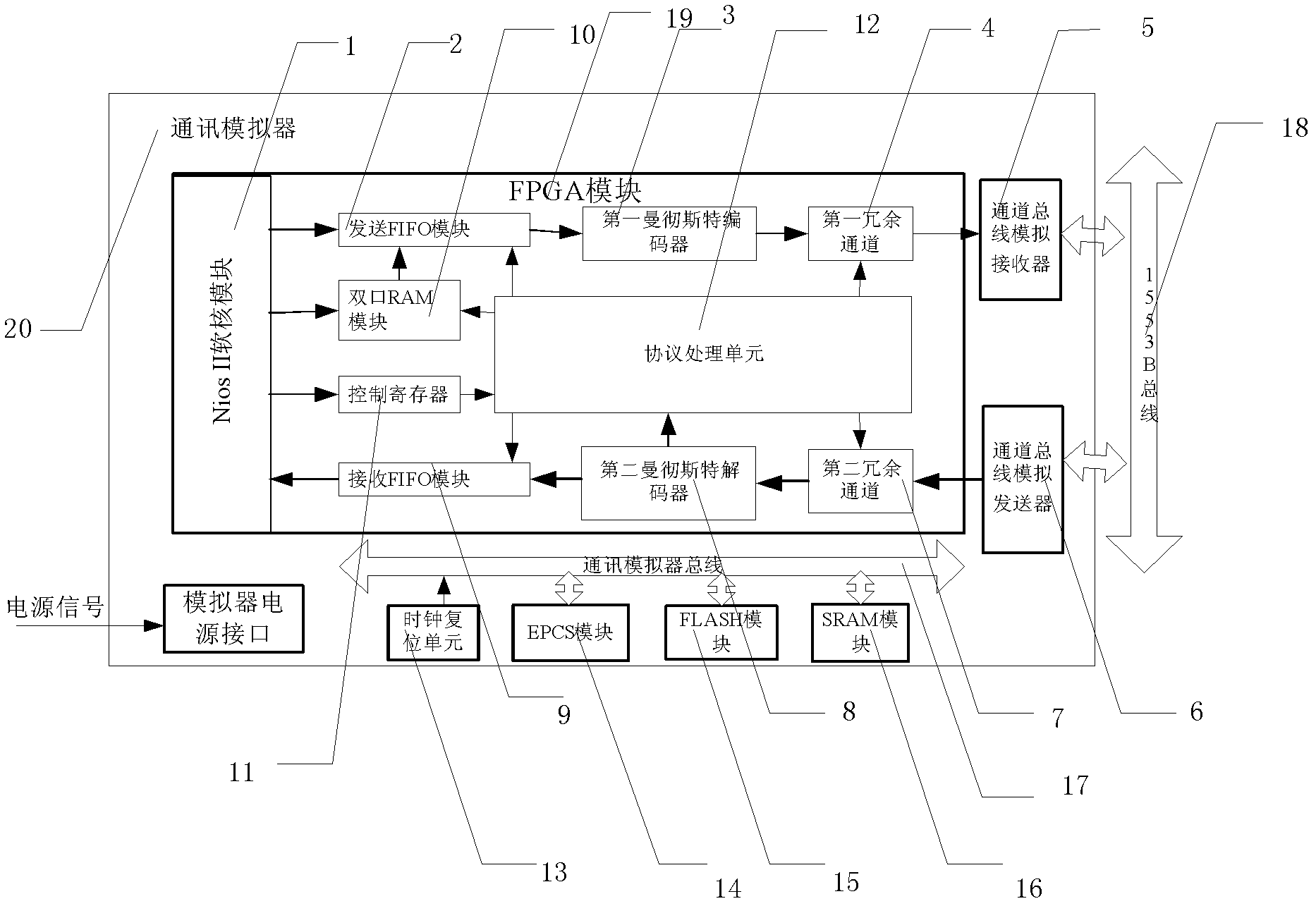

Nios II soft-core based high-speed 1553B communication equipment simulator on missile

InactiveCN102497375AImprove real-time performanceFully verifiedBus networksManchester codeEmbedded system

The invention relates to a Nios II soft-core based high-speed 1553B communication equipment simulator on a missile, which aims to solve the problems that existing bit rate cannot meet the requirement of real-time data transmission, size is large, power consumption is high and flexibility in use is poor. The Nios II soft-core based high-speed 1553B communication equipment simulator comprises an existing communication equipment simulator, a Nios II soft-core module, a channel bus simulation receiver and a channel bus simulation transmitter, signals of the Nios II soft-core module are transmitted to a Manchester encoder through an FIFO (first in first out) transmission module, are transmitted to a 1553B bus through a redundancy channel and the channel bus simulation receiver, the 1553B bus is connected with the channel bus simulation transmitter and transmits the signals to a signal input end of an FIFO receiving module through the redundancy channel and the Manchester encoder and then outputs to a signal receiving end. The Nios II soft-core based high-speed 1553B communication equipment simulator is applicable to high-speed communication.

Owner:HARBIN INST OF TECH

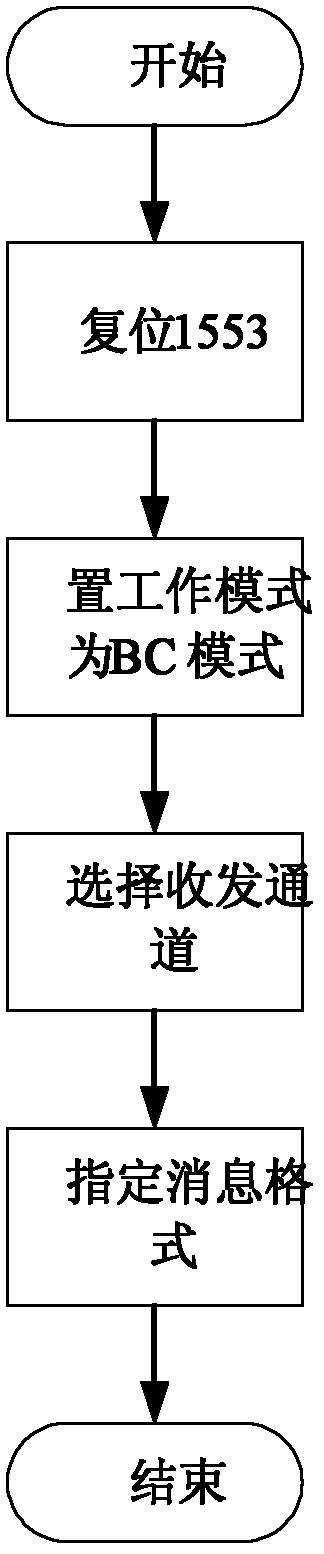

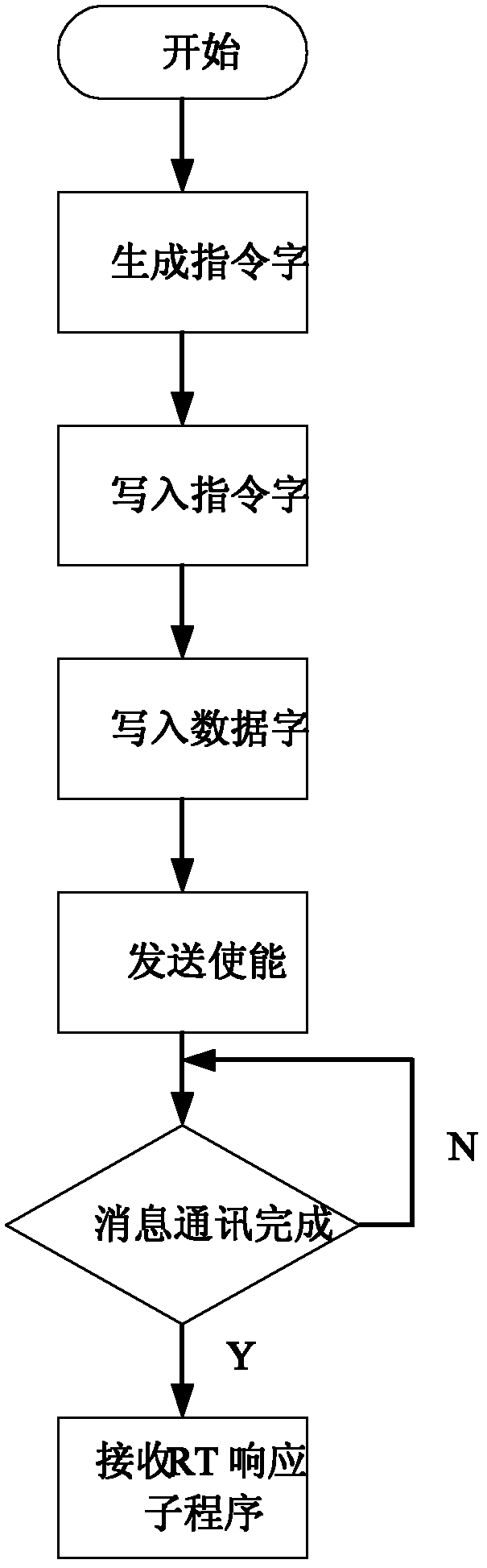

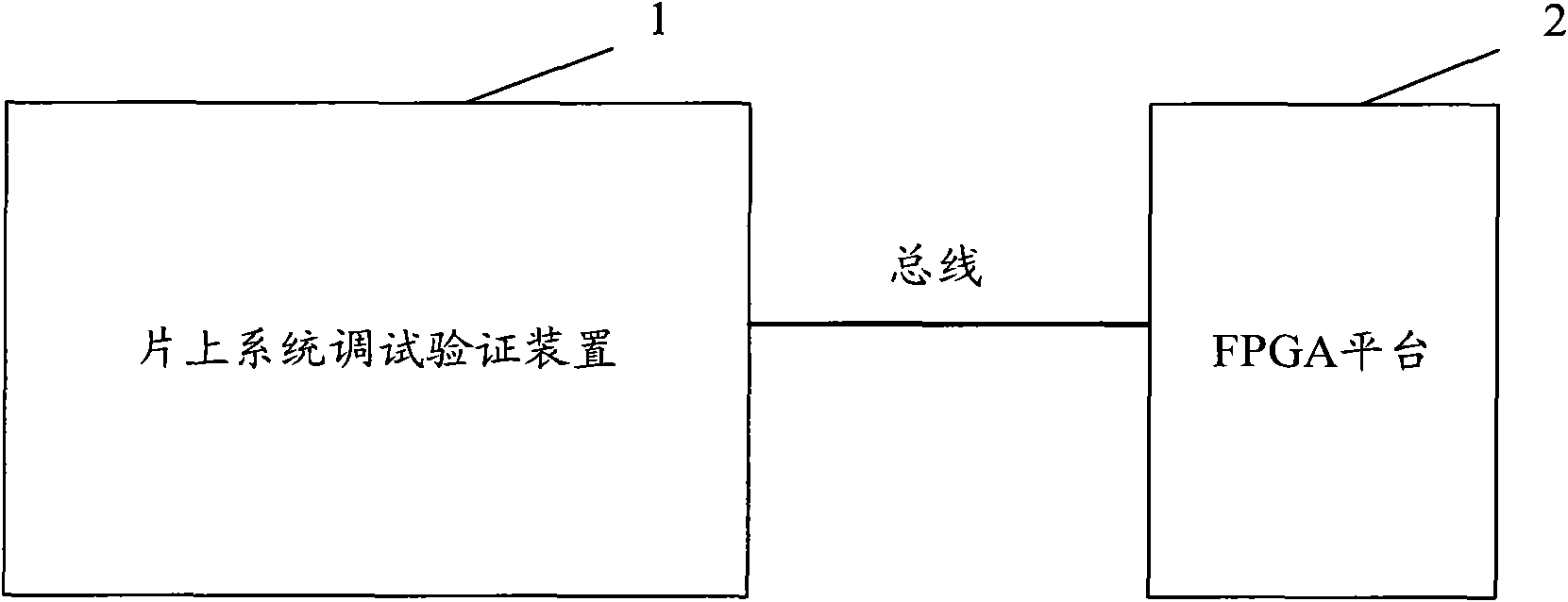

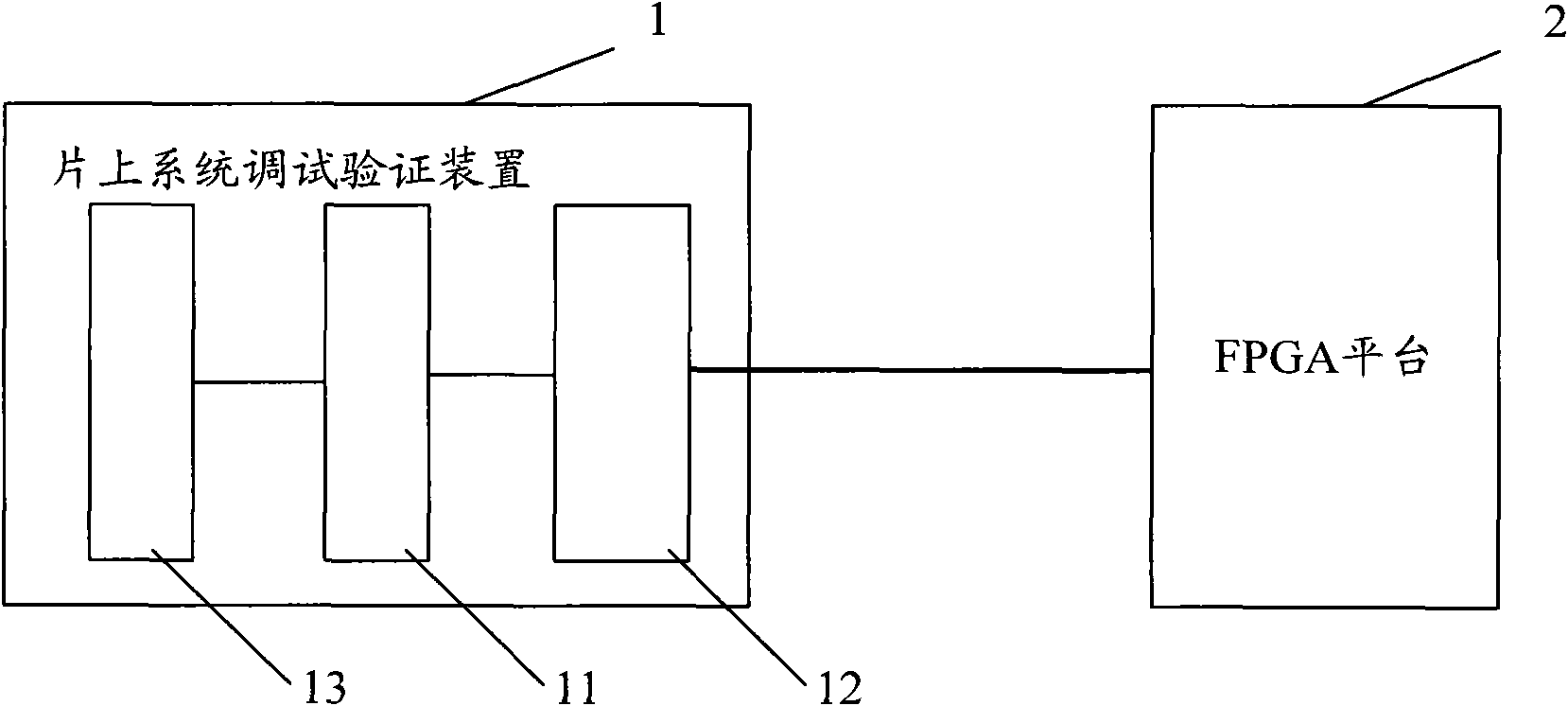

SOC (System on a Chip) debugging and verifying device and method

InactiveCN102043699AFully verifiedImprove development efficiencyFunctional testingField-programmable gate arrayComputer science

The embodiment of the invention discloses an SOC (System on a Chip) debugging and verifying device and method, relating to the field of SOCs. The SOC debugging and checking device realizes sufficient verification on an IP hardcore and an SOC, greatly increases the developing efficiency of SOC products and lowers the developing cost. The SOC debugging and verifying device is in bus connection with an FPGA (Field Programmable Gate Array) platform, and the SOC debugging and verifying are carried out through the bus connection. The SOC debugging and verifying device and method are applied to SOC verifying.

Owner:HISENSE HIVIEW TECH CO LTD

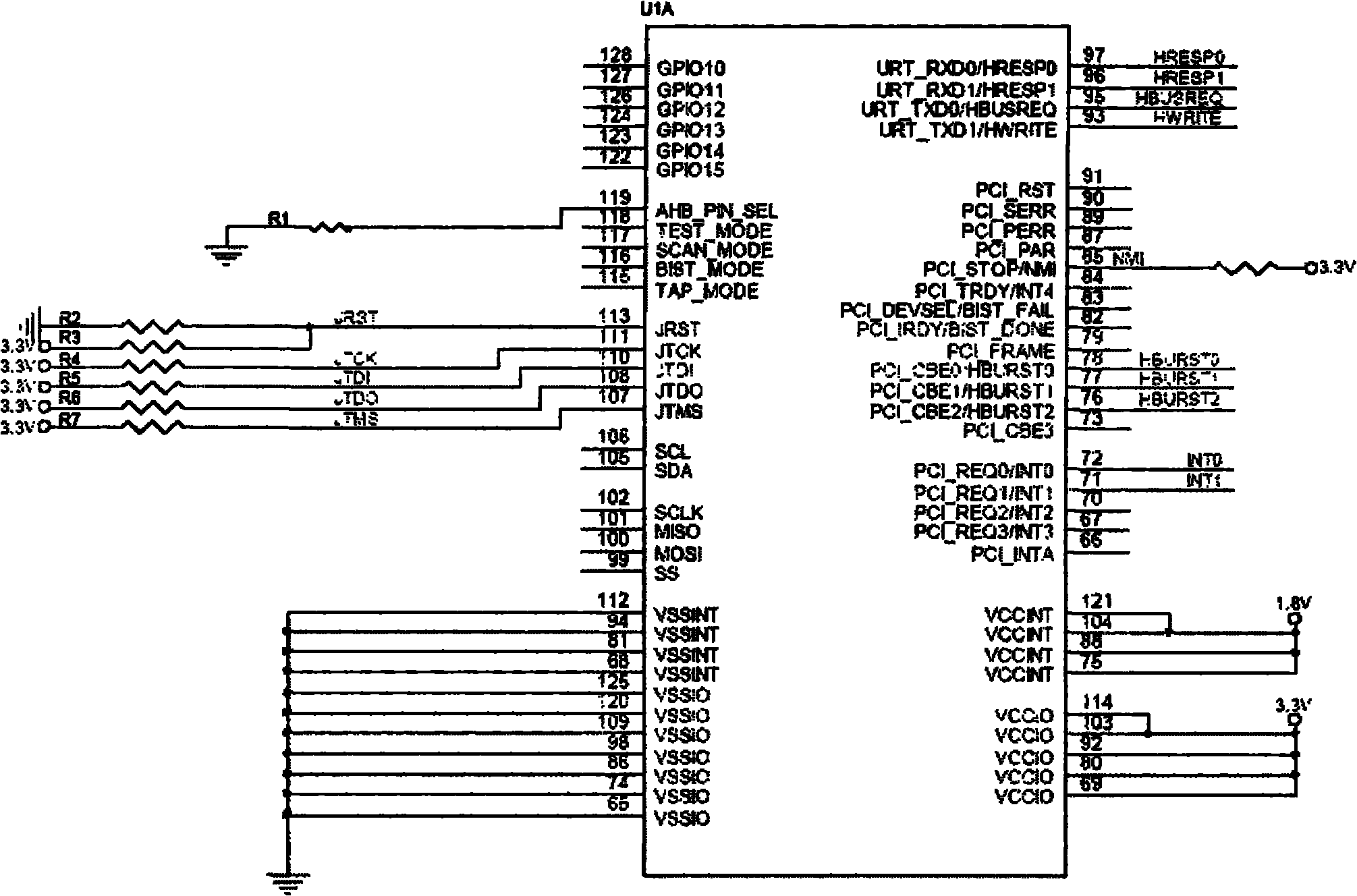

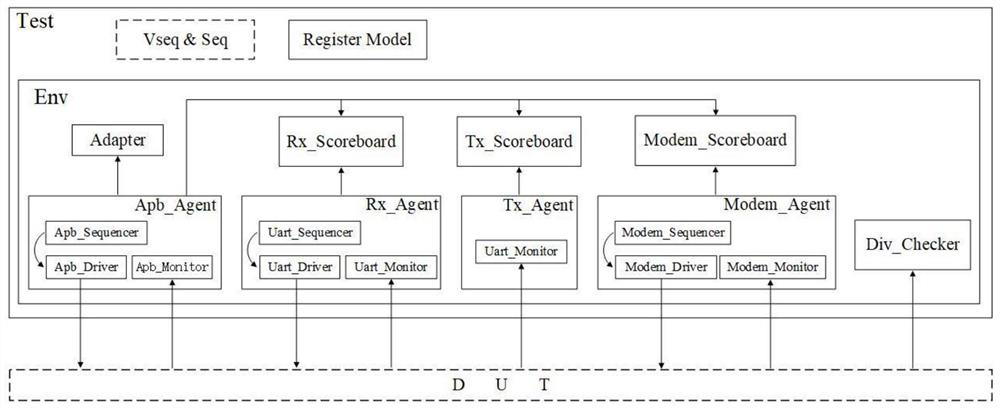

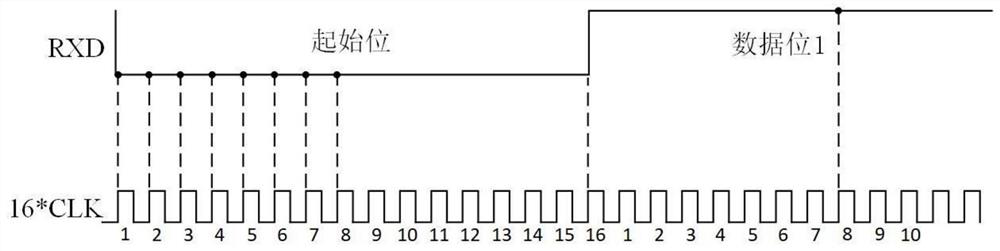

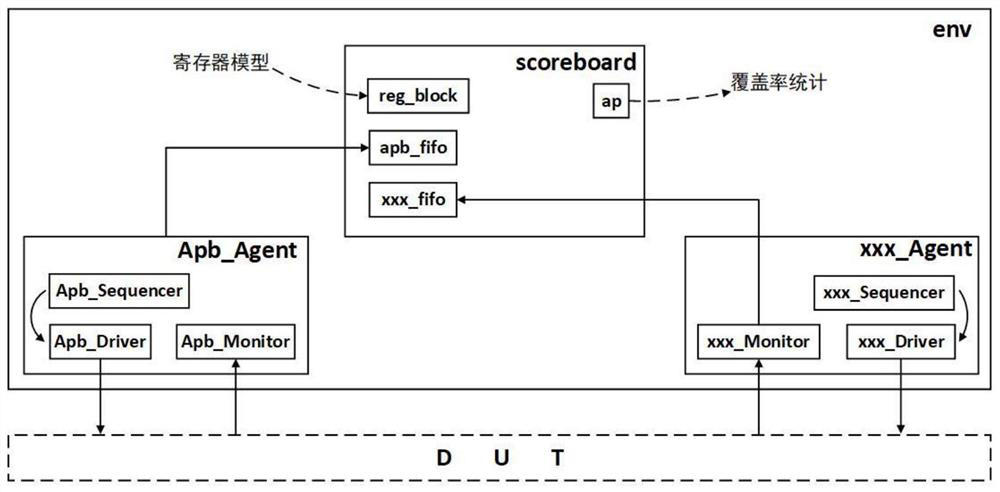

Verification method of APB-UART module based on UVM

PendingCN111913840AVersatilitySpeed up verification workFaulty hardware testing methodsEmbedded systemBaud

The invention relates to the field of chip verification, and mainly realizes a verification method of an APBUART module based on a UVM. A verification platform constructed by the verification method comprises an agent component for realizing data interaction with different protocol ports; a scoreboard assembly used for realizing data comparison; a checker assembly used for realizing baud rate detection; ,adding a register model of an early warning mechanism andverifying the environment env component; and a coverage rate collection assembly. According to the verification method, corresponding test cases and sequences are designed according to multiple functions of the APBUART module. The verification platform can realize the input of various test excitations, has the functions of automaticresult comparison and coverage rate collection, and can quickly and completely verify the APBUART module.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

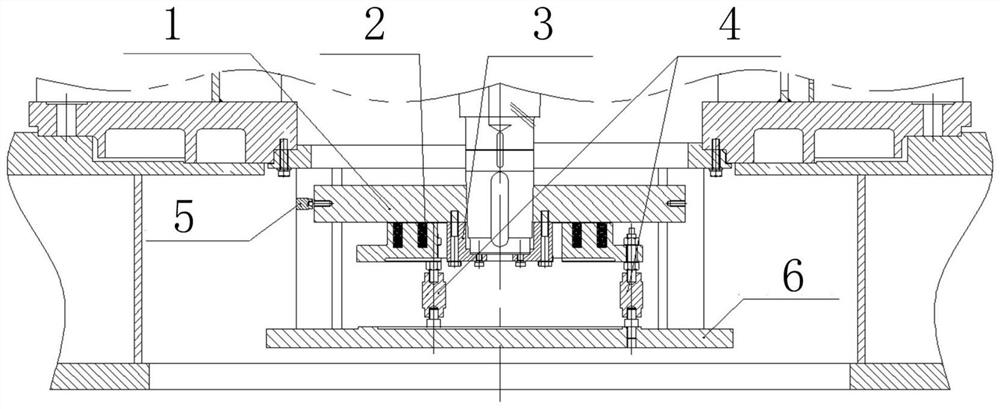

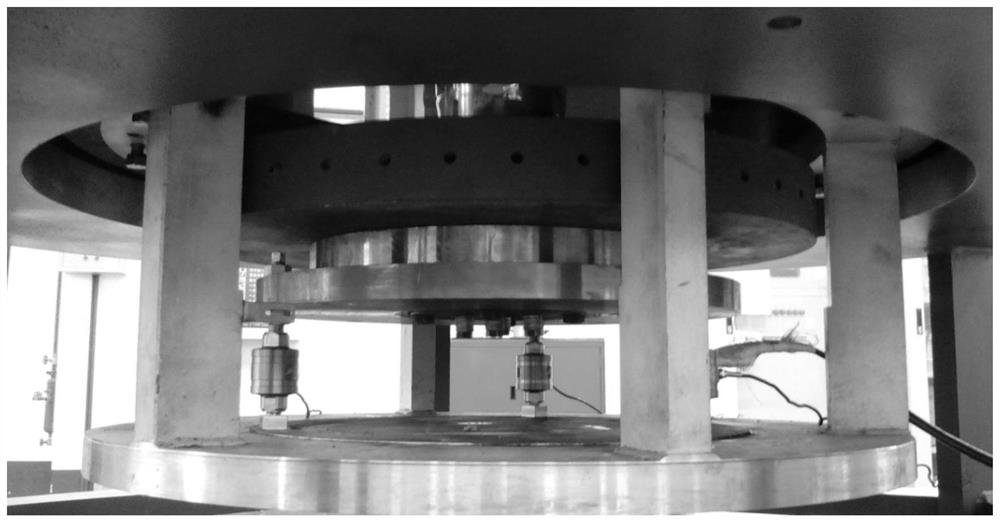

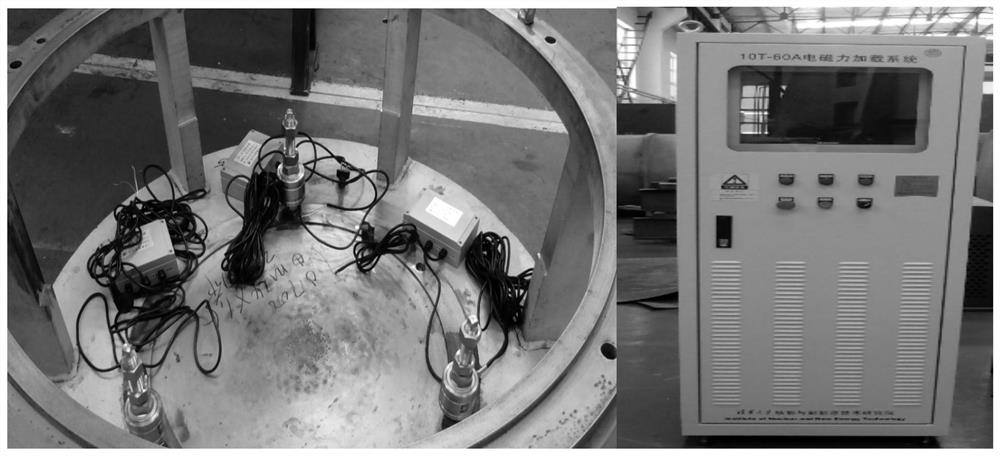

Electromagnetic bearing test device for main helium fan

PendingCN111810435AFull drop testAddressing Air Gap ChangesPump controlNon-positive displacement fluid enginesInterference fitMagnetic bearing

The invention provides an electromagnetic bearing test device for a main helium fan, and belongs to the technical field of electromagnetic bearing test devices for main helium fans. In the invention,a cantilever of a loader counterweight plate is installed at the extension end of a drive motor shaft of the main helium fan, the loader counterweight plate and the shaft adopt a cone interference fit, an electromagnetic force device is installed under the loader counterweight plate, a speed sensor is arranged on one side of the loader counterweight plate, the loader counterweight plate is matchedwith a loader bracket through the motor shaft and equipped with a counterweight plate end cover to realize axial orientation of the loader counterweight plate and the motor shaft, and the loader bracket is equipped with a force sensor. The electromagnetic bearing test device for the main helium fan solves the problem that the air gap between a loading plate and a loading part will change during the loading test, and can ensure that the main helium fan drop test is fully verified.

Owner:JIAMUSI ELECTRIC MACHINE

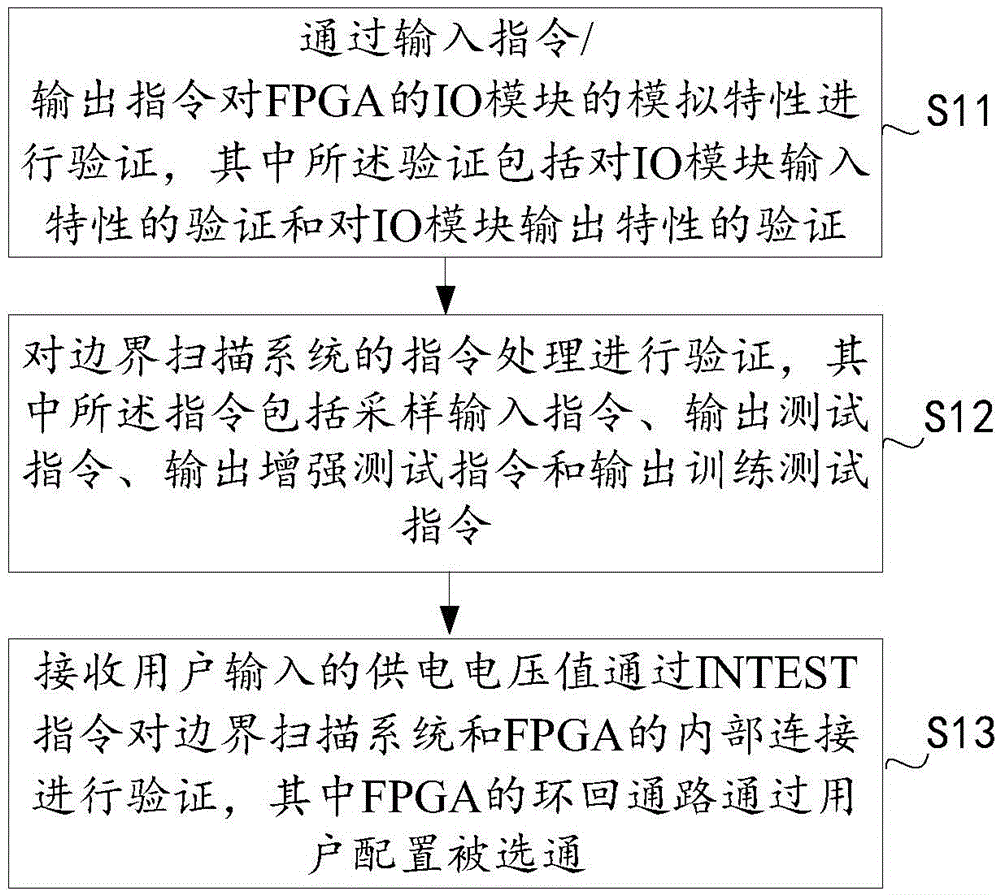

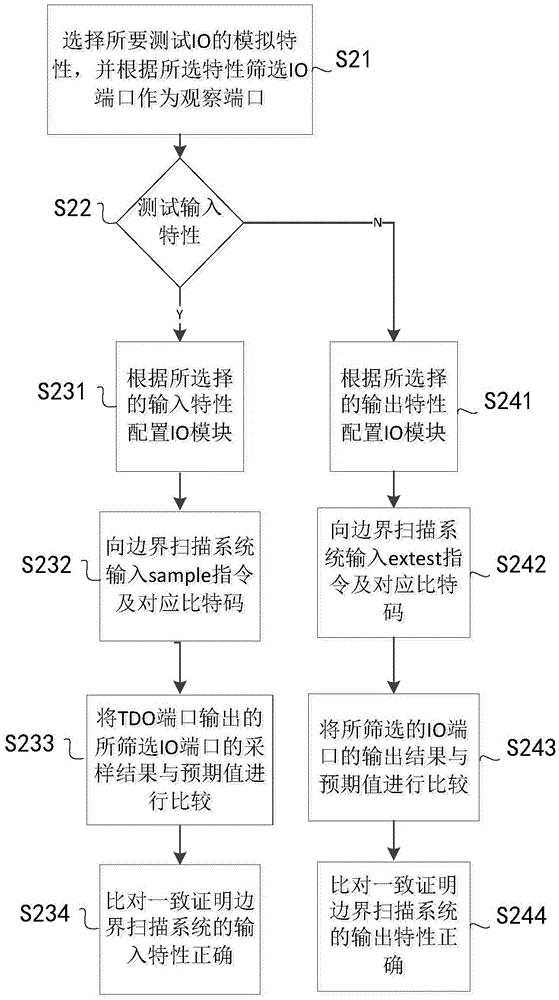

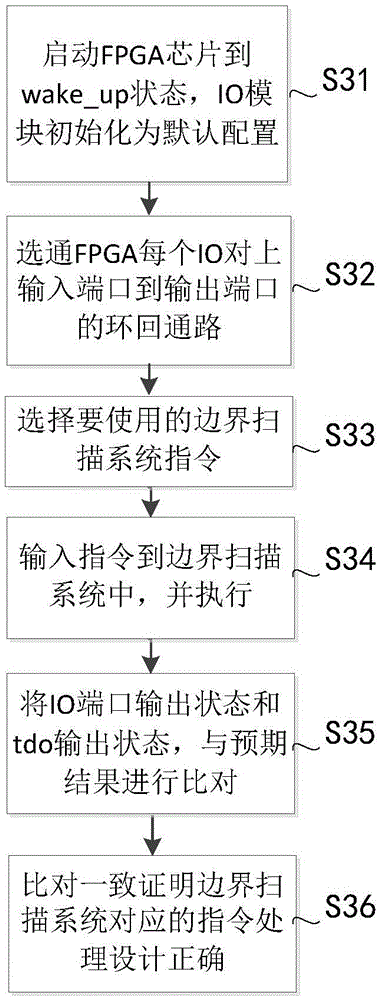

Verifying method and apparatus for FPGA boundary scan system

ActiveCN105487035AFully verifiedGuaranteed correctnessElectrical testingValidation methodsField-programmable gate array

The invention provides a verifying method and apparatus for an FPGA (Field-Programmable Gate Array) boundary scan system, which are used for debugging the FPGA boundary scan system on a simulation platform. The method includes the following steps: verifying the simulation characteristics of an IO module of an FPGA through an input instruction / output instruction, wherein the verifying step includes verifying the input characteristics of the IO module and verifying the output characteristics of the IO module; verifying instruction processing of the boundary scan system, wherein instructions include a sampling input instruction, an output test instruction, an output enhancement test instruction and an output training test instruction; and verifying internal connection of the boundary scan system and the FPGA through an internal test instruction, wherein a round trip pathway of the FPGA is gated through user configuration. The verifying method and apparatus can comprehensively and thoroughly verify the FPGA boundary scan system and ensure correctness of functions of the FPGA boundary scan system.

Owner:SHENZHEN PANGO MICROSYST CO LTD

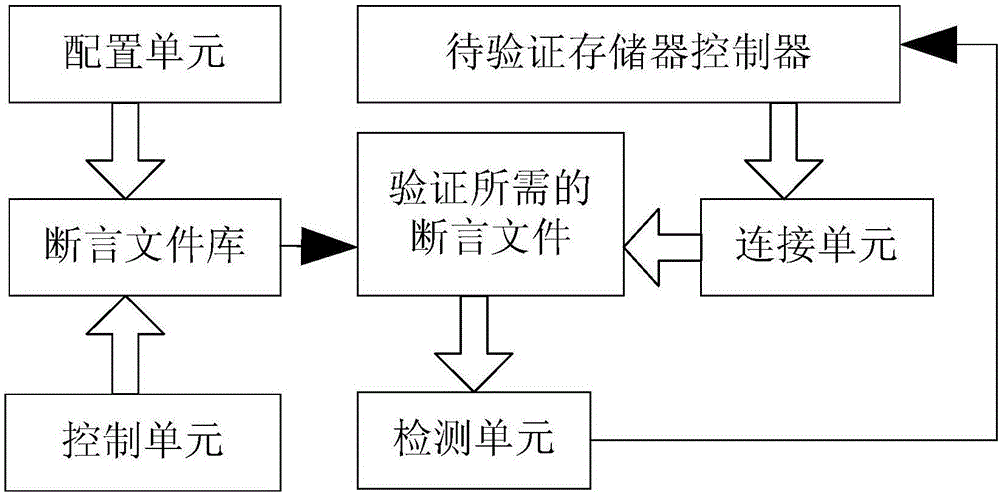

Assertion-based parameterization verification system of interface time sequence of storage controller

The invention provides an assertion-based parameterization verification system of an interface time sequence of a storage controller and relates to the technical field of verification of integrated circuits. The system comprises a configuration unit, a control unit, an assertion document library, a storage controller to be verified and a detection unit, wherein the configuration unit is used for transmitting configuration parameters to the assertion document library; the control unit is used for transmitting control parameters to the assertion document library; the assertion document library is used for selecting assertion documents needed by verification according to values of the configuration parameters and the control parameters, verifying the needed assertion document, matching an interface signal time sequence with an interface signal time sequence requirement, generating matching information and transmitting the matching information to the detection unit; the storage controller to be verified is used for transmitting the interface signal time sequence to the assertion documents needed by verification and modifying the interface signal time sequence according to failure matching information; the detection unit is used for transmitting the failure matching information to the storage controller to be verified when detecting a matching failure signal. Through the assertion-based parameterization verification system of the interface time sequence of the storage controller, plenty of verification time can be reduced; the working difficulty is reduced; and the accuracy of the verification is improved.

Owner:BEIJING MXTRONICS CORP +1

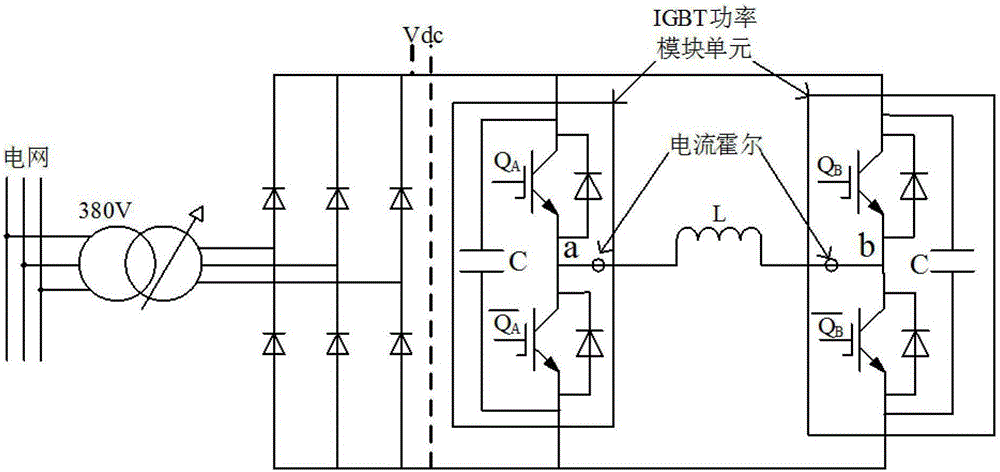

IGBT power module unit load testing method

The invention discloses an IGBT power module unit load testing method. The method comprises the following steps that: (A) testing indexes of power module units are set to be identical with those of a current transformer whole machine; (B) a control system adopts a current Hall detection power module to detect the currents of the power module units; and (C) the current different between the two power module units is calculated, and when the current difference is larger than a set threshold, the power-off open circuit is used to trigger the protection over the IGBT power module units. The method has the advantages that: (1) the method is applicable to load aging tests of IGBT power modules of a wind power current transformer and a photovoltaic inverter; (2) the control mode is easy to realize, and the implementation cost is low; (3) current Hall verification is included, and the verification of the whole IGBT power module unit is more sufficient; and (4) the testing indexes of the IGBT power module units are identical with those of the current transformer whole machine, and the simulation of the real onsite condition of the IGBT is facilitated.

Owner:GUANGDONG MINGYANG LONGYUAN POWER ELECTRONICS

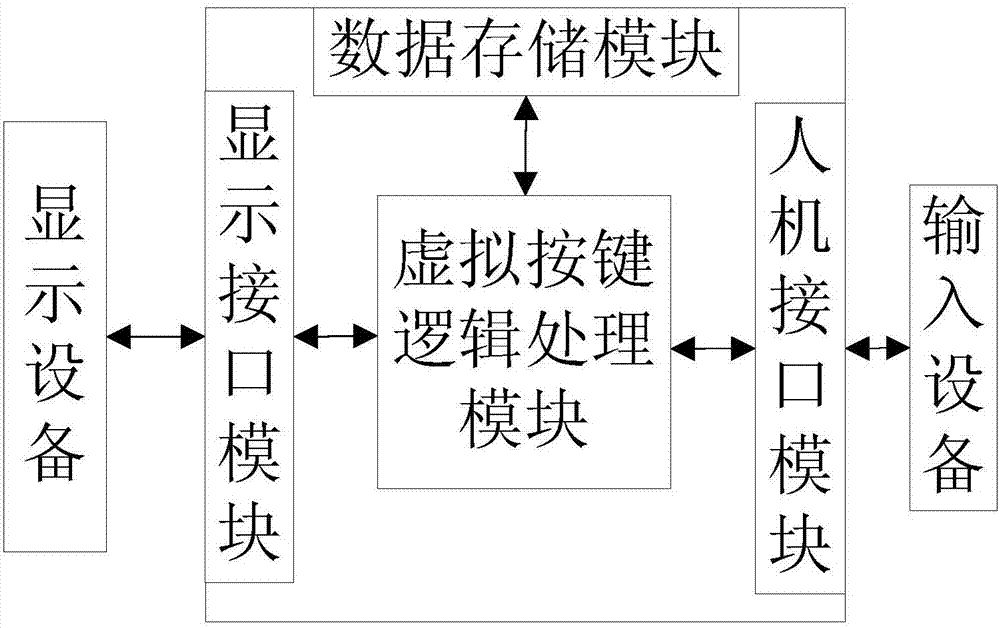

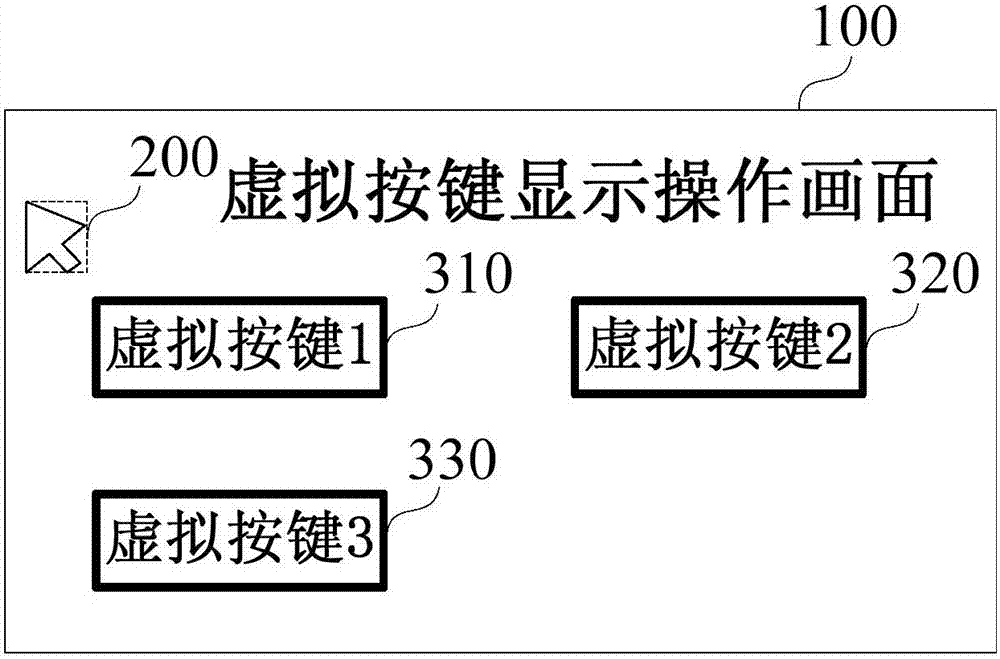

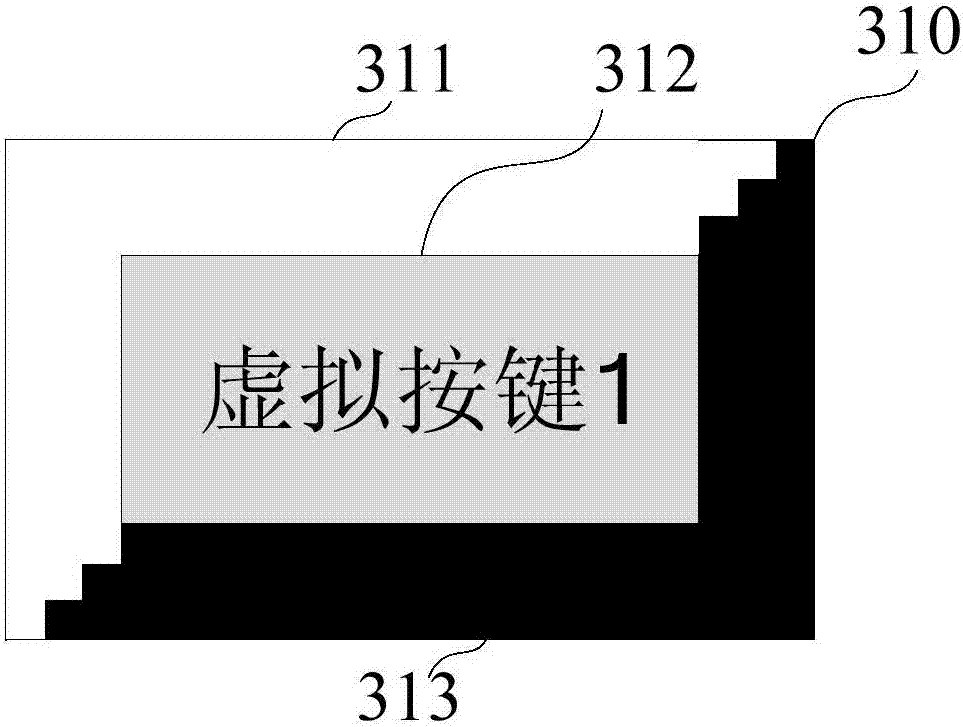

Virtual key display operation device and method

InactiveCN107305465AImprove information securityFully testedInput/output processes for data processingKey pressingOperational system

The invention discloses a virtual button display operation method and device, comprising an input device, a virtual button logic processing module, a display interface module, a man-machine interface module, and a display device. The virtual button logic processing module is used to process the input signal sent by the man-machine interface module, generate different image signals corresponding to the pressed or released states of the virtual button, and send the generated image signal to Display the interface module, and then send it to the display device, so that the display device displays the screen corresponding to the virtual key; when the virtual key is in the selected and unselected states, two different screens are displayed, so that the user can clearly determine the virtual key state and generate corresponding control signals. The disclosed virtual button display operation method and device do not include complex software and hardware such as CPU and operating system during operation, and have the advantages of simple system, easy to be fully tested and verified, and resistant to threats brought by viruses and Trojan horses.

Owner:SHANGHAI LINGXIAN ELECTRONICS SCI & TECH LTD

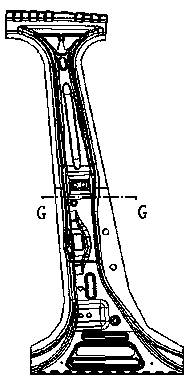

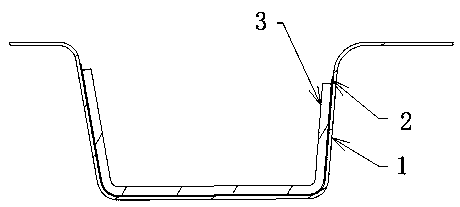

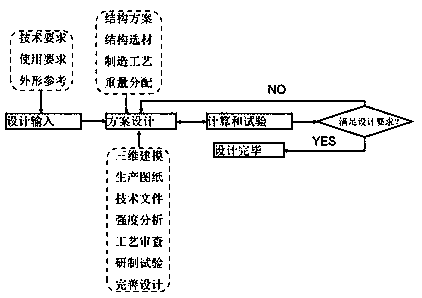

Design method of composite material automobile B column

PendingCN111143946ARapid one-piece moldingFully formedGeometric CADDesign optimisation/simulationFiberCarbon fibers

The invention discloses a design method of a composite material automobile B column. A CFRP / high-strength steel composite structure is adopted, CFRP layering design, CFRP-high-strength steel connection design, CAE modeling and simulation analysis, performance verification and the like are conducted, and the common technical problems of structural design optimization, performance evaluation, connection evaluation and the like of the carbon fiber-thermal forming steel part can be solved. According to the design method of the composite material automobile B column, the strength and rigidity of the designed automobile B column of the high-strength steel and CFRP composite structure are improved by about 10% compared with those of an automobile B column of an original structure, rapid mold pressing integrated forming of carbon fibers and metal is achieved, and sufficient verification is provided for mass production of products.

Owner:JIANGSU HENGRUI CARBON FIBER TECH CO LTD

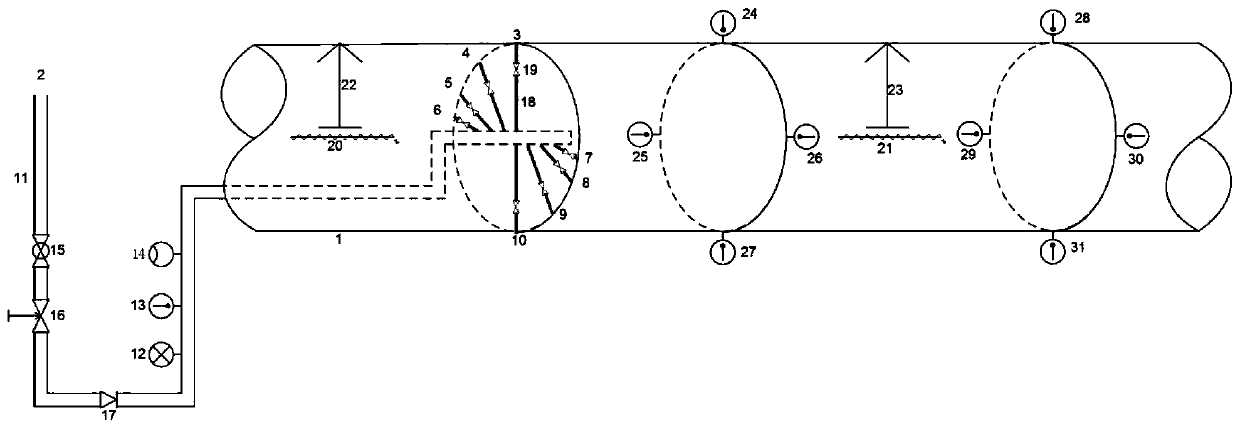

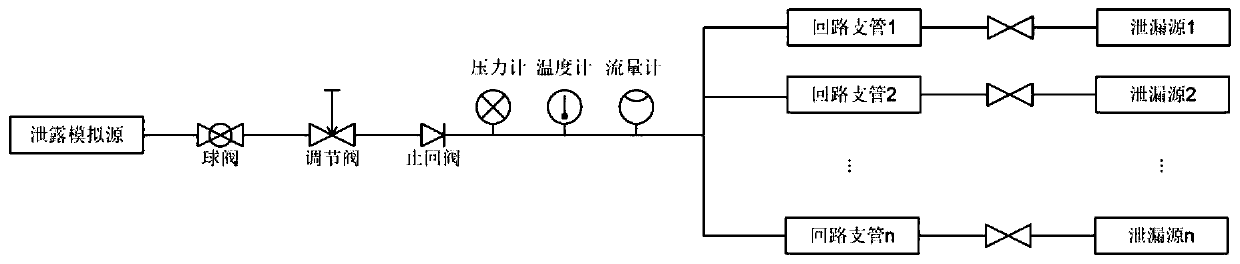

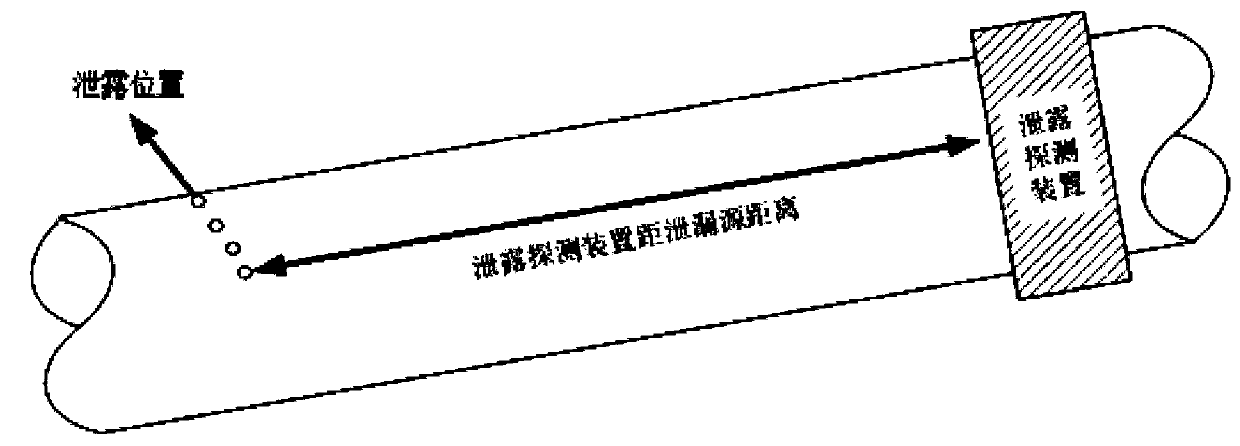

Nuclear process pipeline leakage rate detection device function verification test loop system

ActiveCN110911021AEasy to switchReflect flow statusNuclear energy generationNuclear monitoringNuclear plantProcess engineering

The invention aims to disclose a nuclear process pipeline leakage rate detection device function verification test loop system, which comprises a loop unit for providing a fluid medium in a high-energy pipe and a simulation pipeline unit for simulating the state of a leakage pipeline. Compared with the prior art, pipeline leakage positions in different directions can be easily and freely switched,so that the effective detection capability of the detection device relative to different positions of pipeline leakage defects can be verified; the real pipeline size, material and pipe wall temperature of the leakage pipeline can also be simulated, particularly, a loop device for simulating the size, material and the like of a nuclear power plant main steam pipe does not have public informationyet, thus better reflecting the flowing condition of the leakage fluid relative to the pipeline, the adsorption effect of the pipe surface on the leakage fluid and heat exchange, realizing comprehensive and sufficient verification of the leakage detection device outside a pipeline pressure boundary, guaranteeing the reliability and effectiveness, and achieving the purpose of the invention.

Owner:SHANGHAI NUCLEAR ENG RES & DESIGN INST CO LTD

Industrial personal computer with multi-image shared memory

InactiveCN106919352AImprove information securityFully testedDigital output to display deviceMulti-imageComputer module

The invention discloses an industrial personal computer with a multi-image shared memory. The industrial personal computer mainly comprises a display apparatus, a display and control processing module, a display interface module, an input interface module, and a data storage module, wherein the display and control processing module comprises at least two function sub-modules and processes an input signal sent by the input interface module. Each function sub-module generates a corresponding display operation image and the corresponding display operation image is displayed on the display apparatus; and image data of display regions such as background image display regions and the like of different display operation images is stored by adopting the shared memory, so that the storage space for displaying the image data required by the images is greatly saved; the industrial personal computer disclosed by the invention does not contain complex hardware such as a CPU, a display card and the like, and complex software such as an operation system, display operation image software and the like in a running process; a system is simple, low in cost and easy to fully test and verify; and the industrial personal computer has the characteristics of very high function security and information security.

Owner:SHANGHAI LINGXIAN ELECTRONICS SCI & TECH LTD

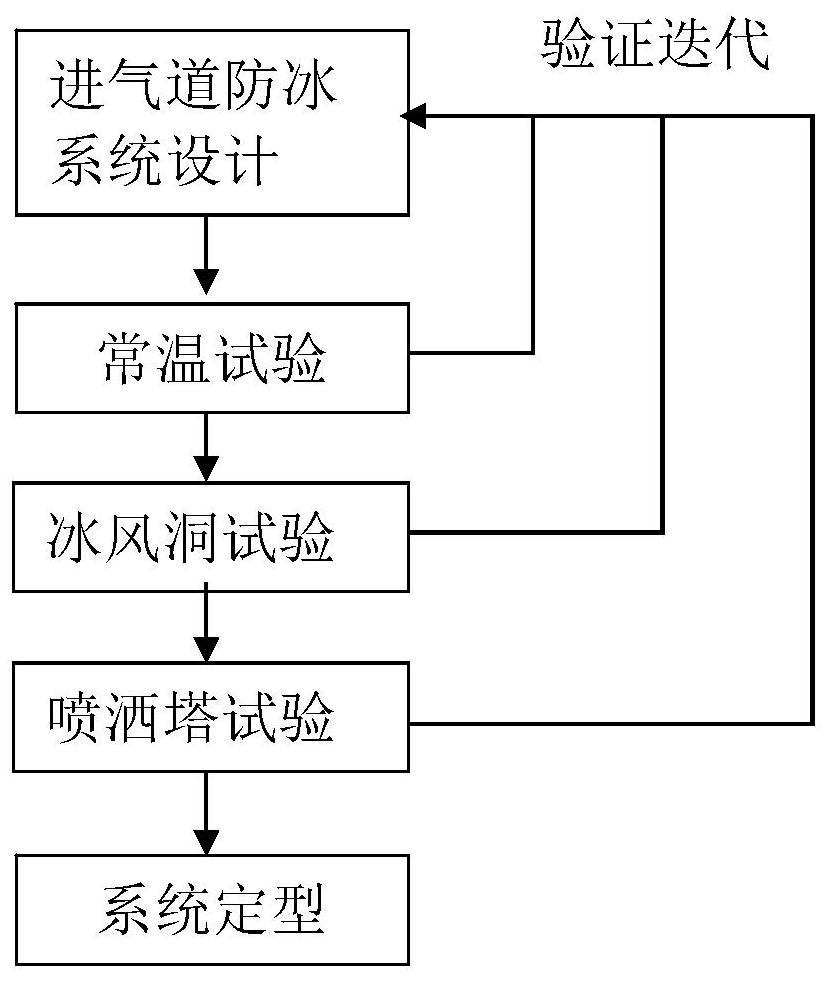

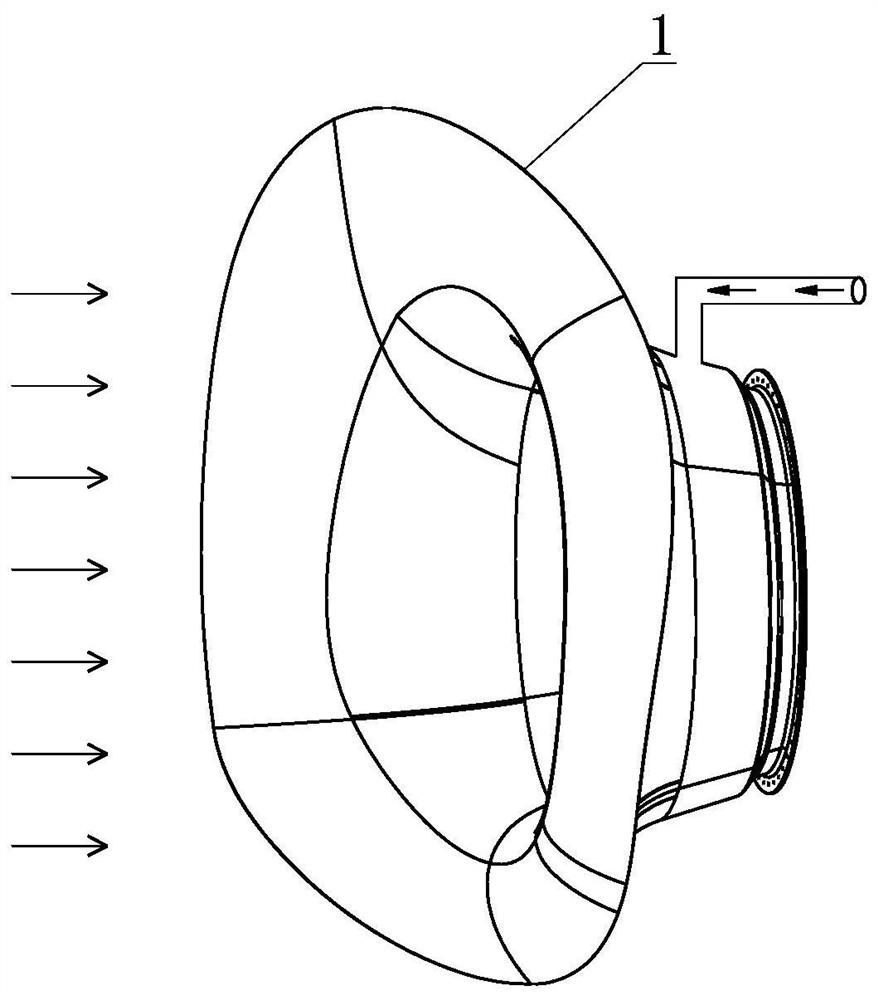

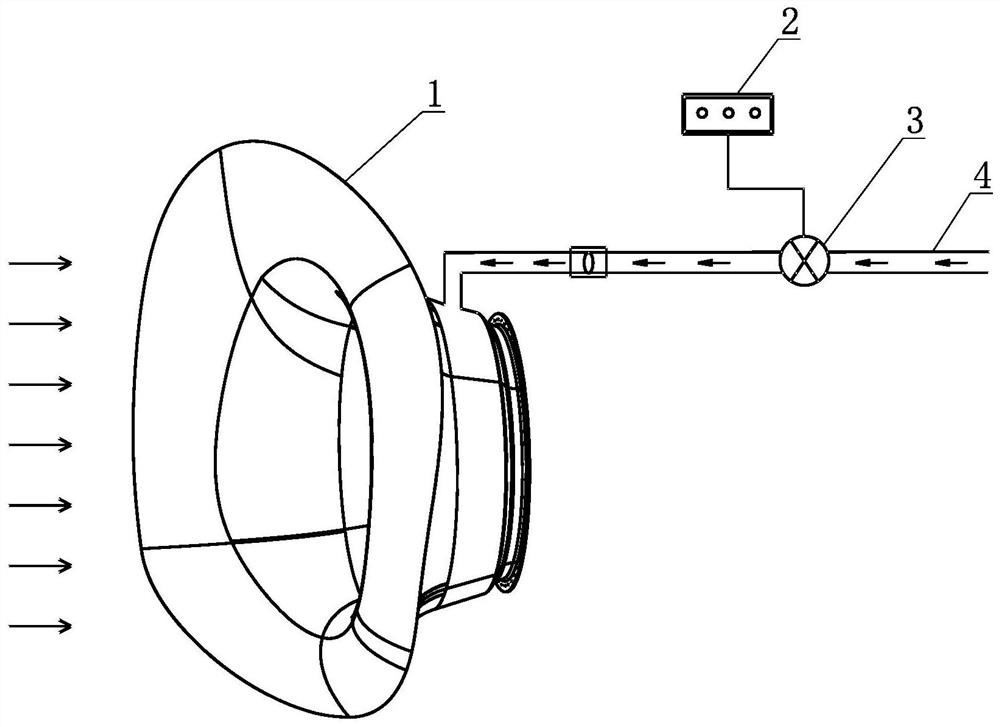

Test method of helicopter air inlet channel anti-icing system

PendingCN114112354AReduce Design IterationsFully testedMachine part testingAerodynamic testingInlet channelMarine engineering

The invention provides a test method of a helicopter air inlet channel anti-icing system. The helicopter air inlet channel anti-icing system comprises an air inlet channel and a heating assembly. The method comprises the steps that a normal temperature test is conducted on the helicopter air inlet channel anti-icing system, and when the temperature characteristic of an air inlet channel does not meet the anti-icing design requirement, iterative correction is conducted on the air inlet channel till the air inlet channel meets the anti-icing design requirement; an icing wind tunnel test is carried out on the helicopter air inlet channel anti-icing system, and when the heating performance of the heating assembly does not meet the design requirement, iterative correction is carried out on the heating assembly till the design requirement is met; and carrying out a spraying tower test on the helicopter air inlet channel anti-icing system, and verifying the anti-icing performance of the helicopter air inlet channel anti-icing system. Test items of different development stages are reasonably planned, the system performance can be fully verified, the repair workload after installation is reduced, and the development time and the test cost can be saved.

Owner:CHINA HELICOPTER RES & DEV INST

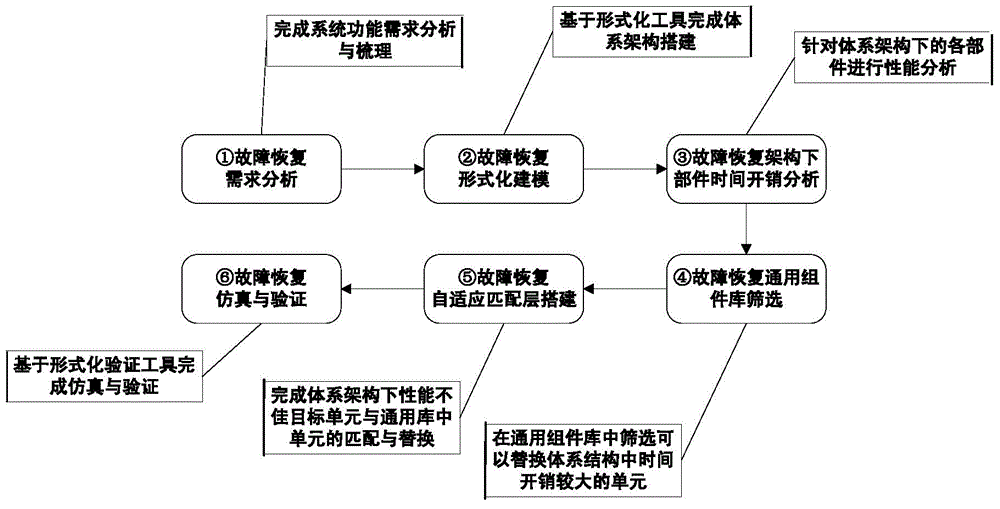

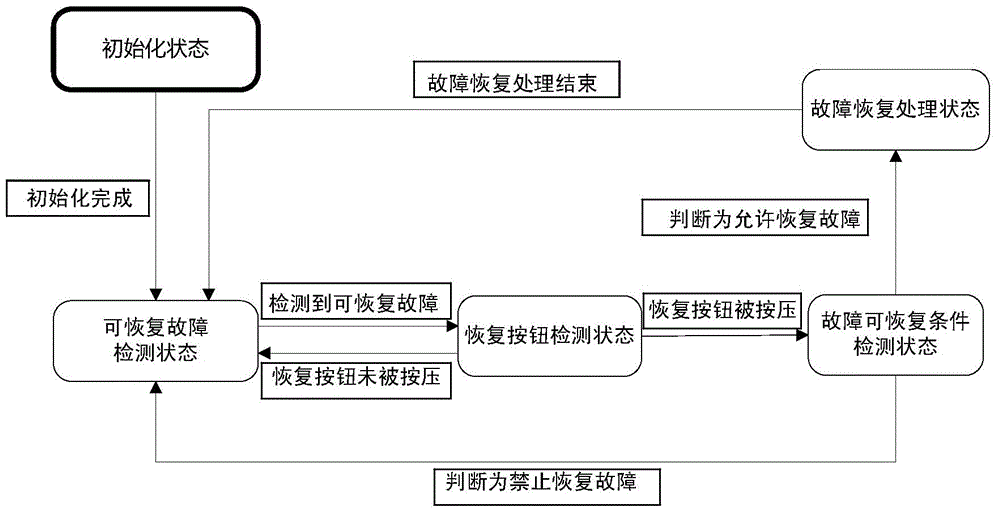

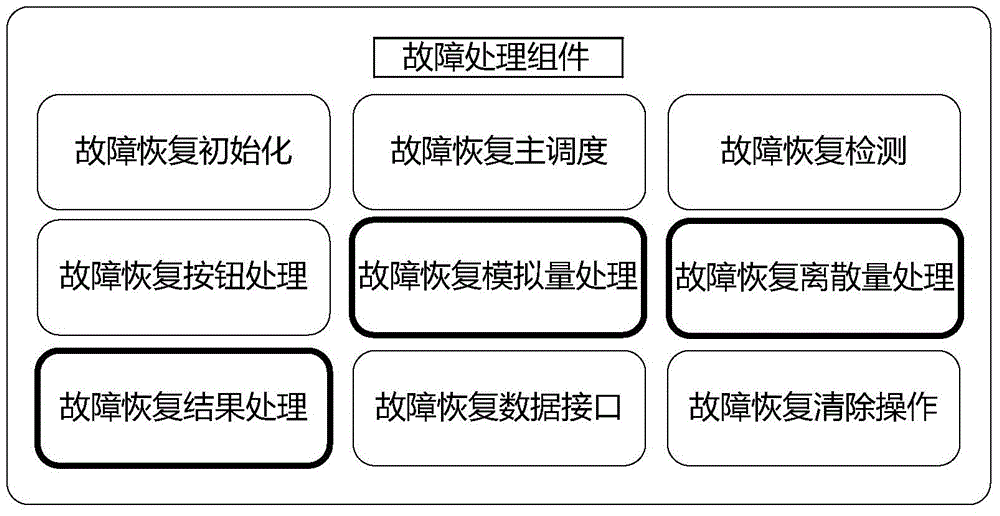

Optimization method for formalized modeling

InactiveCN105095065AImprove performanceAutomatic fastSoftware testing/debuggingRedundant codeControl system

The present invention relates to an optimization method for formalized modeling. In a critical and real-time flight control system that has strict requirements on time, single use of a formalized modeling design method causes time cost brought by partial intermediate redundant codes generated in a modeling process and requirements of a hard real-time task system cannot be met. According to the scheme adopted by the present invention, by introducing a formalized modeling tool and a bridging technological method of a general library, an architecture design of a system is completed by means of a formalized modeling method at an early period and calculation analysis is performed on performances, such as time cost, of each module in the system; and for the module that has relatively large time cost or not good performance, an existing general library is bridged by using a self-adaptive adaptation layer, so that cooperative work of the formalized modeling method and the general library is implemented, and performance optimization is performed on formalized modeling.

Owner:FLIGHT AUTOMATIC CONTROL RES INST

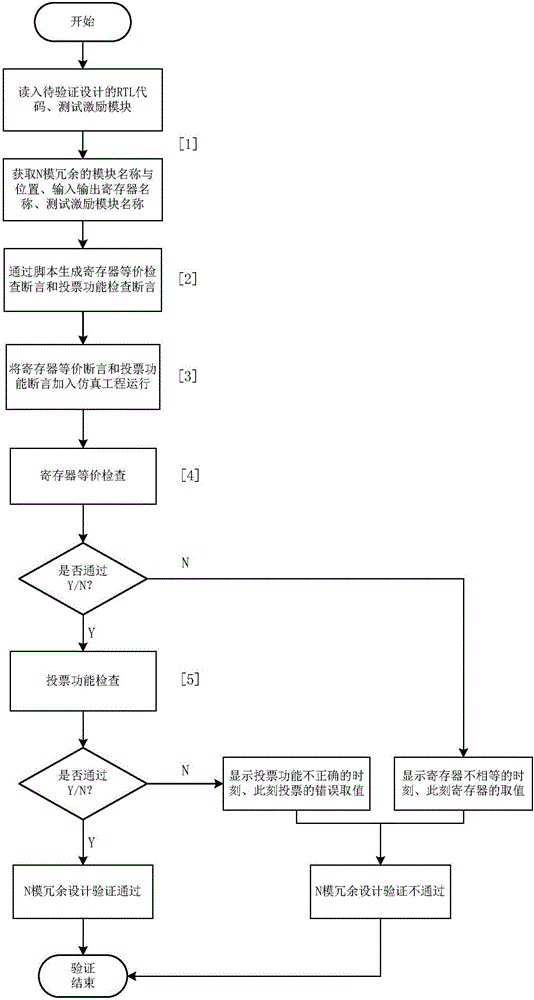

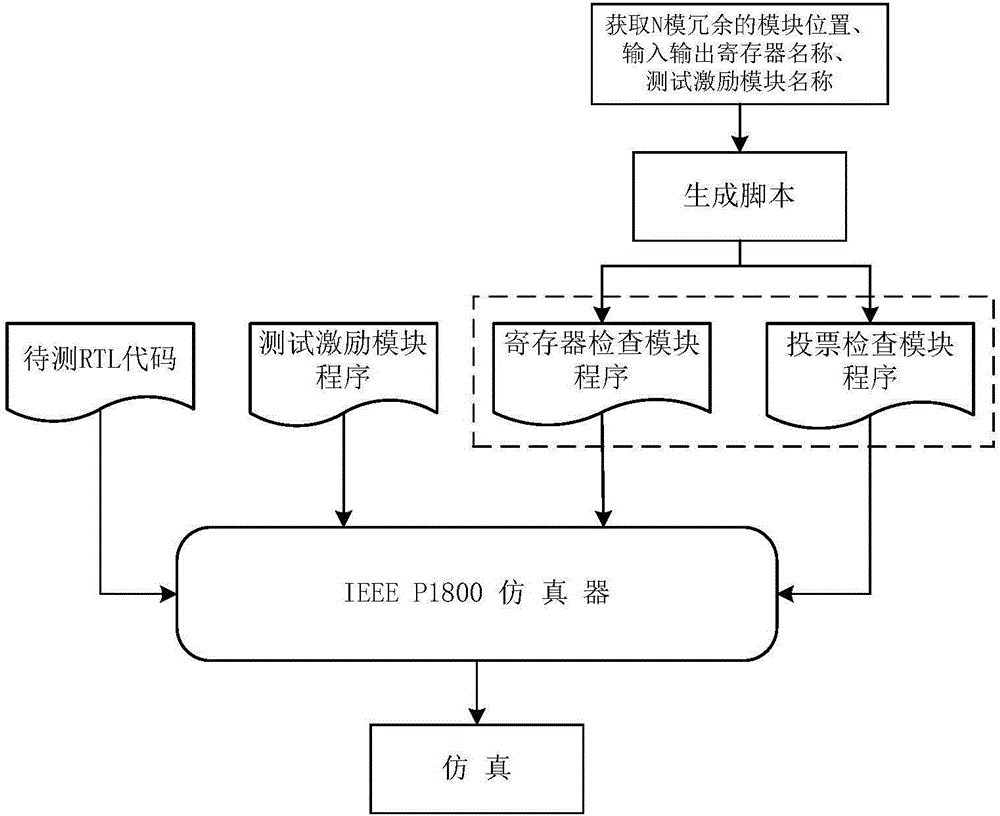

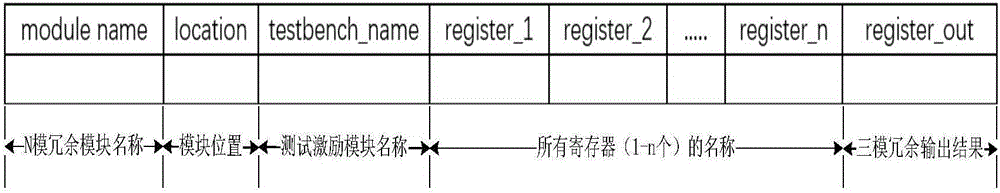

Register transport level N-modular redundancy verifying method

ActiveCN106802848AValidation does not affectFully verifiedFunctional testingComputer architectureProcessor register

The invention discloses a register transport level N-modular redundancy semi-automatization verifying method. The method comprises the steps of checking output of registers of a platform to be verified of n-modular redundancy; receiving output values of the registers 1-n of the platform to be verified, judging whether the output values of the registers 1-n are equal or not, and if the output values of the registers 1-n are equal, passing the verifying step; defining binary system value data; adding 1 to the lowest order of data by each system clock, giving each order of n orders of the data to the registers 1-n respectively, outputting a vote output result on a falling edge of each system clock by the platform to be verified according to values of the registers 1-n of a rising edge of each system clock; calculating the number of all the registers of which a register value is 1 and 0 in each system clock, if the number of the registers of which the register value is 1 is more, making a is equal to1, and if the number of the registers of which the register value is 0 is more, making a is equal to 0; detecting whether the vote output result of the platform to be verified is equal to a or not, and if the vote output result of the platform to be verified is equal to a namely the value of the most quantity, passing the verifying step.

Owner:BEIJING INST OF COMP TECH & APPL

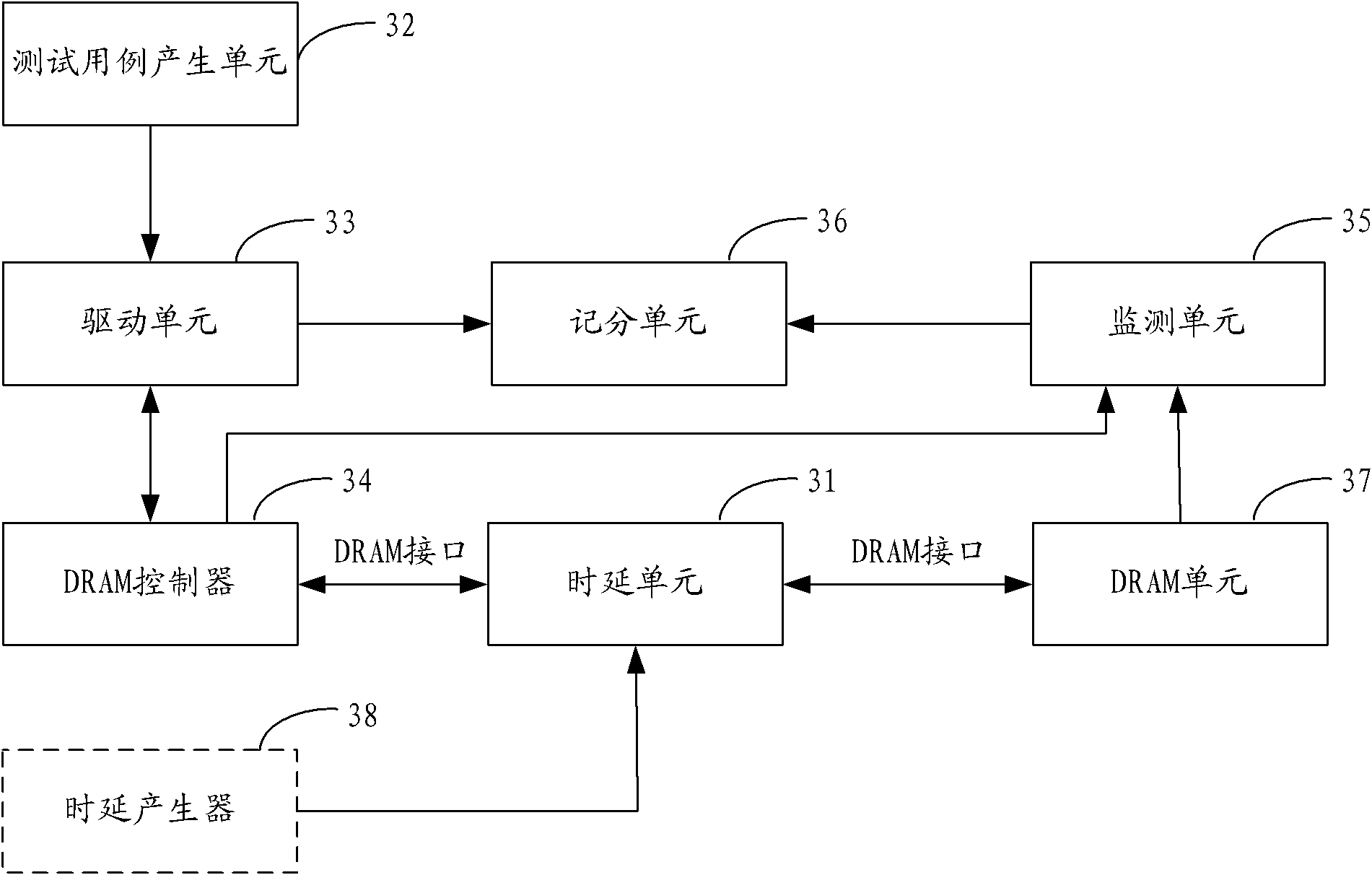

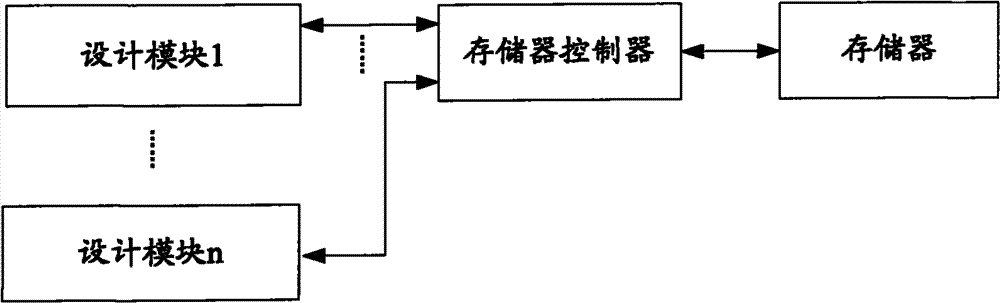

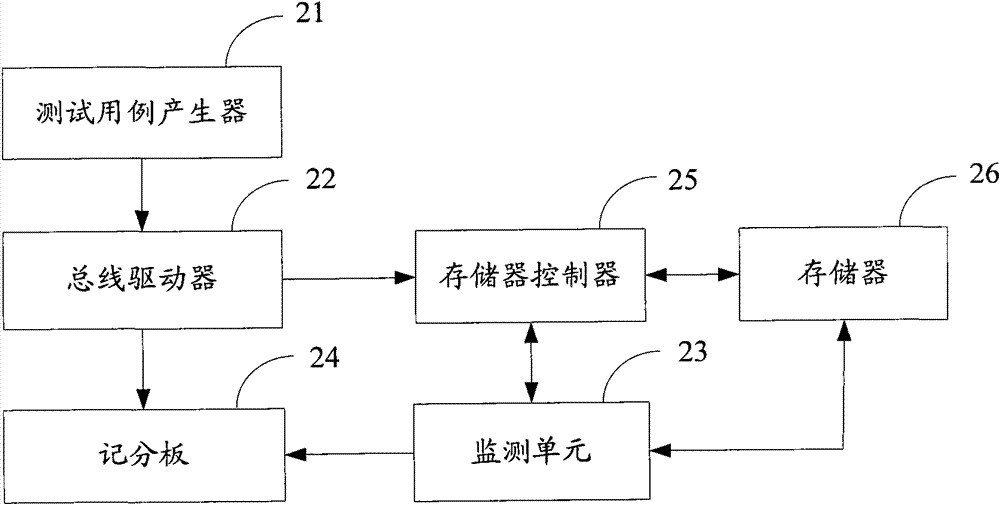

Verification system and method for memory controller

ActiveCN101996265BImplement Parallel VerificationFully verifiedSpecial data processing applicationsComputer hardwareReusability

The invention is suitable for the field of verification, and provides a verification system and a verification method for a memory controller. The system comprises a test case generator, a bus driver, a monitoring unit and a scoreboard, wherein the test case generator is used for generating at least one test case; the bus driver is used for generating a control event according to the test case generated by the test case generator, converting the test case into the interface bus timing of the memory controller and sending the interface bus timing to the memory controller simultaneously; the monitoring unit is used for monitoring a monitoring event which is generated by the memory controller according to the received interface bus timing; and the scoreboard is used for judging whether the memory controller works normally or not according to the control event generated by the bus driver and the monitoring unit monitored by the monitoring unit. By establishing a module level-based verification system for the memory controller, a plurality of channels of the memory controller are parallelly and fully verified, so the system has high reusability and efficiency.

Owner:ANYKA (GUANGZHOU) MICROELECTRONICS TECH CO LTD

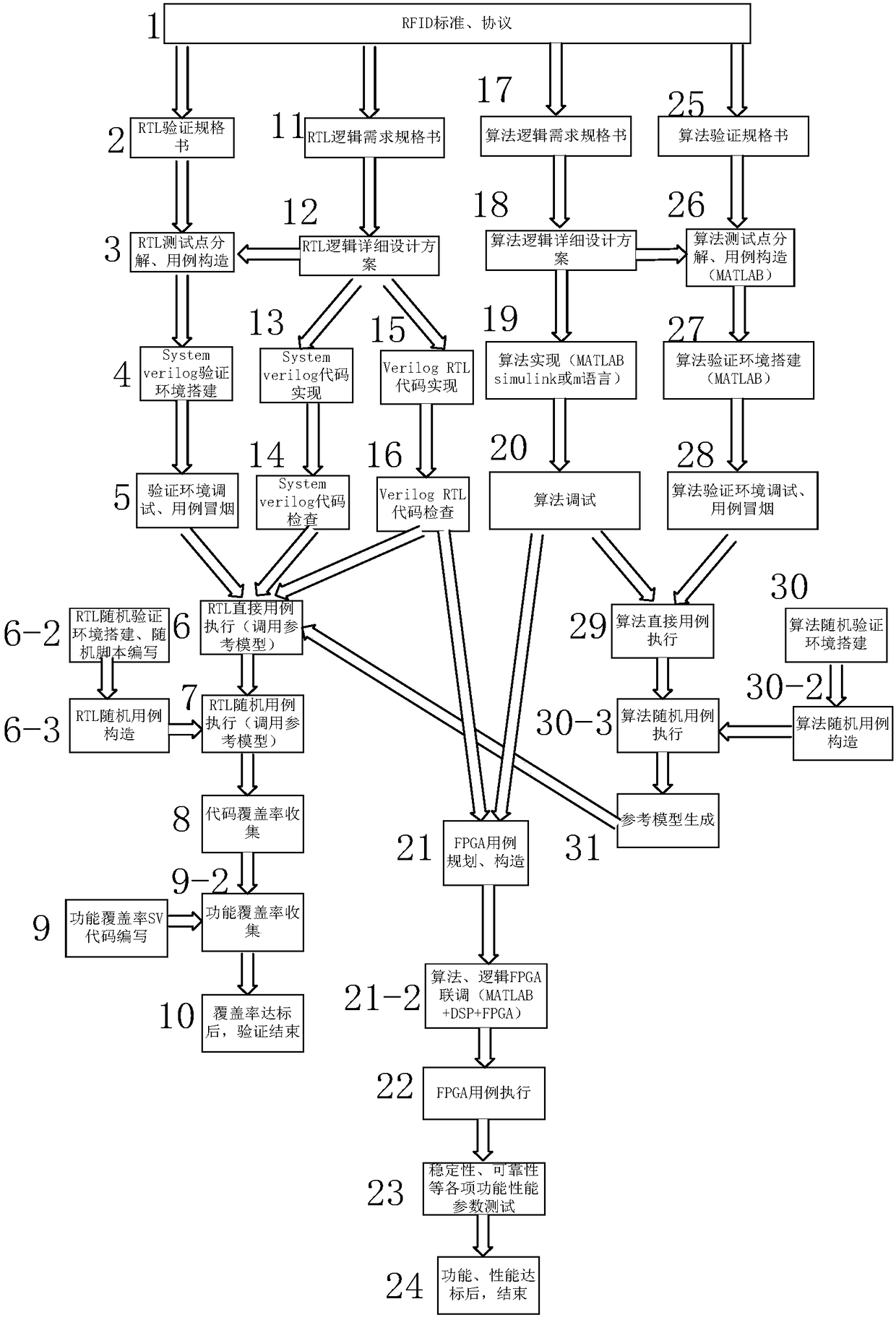

A Design Verification Method for Passive Tag Chip

ActiveCN105844066BAchieve fullyFully verifiedSpecial data processing applicationsComputer architectureDesign methods

The invention discloses a design verification method for a passive tag chip. The method comprises the design verification steps of designing an algorithm, verifying the algorithm, designing an RTL (Register Transfer Level) and verifying the RTL. According to the design verification method, a cross-implementation and cross-verification design method is adopted, and thorough implementation and thorough complete verification of an RFID (Radio Frequency Identification) standard protocol can be achieved, so that the success rate of one-time chip delivery is greatly increased.

Owner:WUXI KEYBRIDGE ELECTRONICS TECH CO LTD