A Design Verification Method for Passive Tag Chip

A design verification and passive tag technology, which is applied in the field of passive tag chip design verification, can solve problems such as imperfection, code coverage and function coverage that are difficult to meet the requirements of filming, difficult positioning, etc., and achieve an improved success rate Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

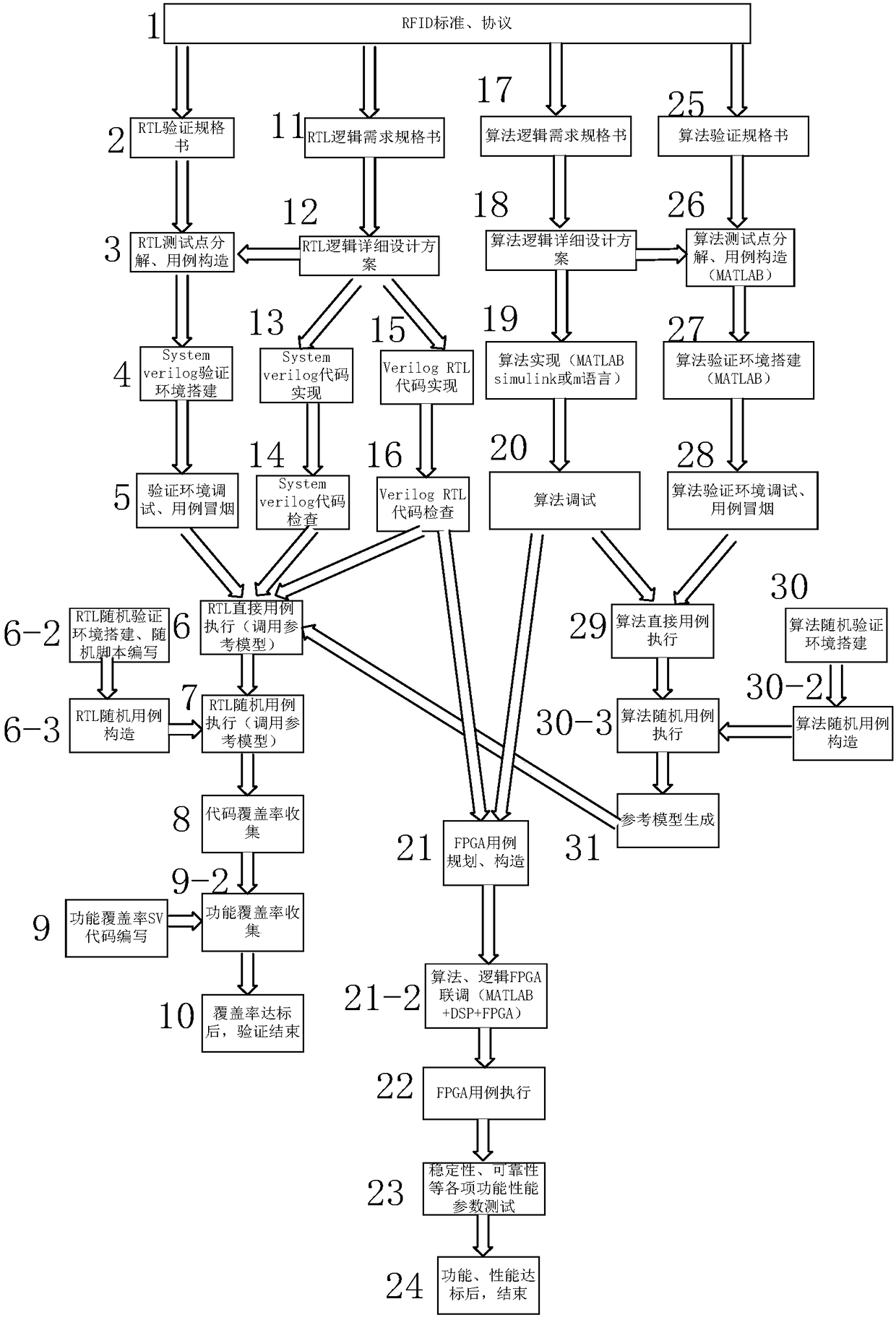

[0044] figure 1 As shown, a design verification method for a passive tag chip is disclosed, including the following steps:

[0045] Step (1), determine the RFID standard protocol to determine the various functions and performance indicators to be achieved by the RFID; wherein, the above-mentioned RFID standard protocol can be formulated by the state or by the RFID industry.

[0046] In step (2), after the RFID standard protocol is determined, the logic verification engineer begins to write the RTL (RegisterTransferLevel register transfer level circuit) logic verification specification. When writing, it is necessary to refer to the logic detailed design plan written by the logic design engineer in step (12), and the RTL The verification specifications in the logic verification specification must cover all the functions and performance indicators in the standard protocol of step (1); after the logic verification specification is written, it needs to be reviewed by logic and algo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More