Method for reducing size of territory file

A file size and layout technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of increasing layout file size, lack of communication, and high complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be described in detail below in conjunction with the embodiments and accompanying drawings, but the present invention is not limited thereto.

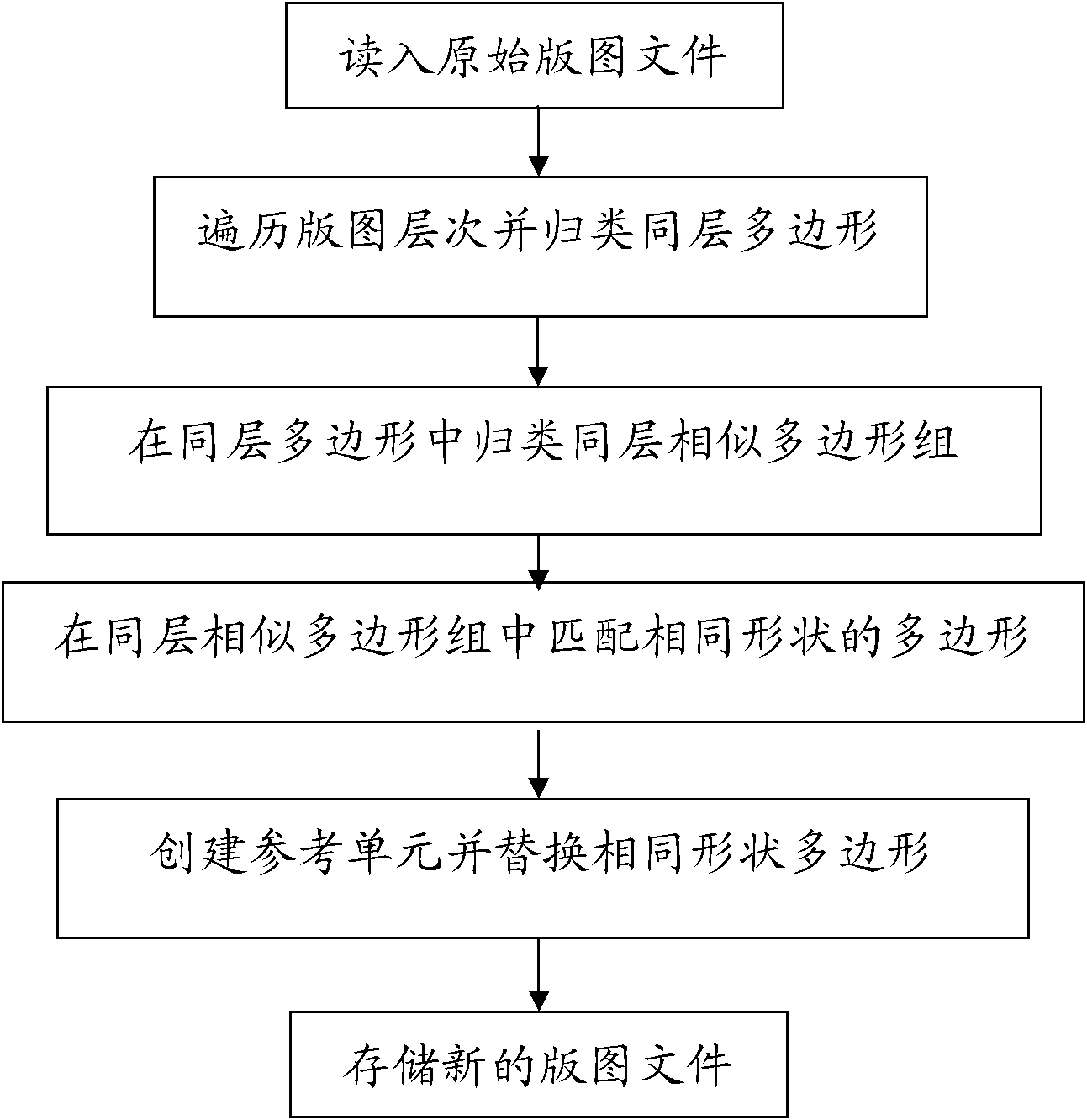

[0033] like figure 1 As shown, a method for reducing the size of the layout file includes the following steps:

[0034] (1) read in the original layout file;

[0035] The original layout file stores the layers of all related geometric figures and the basic composition of the geometric figures, and reading the layout file will obtain the layer and basic composition information of all the geometric figures. Usually, there are several layers stored in the original layout file, and there are several polygons on each layer, and each polygon includes the layer to which the polygon belongs and the coordinates of all vertices of the polygon.

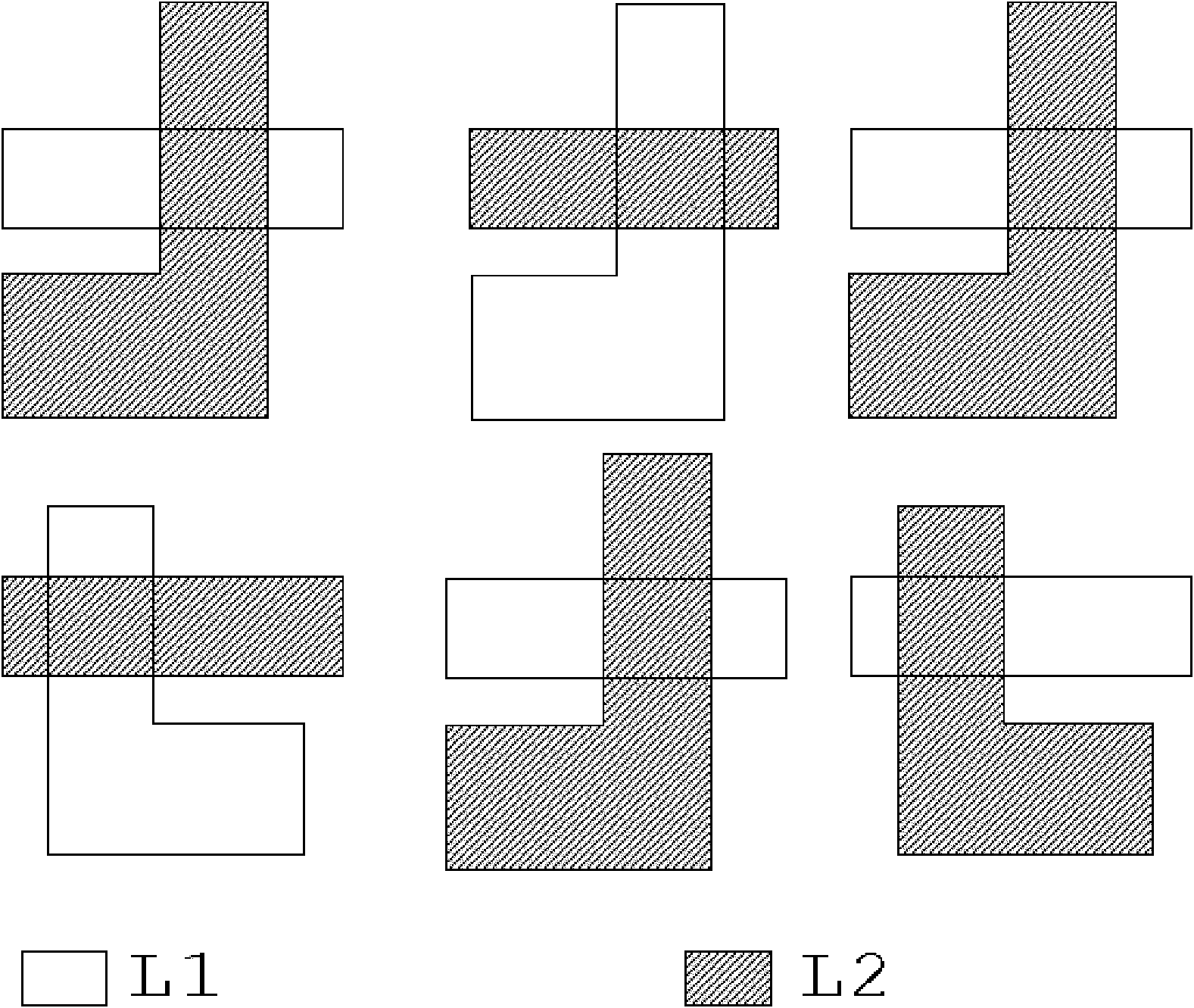

[0036] For simplicity, in figure 2 The schematic diagrams of two typical different levels and several polygons on the levels in the original layout file are given in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More