Method and device for FPGA (field programmable gate array) to communicate with DSP (digital signal processor) via DDR2 (double data rate 2) interface

A DDR2, interface technology, which is applied in the field of field programmable gate arrays and digital signal processors through DDR2 interfaces, can solve the problems of large FPGA resource consumption, increased device cost, resource consumption, etc., and achieve the effect of reducing costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] Hereinafter, the implementation of the method and device for FPGA to communicate with DSP through the DDR2 interface in the embodiment of the present invention will be described in detail in conjunction with the accompanying drawings.

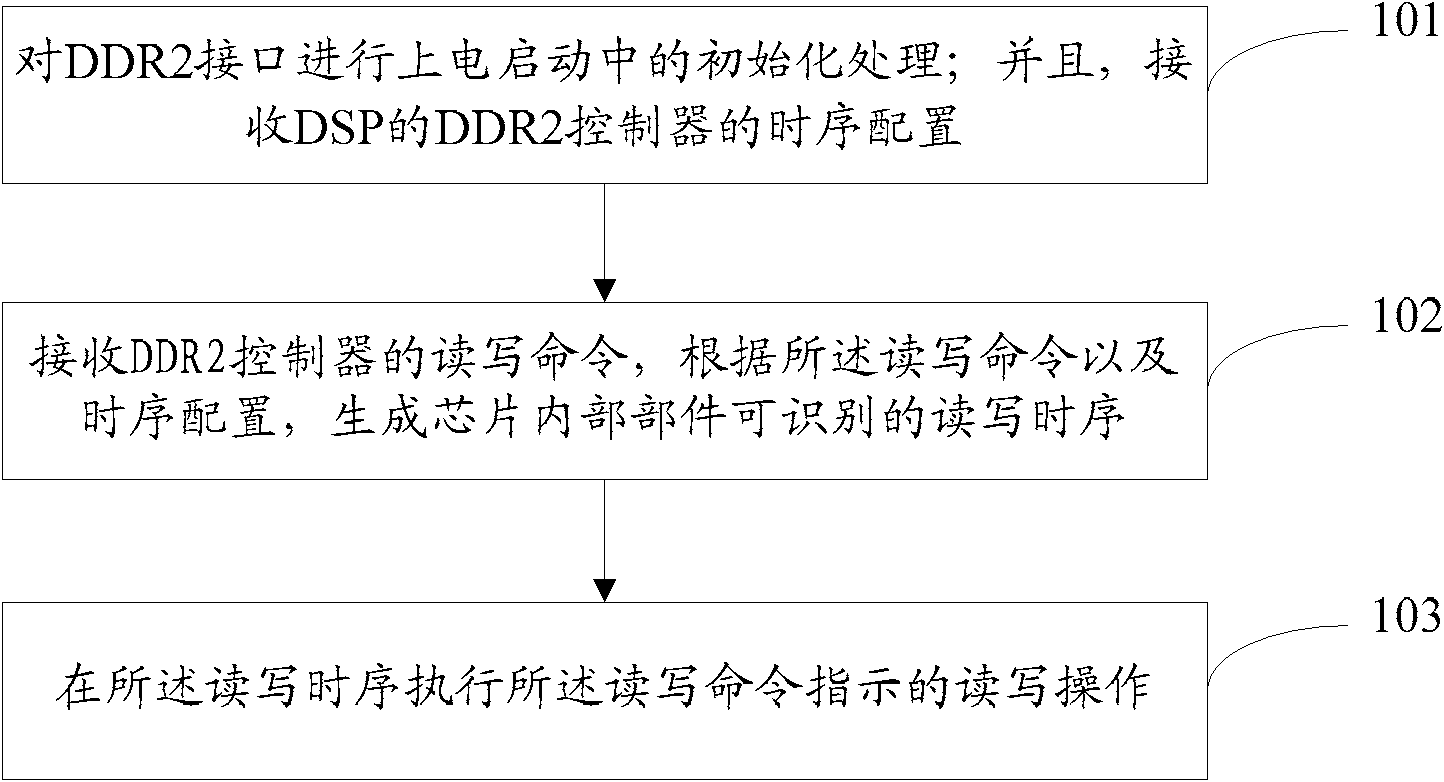

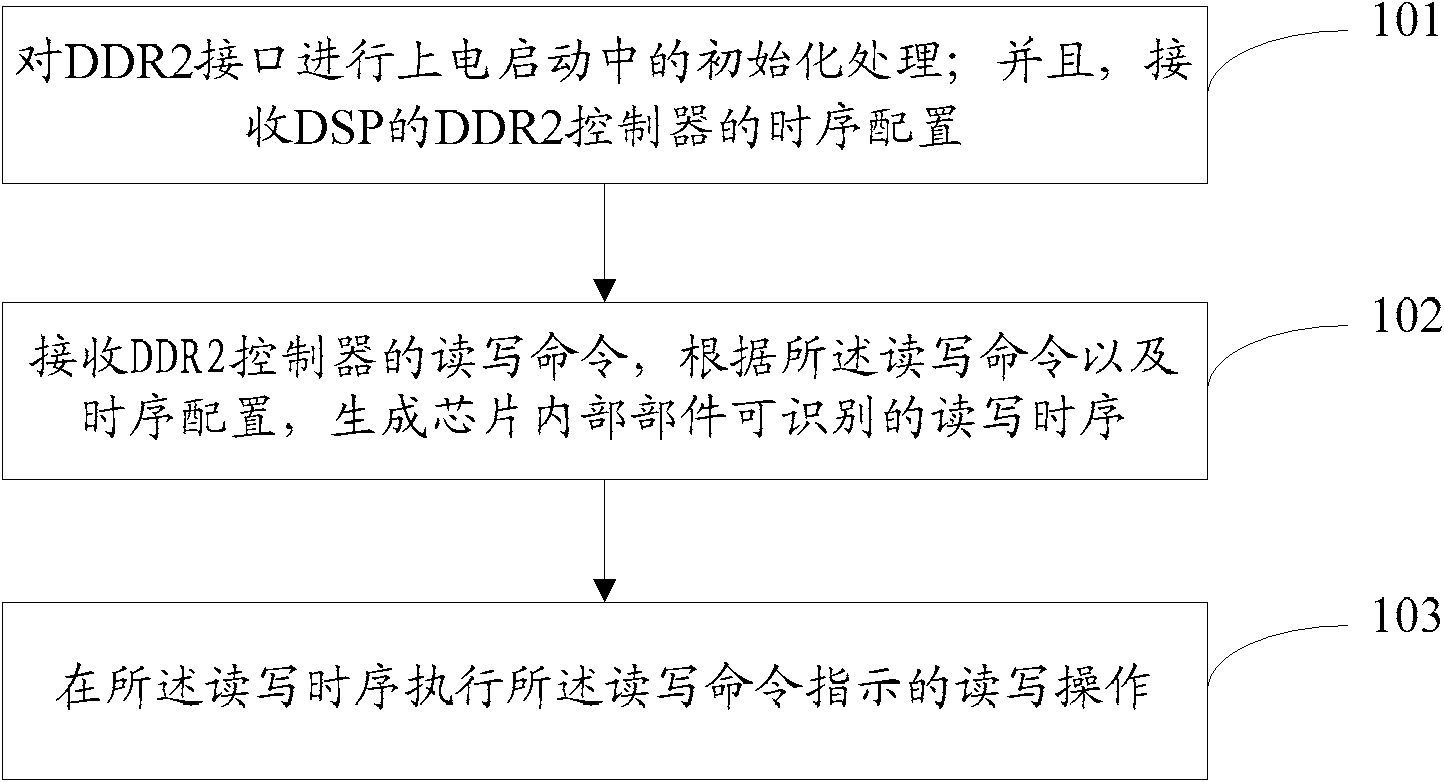

[0052] figure 1 For the embodiment of the present invention FPGA communicates with the method flow diagram of DSP through DDR2 interface, this method can be applicable to in the FPGA chip; figure 1 As shown, the method includes:

[0053] Step 101: The FPGA performs initialization processing on the DDR2 interface during power-on startup; and receives the timing configuration of the DDR2 controller of the DSP;

[0054] Wherein, the initialization process may include:

[0055] A: Receive the initialization command of the mode register (MR) and the initialization command of the extended mode register (EMR) from the DDR2 of the DSP;

[0056] MR includes parameters such as CAS latency (CL), trigger type, and trigger length (BL).

[0057] E...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More