Thin film transistor

一种薄膜晶体管、晶体的技术,应用在晶体管、电固体器件、半导体器件等方向

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0095] In this embodiment, an example of a form of a thin film transistor will be described with reference to the drawings.

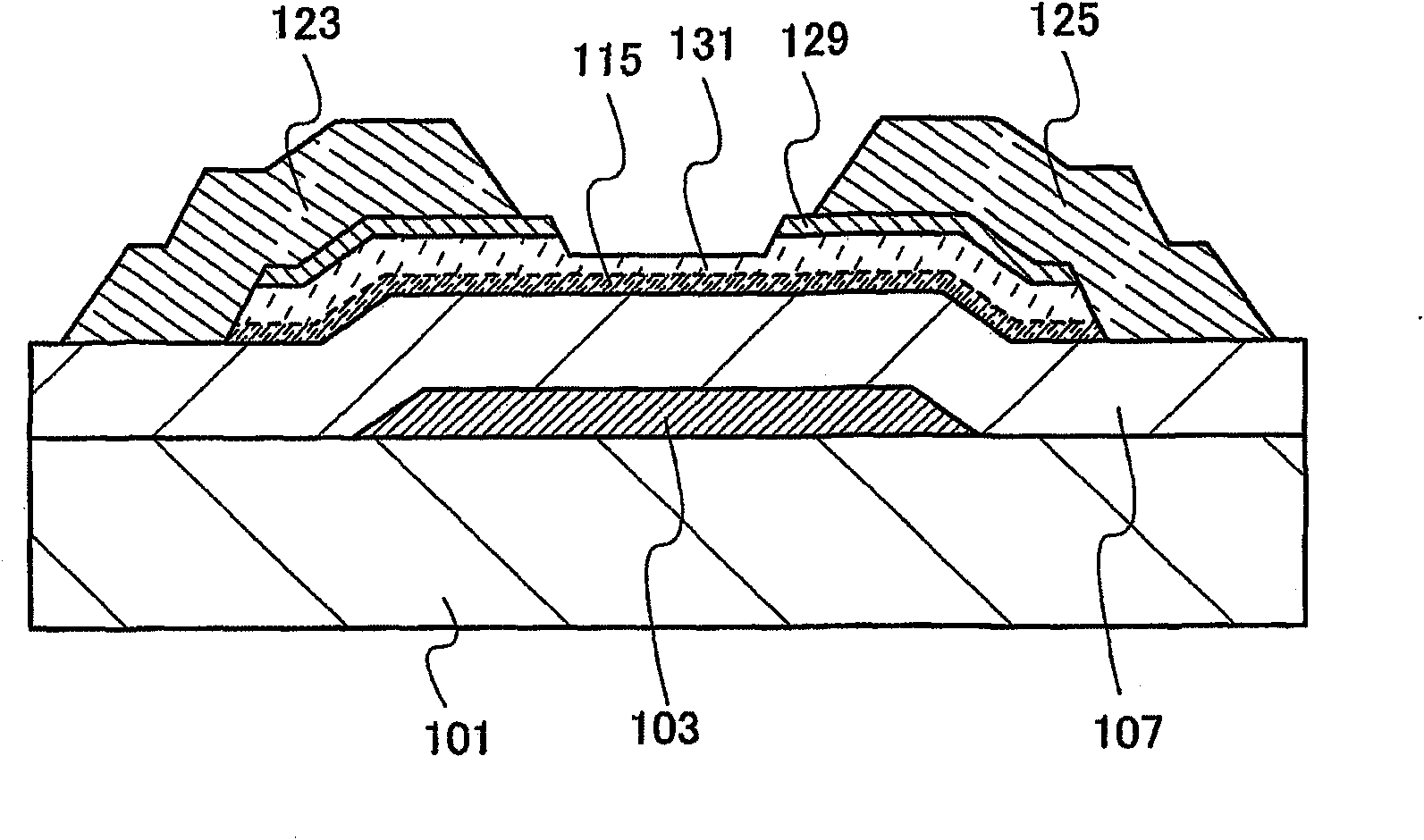

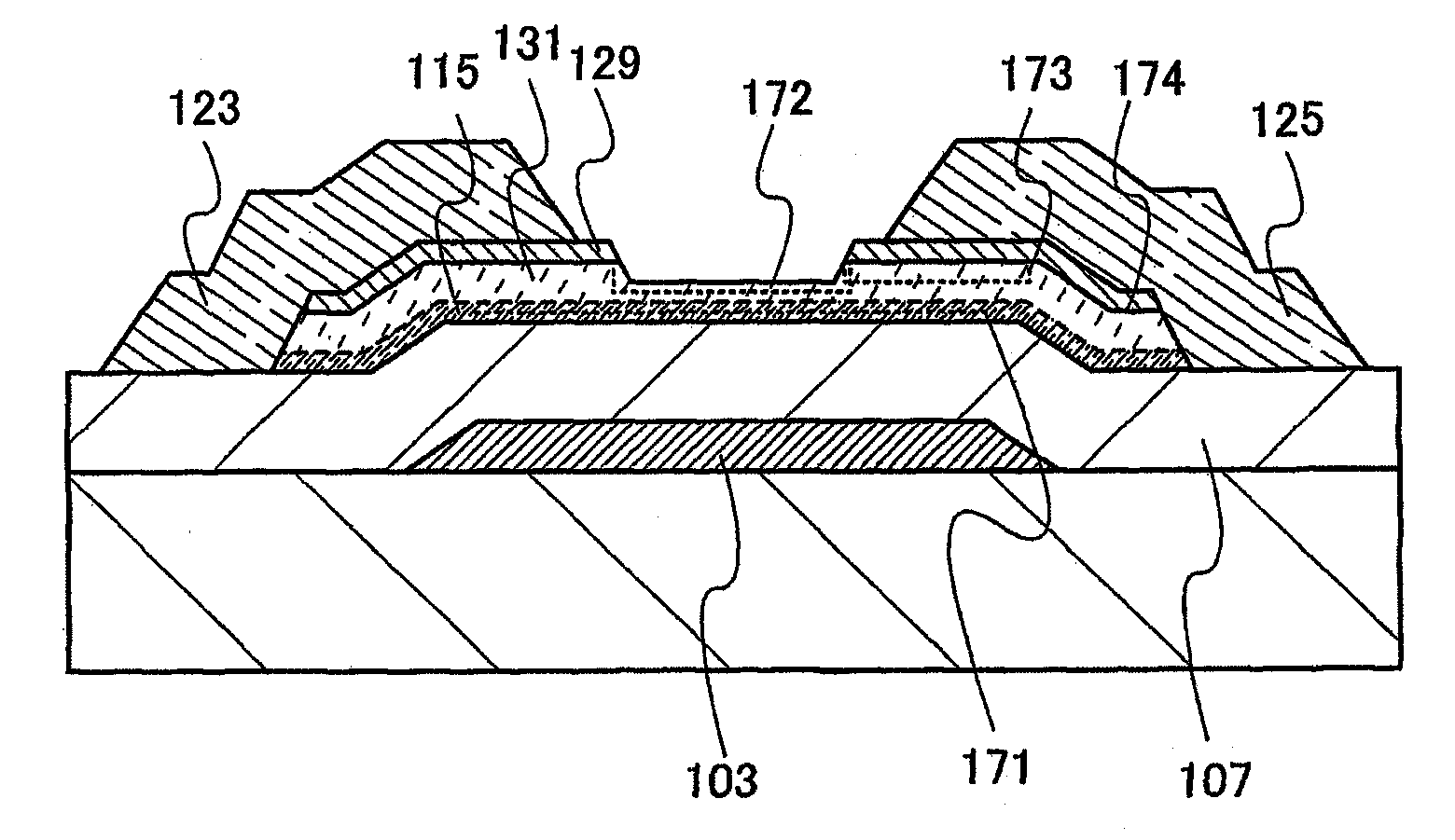

[0096] Figure 1A and 1B A cross-sectional view showing a thin film transistor according to this embodiment. Figure 1A The illustrated thin film transistor has a gate electrode layer 103 on a substrate 101, a gate insulating layer 107 covering the gate electrode layer 103, a semiconductor layer 115 in contact with the gate insulating layer 107 and serving as a channel formation region, and a semiconductor layer 115 on the semiconductor layer 115. The buffer layer 131, and the source region and the drain region 129 disposed on the buffer layer 131 and in contact with a part thereof. In addition, the thin film transistor further has wiring layers 123 and 125 provided on and in contact with the source region and the drain region 129 . The wiring layers 123 and 125 constitute source electrodes and drain electrodes. In addition, each layer is patterned in...

Embodiment 2

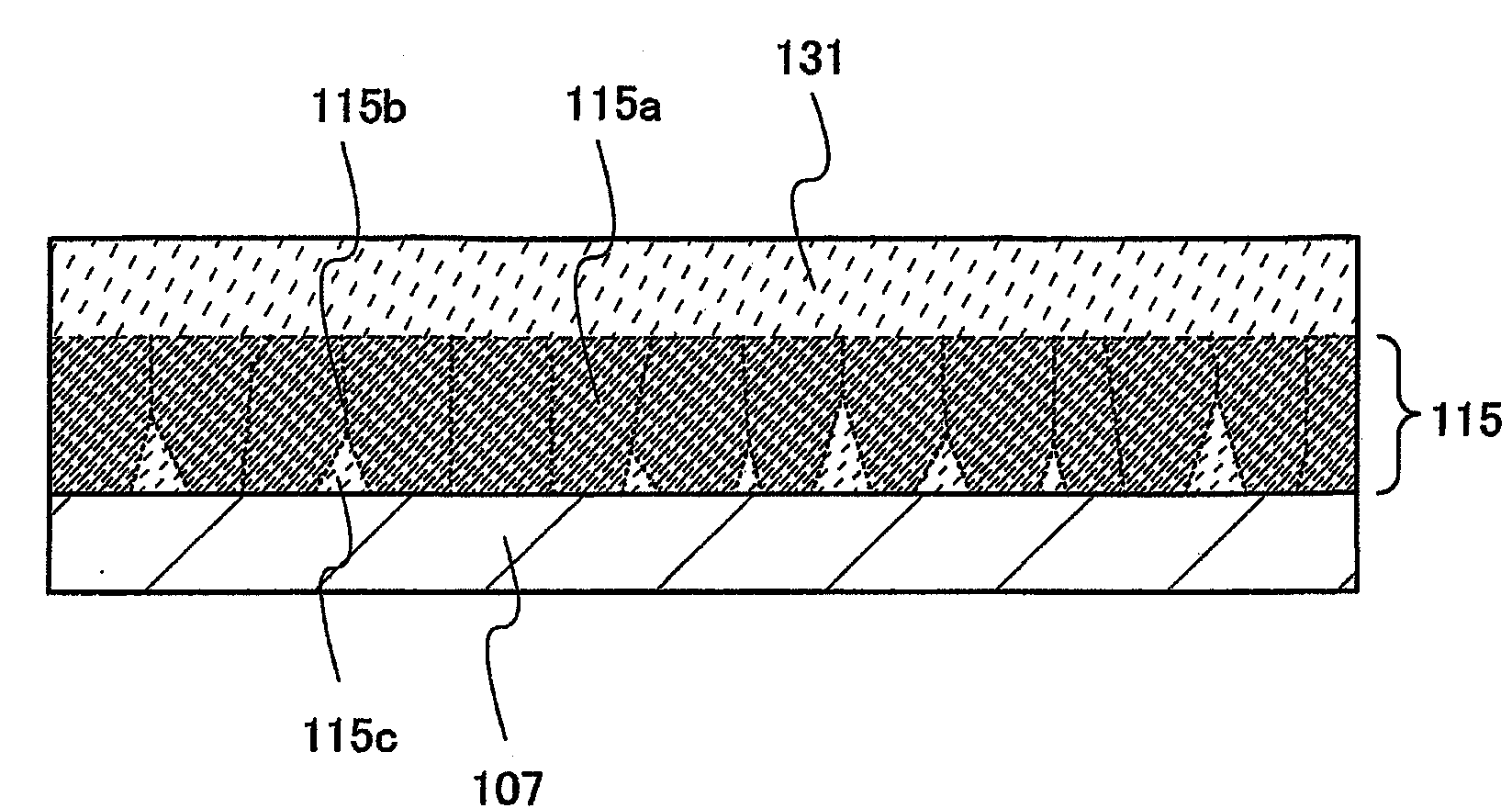

[0194] In this example, reference will be made to Figure 9 to Figure 10B A mode usable for the semiconductor layer 115 in the thin film transistor shown in Embodiment 1 will be described.

[0195] In the thin film transistor described in this embodiment, dispersed microcrystalline semiconductor particles or network-shaped microcrystalline semiconductor 118 are formed on the gate insulating layer 107 (refer to Figure 9 ).

[0196] Figure 10A The shown dispersed microcrystalline semiconductor particles 118a or Figure 10B The shown network microcrystalline semiconductor 118b can use silicon or silicon germanium (Si germanium) whose content of silicon is more than that of germanium. X Ge 1-X , 0.5 Figure 10A The shape of the dispersed microcrystalline semiconductor particles 118a shown is circular, while as Figure 9 The cross-sectional shape shown is hemispherical. When the diameter of dispersed microcrystalline semiconductor particles is set to be 1nm to 30nm when view...

Embodiment 3

[0203] In this Example 3, reference will be made to Figure 11 The semiconductor layer 115 in Embodiment 1 is described as a thin film transistor formed by using a semiconductor layer having a crystalline region in an amorphous structure, that is, a thin film transistor having a crystalline region in an amorphous structure is formed between the gate insulating layer and the source region and the drain region. semiconductor layer of thin film transistors.

[0204] Figure 11 is a cross-sectional view of the thin film transistor according to the present embodiment. Figure 11 The shown thin film transistor comprises: a gate electrode layer 103 on a substrate 101; a gate insulating layer 107 covering the gate electrode layer 103; a semiconductor layer 132 disposed on and in contact with the gate insulating layer 107; A portion of 132 contacts the source and drain regions 129 . In addition, the thin film transistor includes wiring layers 123 and 125 disposed on and in contact w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More