Patents

Literature

30results about How to "Reduce cut-off current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device and method for driving semiconductor device

InactiveCN102376713AReduce cut-off currentReduce frequencySolid-state devicesRead-only memoriesSemiconductor materialsCapacitor

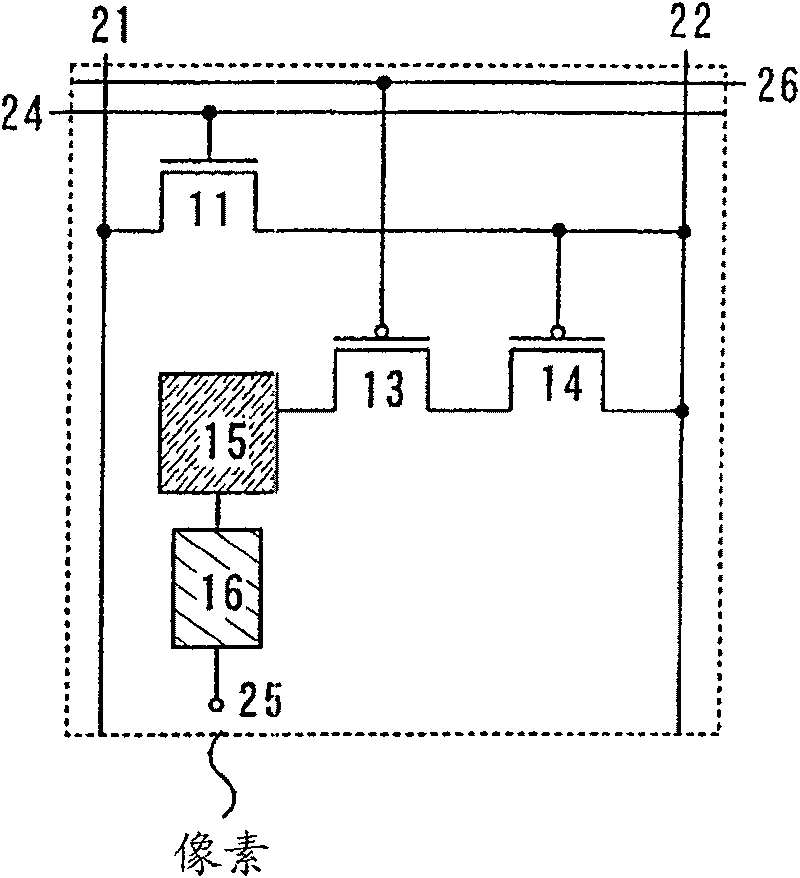

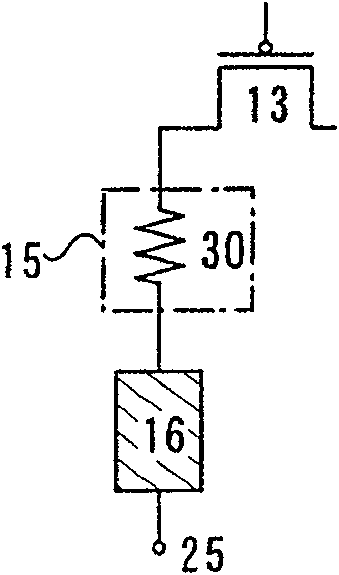

The present invention relates to a semiconductor device and a method for driving the semiconductor device. It is an object to provide a semiconductor device with a novel structure in which stored data can be held even when power is not supplied, and does not have a limitation on the number of writing operations. The semiconductor device includes a plurality of memory cells each including a transistor including a first semiconductor material, a transistor including a second semiconductor material that is different from the first semiconductor material, and a capacitor, and a potential switching circuit having a function of supplying a power supply potential to a source line in a writing period. Thus, power consumption of the semiconductor device can be sufficiently suppressed.

Owner:SEMICON ENERGY LAB CO LTD

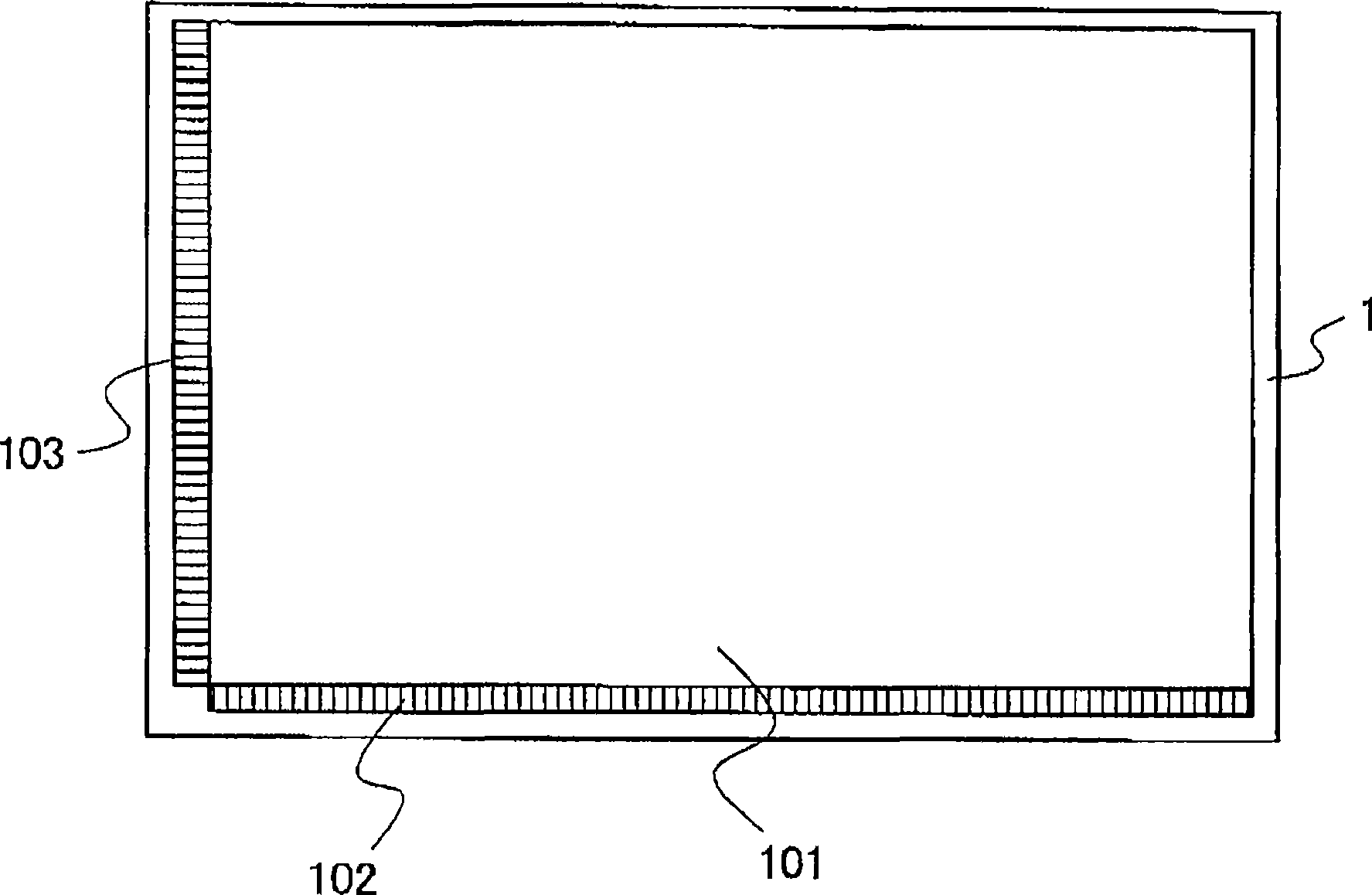

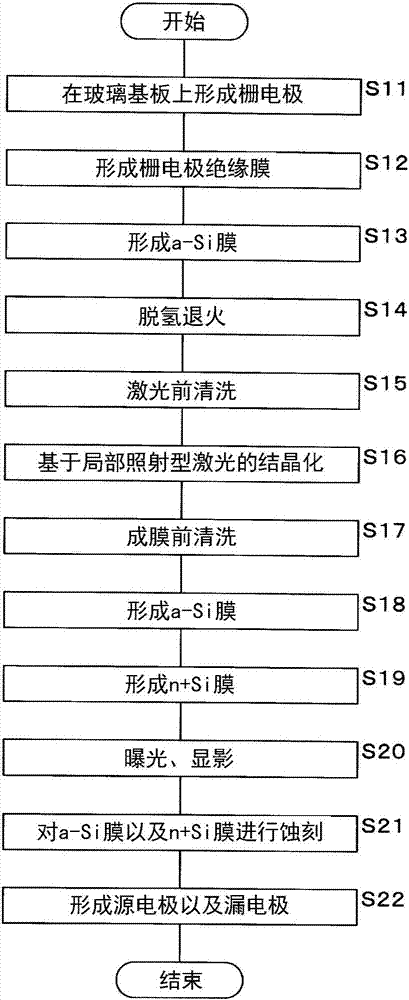

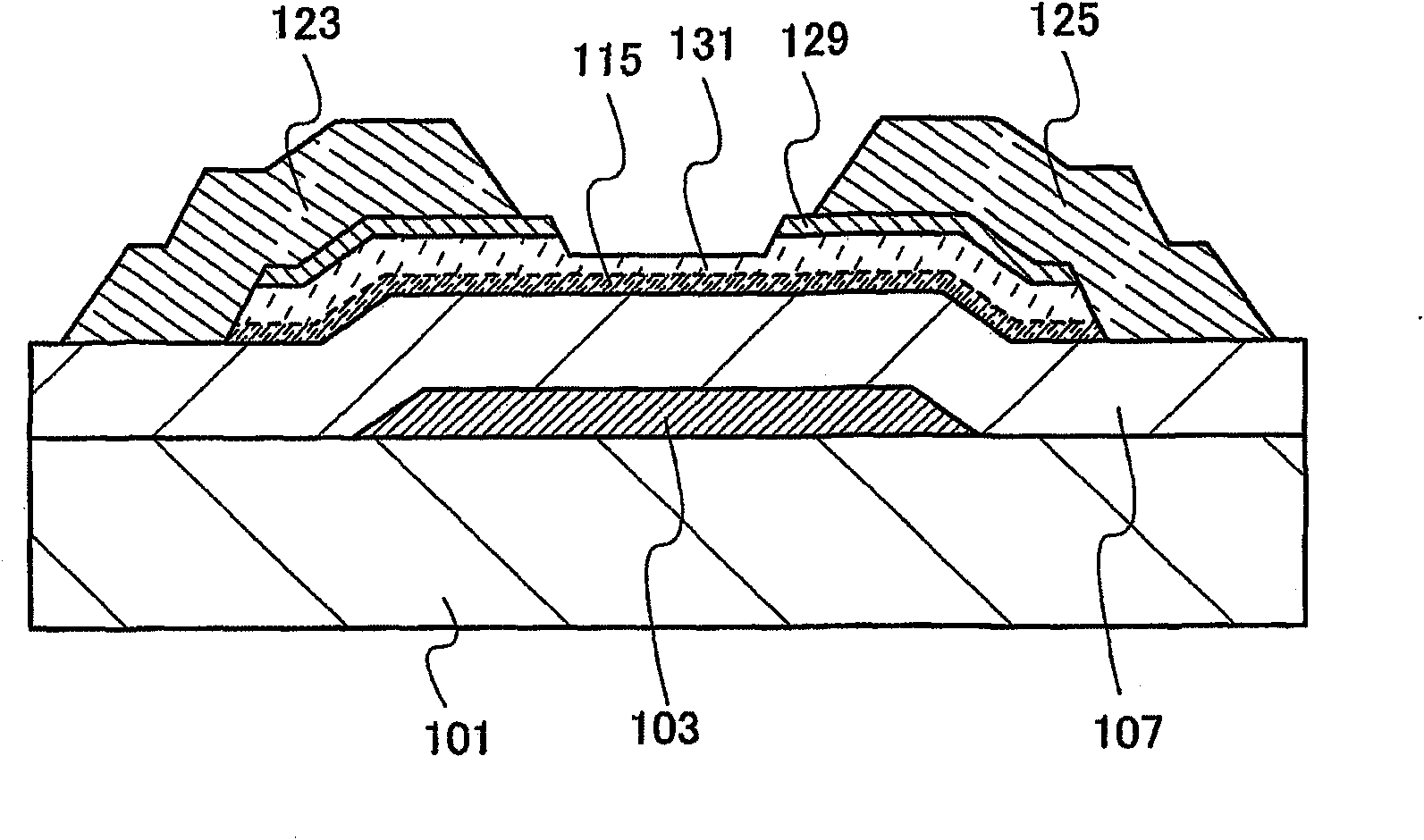

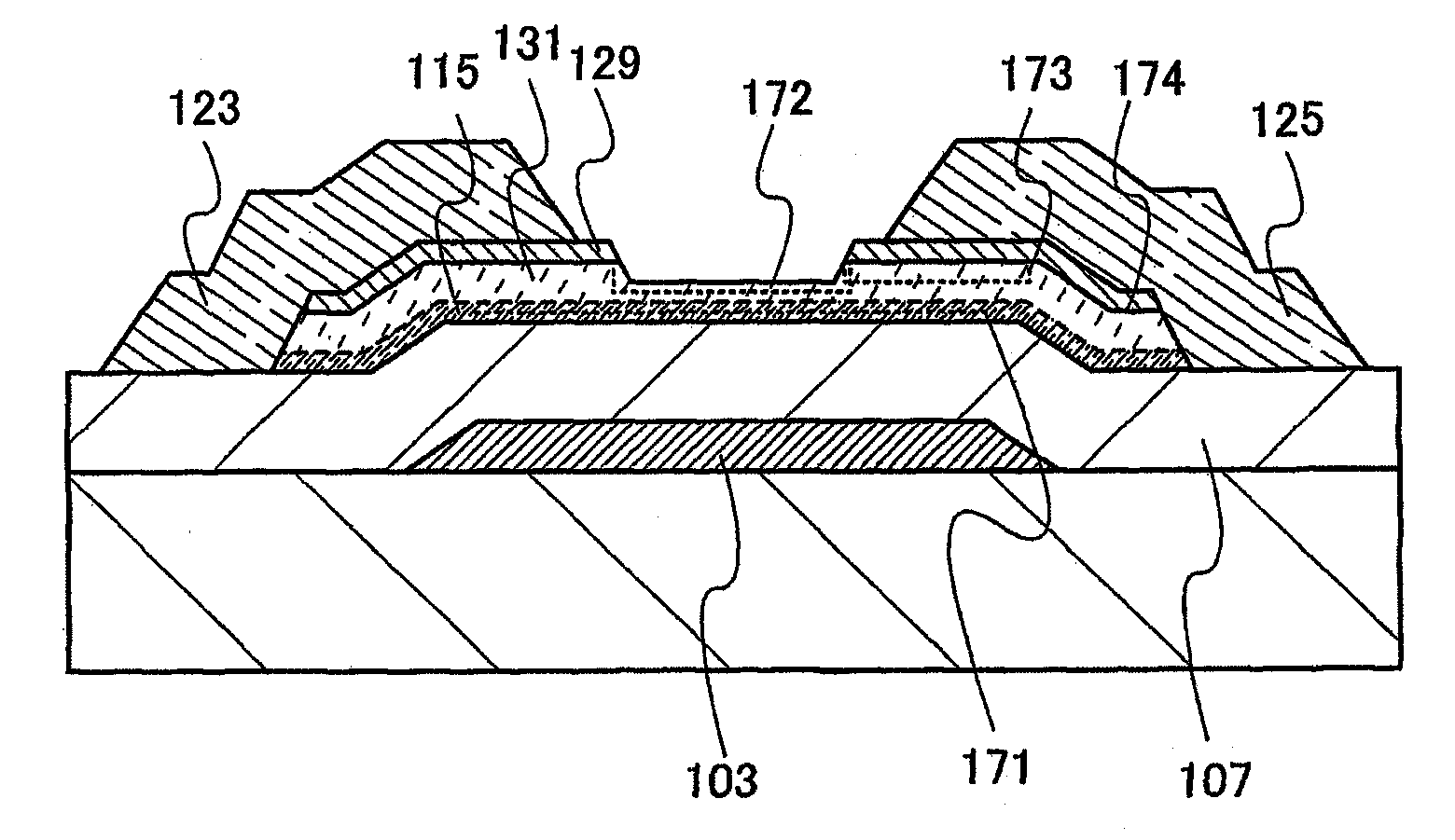

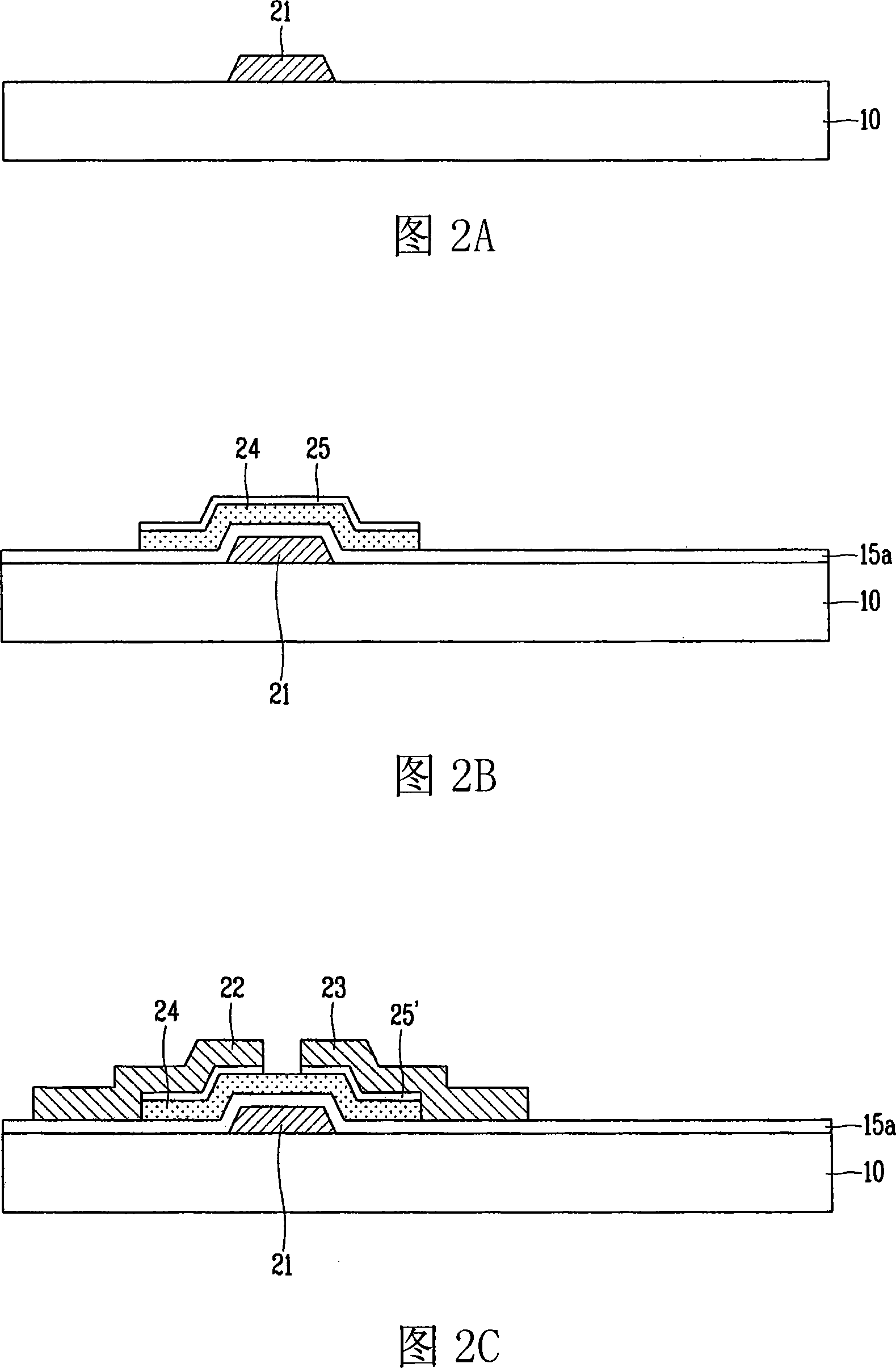

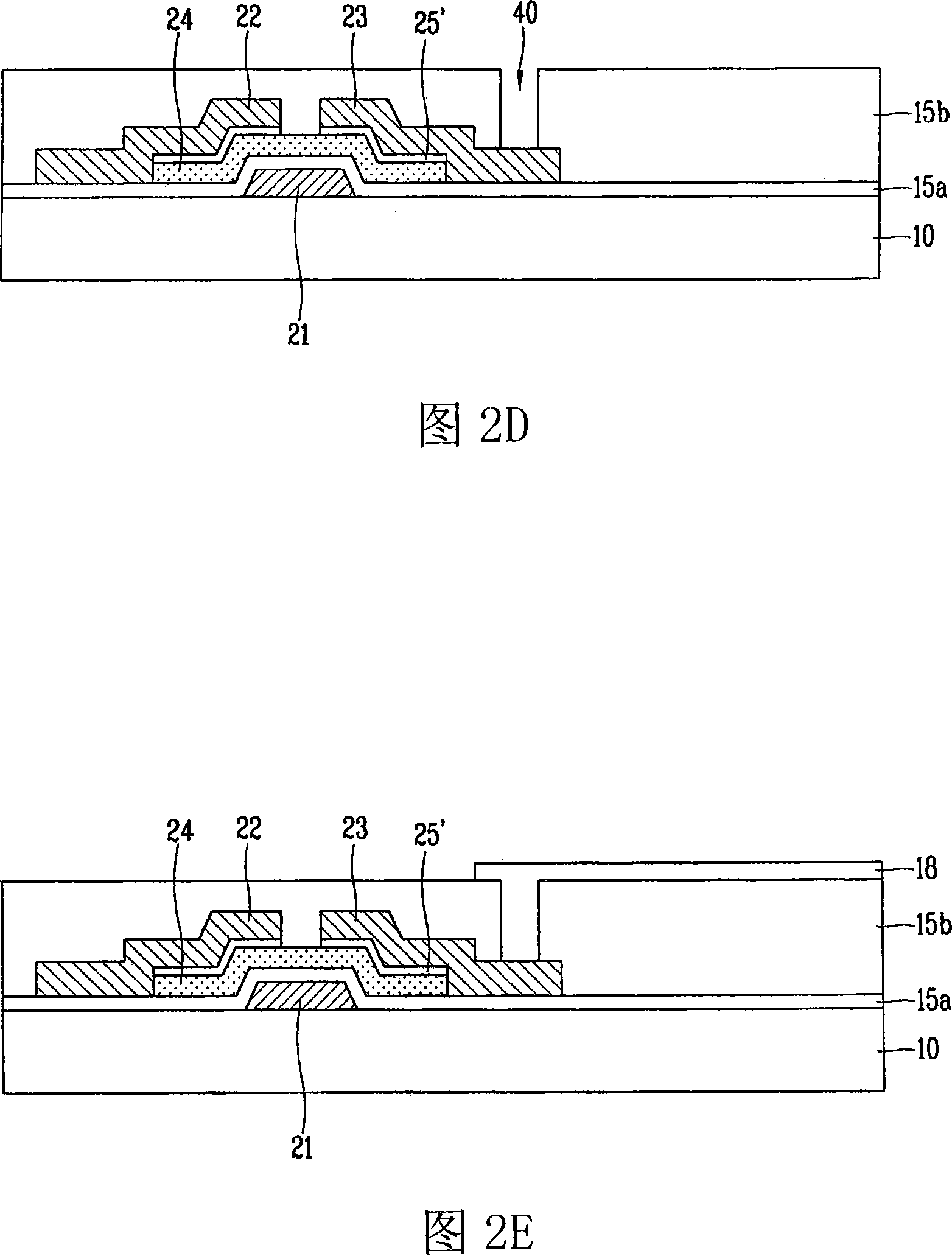

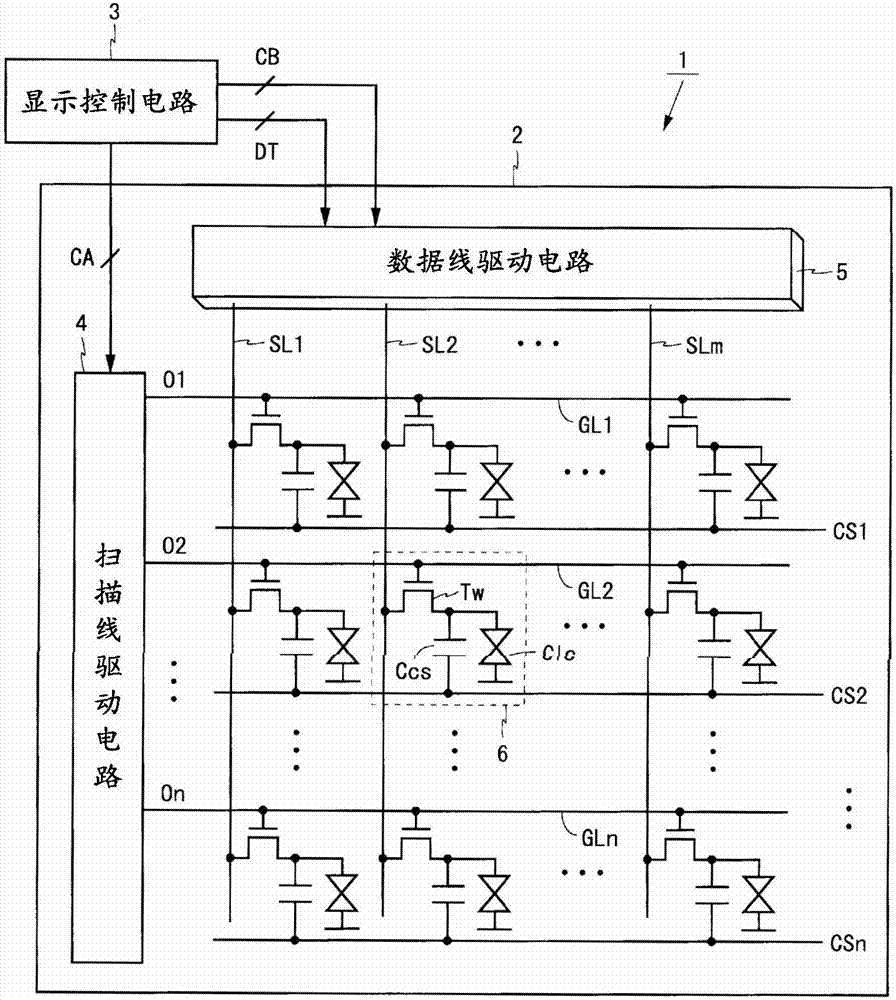

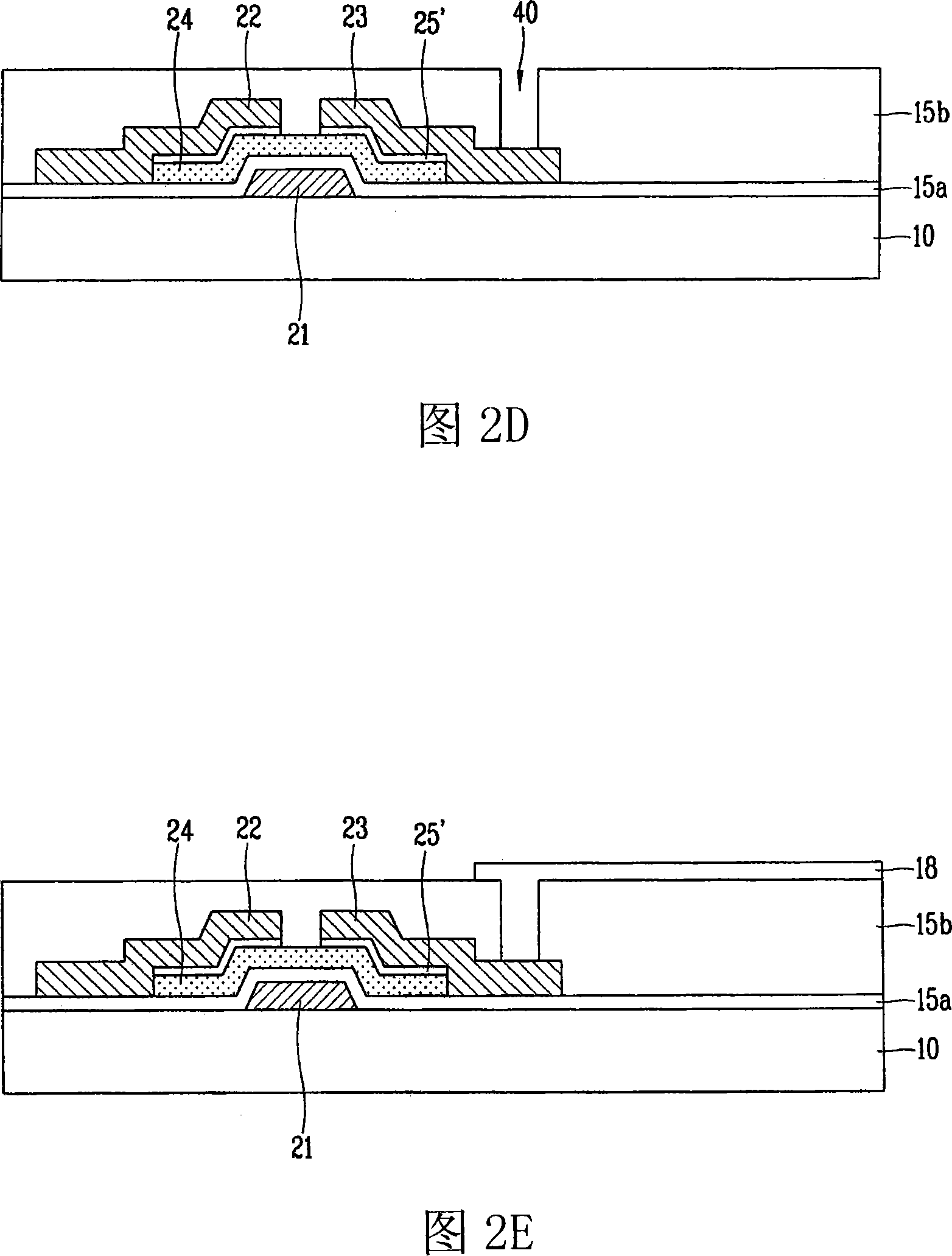

Display device and method of manufacturing display device

ActiveCN101414638ASimple structureIncrease the number of processesTransistorSolid-state devicesAmorphous siliconDisplay device

Owner:JAPAN DISPLAY INC +1

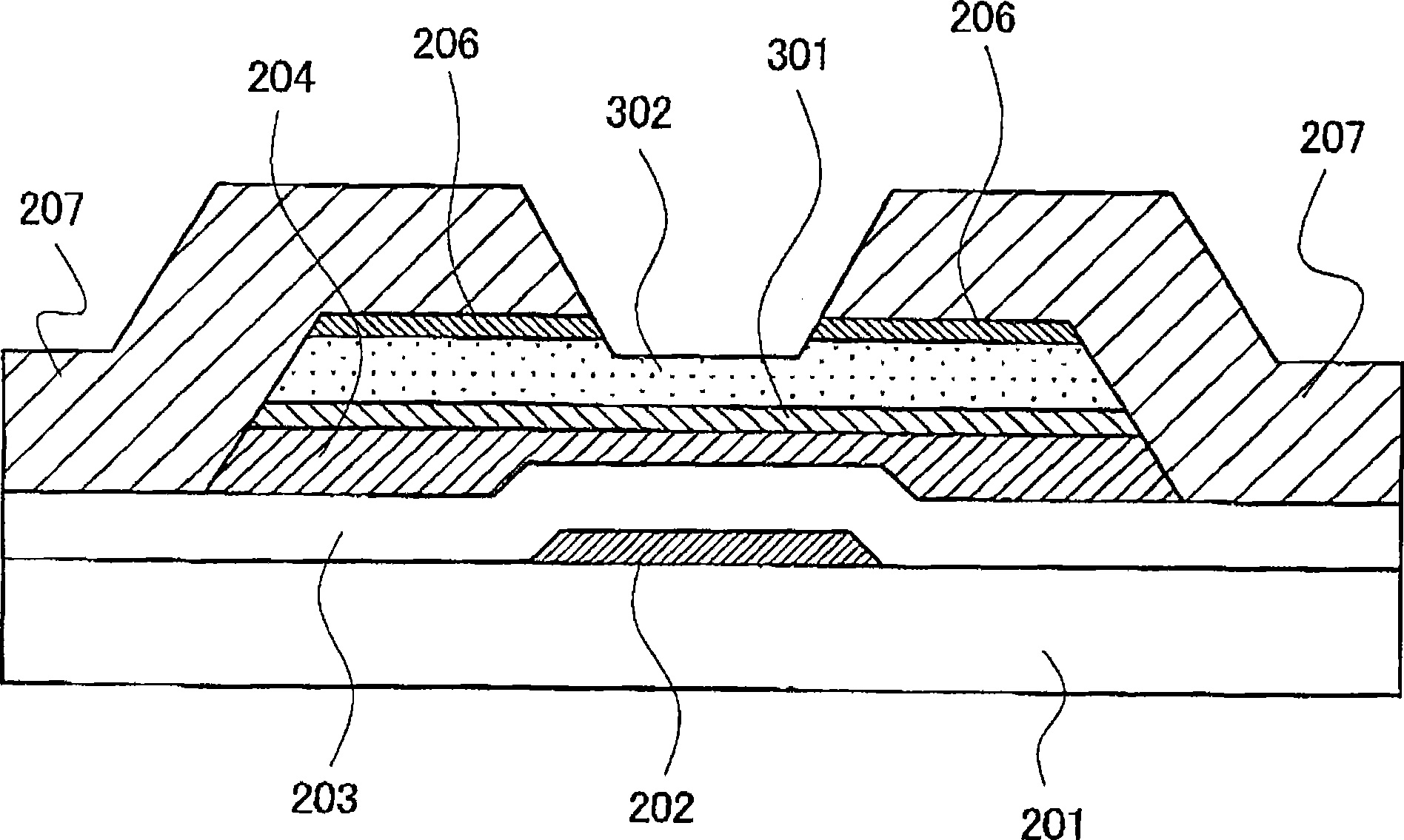

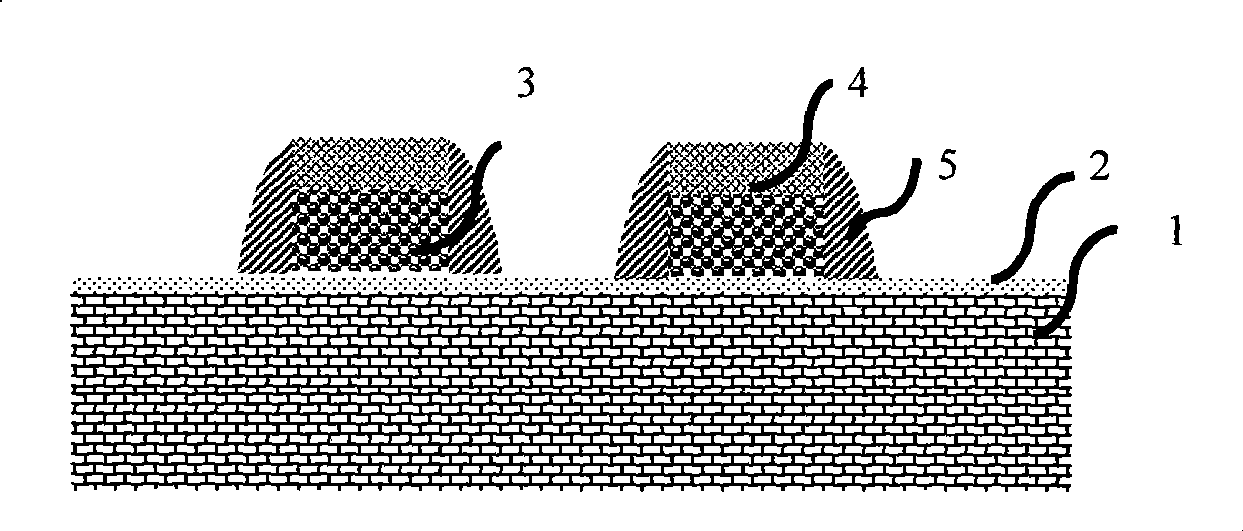

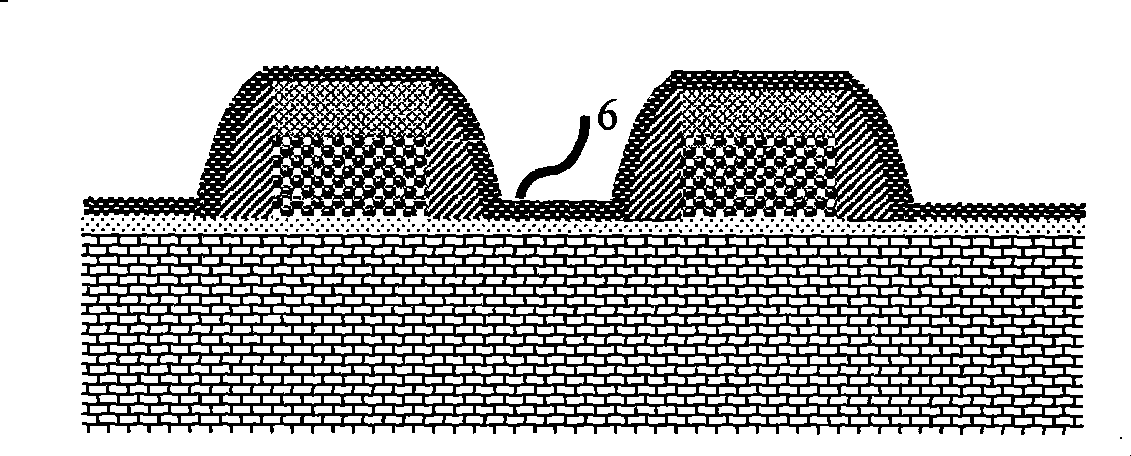

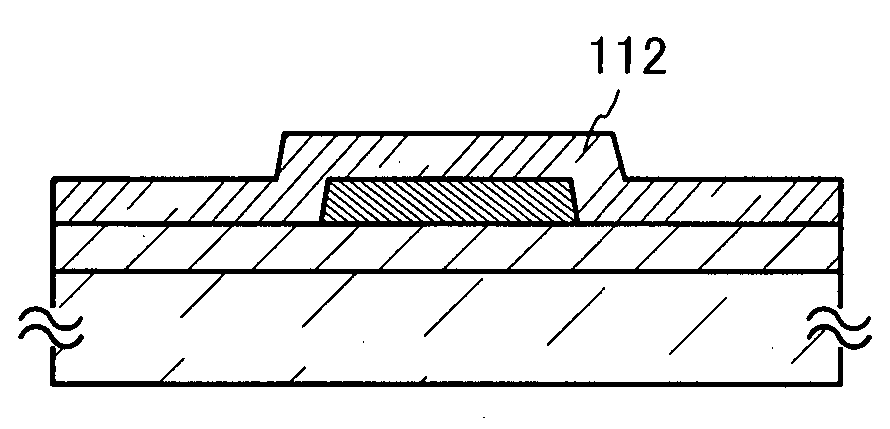

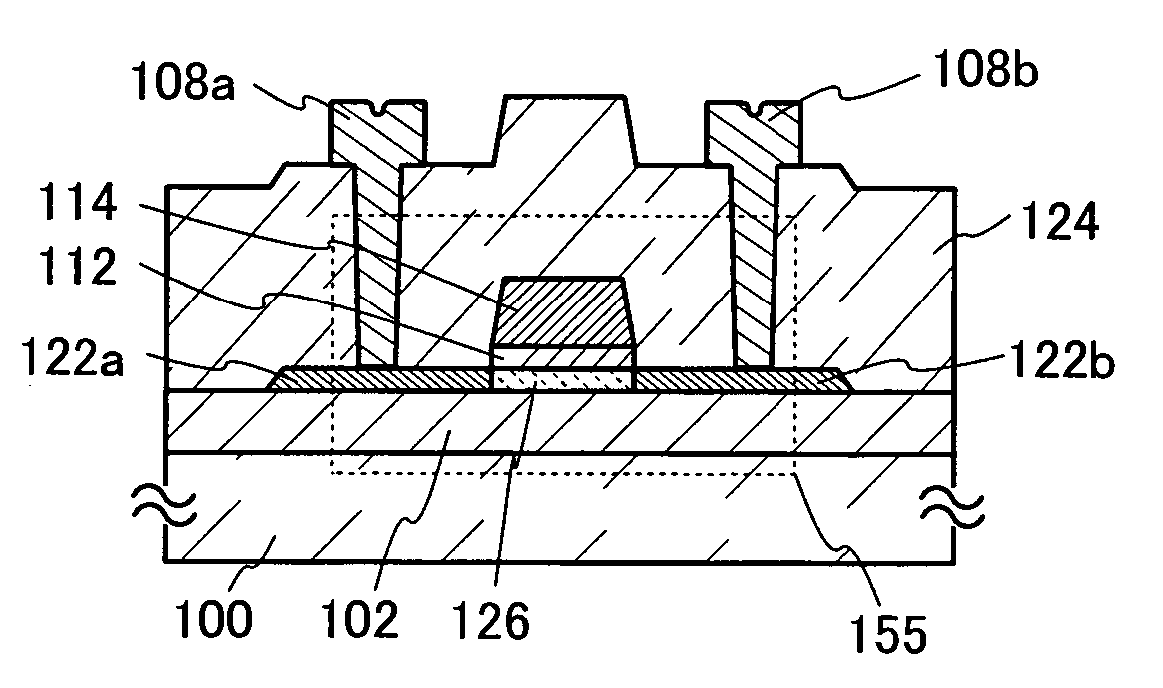

Semiconductor device and method of manufacturing the same

InactiveCN101207156APrevent degradationReduce cut-off currentTransistorSolid-state devicesHigh concentrationDevice material

An object of the present invention is to improve the operating characteristics and reliability of semiconductor devices. The invention relates to a peninsula body device, which includes: an island-shaped semiconductor film having a channel formation region, a first low concentration impurity region, a second low concentration impurity region, and a high concentration impurity region including a silicide layer; a gate insulation film; a first gate electrode overlapping the channel formation region and the first low concentration impurity region with the gate insulating film sandwiched therebetween; a first gate electrode overlapping the channel formation region with the gate insulating film sandwiched therebetween a second gate electrode; sidewalls formed on the sides of the first gate electrode and the second gate electrode, wherein the film thickness of the gate insulating film on the second low-concentration impurity region is thinner than that on the other side film thickness over the area.

Owner:SEMICON ENERGY LAB CO LTD

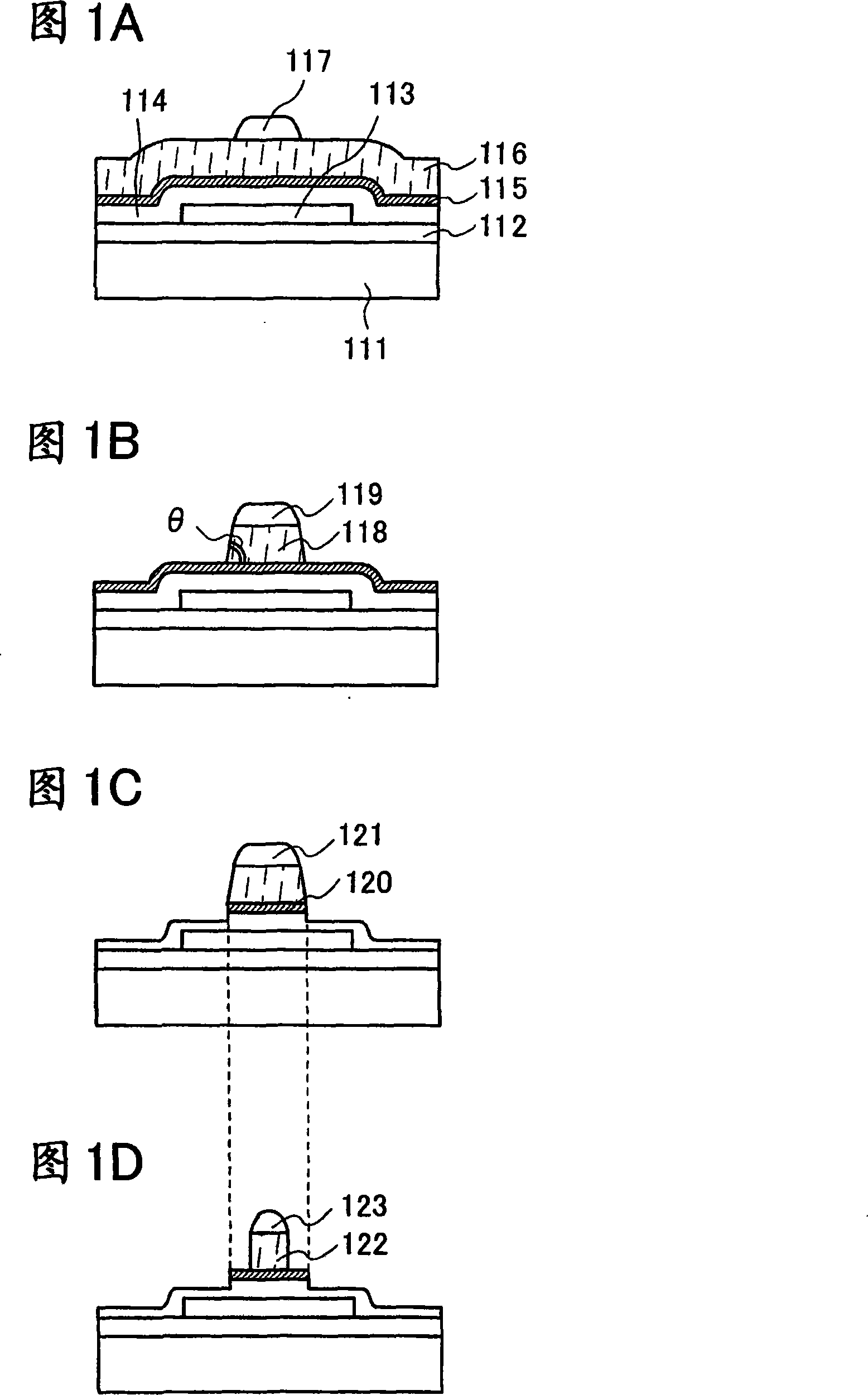

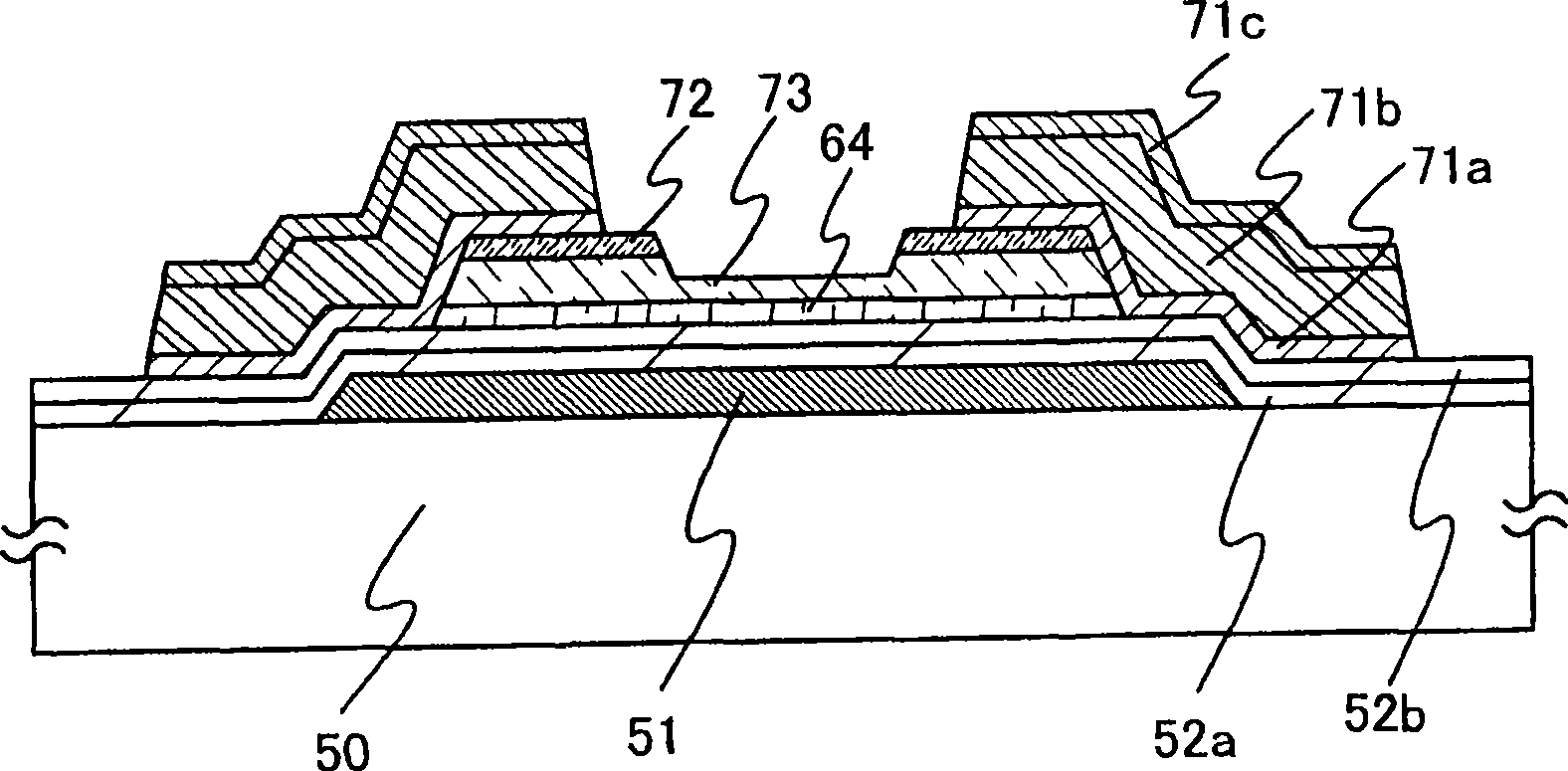

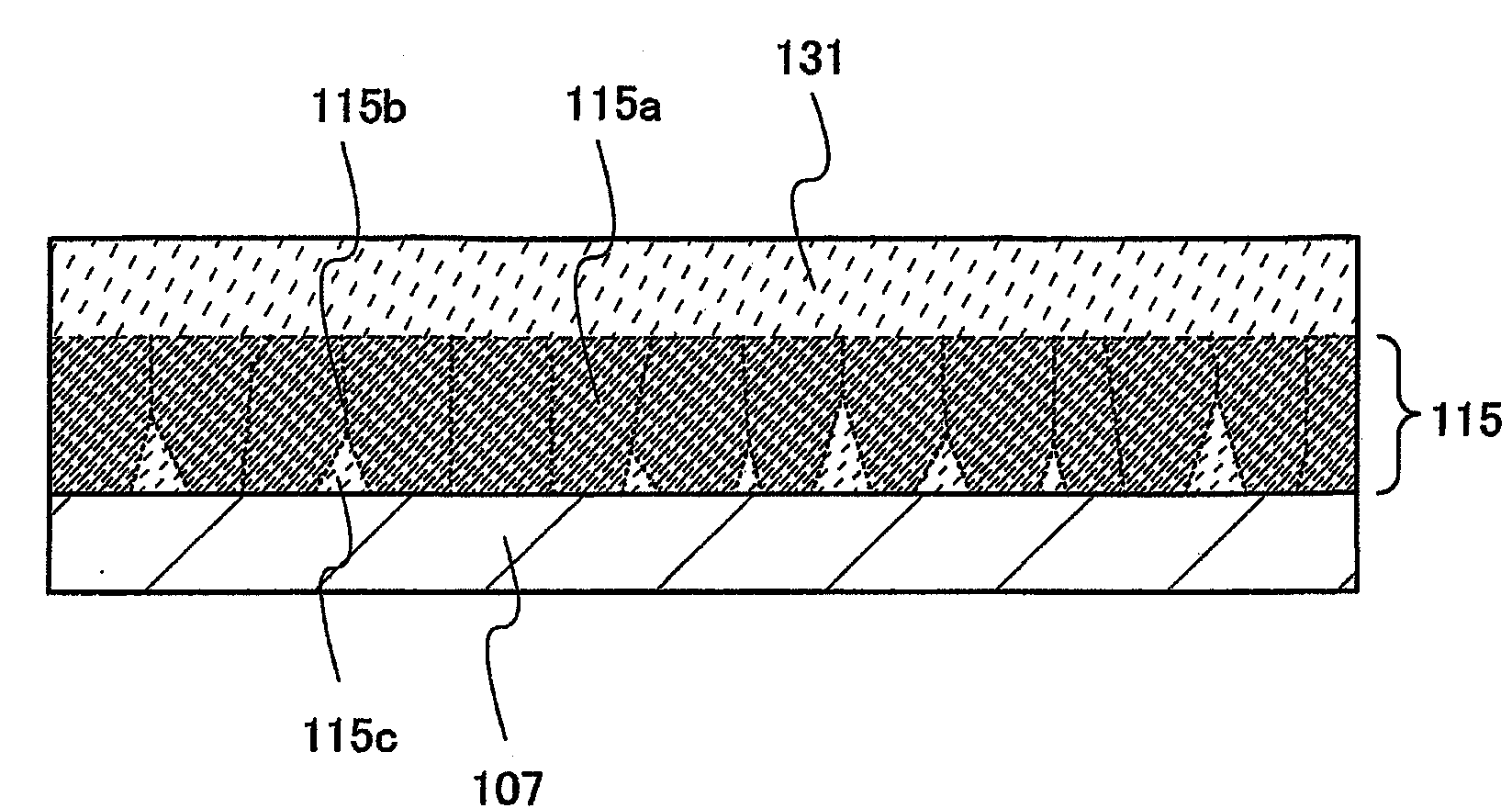

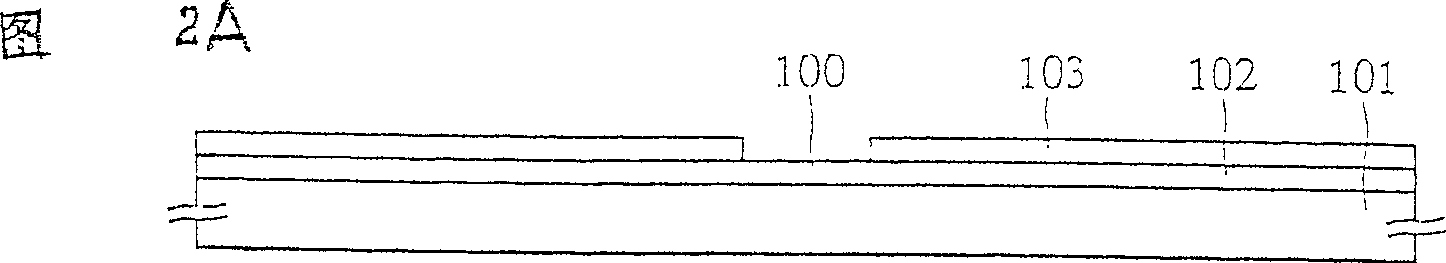

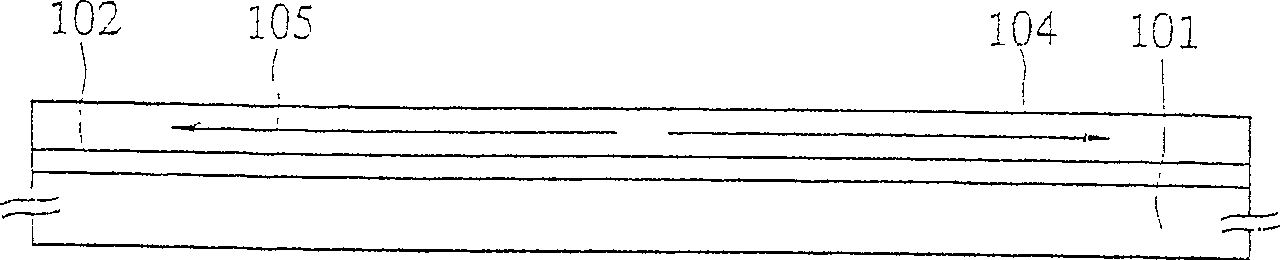

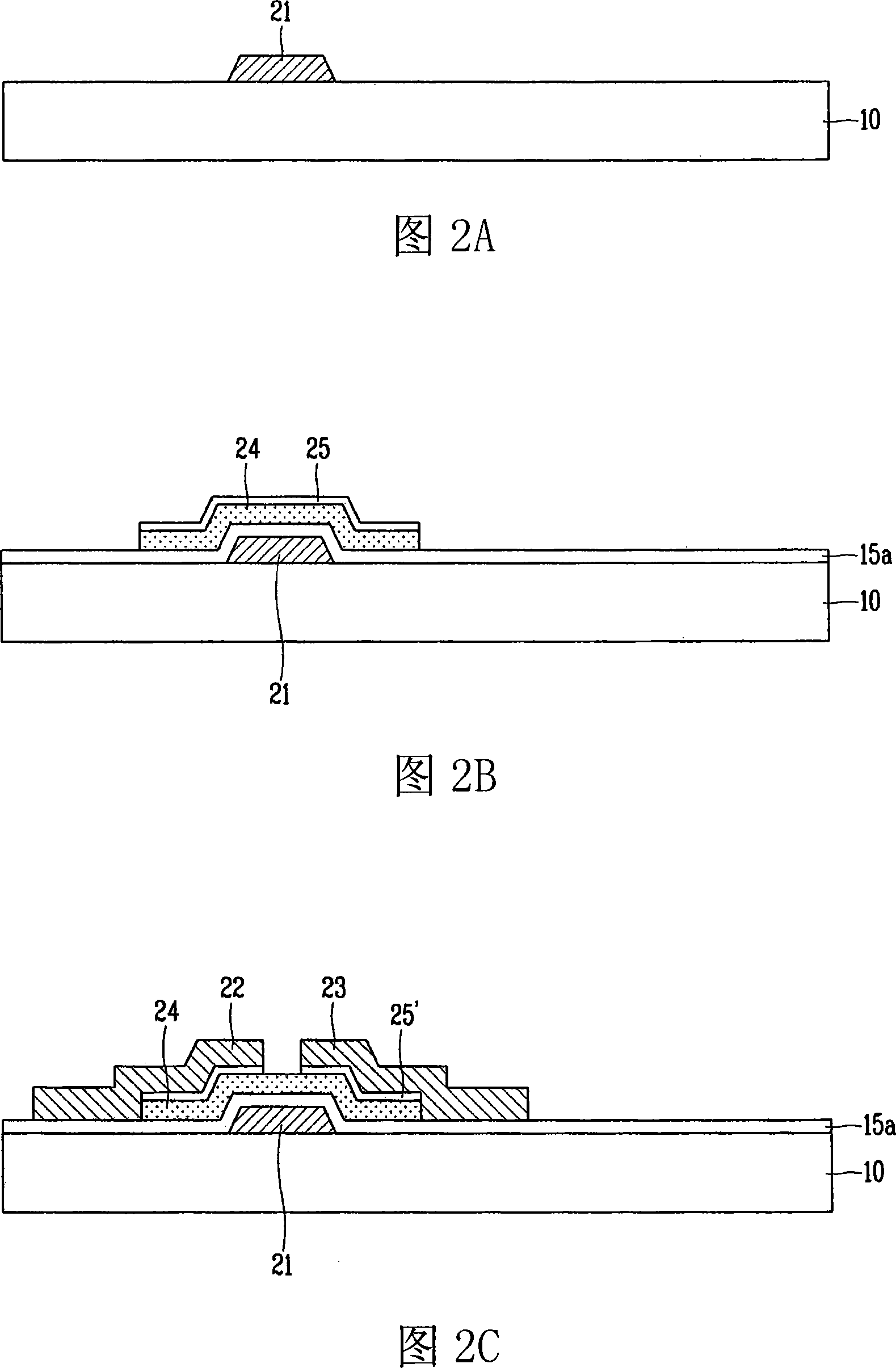

Thin film transistor, display device, and method for manufacturing the same

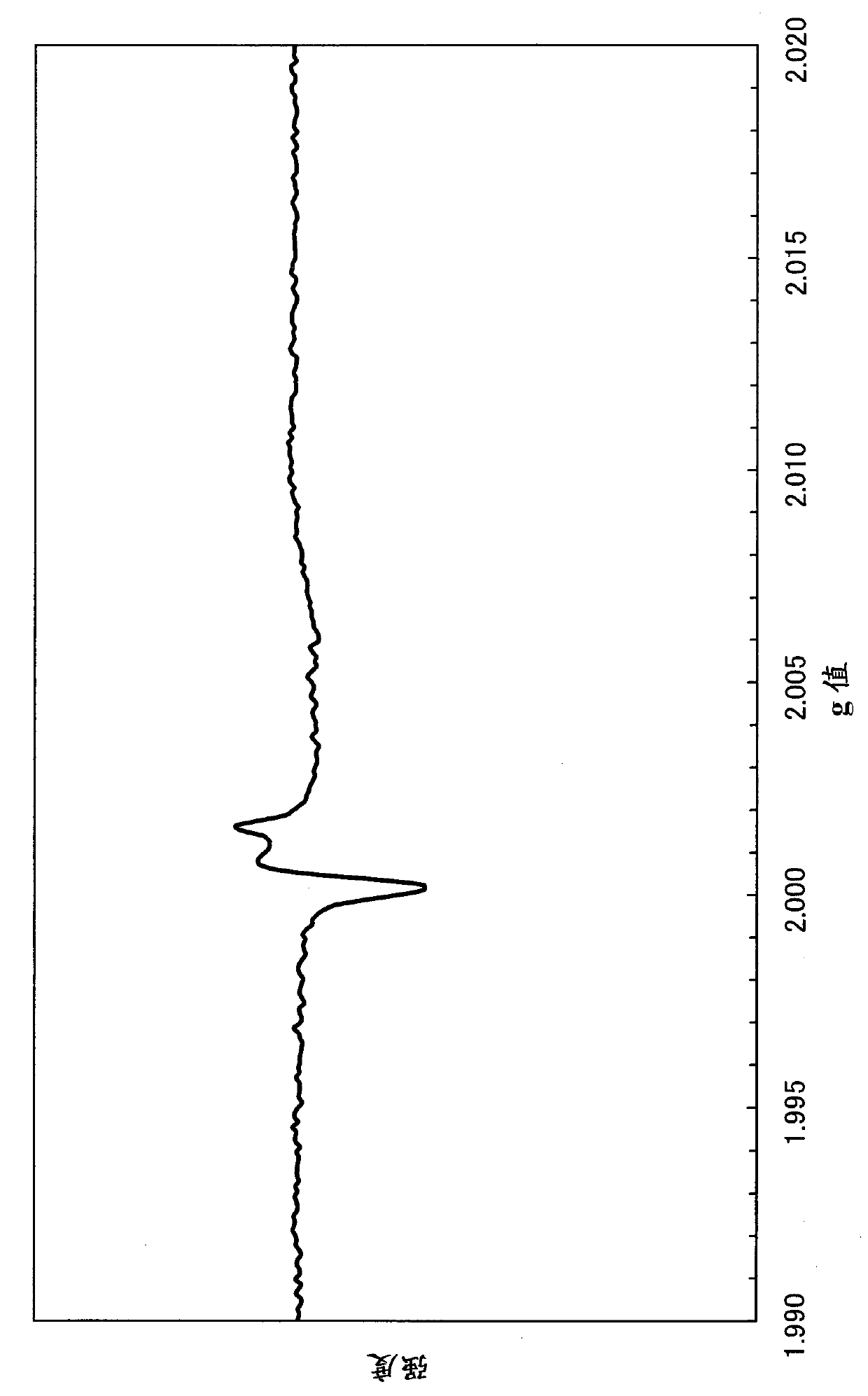

InactiveCN101452961AReduce cut-off currentExcellent electrical propertiesTransistorSolid-state devicesDisplay deviceHigh field

A thin film transistor having excellent electric characteristics, a display device including the thin film transistor, and a manufacturing method thereof are provided. In a thin film transistor in which a microcrystalline germanium film, a gate insulating film in contact with one surface of the microcrystalline germanium film, and a gate electrode overlap with one another and a display device including the thin film transistor, a buffer layer is formed over the other surface of the microcrystalline germanium film. By using a microcrystalline germanium film for a channel formation region, a thin film transistor with high field-effect mobility and high on-current can be manufactured, and by providing a buffer layer between the microcrystalline germanium film functioning as a channel formation region and a source and drain regions, a thin film transistor with low off-current can be manufactured, that is, a thin film transistor with excellent electric characteristics can be manufactured.

Owner:SEMICON ENERGY LAB CO LTD

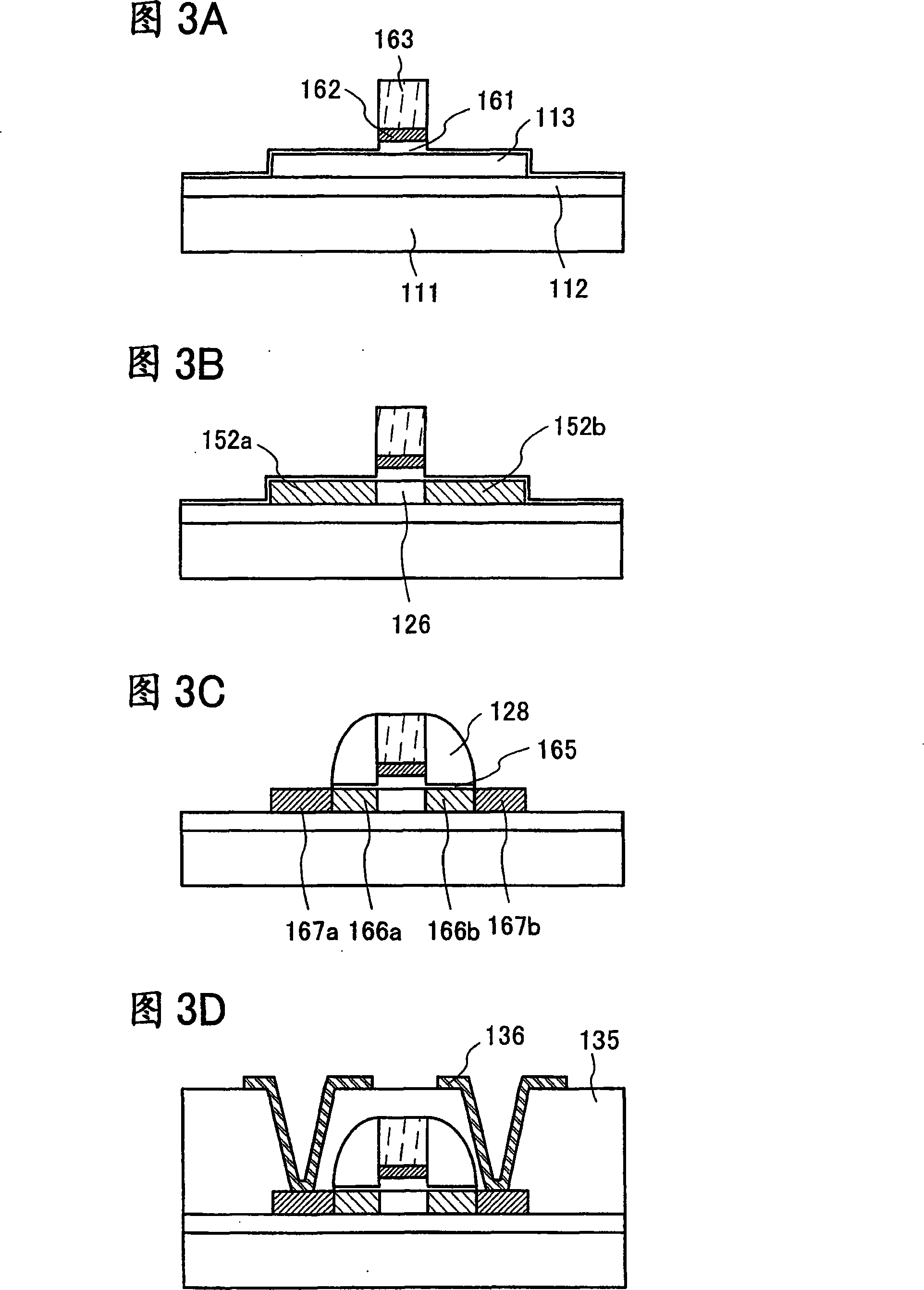

Thin film transistor and display panel

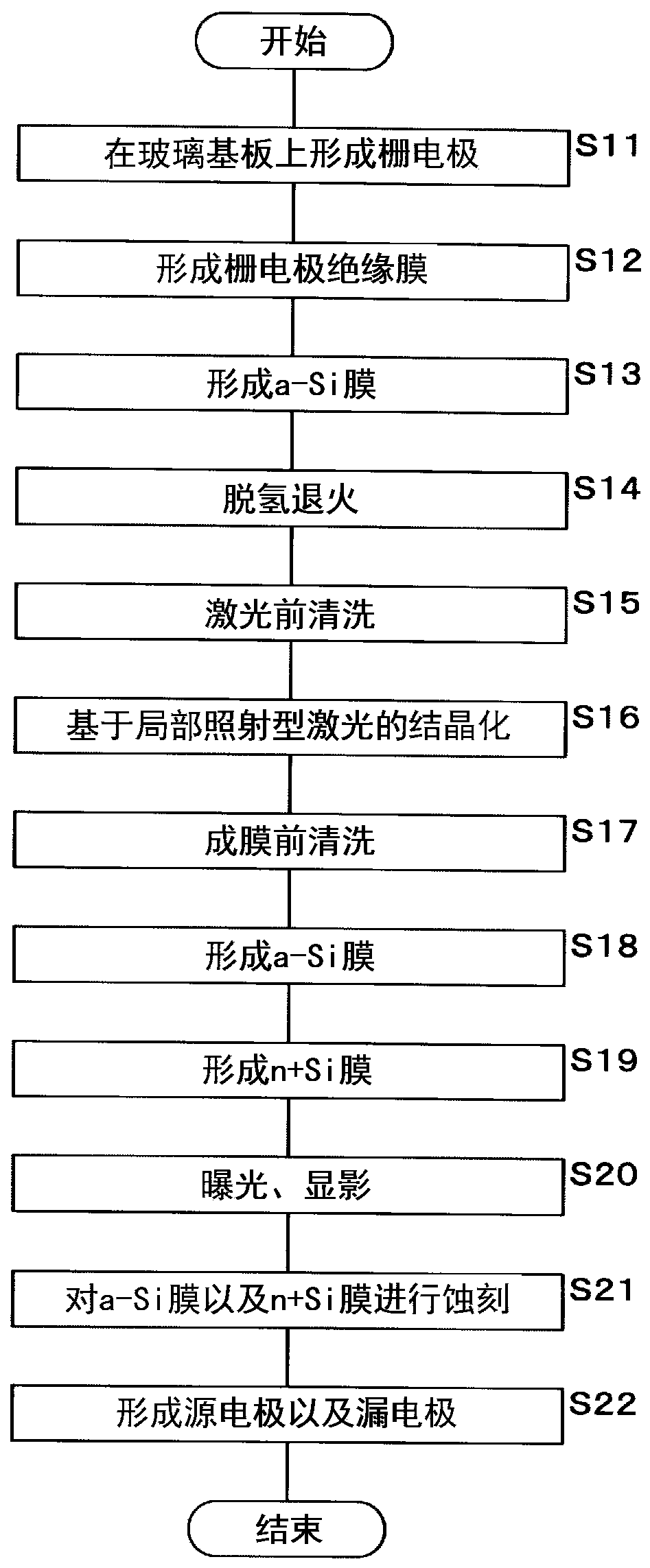

InactiveCN107408578AReduce cut-off currentTransistorSemiconductor/solid-state device manufacturingPolycrystalline siliconOxide thin-film transistor

Provided are a thin film transistor wherein an off current is reduced, and a display panel that is provided with the thin film transistor. This thin film transistor is provided with: a gate electrode formed on a surface of a substrate; a first amorphous silicon layer formed on the upper side of the gate electrode; a plurality of polysilicon layers, which are separated from each other by having the first amorphous silicon layer among the layers, and which are formed on the upper side of the gate electrode by being separated from the gate electrode by a distance needed; a second amorphous silicon layer and an n+ silicon layer, which are formed on the upper side of the polysilicon layers and the first amorphous silicon layer; and a source electrode and a drain electrode, which are formed on the n+ silicon layer.

Owner:SAKAI DISPLAY PROD

Thin film transistor

InactiveCN102077331AIncrease the on-currentReduce cut-off currentTransistorSolid-state devicesNitrogenSemiconductor

Owner:SEMICON ENERGY LAB CO LTD

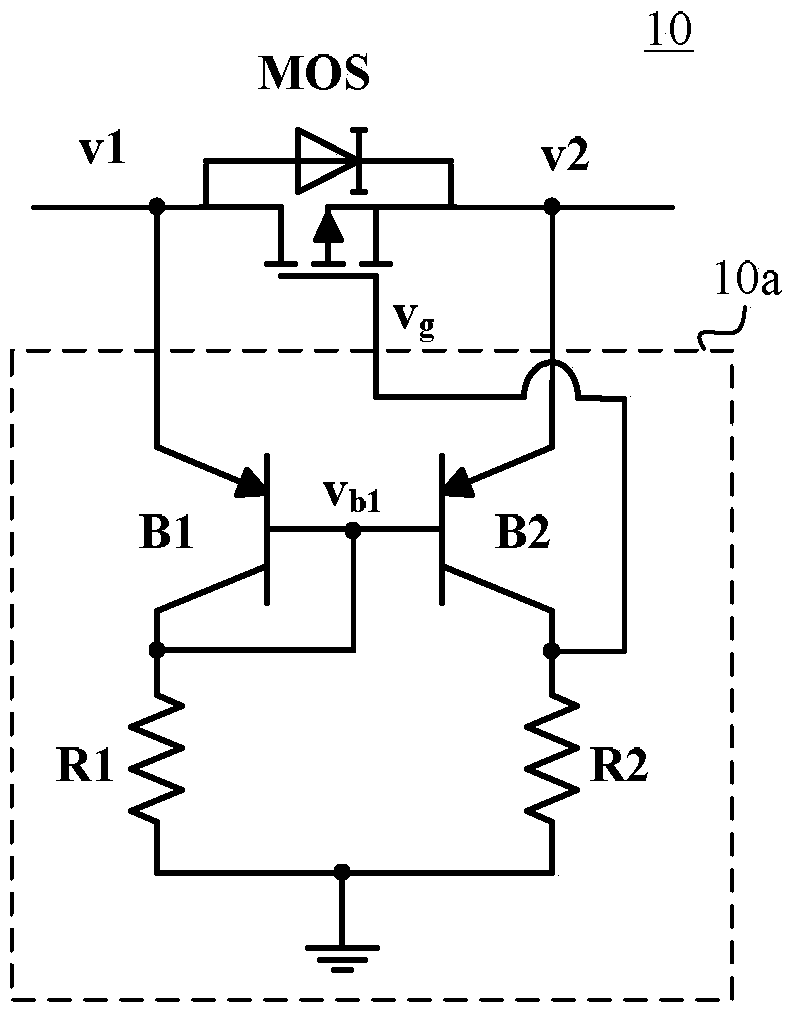

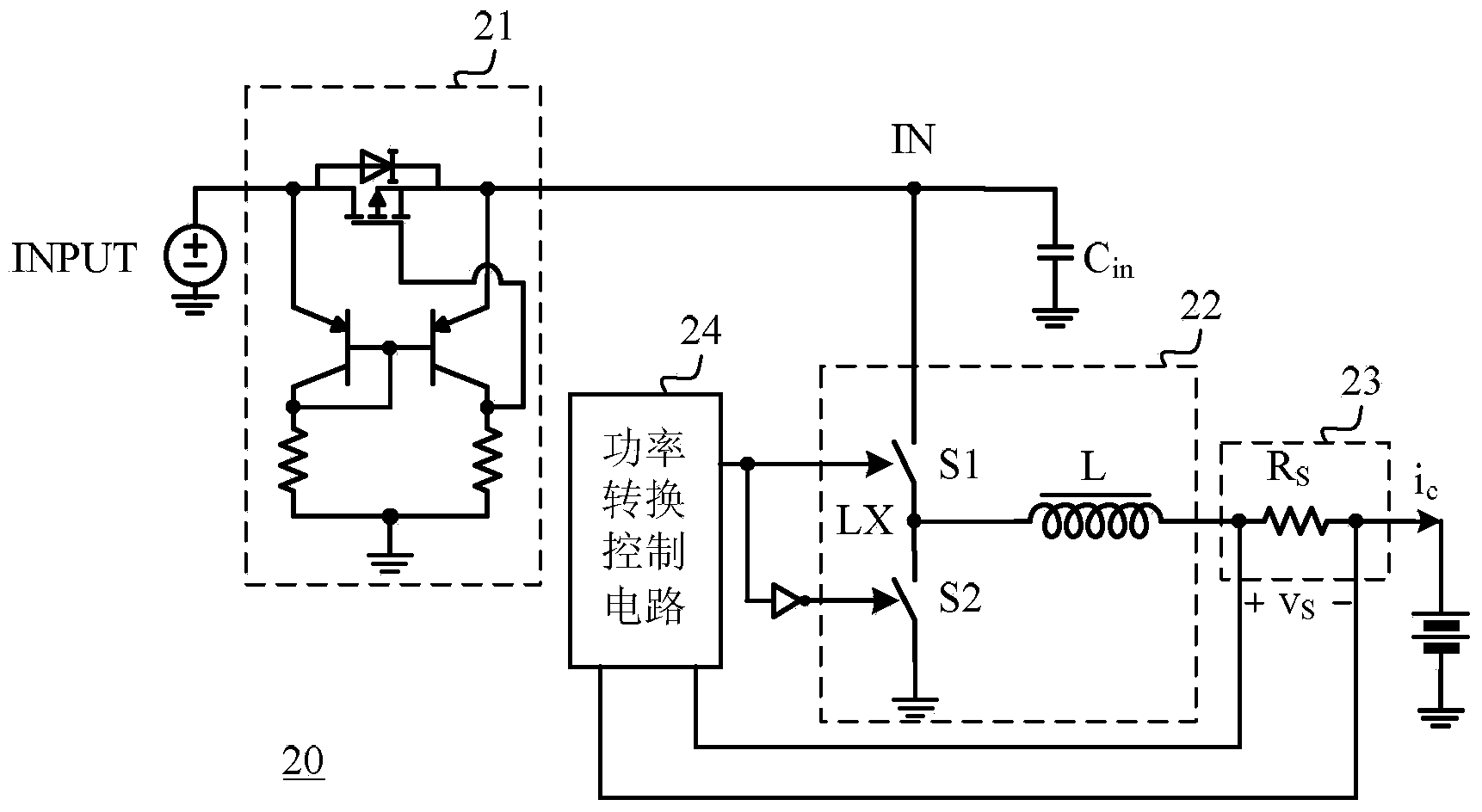

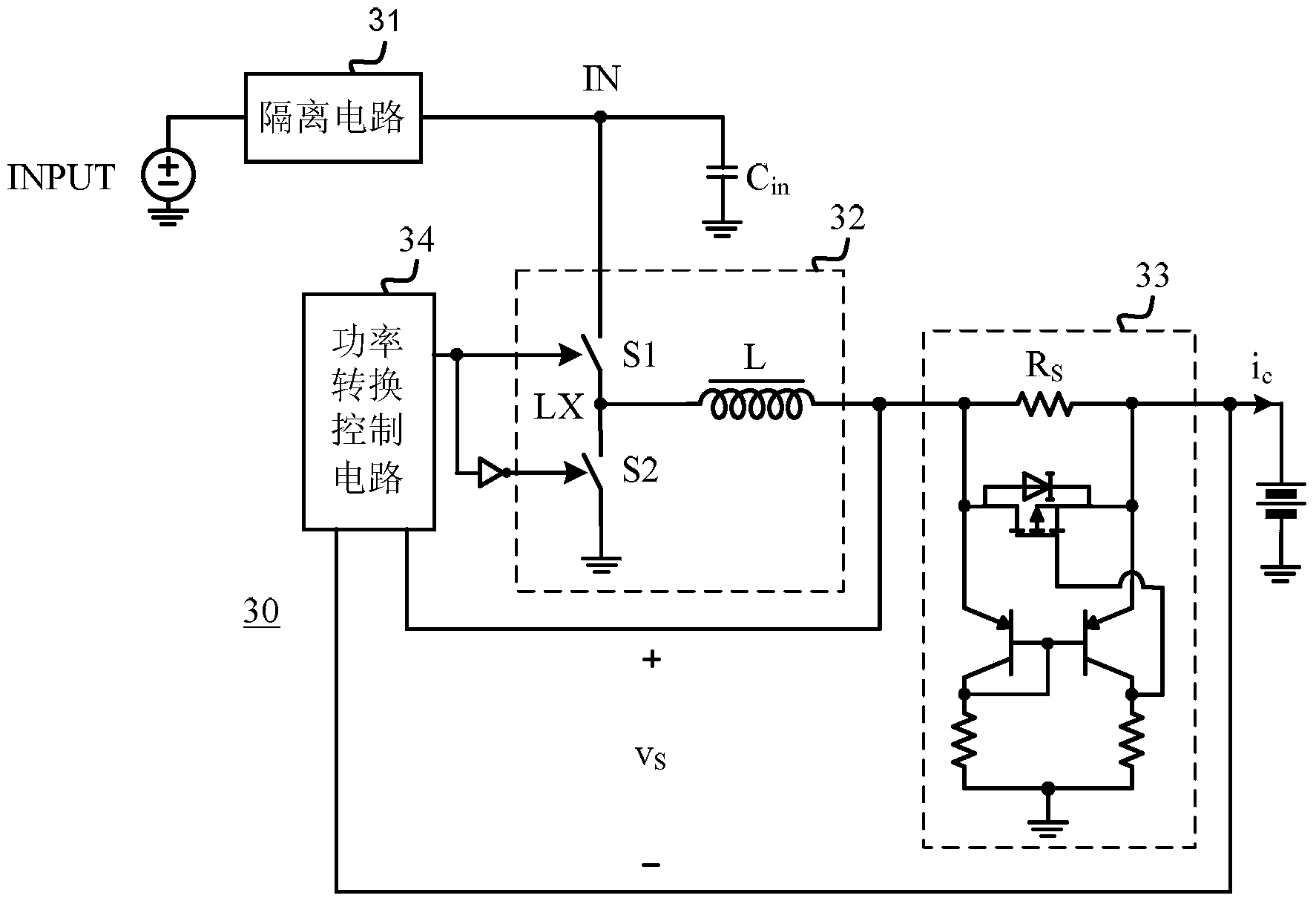

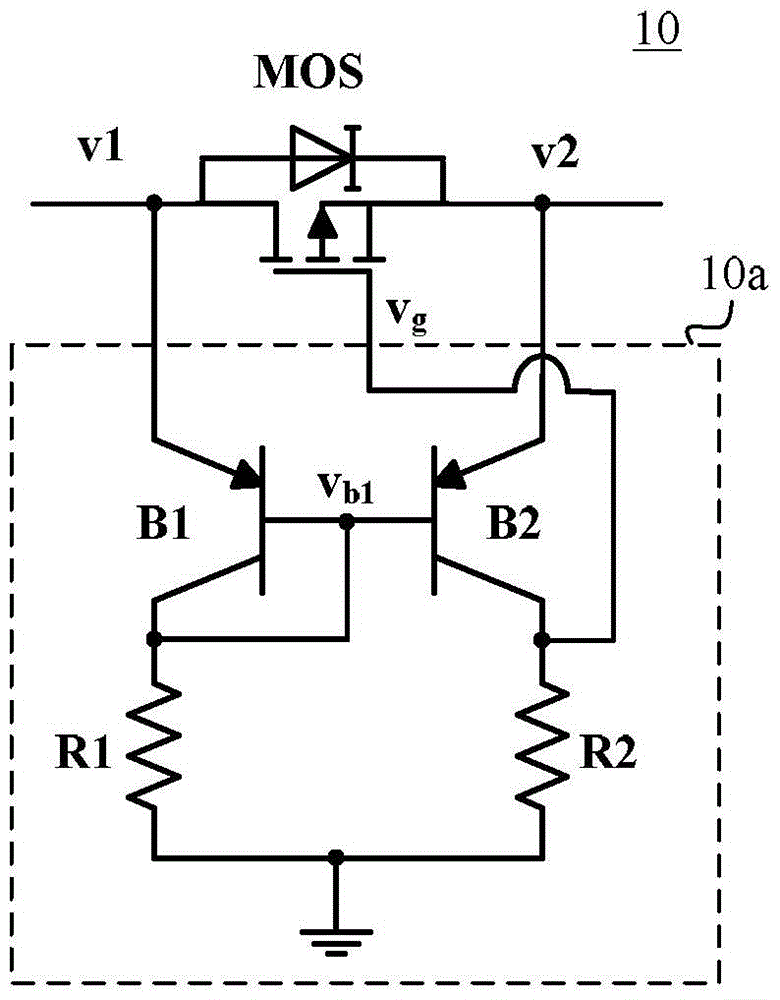

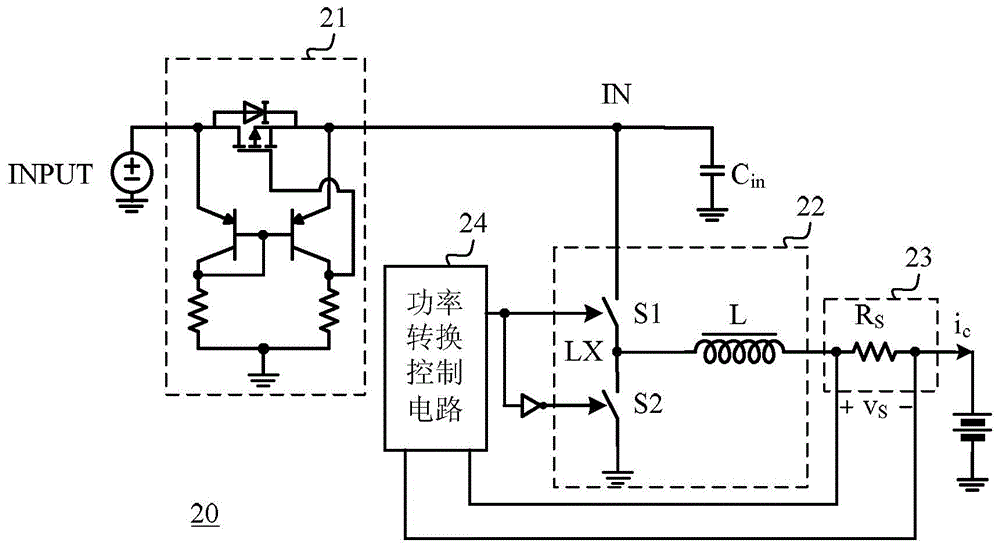

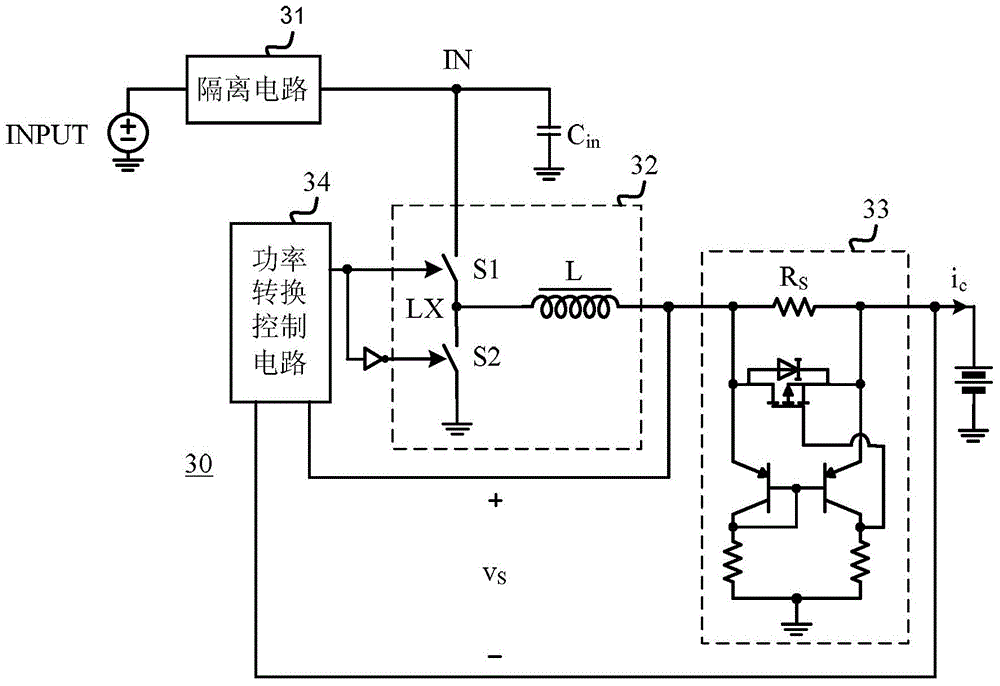

Synchronous rectifying circuit and charging circuit comprising same

ActiveCN104104228ASimple structureReduce manufacturing costBatteries circuit arrangementsDc-dc conversionControl signalEngineering

Disclosed are a synchronous rectifying circuit and a charging circuit comprising the same. The synchronous rectifying circuit comprises a rectifying transistor and a synchronous rectifying control circuit, wherein the synchronous rectifying control circuit is used for generating synchronous rectifying control signals according to the voltage difference between the drain electrode and the source electrode of the rectifying transistor to control on and off of the rectifying transistor. The synchronous rectifying circuit is simple in structure, small in number of devices and low in cost. When applied to the charging circuit, the synchronous rectifying circuit can overcome the problem that a battery is difficult to be fully charged.

Owner:NANJING SILERGY SEMICON TECH CO LTD

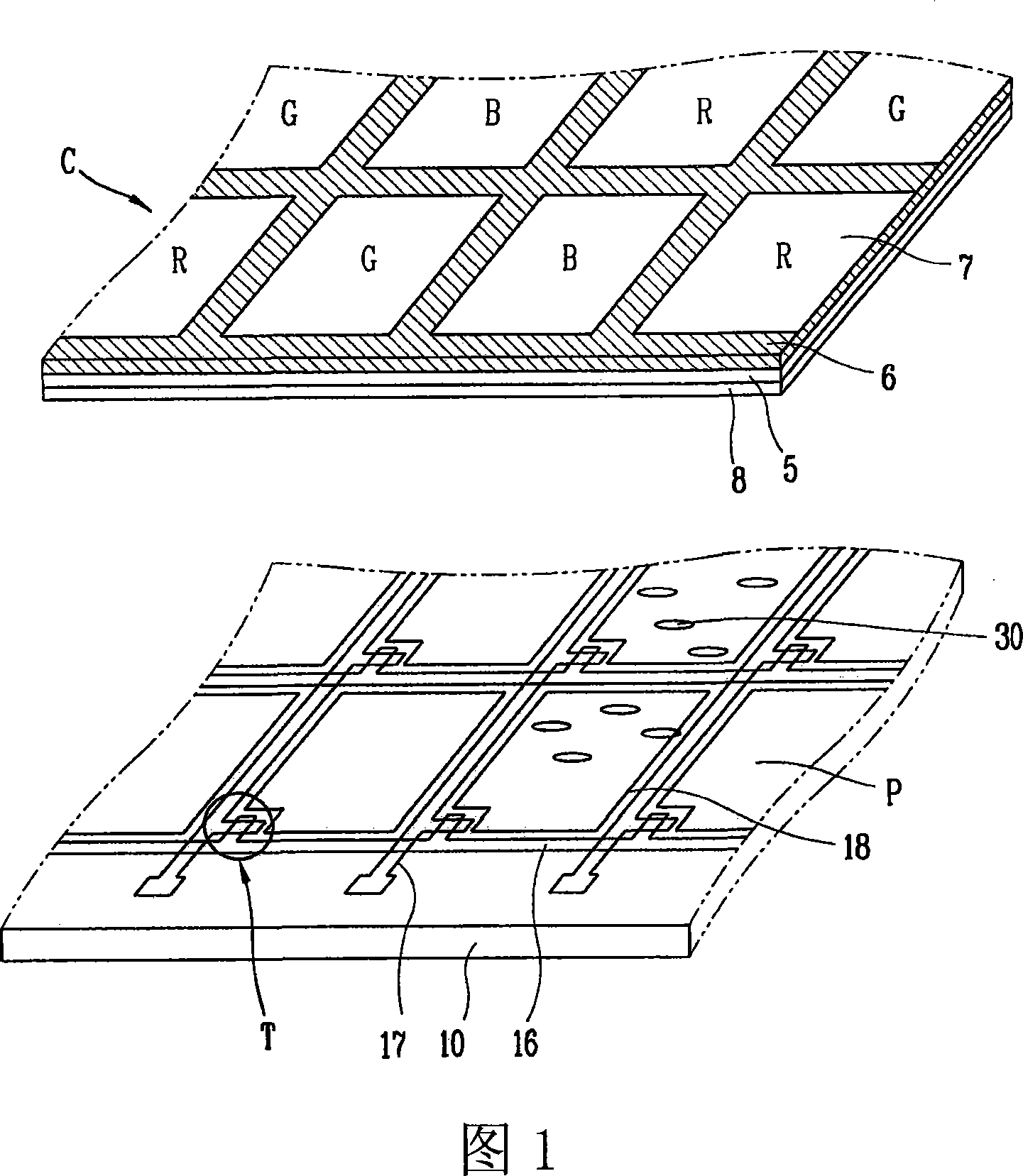

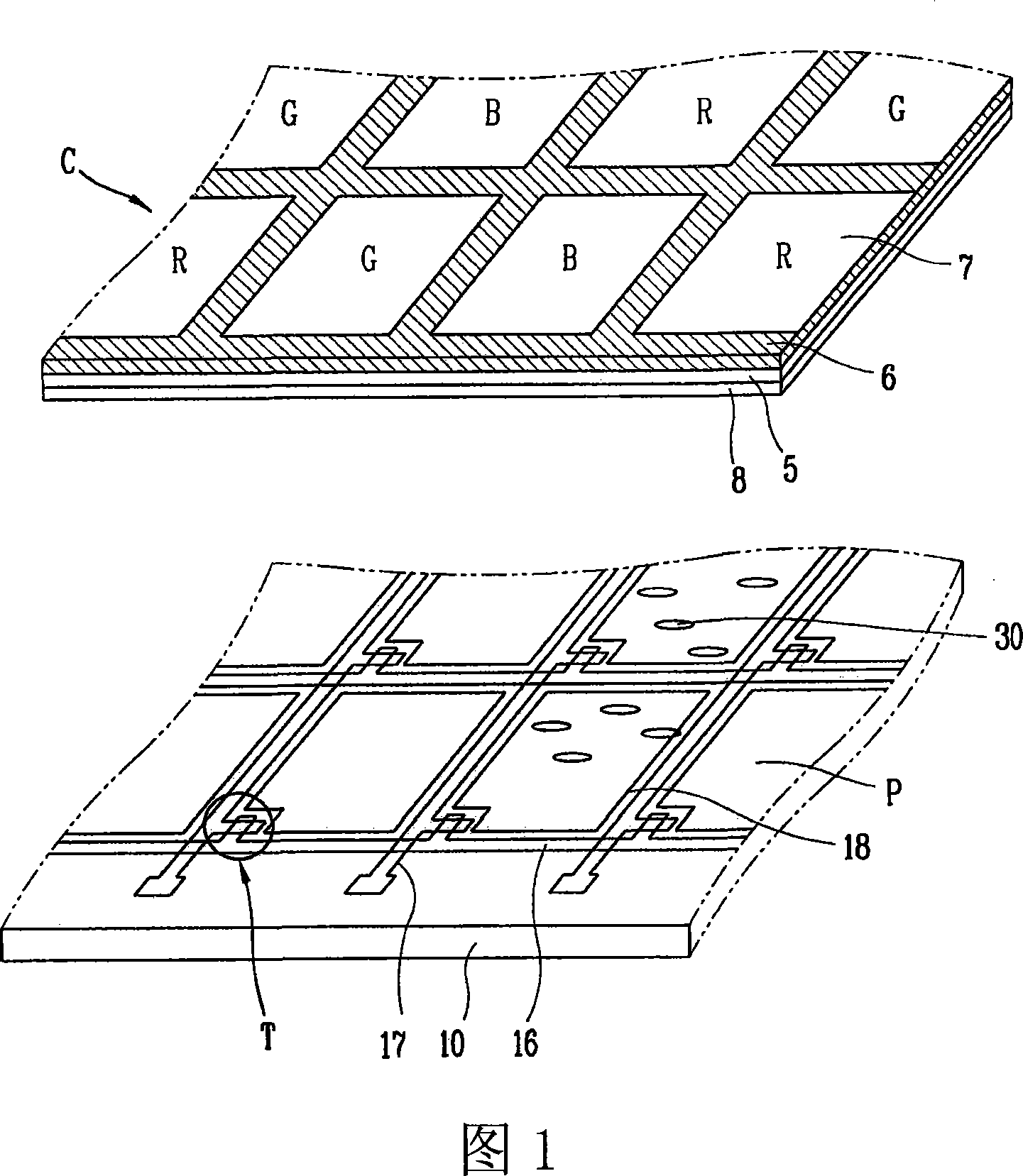

Liquid crystal display device and manufacturing method thereof

InactiveCN101207092AImprove reliabilityReduce cut-off currentSemiconductor/solid-state device detailsSolid-state devicesLiquid-crystal displayActive electrode

The invention discloses a LCD device, comprising a first substrate divided into a pixel part, a first and a second pad part; a gate and a gate line formed in the pixel part of the first substrate; an active pattern formed on the gate in an island shape and provided with a width smaller than that of the gate; an insulation film formed on the first substrate and provided with a first and a second contact hole respectively exposed with the active electrode region and the drain electrode region of the active pattern; an active electrode and a drain electrode, formed in the pixel part of the first substrate and electrically connected with the active electrode region and the drain electrode region of the active pattern through the first and the second contact hole; a data line formed in the pixel part of the first substrate and crossed with the gate line so as to limit the pixel region; an etching barrier structure positioned between the active electrode and the drain electrode and formed as the insulation film; a pixel electrode electrically connected with the pixel electrode; and a second substrate adhered with the first substrate in a face to face mode, the second substrate is a filter substrate.

Owner:LG DISPLAY CO LTD

Perovskite photoelectric detector and preparation method thereof

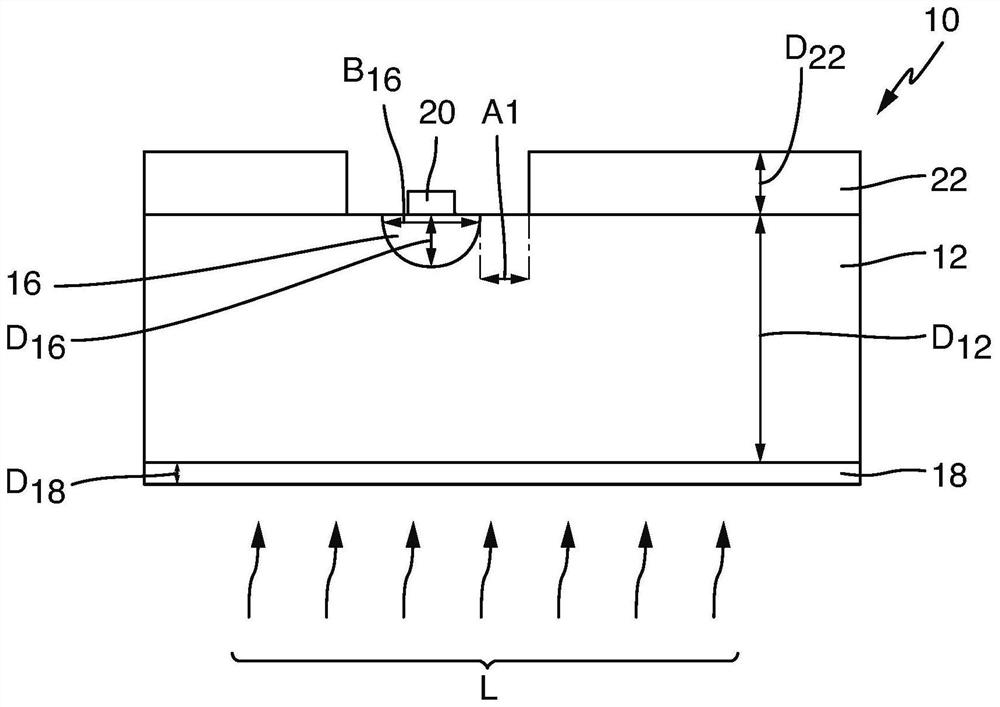

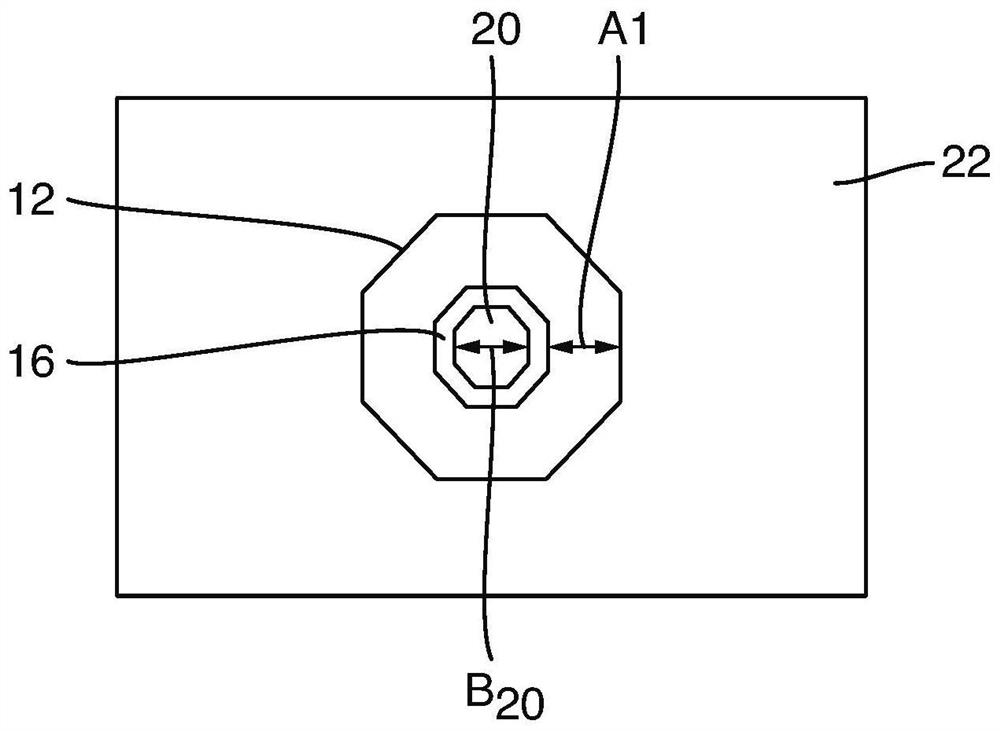

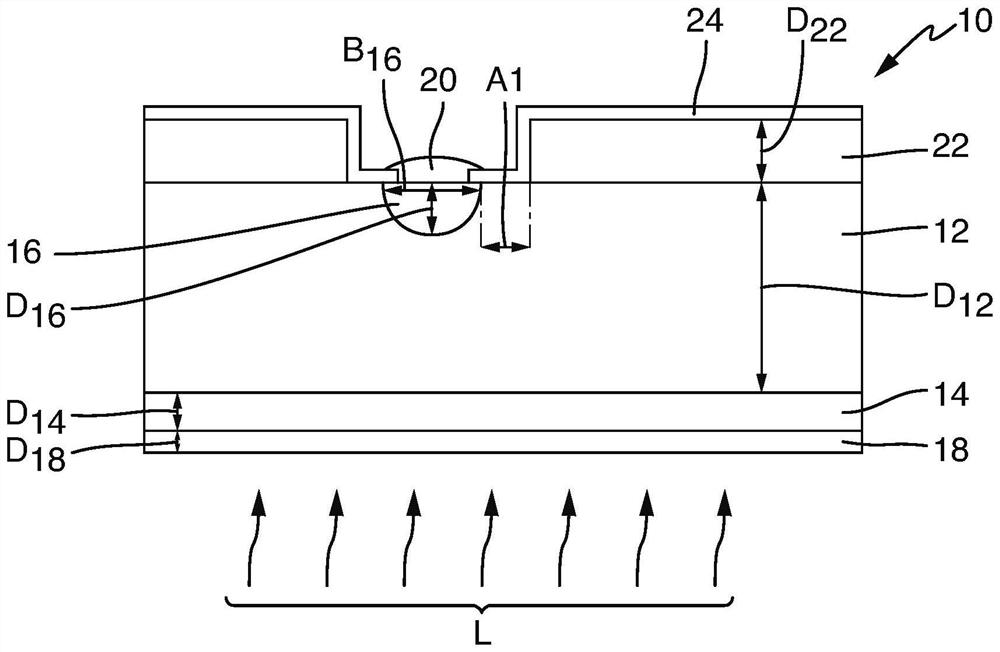

InactiveCN112201673ASolve the problem of high noise currentIncrease power consumptionTransistorSolid-state devicesPhotovoltaic detectorsMaterials science

The embodiment of the invention provides a perovskite photoelectric detector, which is characterized in that the detector comprises a double-gate metal oxide thin film transistor and a perovskite photodiode, the double-gate metal oxide thin film transistor is provided with a gate, the perovskite photodiode is provided with an electrode, and the grid electrode of the double-grid metal oxide thin film transistor is connected with the electrode of the perovskite photodiode. The detector provided by the invention combines the advantages of a double-gate metal oxide thin film transistor and a perovskite material, and greatly improves the performance of an optical detector in the aspect of weak light detection.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

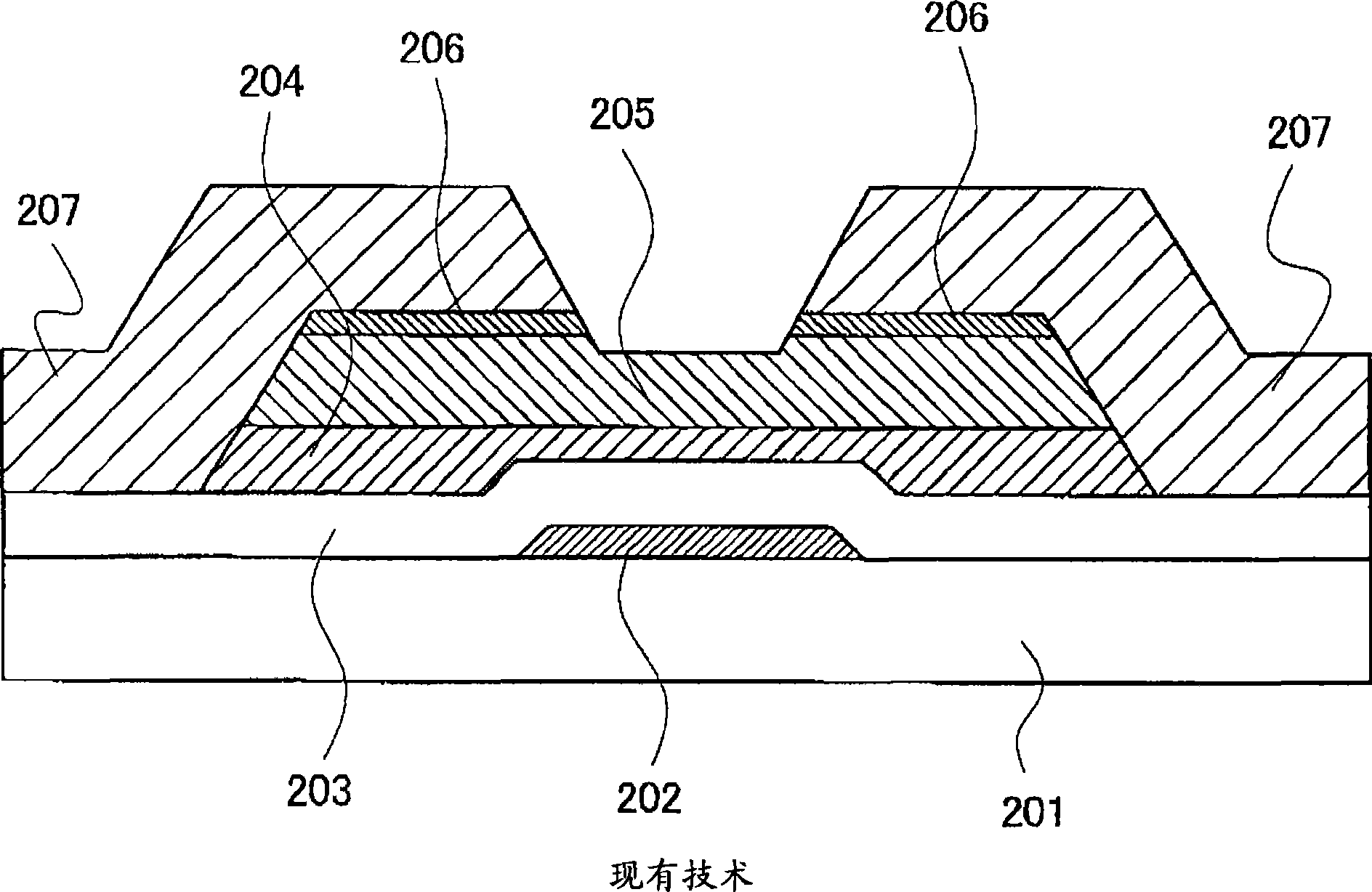

Semiconductor device and its production method

InactiveCN1881568AImprove mobilityReduce cut-off currentTransistorSolid-state devicesActive matrixImpurity

Nickel is introduced to a predetermined region of a peripheral circuit section, other than a picture element section, on an amorphous silicon film to crystallize from that region. After forming gate electrodes and others, sources, drains and channels are formed by doping impurities, and laser is irradiated to improve the crystallization. After that, electrodes / wires are formed. Thereby an active matrix type liquid crystal display whose thin film transistors (TFT) in the peripheral circuit section are composed of the crystalline silicon film whose crystal is grown in the direction parallel to the flow of carriers and whose TFTs in the picture element section are composed of the amorphous silicon film can be obtained.

Owner:SEMICON ENERGY LAB CO LTD

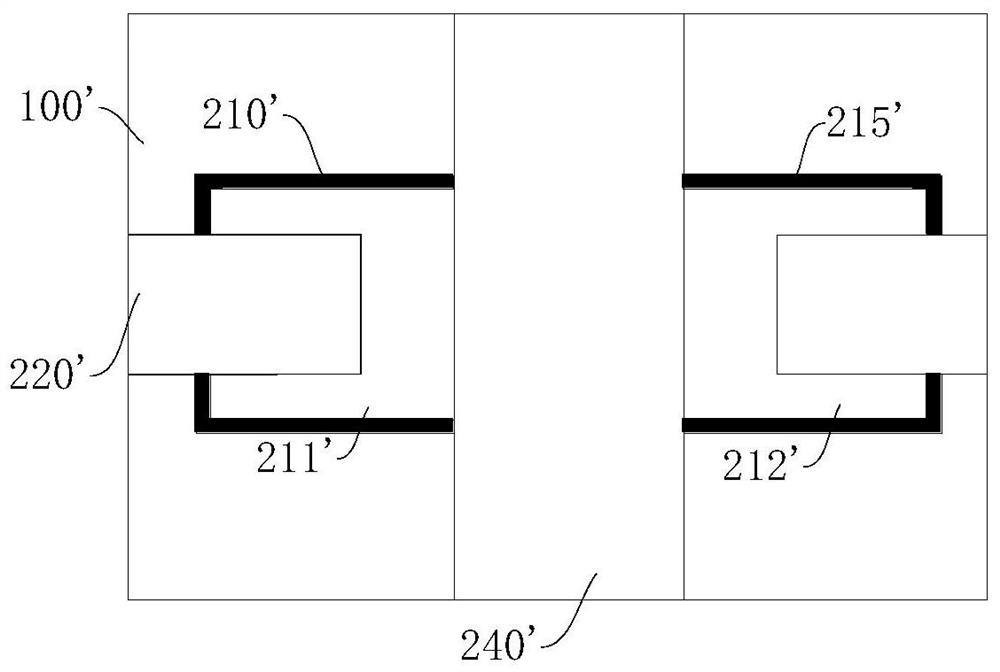

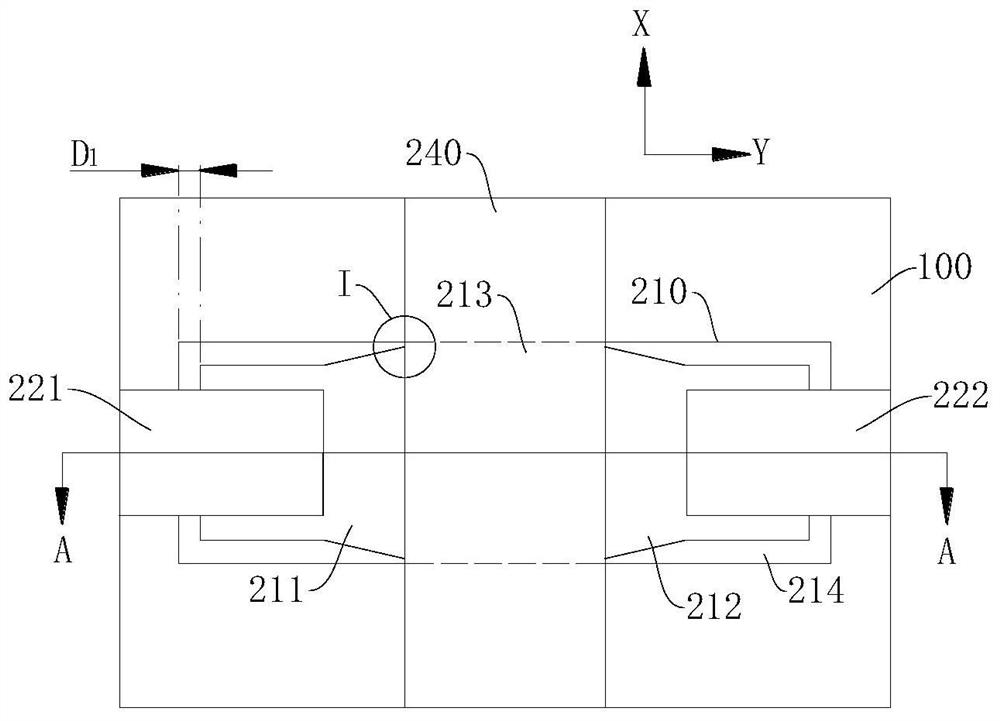

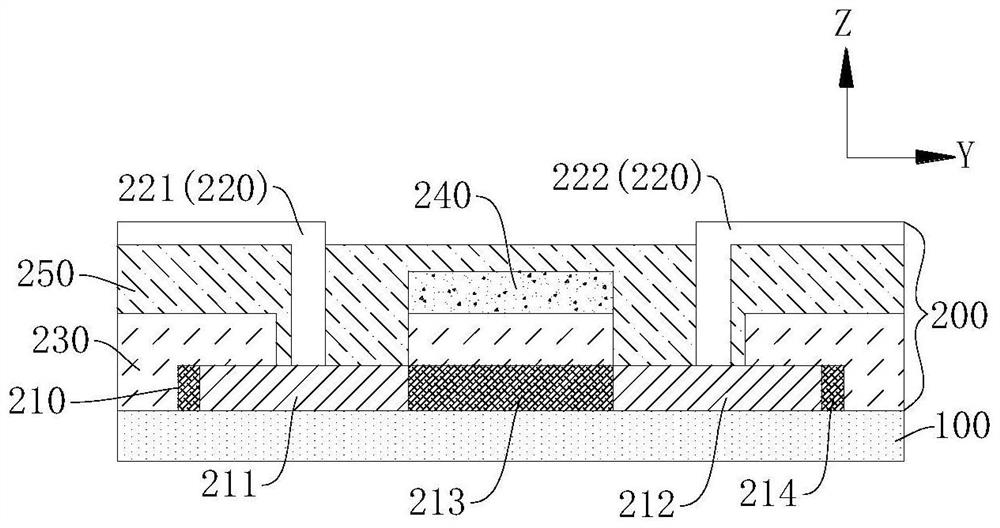

Array substrate, manufacturing method of array substrate and display device

ActiveCN112349733AReduce cut-off currentLarge flowSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceThin membrane

The embodiment of the invention provides an array substrate, a manufacturing method of the array substrate and a display device. The array substrate comprises a substrate and a plurality of thin filmtransistors located on one side of the substrate. The thin film transistor comprises an active structure which is arranged on one side of the substrate and comprises a first region and a second region, wherein the resistivity of the first region is smaller than that of the second region, the first region comprises a source region and a drain region, and the second region comprises a channel regionand an auxiliary region, the channel region being located between the source region and the drain region, and the auxiliary region surrounding at least part of the source region and / or the drain region; a source-drain electrode which comprises a source electrode and a drain electrode, wherein the source electrode is connected to the source region, and the drain electrode is connected to the drainregion; a first insulating layer arranged on one side of the active structure; and a grid electrode arranged on the side, deviating from the active structure, of the first insulating layer, wherein the orthographic projection of the grid electrode on the substrate covers the orthographic projection of at least part of the channel region on the substrate. The cut-off current of the thin film transistor can be reduced.

Owner:HUBEI YANGTZE IND INNOVAION CENT OF ADVANCED DISPLAY CO LTD

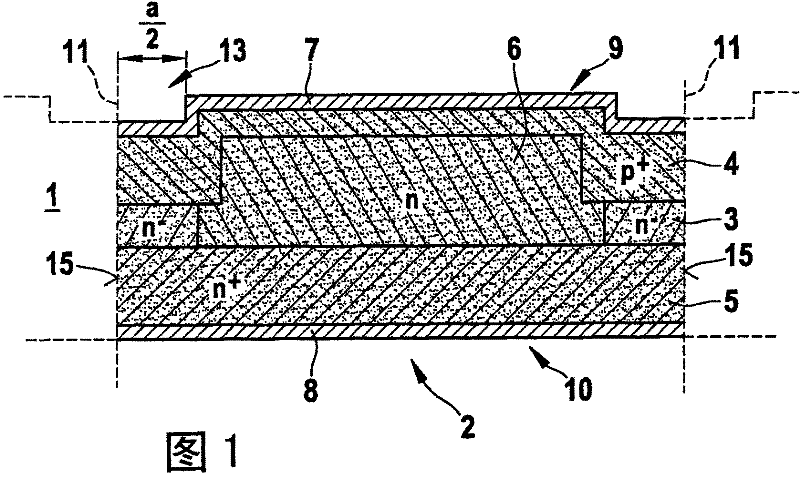

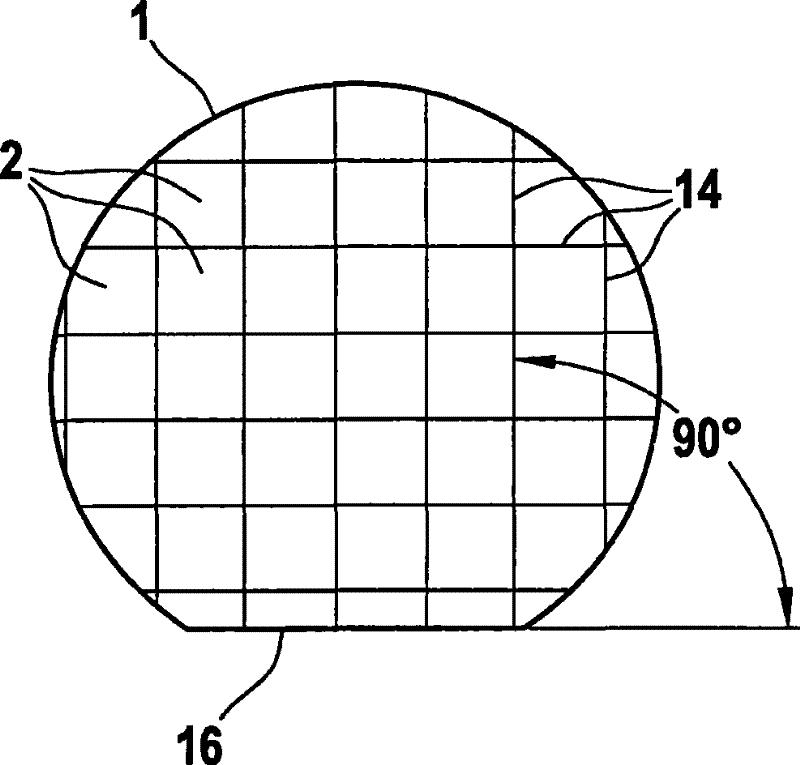

Method for manufacturing semiconductor chips from wafers

ActiveCN101095222BReduce cut-off currentReduce process stepsSemiconductor/solid-state device manufacturingSemiconductor devicesCrystal structureSemiconductor chip

The invention relates to a method for producing semiconductor chips (2) from a wafer (1) containing a plurality of semiconductor chips (2). When given breaks (14) are produced on the wafer surface after the wafer (1) is completed, and the wafer (1) is broken along these given breaks (14) to separate the semiconductor chips (2), it is possible Defects in the crystal structure of the chip (2) are significantly reduced.

Owner:ROBERT BOSCH GMBH

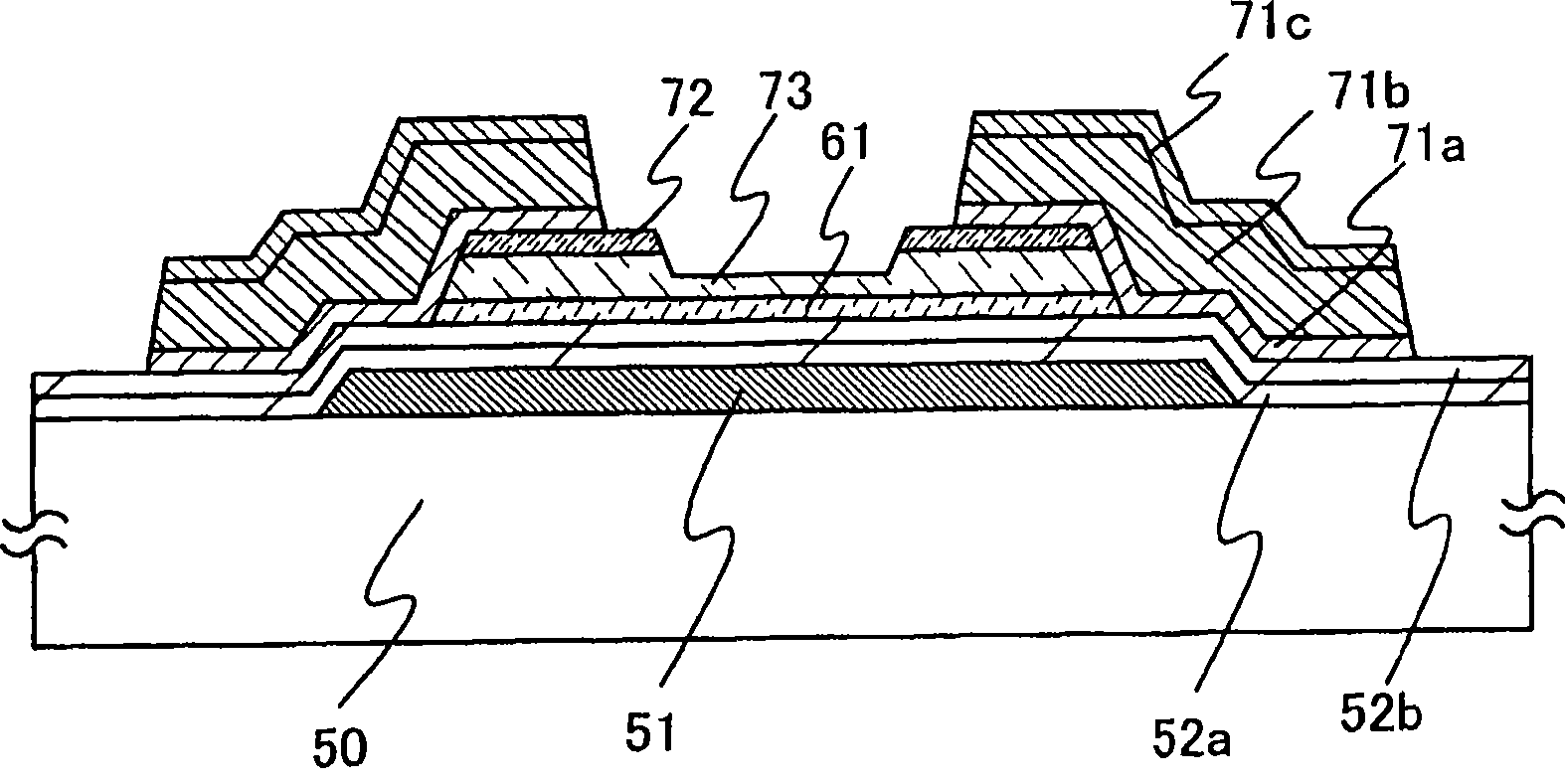

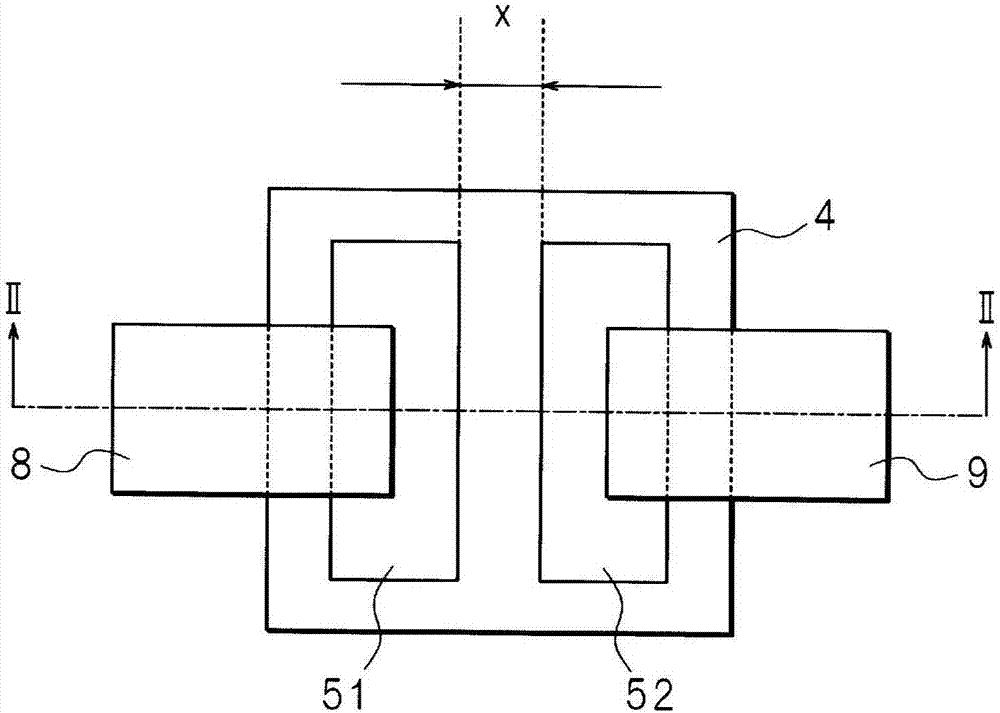

Thin film transistor and method for fabricating the same

ActiveCN103367456AImprove featuresHigh electron mobilityTransistorSolid-state devicesTransistorElectrical and Electronics engineering

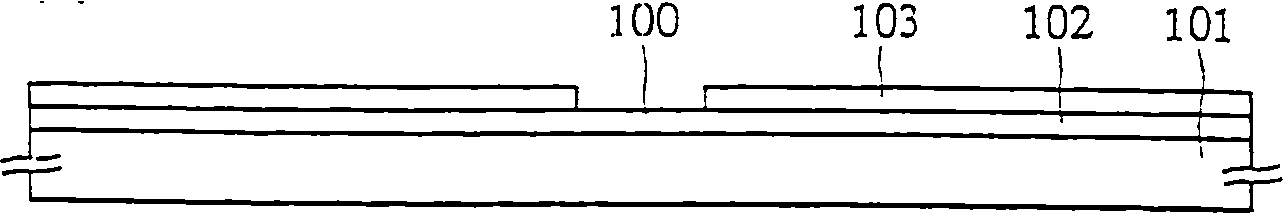

A thin film transistor and a method for fabricating the same are disclosed. The thin film transistor includes: a gate electrode formed on a substrate and having a plurality of horizontal electrode parts spaced apart at regular intervals; a gate insulating film formed over the entire surface of the substrate including the gate electrode; an active pattern formed on the gate insulating film above the plurality of horizontal electrode parts; an etch stop film pattern formed above the active pattern and the gate insulating film so as to overlap top portions of the active pattern and the gate electrode and; a source electrode formed on the active pattern, the gate insulating film, and the etch stop film pattern so as to overlap top portions of adjacent horizontal electrode parts; and a drain electrode formed on the active pattern, the gate insulating film, and the etch stop film pattern so as to overlap top portions of horizontal electrode parts located on the outermost ends.

Owner:LG DISPLAY CO LTD

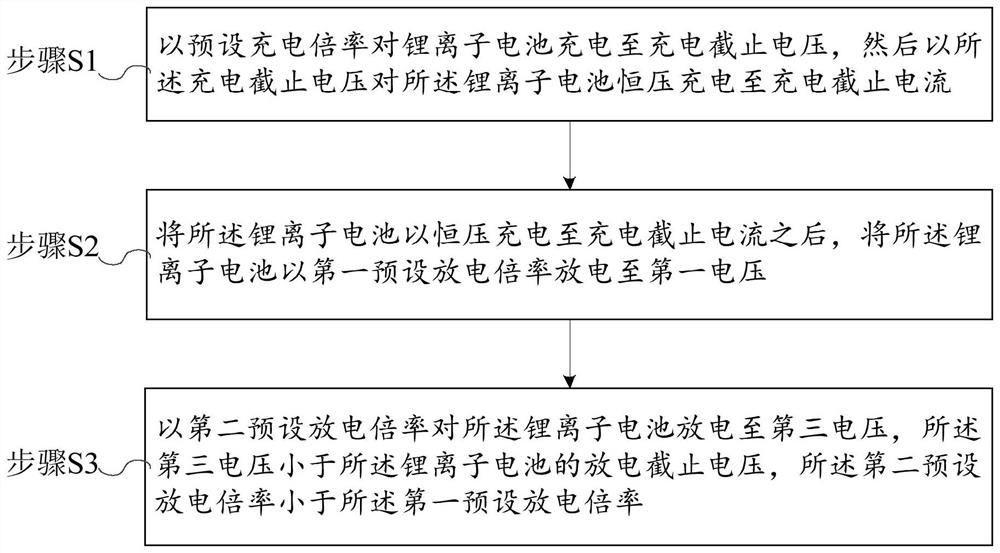

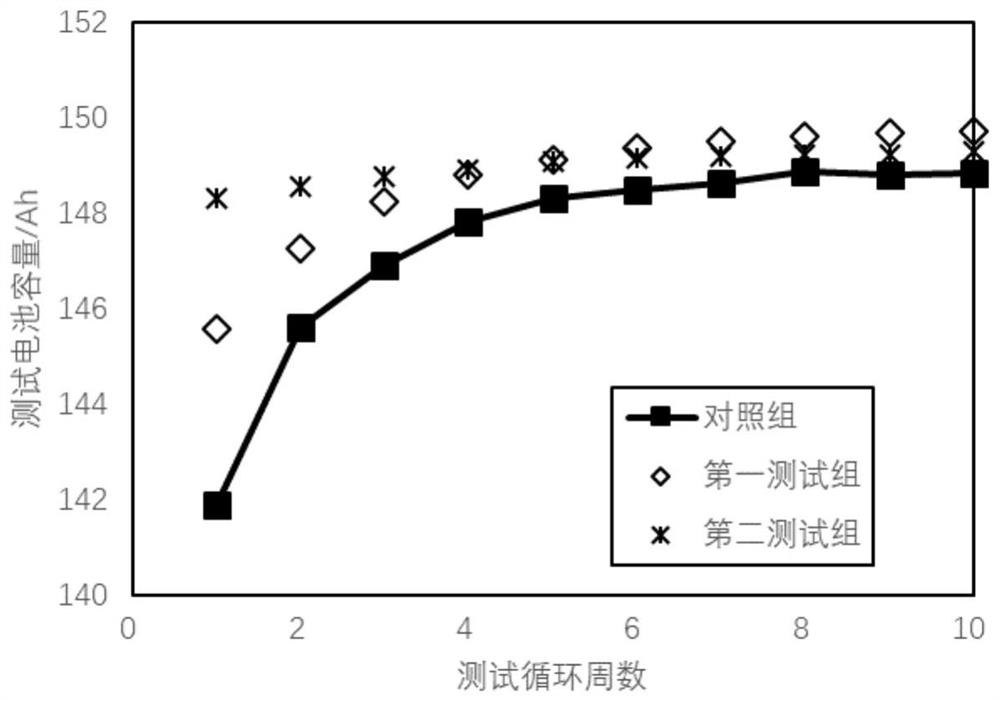

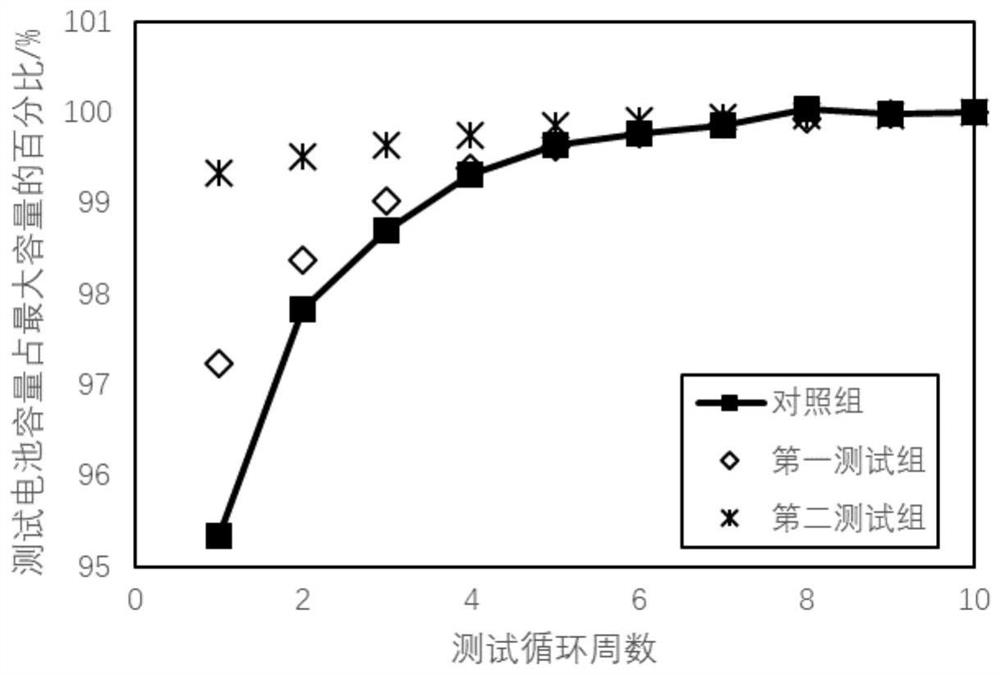

Capacity grading activation method of lithium ion battery

PendingCN114267893AImproved lithium diffusion propertiesIncreased capacity for the first week of testingSecondary cells charging/dischargingLithium electrodeElectrical and Electronics engineering

The invention provides a capacity grading activation method of a lithium ion battery. The capacity grading activation method of the lithium ion battery comprises the following steps: charging the lithium ion battery to a charging cut-off voltage at a preset charging rate, and then performing constant-voltage charging on the lithium ion battery to a charging cut-off current at the charging cut-off voltage; discharging the lithium ion battery to a first voltage at a first preset discharge rate; the lithium ion battery is discharged to a third voltage at a second preset discharge rate, the third voltage is smaller than the discharge cut-off voltage of the lithium ion battery, and the second preset discharge rate is smaller than the first preset discharge rate. According to the capacity grading activation method disclosed by the invention, the positive electrode active material can realize sufficient lithium removal and lithium insertion processes, and the lithium diffusion performance is improved by adjusting defects, so that the test first-cycle capacity of the lithium ion battery is improved.

Owner:SUNWODA ELECTRIC VEHICLE BATTERY CO LTD

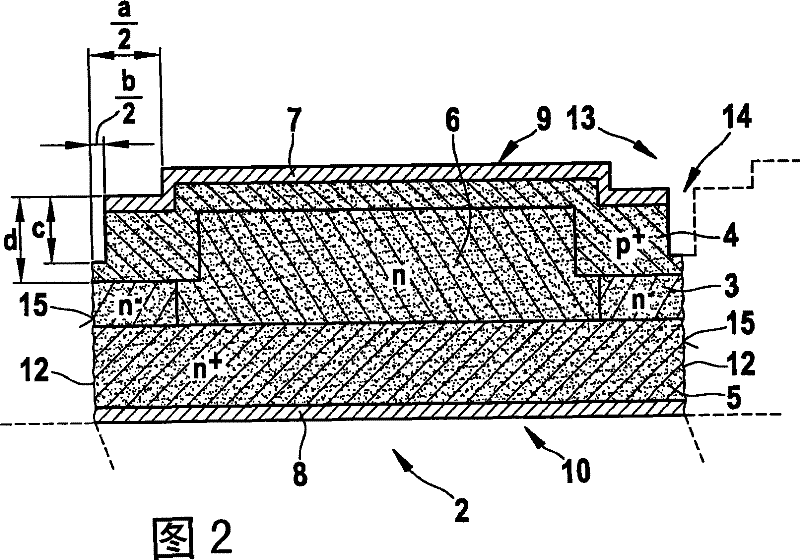

Stacked photonic iii-v semi-conductor device

ActiveCN113437167AIdeal change processReduce cut-off currentDiodePhotovoltaic energy generationDevice materialEngineering

A stacked photonic III-V semiconductor device has a second metallic connection contact layer at least formed in regions, a highly doped first semiconductor contact region of a first conductivity type, a very low doped absorption region of the first or second conductivity type having a layer thickness of 20 [mu]m-2000 [mu]m, a first metallic connection contact layer at least formed in regions, wherein the first semiconductor contact region extends into the absorption region in a trough shape, the second metallic connection contact layer is integrally bonded to the first semiconductor contact region and the first metallic connection contact layer is arranged below the absorption region. In addition, the stacked photonic III-V semiconductor device has a doped III-V semiconductor passivation layer of the first or second conductivity type, wherein the III-V semiconductor passivation layer is arranged at the upper side of the absorption region at a first distance of at least 10 [mu]m to the first semiconductor contact region.

Owner:AZUR SPACE SOLAR POWER

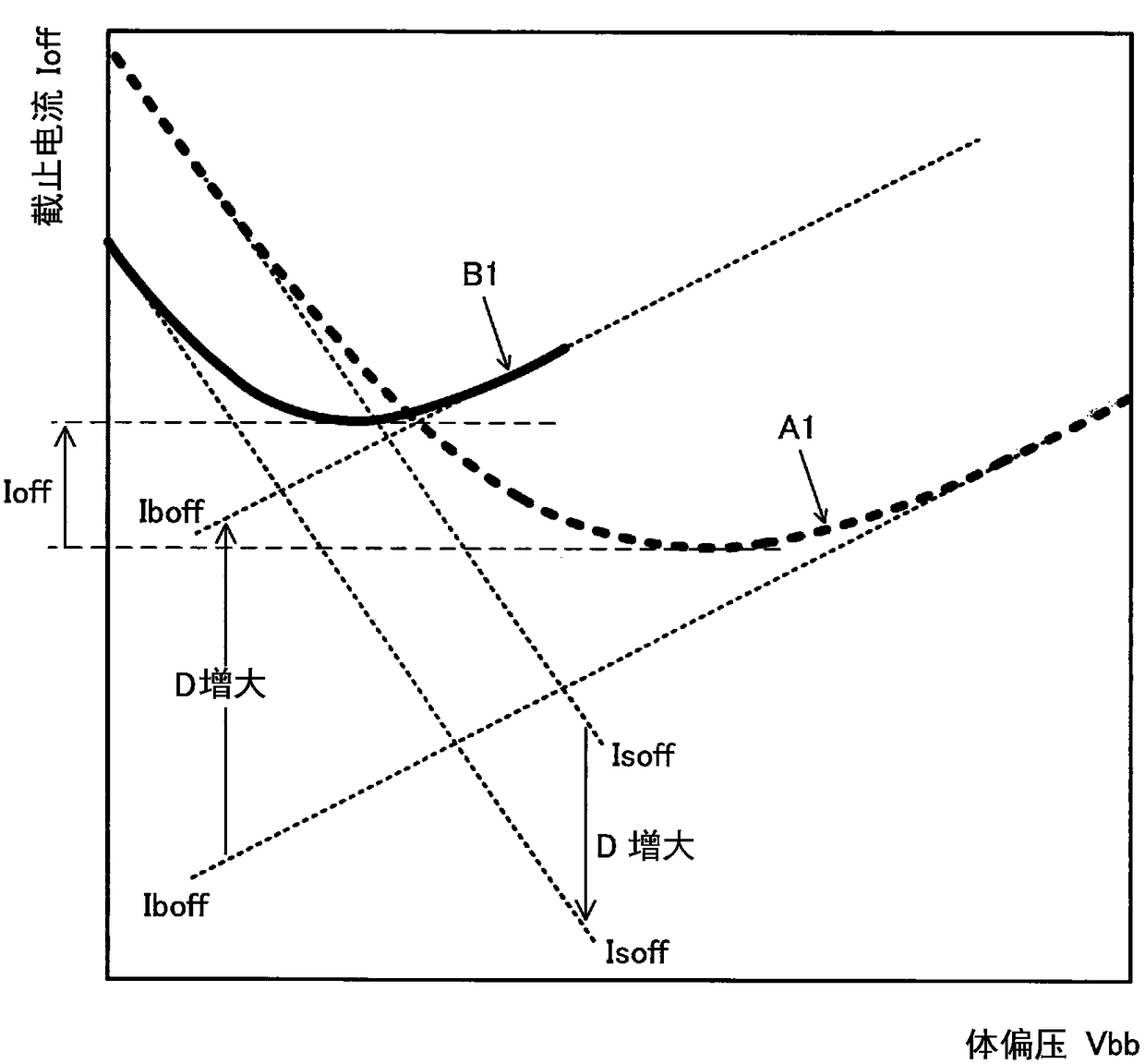

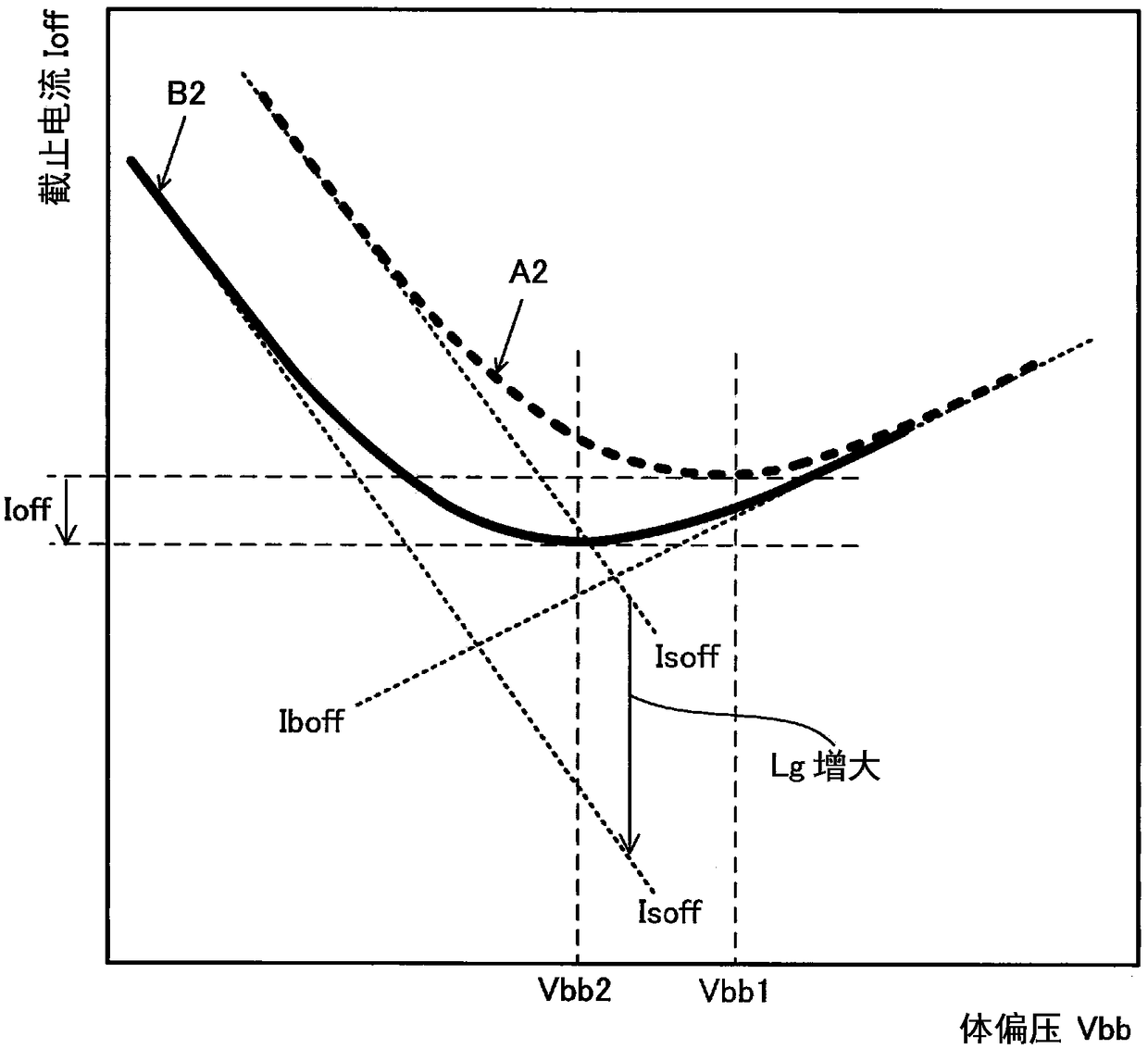

Semiconductor device

ActiveCN106024783AReduce cut-off currentTransistorSemiconductor/solid-state device manufacturingHigh concentrationImpurity

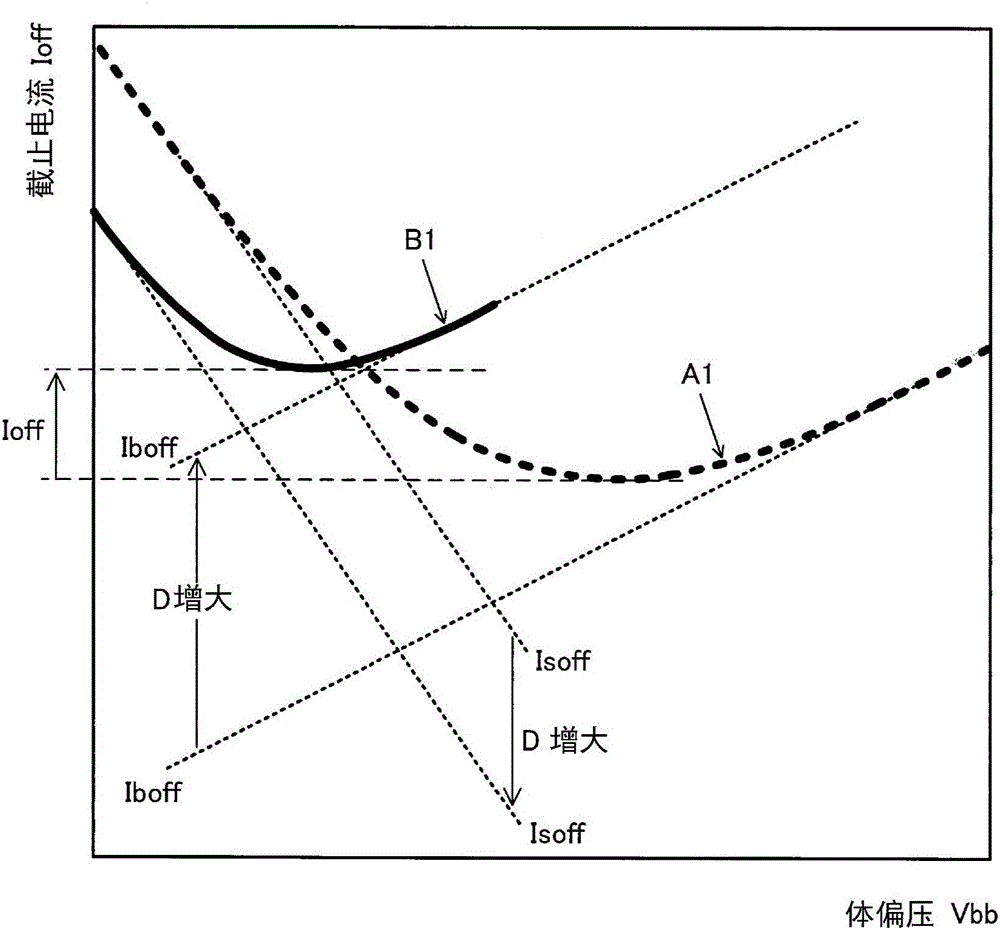

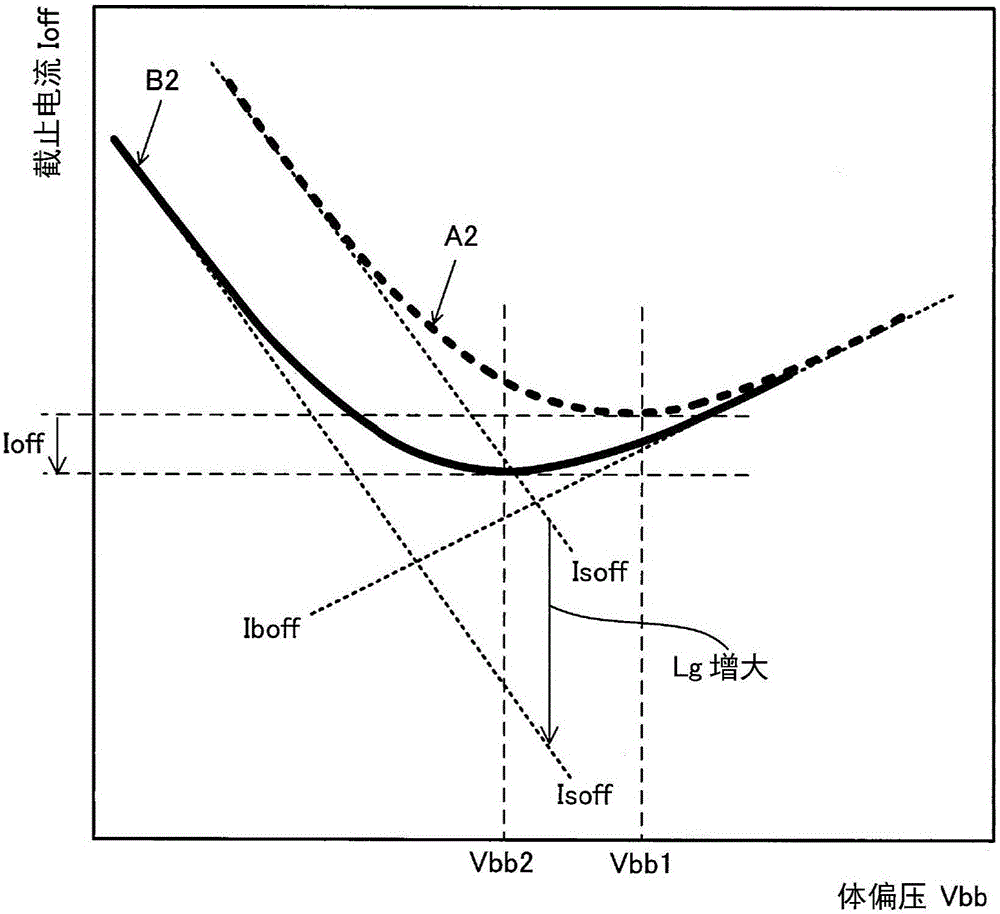

A semiconductor device includes first and second transistors connected to the same power supply. Each of the first and second transistors includes, under a channel region of a low concentration provided between a source region and a drain region of a first conductivity type, an impurity region of a second conductivity type having a higher concentration. The thickness of the gate insulating film in one of the first and second transistors is made larger than the thickness of the gate insulating film in the other one.

Owner:MIE FUJITSU SEMICON

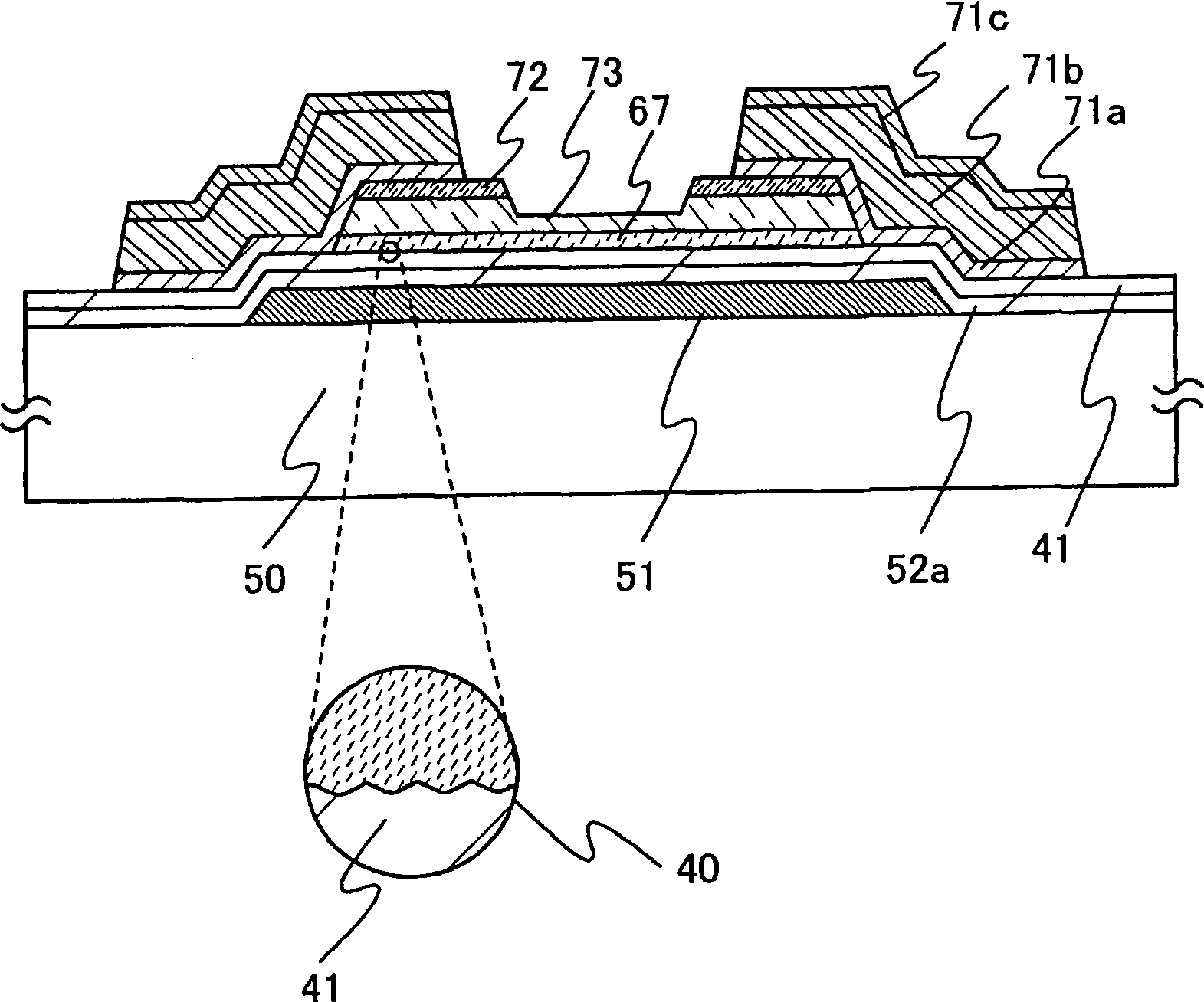

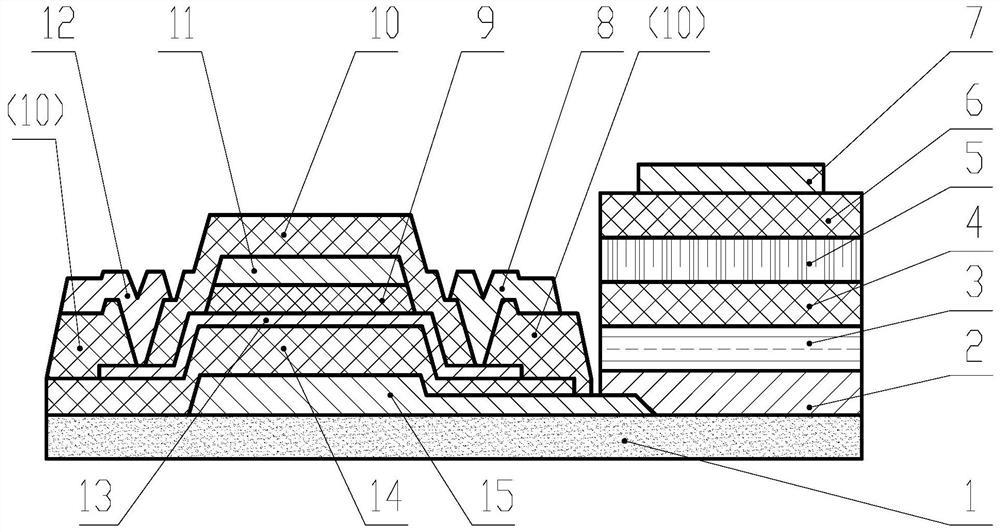

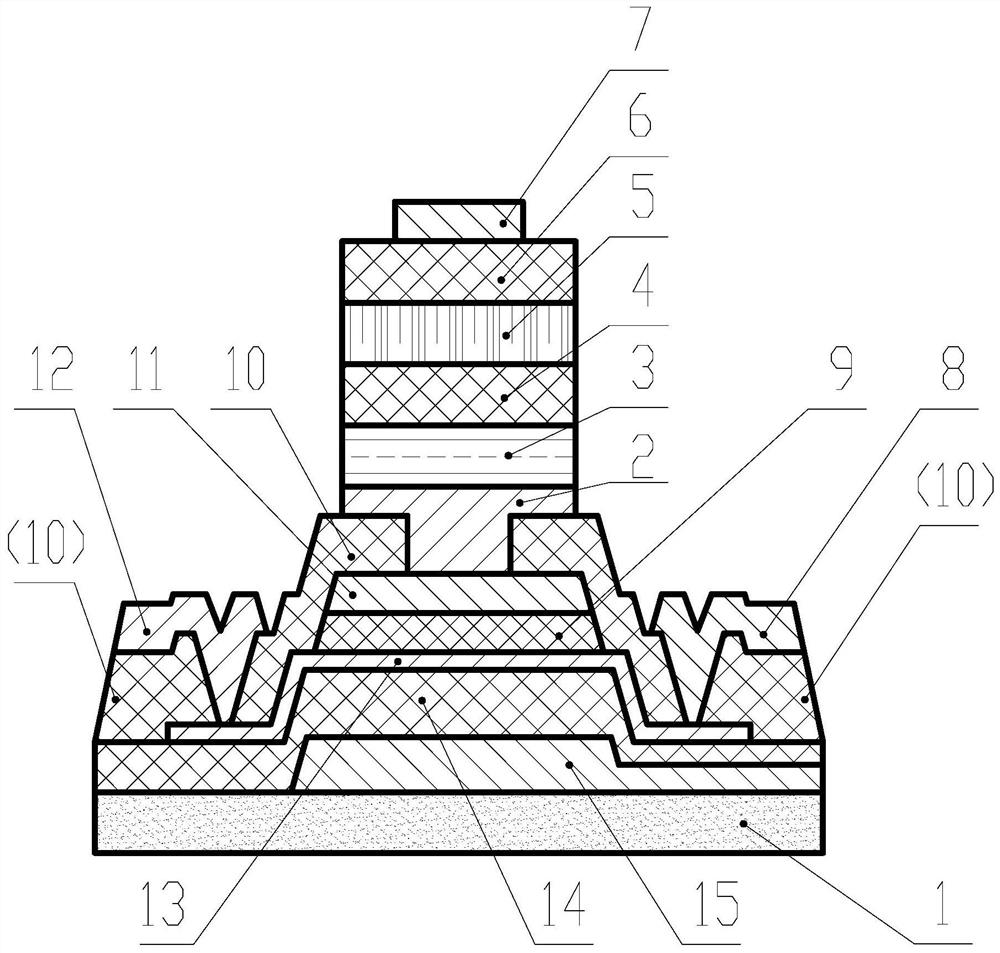

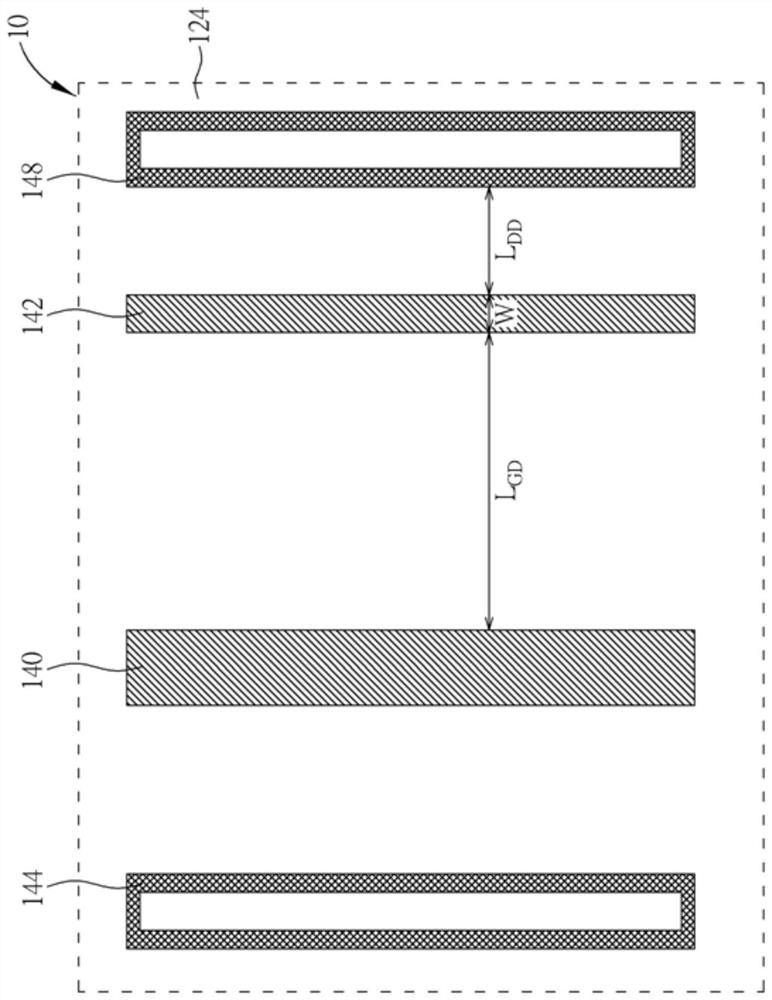

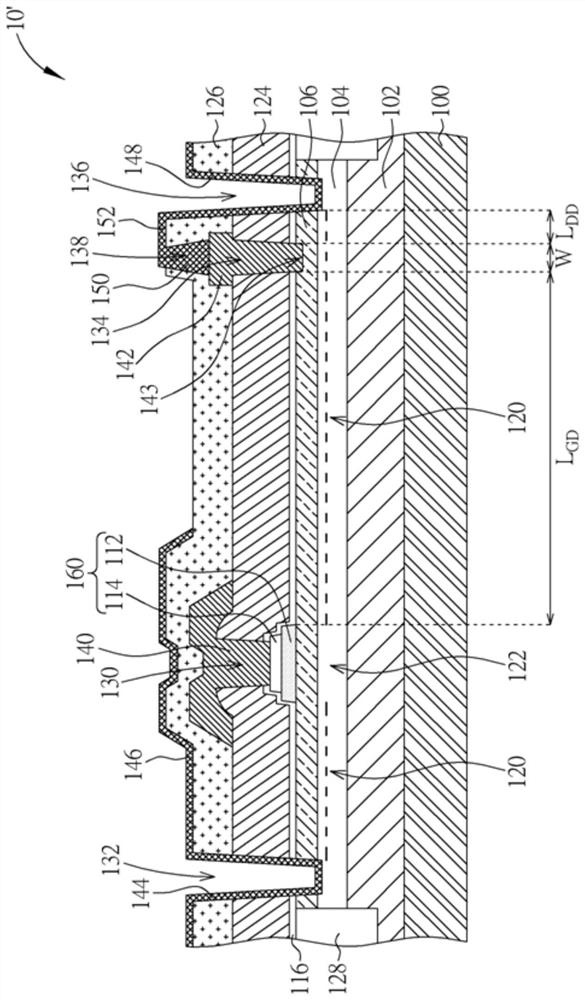

Thin film transistor and display panel

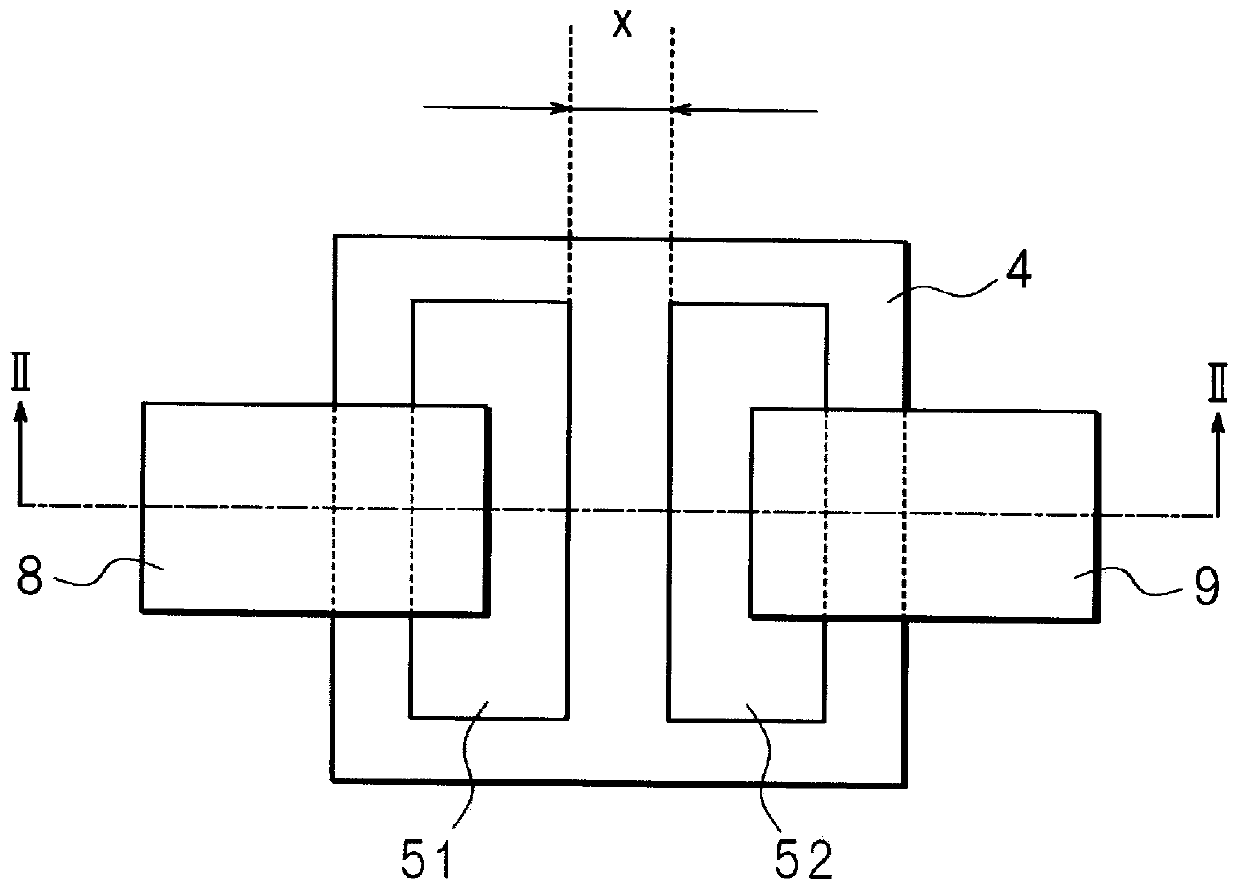

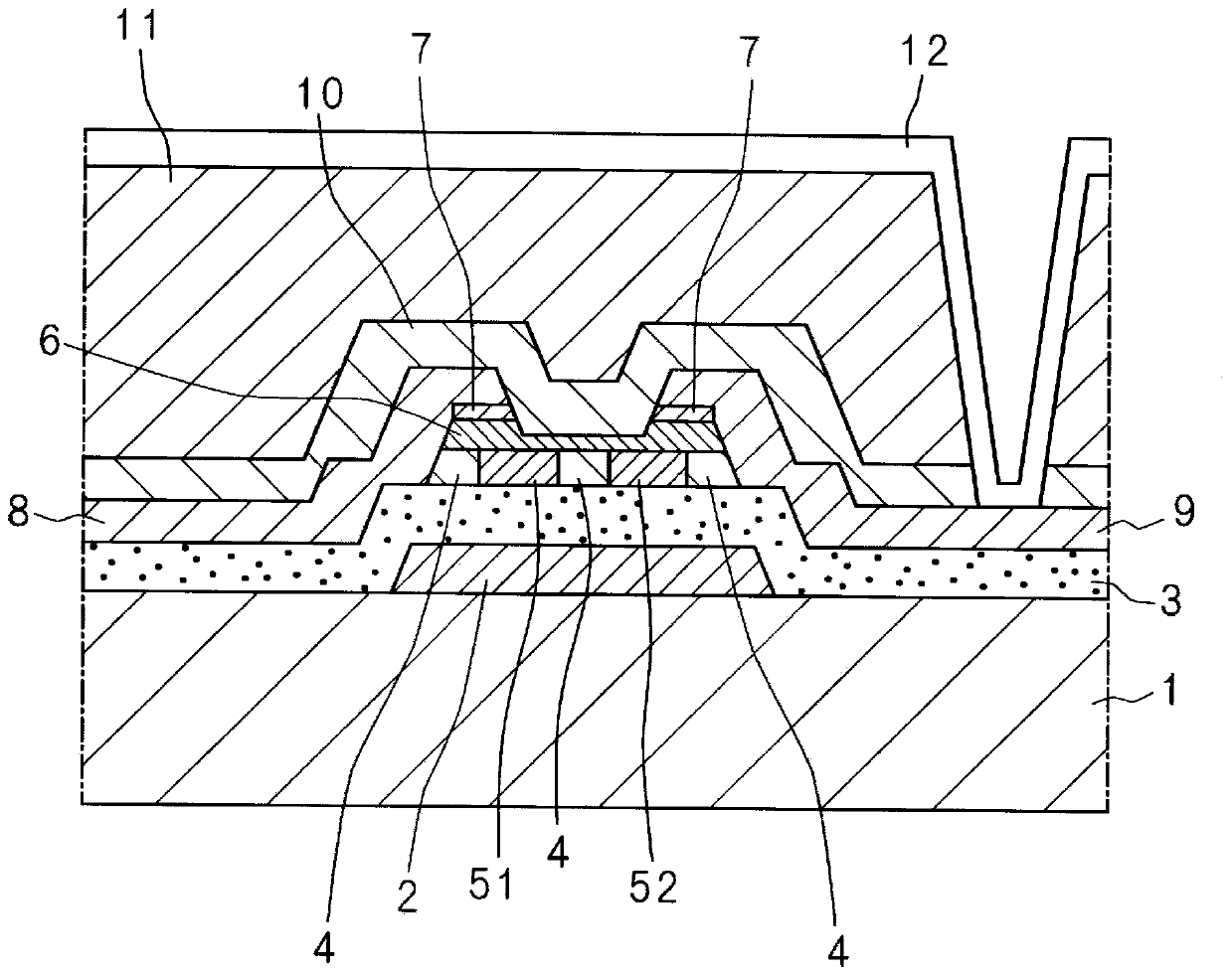

InactiveCN107408578BReduce cut-off currentTransistorSemiconductor/solid-state device manufacturingAmorphous siliconThin membrane

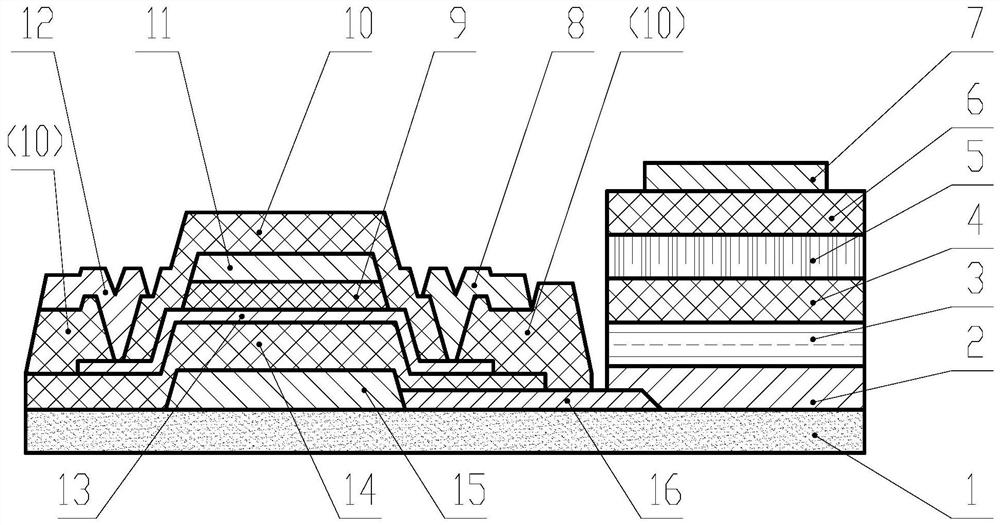

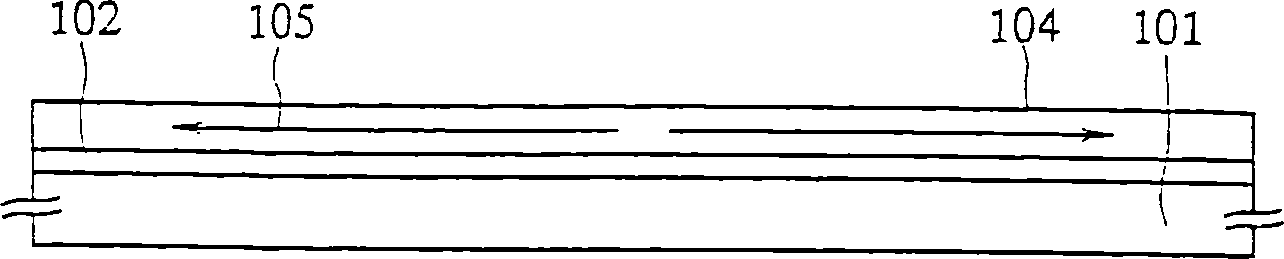

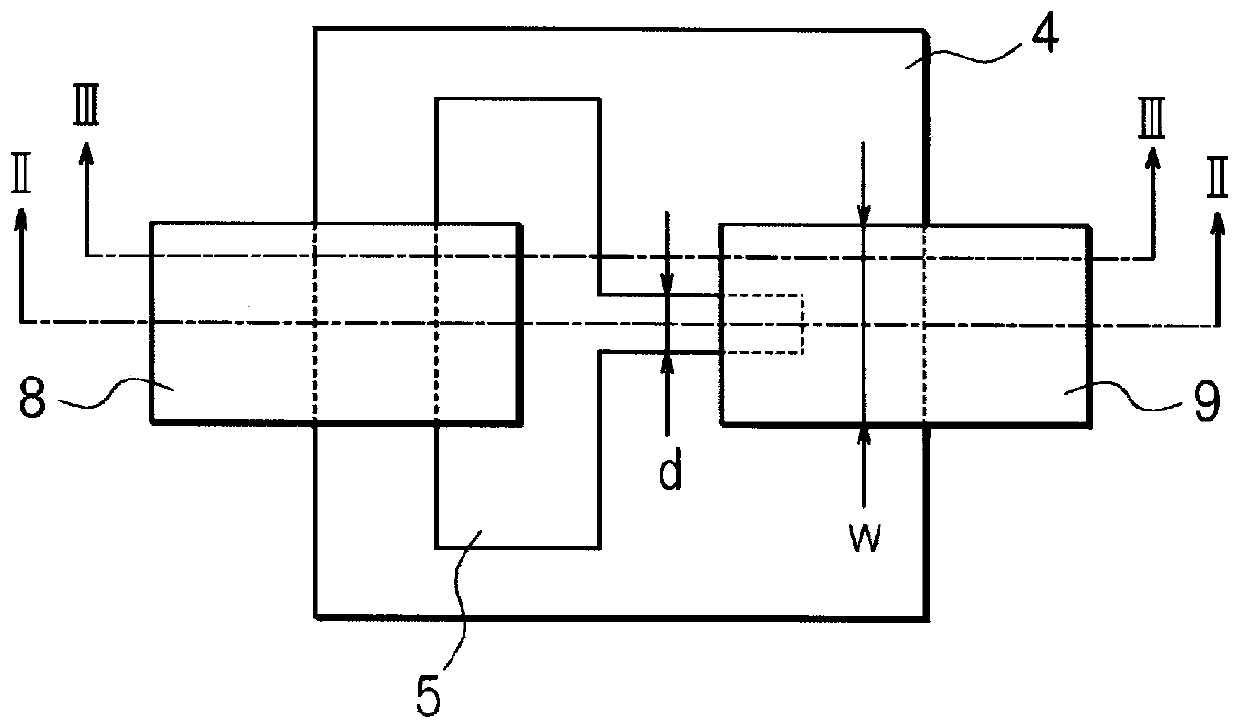

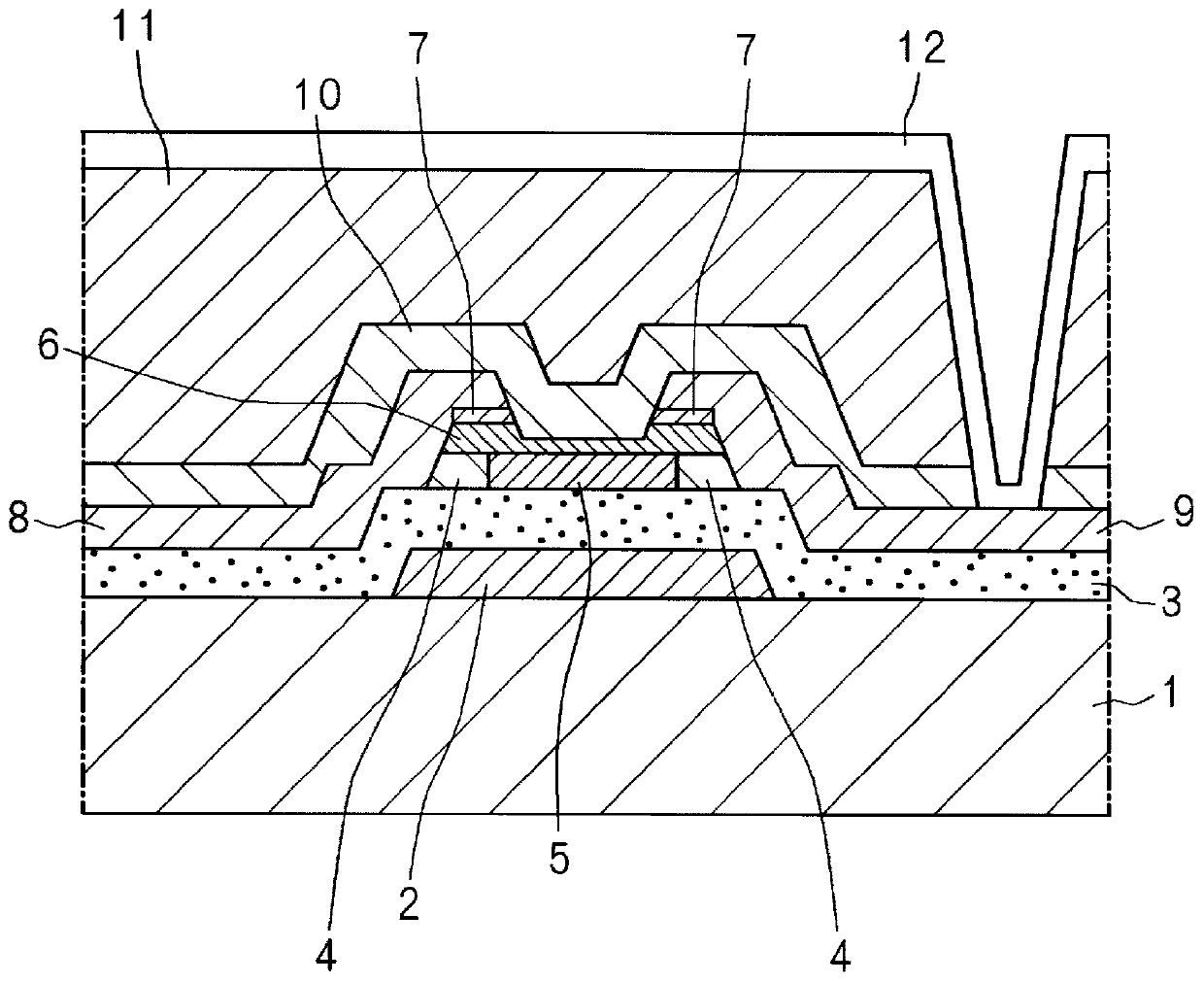

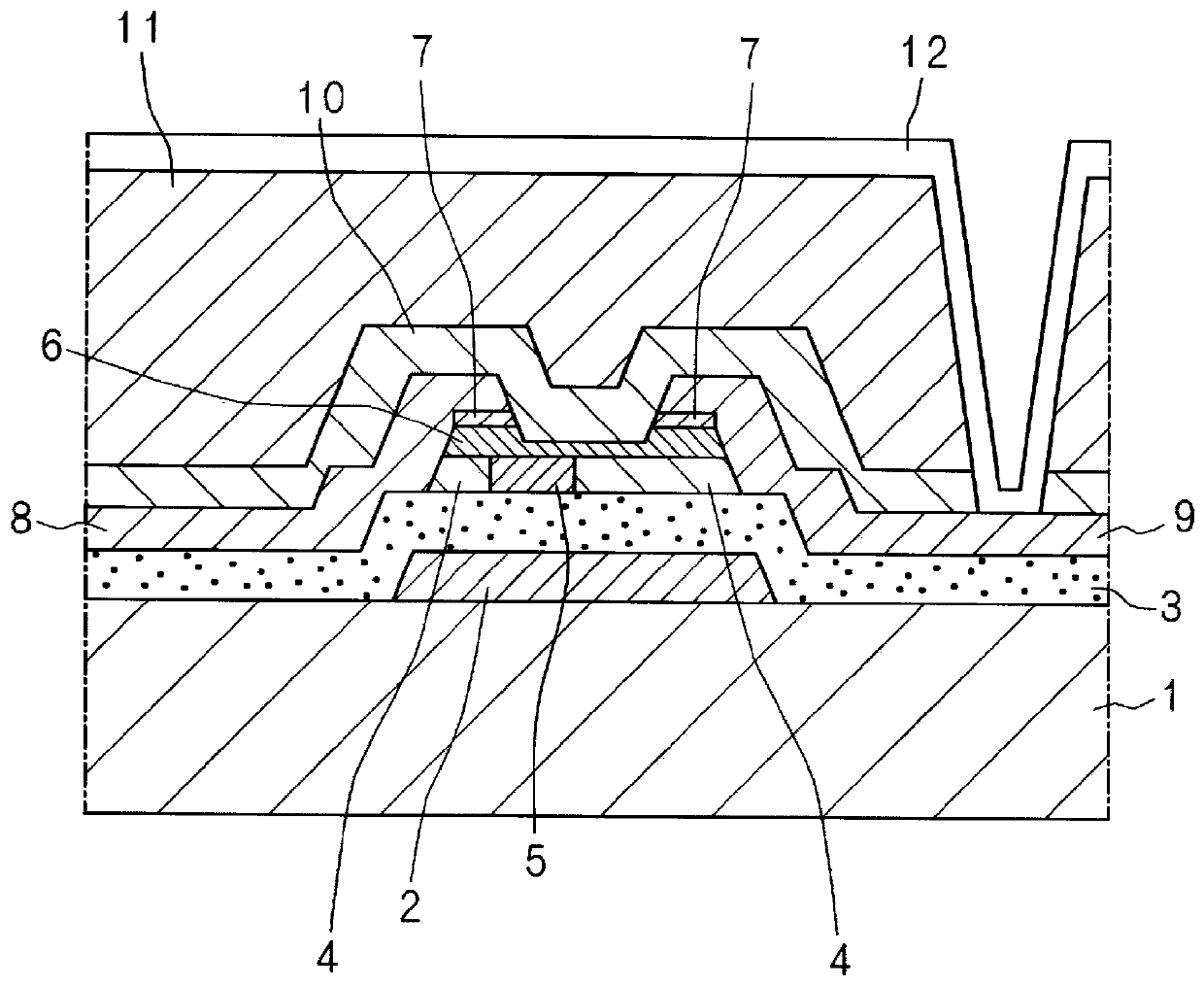

The invention provides a thin film transistor capable of reducing cut-off current and a display panel with the thin film transistor. The thin film transistor comprises: a gate electrode (2), formed on the surface of the substrate (1); a first amorphous silicon layer (4), formed on the upper side of the gate electrode (2); a plurality of polysilicon layers (51, 52, 53 ), are separated by the first amorphous silicon layer (4), and have the desired spacing dimension and are formed on the upper side of the gate electrode (2); the second amorphous silicon layer (6) and the n+ silicon layer (7), It is formed on the upper side of multiple polysilicon layers (51, 52, 53) and the first amorphous silicon layer (4); the source electrode (8) and the drain electrode (9) are formed on the n+ silicon layer (7).

Owner:SAKAI DISPLAY PROD

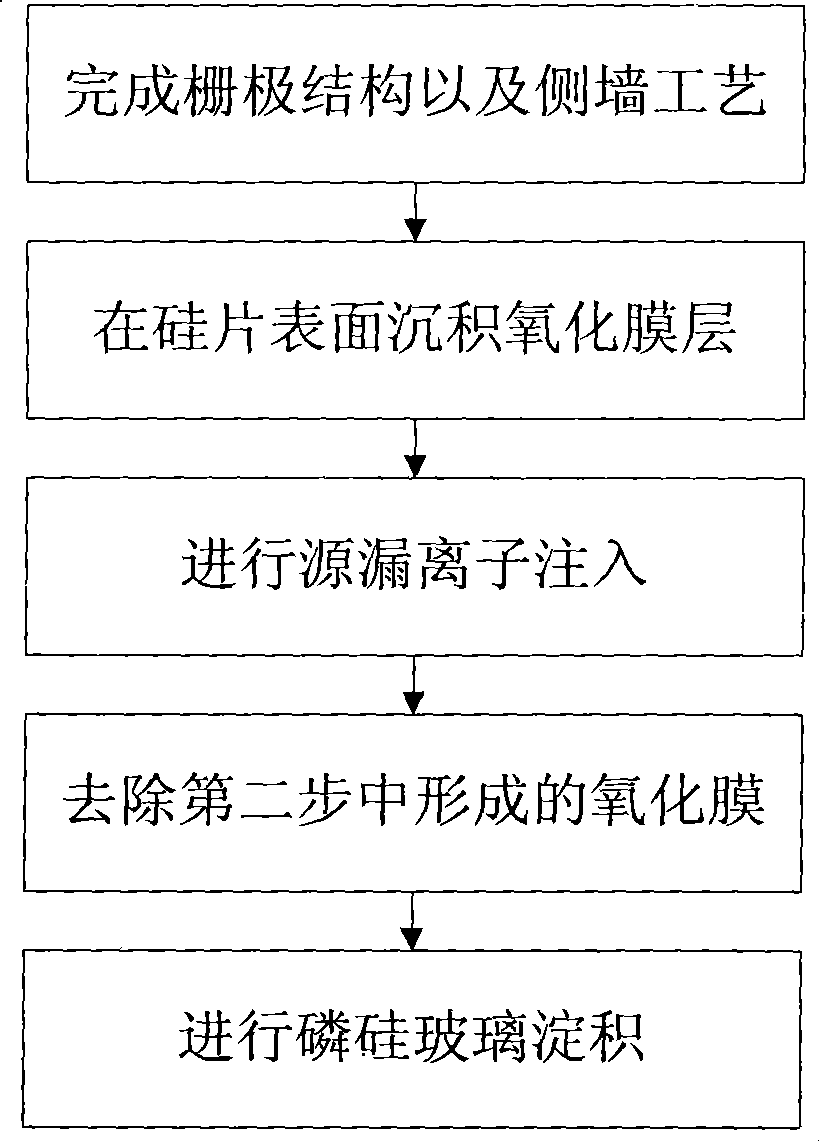

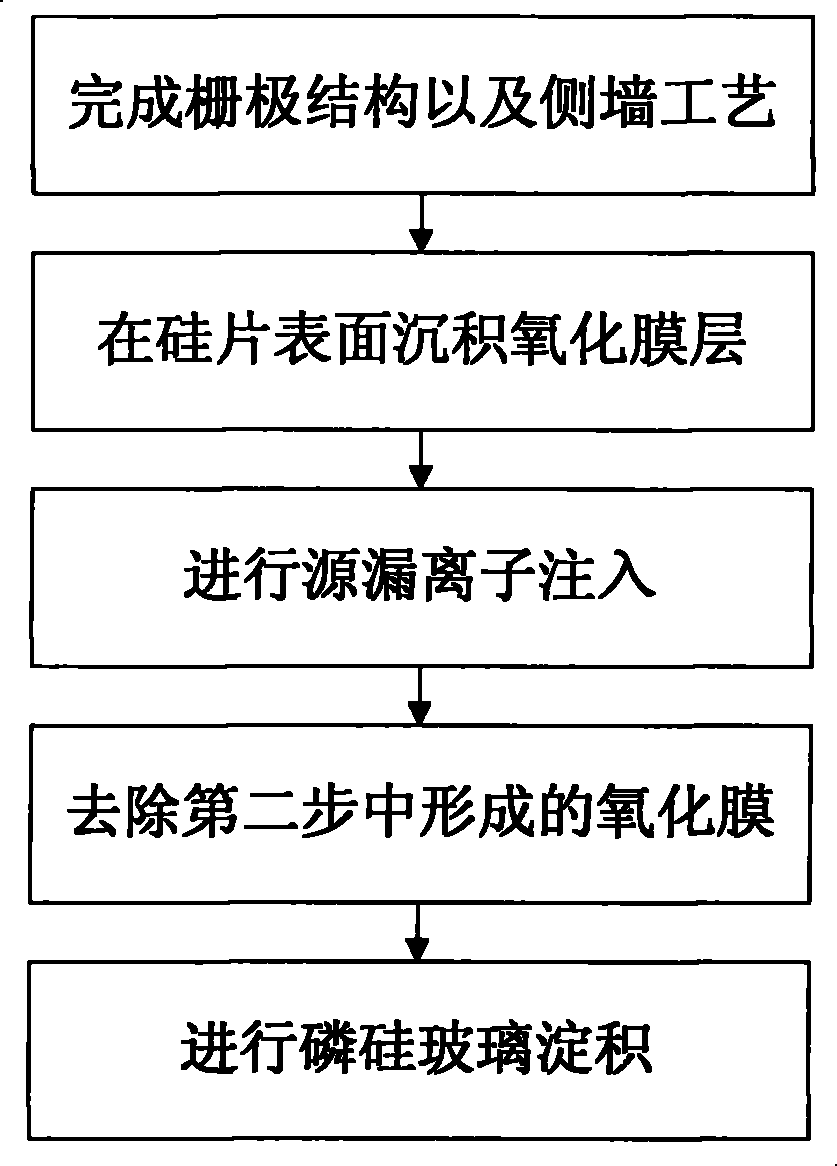

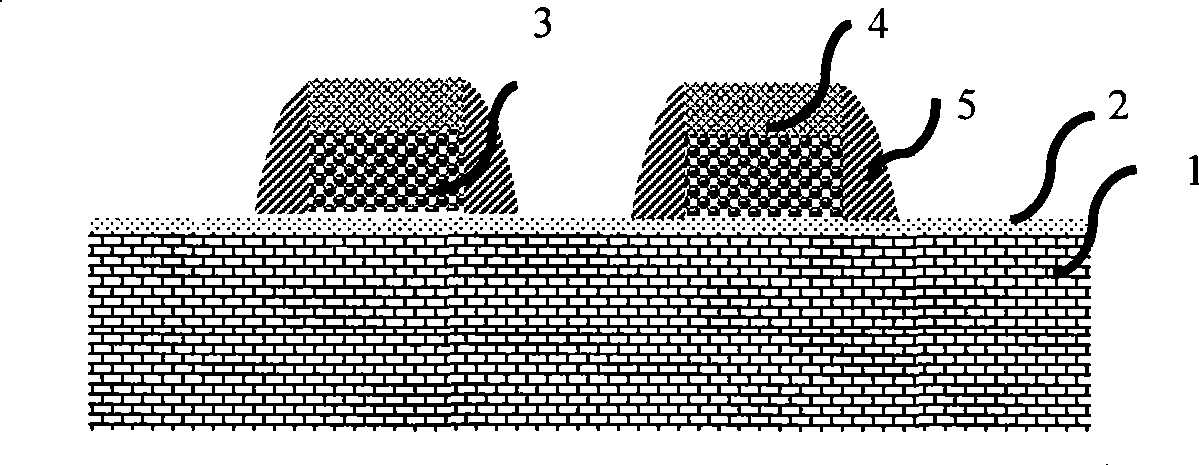

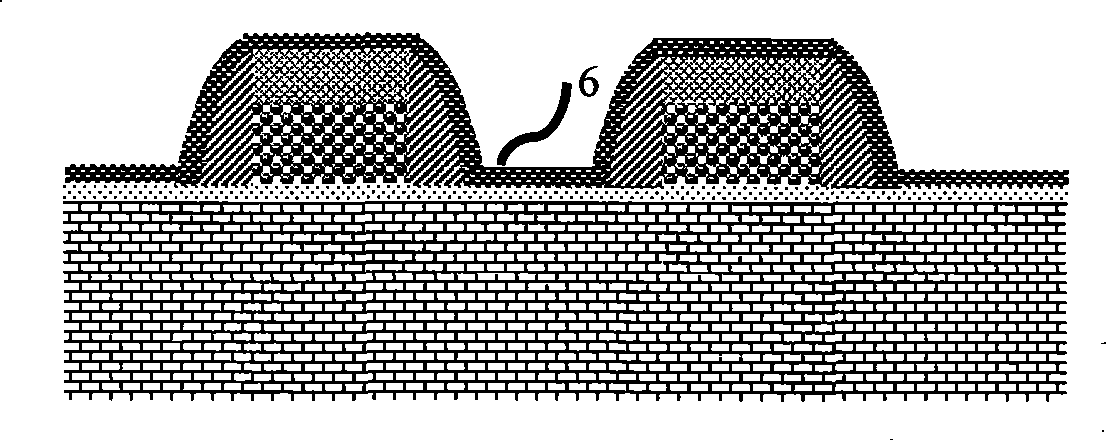

Manufacturing method of flash memory

ActiveCN101740521BIncrease widthIncrease distanceSemiconductor/solid-state device manufacturingIon implantationHard mask

The invention discloses a manufacturing method of a flash memory, comprising the following steps after forming a grid electrode silicon nitride side wall: 1) depositing a first layer of oxidation film on silicon wafer surface; 2) reverse etching the first layer of oxidation film, etching to a hard masking layer above grid electrode structure, and etching to a silicon substrate on other regions ofthe silicon wafer surface to form a smooth oxidation film side wall; 3) depositing a second layer of oxidation film on the silicon wafer surface; 4) carrying out ion implantation of source leakage; 5) adopting wet etching technology, and simultaneously removing the first layer of oxidation film and the second layer of oxidation film; and 6) depositing an interlayer membrane film on the surface ofthe silicon wafer. Under the condition of changing no other properties of a device, the invention lowers the cut-off current of the device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Thin film transistor and display panel

InactiveCN106663697BReduce cut-off currentTransistorSolid-state devicesAmorphous siliconThin membrane

Provided are a thin film transistor capable of reducing off-state current and a display panel having the thin film transistor. The thin film transistor comprises: a gate electrode (2) formed on the surface of the substrate (1); a polysilicon layer (5) formed on the upper side of the gate electrode; an amorphous silicon layer (4, 6) formed to cover Above-mentioned polysilicon layer; n+ silicon layer (7), is formed on the upper side of above-mentioned amorphous silicon layer; And source electrode (8) and drain electrode (9) are formed on above-mentioned n+ silicon layer; Above-mentioned polysilicon layer, In a projected state where the source electrode and the drain electrode are projected on the surface of the substrate, a part of the polysilicon layer overlaps with a part of the source electrode and a drain electrode, and is positioned on the source electrode and the drain electrode in the projected state. In the polysilicon layer between the electrodes, the minimum dimension in the width direction perpendicular to the length direction between the source electrode and the drain electrode is smaller than the width direction dimension of the source electrode and the drain electrode.

Owner:SAKAI DISPLAY PROD

Semiconductor device

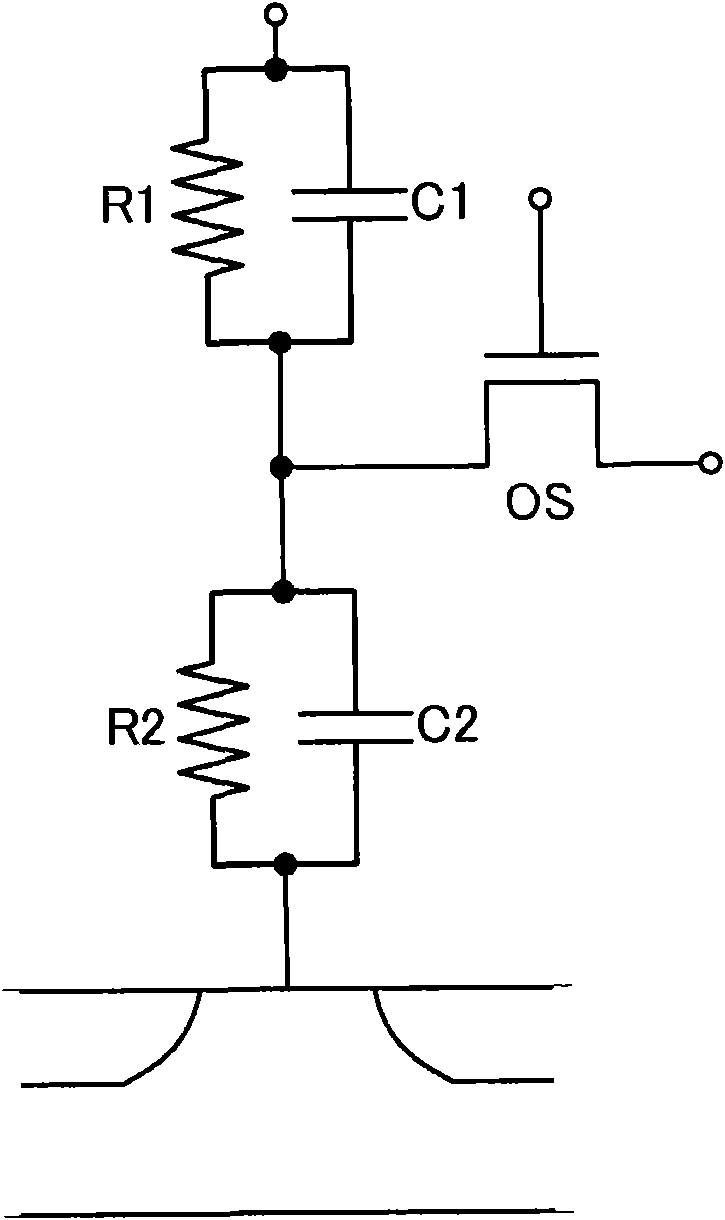

InactiveCN1573847BReduce sudden changesPrevent electrostatic discharge damageTransistorStatic indicating devicesEngineeringCapacitor

Owner:SEMICON ENERGY LAB CO LTD

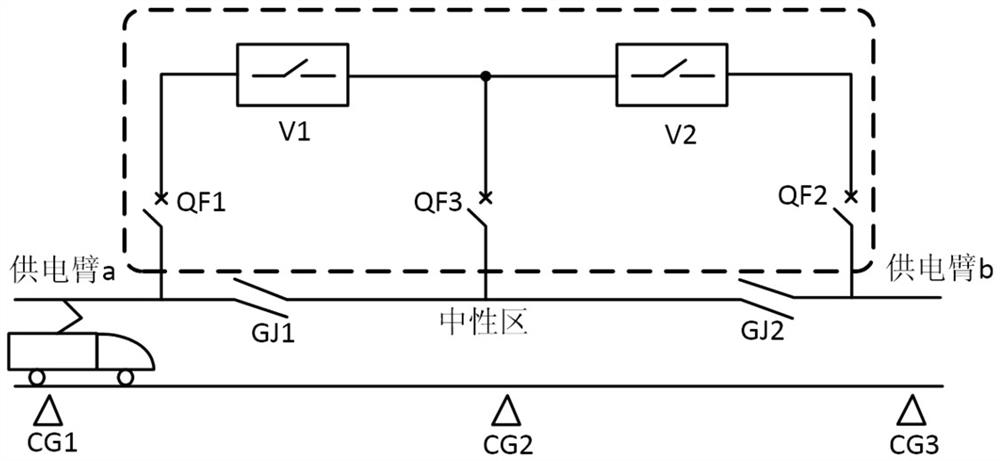

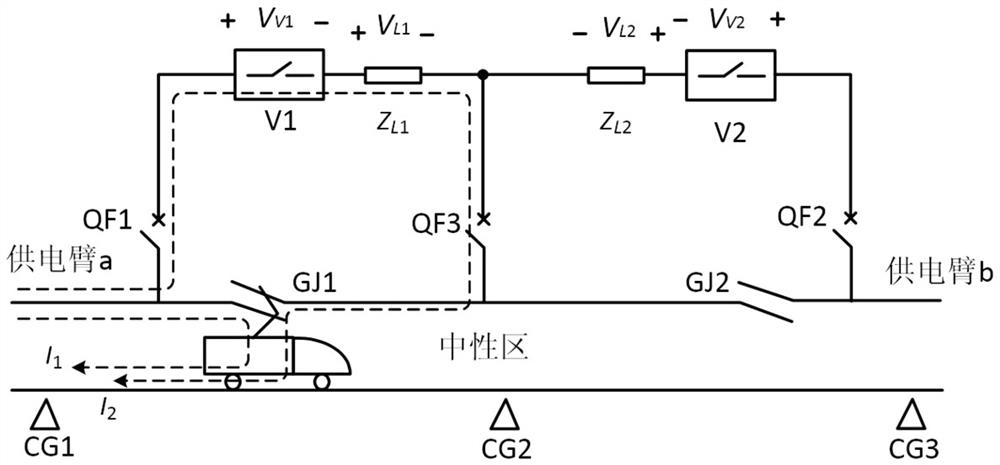

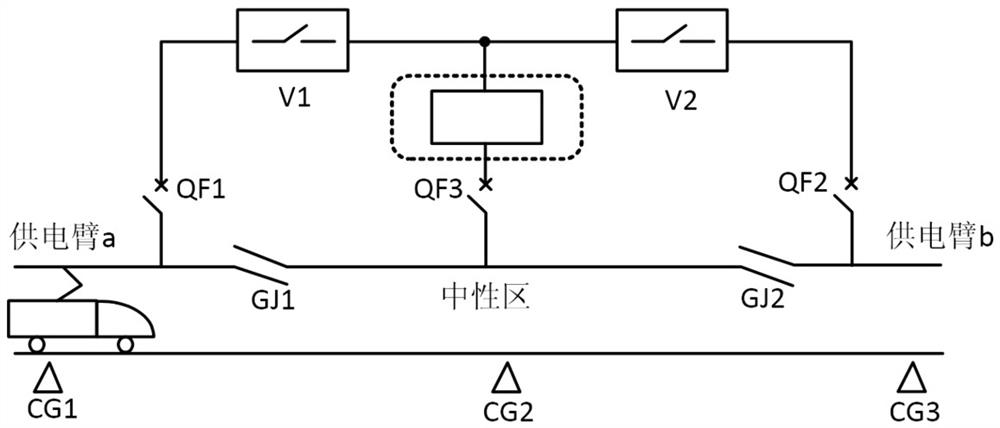

Ground automatic over-phase arc suppression method, suppression device and over-phase device

ActiveCN111660877BIncrease currentFacilitate the commutation processPower supply linesControl engineeringControl theory

The invention discloses a ground automatic over-phase-separation arc suppression method. In the process of over-phase, compensation current is output to a power supply circuit composed of a power supply arm, a ground over-phase device and a neutral zone to promote commutation, thereby reducing power receiving The bow cuts off the current when it touches or breaks away from the catenary to suppress the arc. The invention also discloses a suppressing device, which includes a compensation module, which is connected in series in the power supply circuit composed of the power supply arm, the ground over-phase splitting device and the neutral zone, and is used to output compensation current to promote commutation and reduce power receiving. The cut-off current of the bow when it touches or breaks away from the catenary. The invention also discloses a ground automatic phase splitting device, which includes at least two switch assemblies, and the two switch assemblies are respectively connected with the two-phase power supply arm and the neutral zone; the two switch assemblies are connected with the neutral zone as described above The arc suppression device described above. The suppressing method, suppressing device and excessive phase splitting device of the present invention all have the advantages of effectively reducing or avoiding arc generation and the like.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

Semiconductor device and its production method

InactiveCN100501980CReduce cut-off currentImprove pass rateTransistorSolid-state devicesActive matrixImpurity

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method of manufacturing the same

ActiveCN102906882AReduce cut-off currentStable electrical characteristicsTransistorElectroluminescent light sourcesSemiconductorOxygen deficiency

Oxygen is released from the insulating layer, whereby oxygen deficiency in the oxide semiconductor layer and an interface state between the insulating layer and the oxide semiconductor layer can be reduced. Accordingly, a semiconductor device where reliability is high and variation in electric characteristics is small can be manufactured.

Owner:SEMICON ENERGY LAB CO LTD

High electron mobility transistor and high voltage semiconductor device

PendingCN113871476AIncrease the on-resistanceIncrease contact areaSemiconductor devicesDevice materialElectrical connection

The invention discloses a high electron mobility transistor which includes a substrate, a III-V channel layer, a III-V barrier layer, a III-V cover layer, a source electrode, a first drain electrode, a second drain electrode and a connecting part, wherein the III-V channel layer, the III-V barrier layer and the III-V cover layer are sequentially arranged on the substrate; the source electrode is disposed on one side of the III-V cover layer, and the first drain electrode and the second drain electrode are disposed on the other side of the III-V cover layer; the bottom surface of the first drain electrode is separated from the bottom surface of the second drain electrode, and the composition of the first drain electrode is different from the composition of the second drain electrode; and the connecting part is electrically connected to the first drain electrode and the second drain electrode.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

Synchronous rectification circuit and charging circuit using it

ActiveCN104104228BSimple structureReduce manufacturing costBatteries circuit arrangementsDc-dc conversionControl signalEngineering

Disclosed are a synchronous rectifying circuit and a charging circuit comprising the same. The synchronous rectifying circuit comprises a rectifying transistor and a synchronous rectifying control circuit, wherein the synchronous rectifying control circuit is used for generating synchronous rectifying control signals according to the voltage difference between the drain electrode and the source electrode of the rectifying transistor to control on and off of the rectifying transistor. The synchronous rectifying circuit is simple in structure, small in number of devices and low in cost. When applied to the charging circuit, the synchronous rectifying circuit can overcome the problem that a battery is difficult to be fully charged.

Owner:NANJING SILERGY SEMICON TECH CO LTD

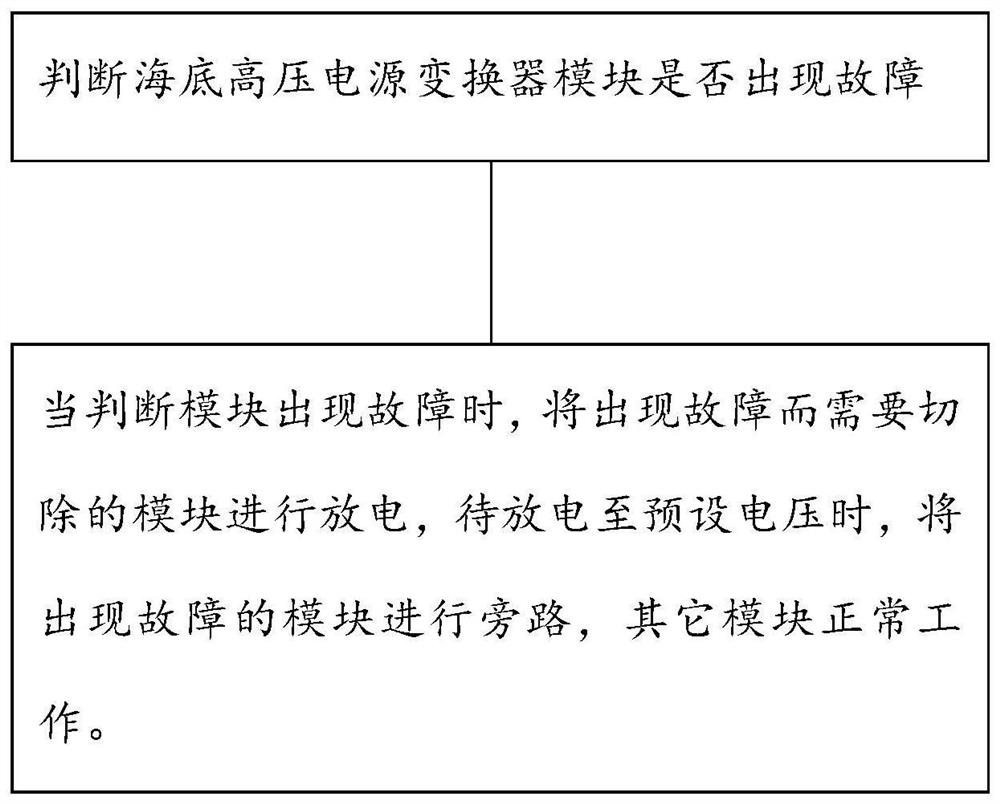

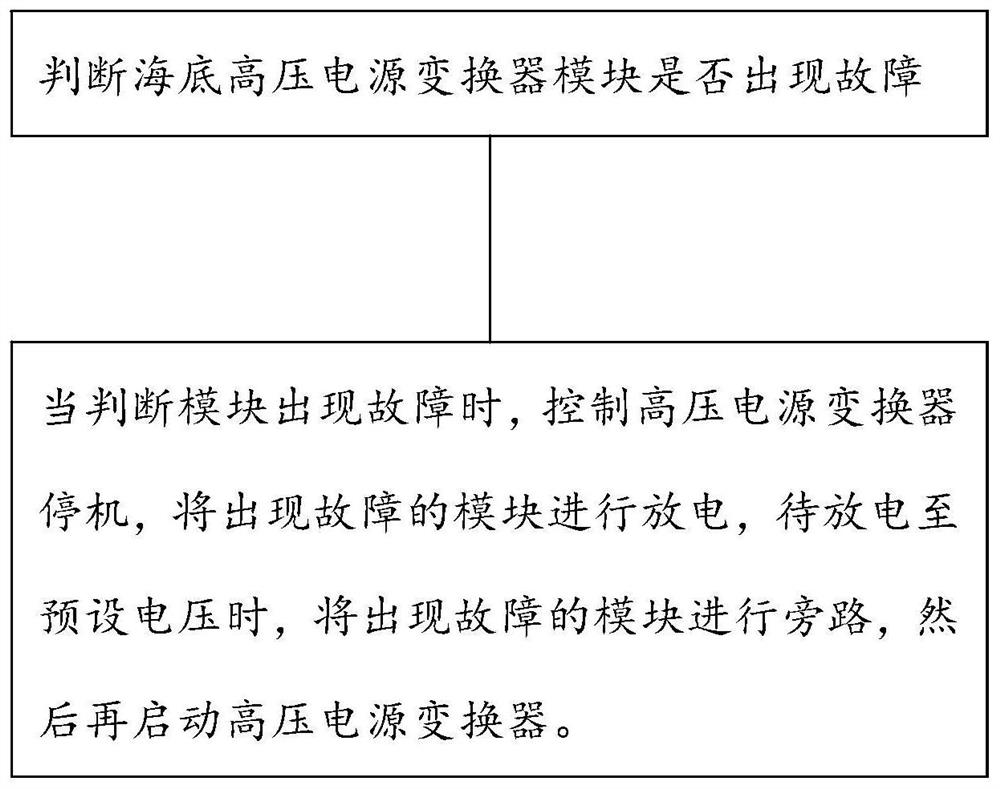

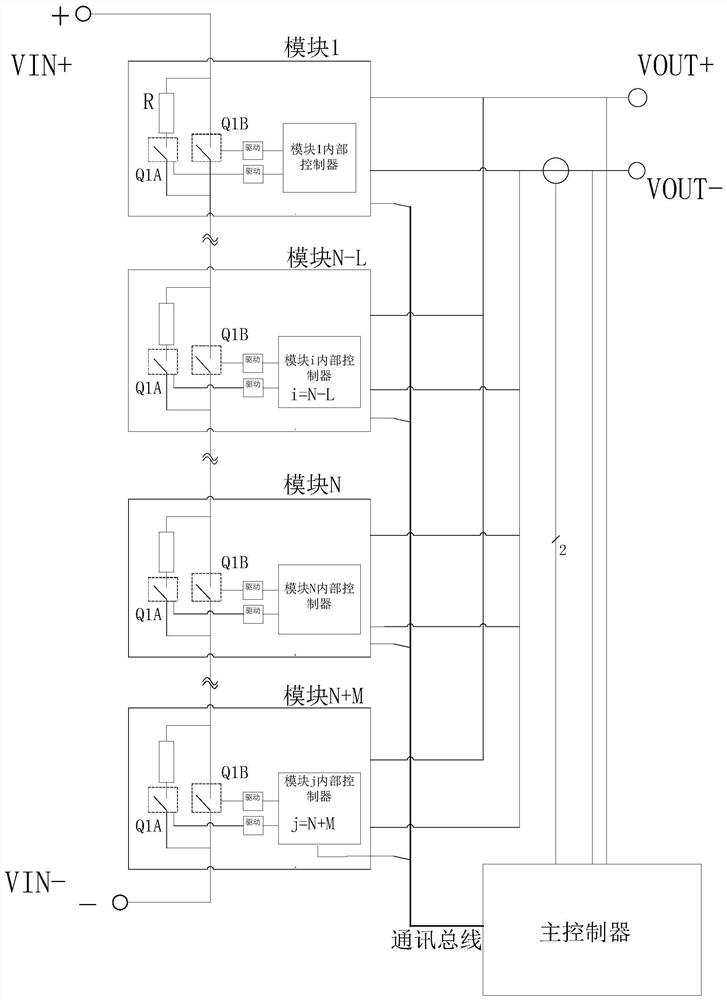

Seabed high-voltage power converter module redundancy switching method and system

PendingCN113054737AReduce volumeReduce cut-off currentEmergency power supply arrangementsControl engineeringControl theory

The invention discloses a seabed high-voltage power converter module redundancy switching method and switching system, belongs to the technical field of seabed power supplies, and is used for solving the technical problems that the existing seabed power supply redundancy is high in cost and needs redundancy. The method comprises a non-stop switching method and a stop switching method. The non-stop switching method comprises the following steps of: judging whether a module has a fault or not; and when judging that the module has a fault, discharging the module which has a fault and needs to be removed, and when the module is discharged to the preset voltage, bypassing the module which breaks down has a fault, and enabling other modules to operate normally without shutdown. The shutdown switching method comprises the following steps of: judging whether a module breaks down or not; when judging that the module breaks down, controlling a high-voltage power supply converter to be shut down, discharging the module which breaks down, when the module is discharged to the preset voltage, bypassing the module with the fault, and then starting the high-voltage power supply converter. The seabed high-voltage power converter module redundancy switching method has the advantages of being lower in cost, capable of achieving redundancy switching without shutdown, high in reliability and the like.

Owner:O&C ELECTRIC TECHN CO LTD

Method for manufacturing flash memories

ActiveCN101740386BIncrease widthIncrease distanceSemiconductor/solid-state device manufacturingThin oxidePower flow

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

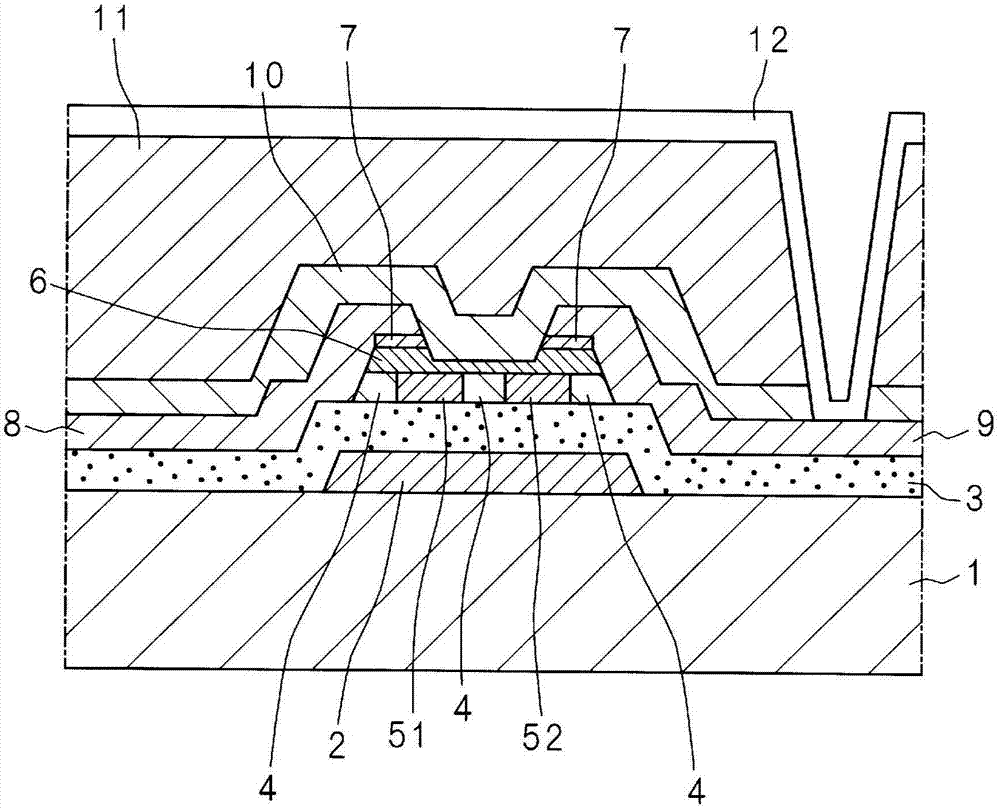

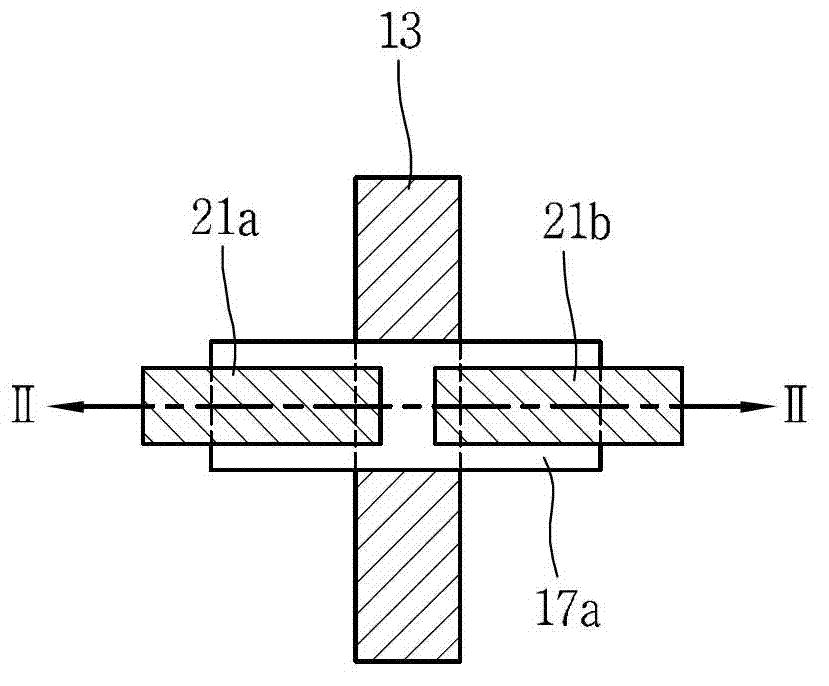

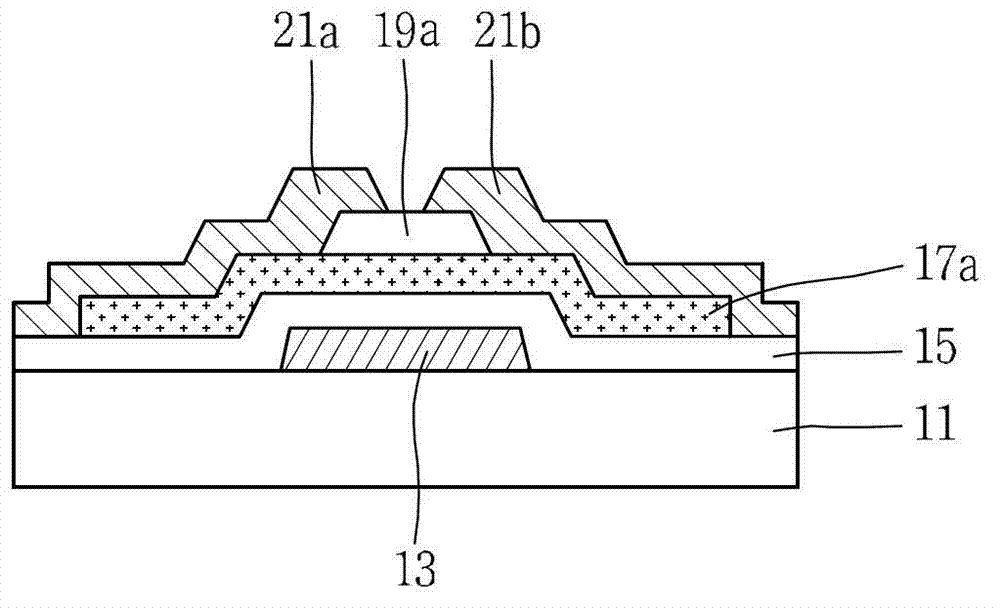

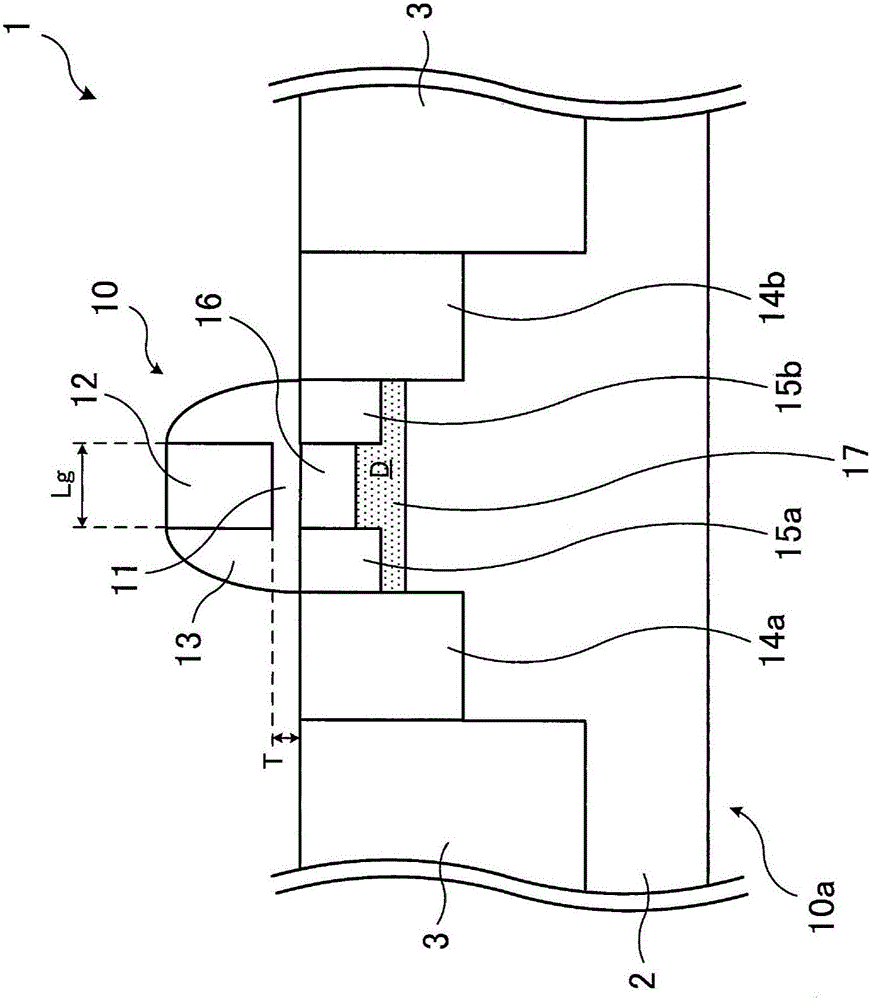

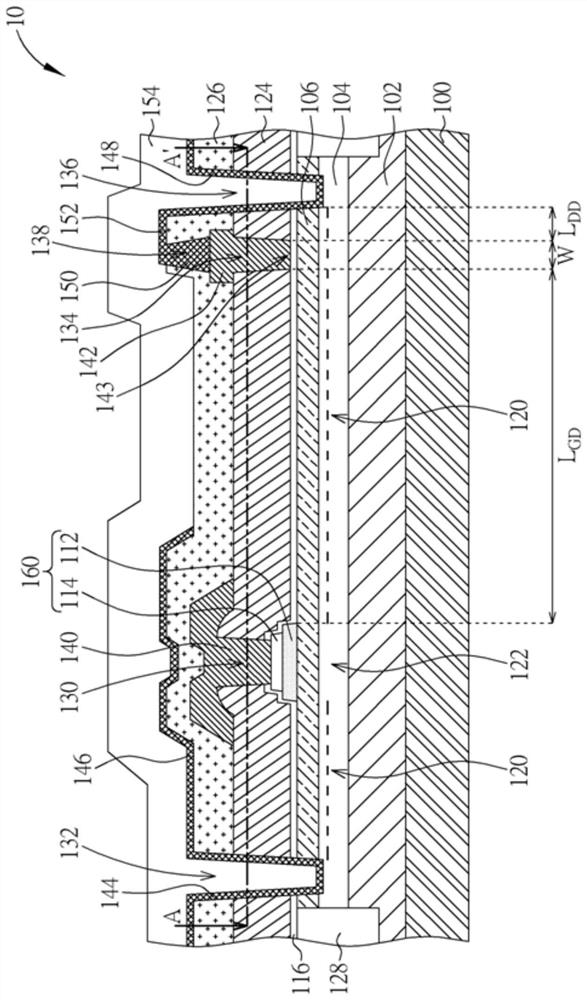

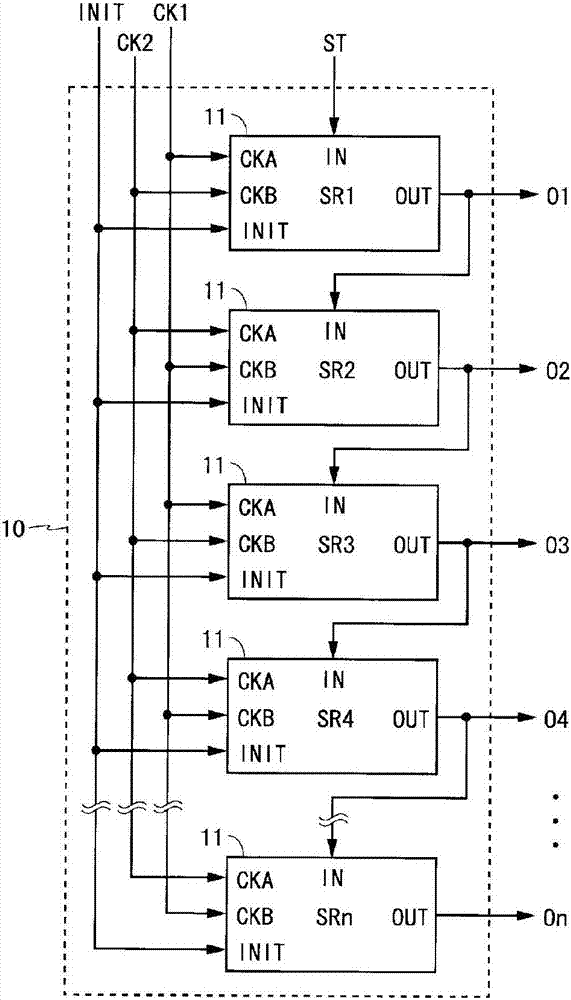

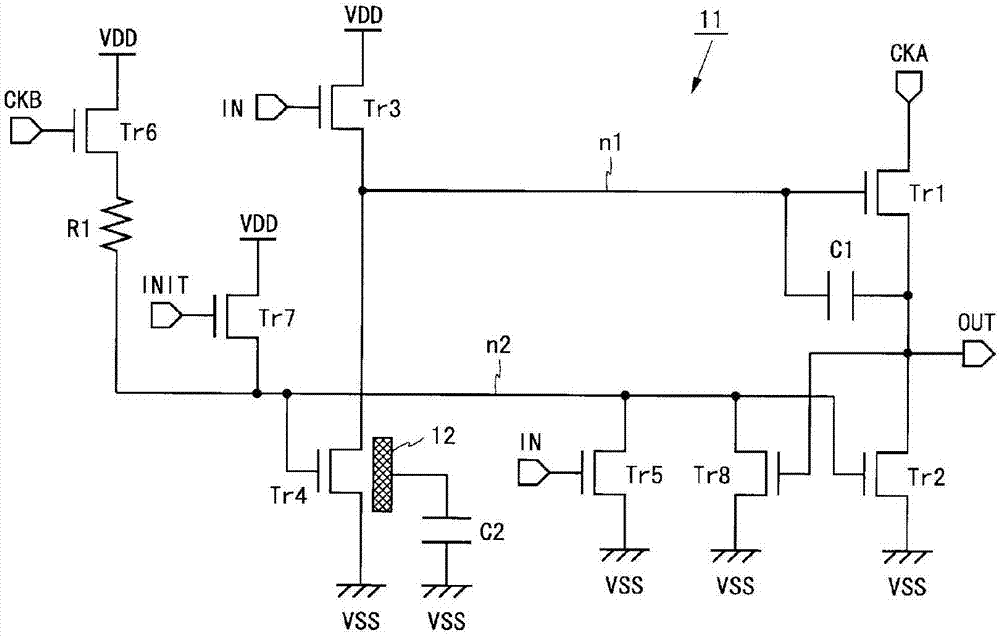

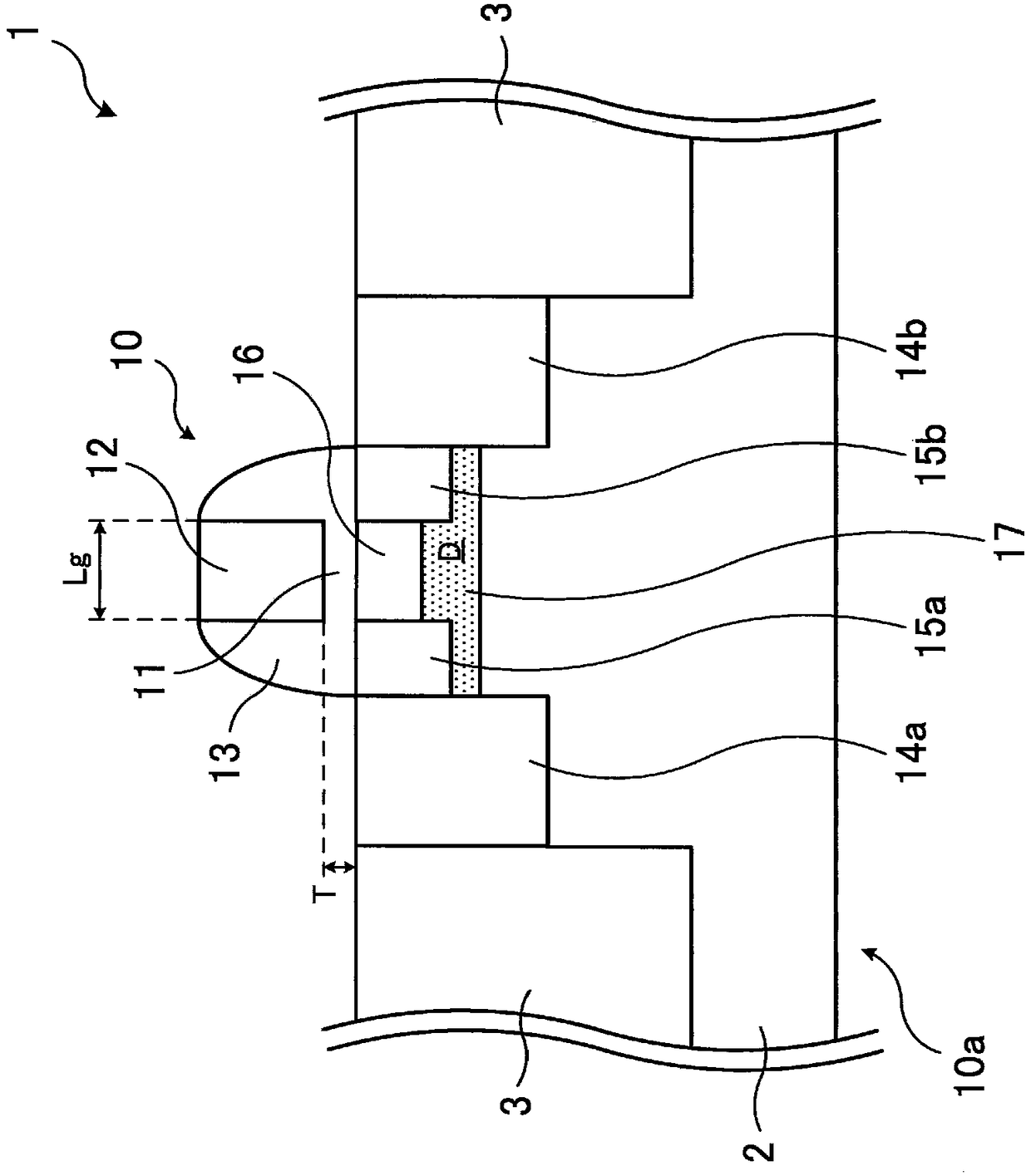

Drive circuit for display device

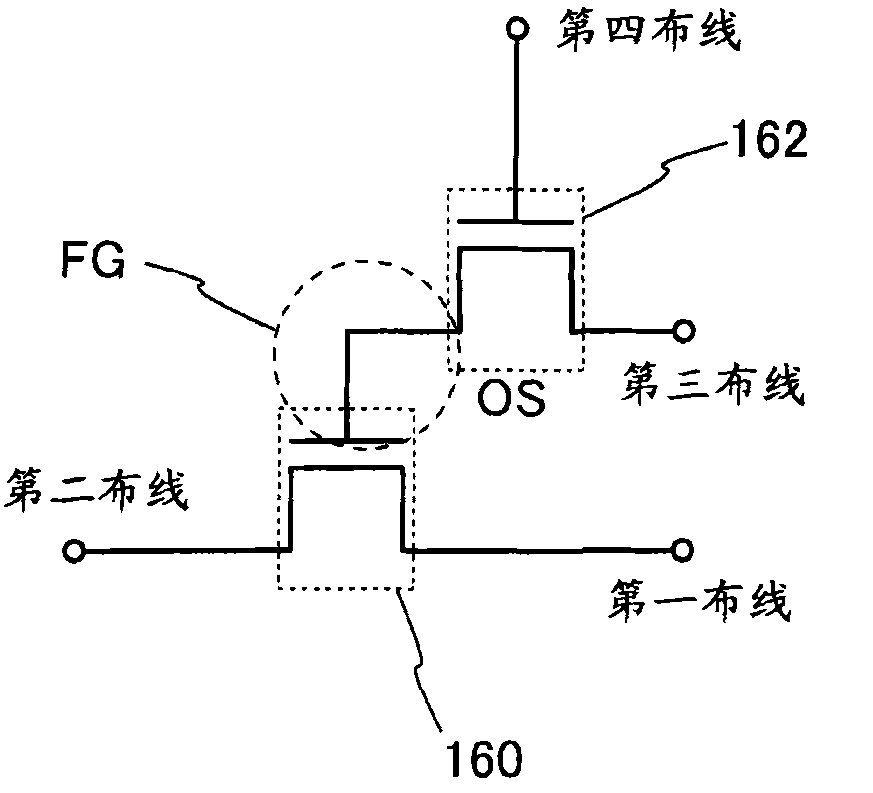

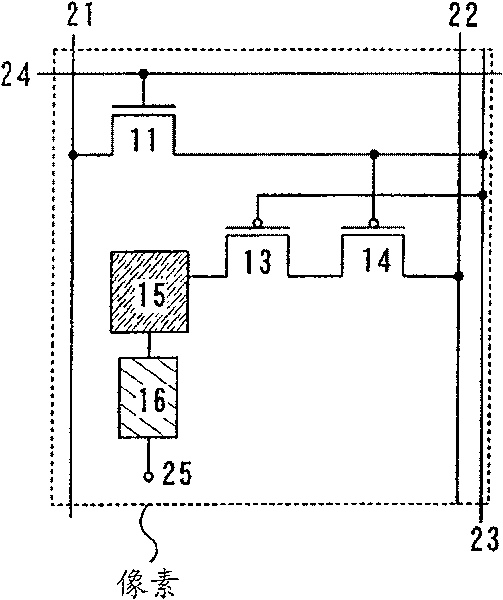

InactiveCN107533819ALow costAccurate operationTransistorStatic indicating devicesCapacitanceDisplay device

A drive circuit for a display device includes a TFT having a source electrode 15, a drain electrode 14, and a gate electrode 13. An electrically isolated light shielding film 12 is provided, which hasa main part for shielding a channel part of the TFT from light and an extension part 20 integrally formed with the main part. An auxiliary capacitance C2 is formed with the extension part 20 and an electrode member 21 integrally formed with the source electrode 15, arranged so as to appear stacked in a plan view. The electrode member 21 may be replaced by an electrode member formed in the same layer as the channel part and connected to the source electrode 15, an electrode member connected to one conduction electrode in another TFT, or an electrode member integrally formed with the gate electrode 13. Thereby, a drive circuit with a small area, including a light-shielded thin film transistor, is provided at a low cost.

Owner:SHARP KK

Liquid crystal display device and manufacturing method thereof

InactiveCN101207092BImprove reliabilityReduce cut-off currentSemiconductor/solid-state device detailsSolid-state devicesLiquid-crystal displayEngineering

The invention discloses a LCD device, comprising a first substrate divided into a pixel part, a first and a second pad part; a gate and a gate line formed in the pixel part of the first substrate; an active pattern formed on the gate in an island shape and provided with a width smaller than that of the gate; an insulation film formed on the first substrate and provided with a first and a second contact hole respectively exposed with the active electrode region and the drain electrode region of the active pattern; an active electrode and a drain electrode, formed in the pixel part of the first substrate and electrically connected with the active electrode region and the drain electrode region of the active pattern through the first and the second contact hole; a data line formed in the pixel part of the first substrate and crossed with the gate line so as to limit the pixel region; an etching barrier structure positioned between the active electrode and the drain electrode and formed as the insulation film; a pixel electrode electrically connected with the pixel electrode; and a second substrate adhered with the first substrate in a face to face mode, the second substrate is a filter substrate.

Owner:LG DISPLAY CO LTD

Semiconductor device

ActiveCN106024783BReduce cut-off currentTransistorSemiconductor/solid-state device manufacturingDevice materialEngineering physics

A semiconductor device includes a first transistor and a second transistor connected to the same power source. Each of the first transistor and the second transistor includes a higher-concentration impurity region of the second conductivity type under the low-concentration channel region disposed between the source region and the drain region of the first conductivity type. The thickness of the gate insulating film of one of the first transistor and the second transistor is made larger than that of the other. According to the present disclosure, off-current in a transistor can be suppressed low.

Owner:MIE FUJITSU SEMICON