Interface logic for a multi-core system-on-a-chip (SOC)

A technology of interface logic and logic, applied in the field of interface logic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

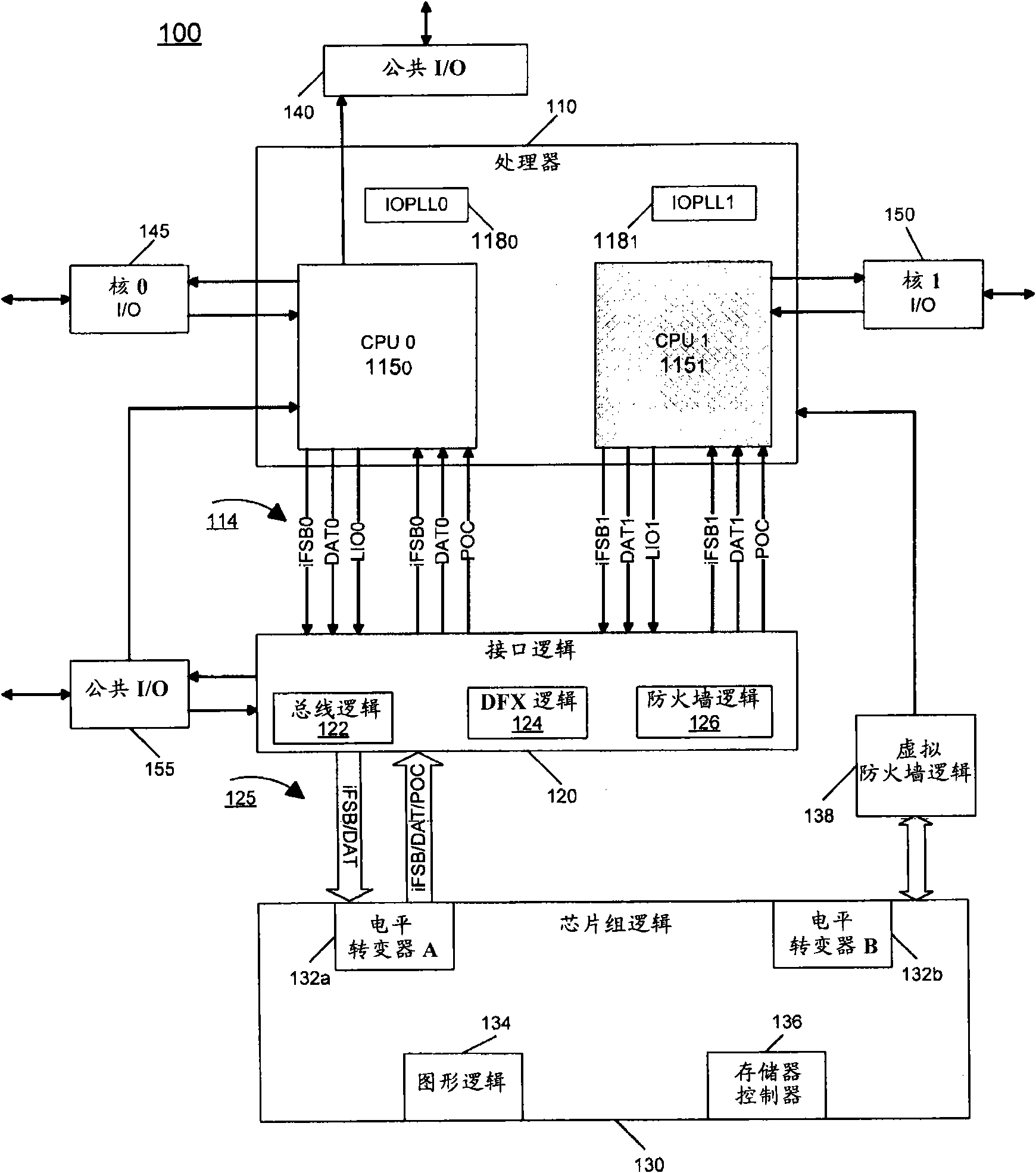

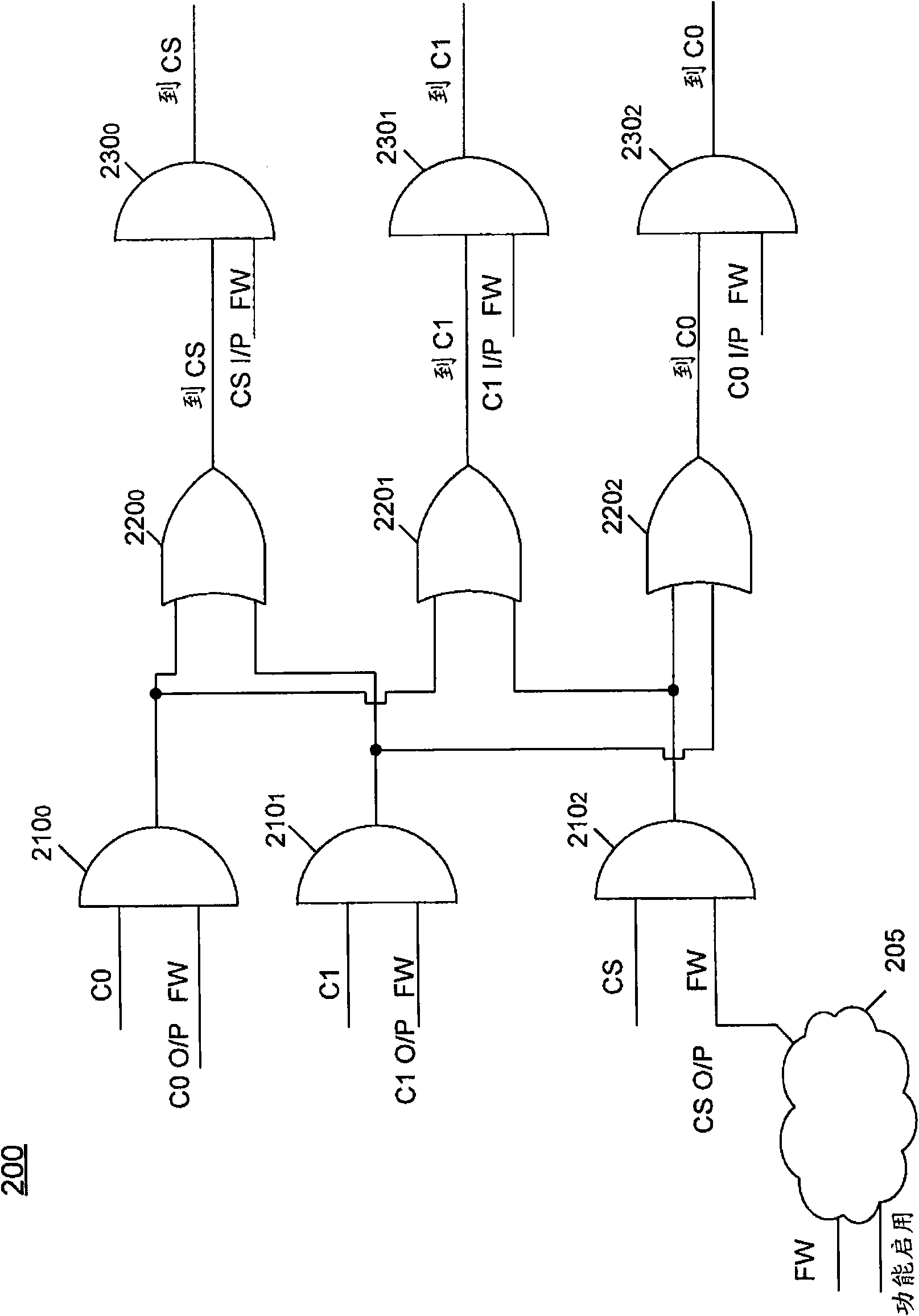

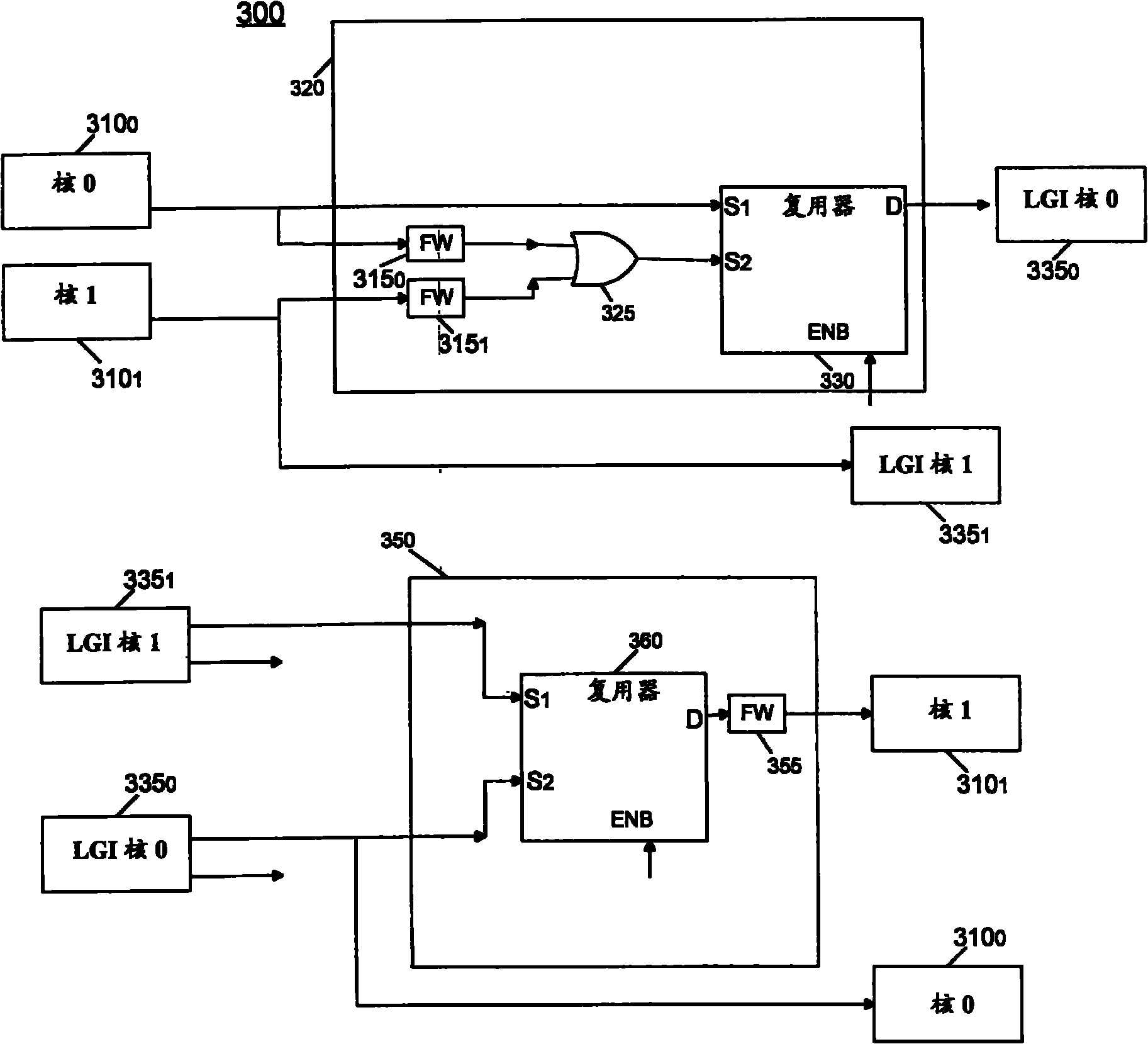

[0012] In various embodiments, a multi-core system-on-chip (SoC) may be provided with interface logic to one or more integrated cores (also referred to herein as a central processing unit (CPU)), as well as with an integrated memory controller and Associated input / output (10) buffers. The CPU, which may be a pair of cores in one embodiment, is coupled to the rest of the SoC via an internal front side bus (FSB) interconnect. The interface logic also provides functional and test access for configurations as single core (in addition to dual core) for market and high volume manufacturing (HVM) flexibility. In one embodiment, the interface logic component can interface the two CPUs with other chipset logic in the SoC (eg, Northbridge controller). Interface logic can be fused (fuse) to support single-core or dual-core product base keeping unit (product stock keeping unit) (SKU).

[0013] In one embodiment, the interface logic can thus be used to resolve the dual-core CPU iFSB (Int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More