Method for judging input overflowing amplitude of pipelining type analog-to-digital converter

A technology for analog-to-digital converters and judging pipelines, applied in the direction of analog-to-digital converters, etc., can solve the problems of system efficiency reduction, unknown overflow range, and unpredictable adjustment process time, so as to improve efficiency and shorten adjustment time Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

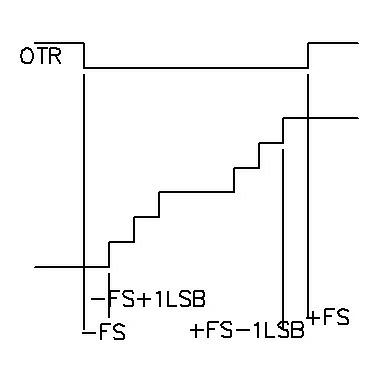

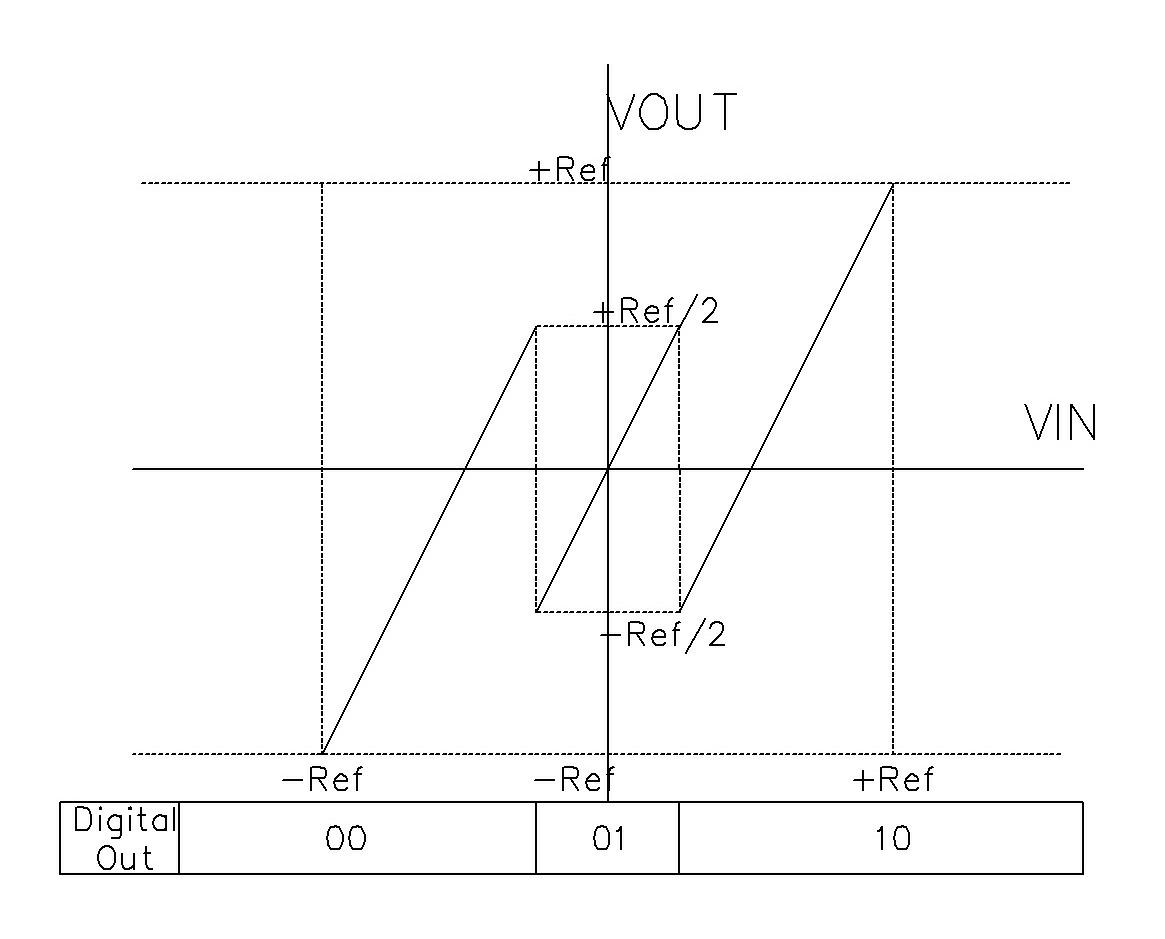

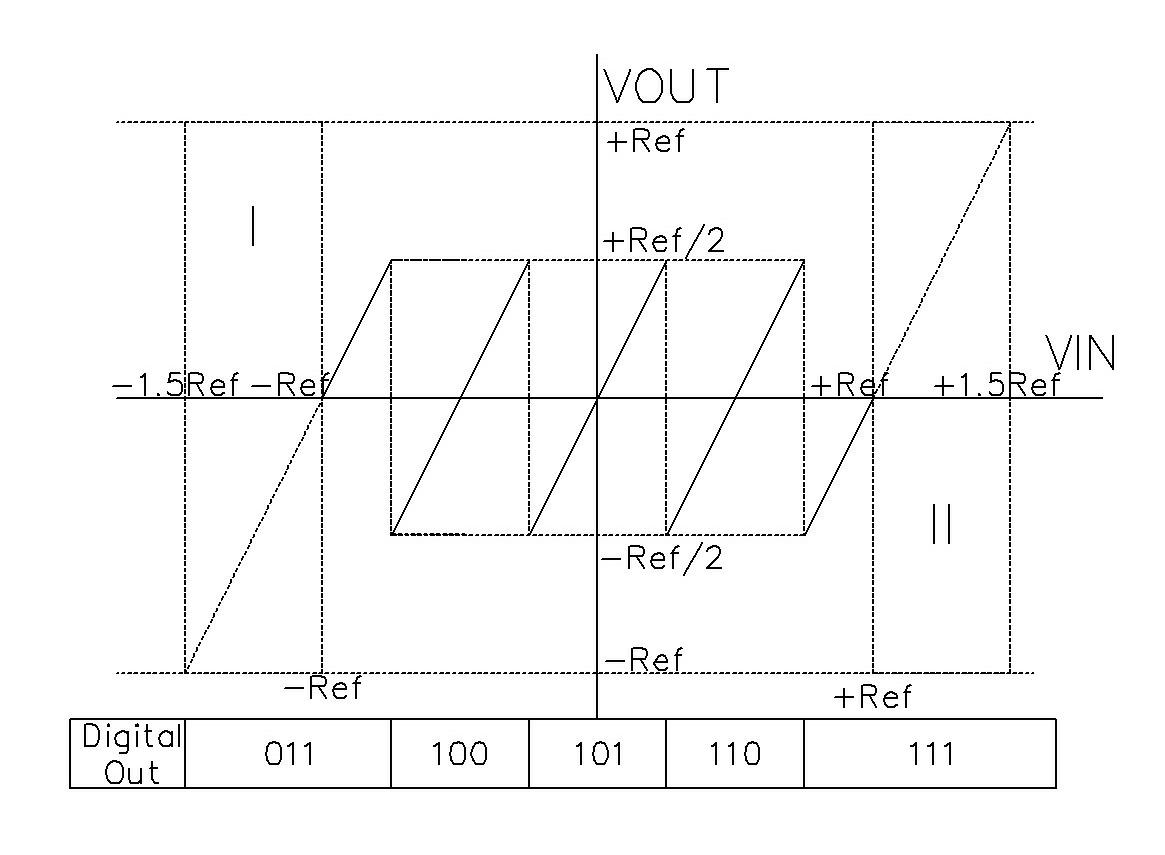

[0020] Specific embodiment one: the first stage adopts the judging method of the input overflow range of ten pipelined analog-to-digital converters of 1.5bit, see image 3 , Figure 5 , Figure 6 , after the signal is input into the pipeline analog-to-digital converter, the digital circuit of the first stage adopts a three-digit digital encoding method, and the outputs of the other nine digital circuits are all traditional digital encoding methods. The last bit is added, the digital output after the addition is completed, and the first digit of the first-level digital output does not participate in the addition process, which is the internal overflow judgment bit; when the addition is completed, the first two digits of the digital output are set to 11, internal When the overflow judgment bit is 0, and the highest bit corresponding to the output of the remaining nine stages except the first stage is 0, it is judged to be a negative overflow, and the overflow flag bit signal is...

specific Embodiment 2

[0021] Specific embodiment two: the first stage adopts the judging method of the input overflow range of ten pipelined analog-to-digital converters of 1.5bit, see Figure 4 , Figure 5 , Figure 7 , after the signal is input into the pipeline analog-to-digital converter, the digital circuit of the first stage adopts a three-digit digital encoding method, and the outputs of the other nine digital circuits are all traditional digital encoding methods. The last bit is added, the digital output after the addition is completed, and the first digit of the first-level digital output does not participate in the addition process, which is the internal overflow judgment bit; when the addition is completed, the first two digits of the digital output are set to 11, internal When the overflow judgment bit is 1, and the highest bit corresponding to the output of the remaining nine stages except the first stage is 0, it is judged to be a negative overflow, and the overflow flag bit signal i...

specific Embodiment 3

[0022]Specific embodiment three: the first stage adopts the judging method of the input overflow range of the eight-bit pipelined analog-to-digital converter of 1.5bit, see Figure 4 , Figure 5 , Figure 8 , after the signal is input into the pipeline analog-to-digital converter, the first-stage digital circuit adopts a three-digit digital encoding method, and the outputs of the remaining seven-stage digital circuits are all traditional digital encoding methods. The last bit is added, the digital output after the addition is completed, and the first bit of the first-level digital output does not participate in the addition process, and is an internal overflow judgment bit;

[0023] It is set that when the first two digits of the digital output are 11 after the addition is completed, the internal overflow judgment bit is 1, and the corresponding highest bit of the remaining seven outputs except the first level is 0 after the addition, it is judged to be negative Overflow, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More