Methods for improving reverse narrow channel effect and manufacturing metal oxide semiconductor (MOS) transistor

A MOS transistor, inverse narrow channel technology, applied in the field of semiconductor device manufacturing, can solve the problems of reduced working speed, large threshold voltage change, inverse narrow channel, etc., to achieve the effect of slowing down the trend and improving the effect of the inverse narrow channel

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

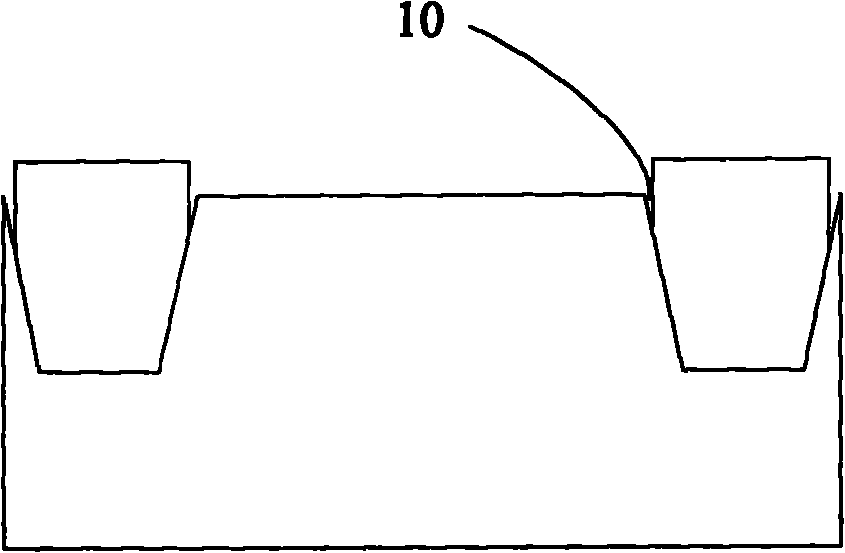

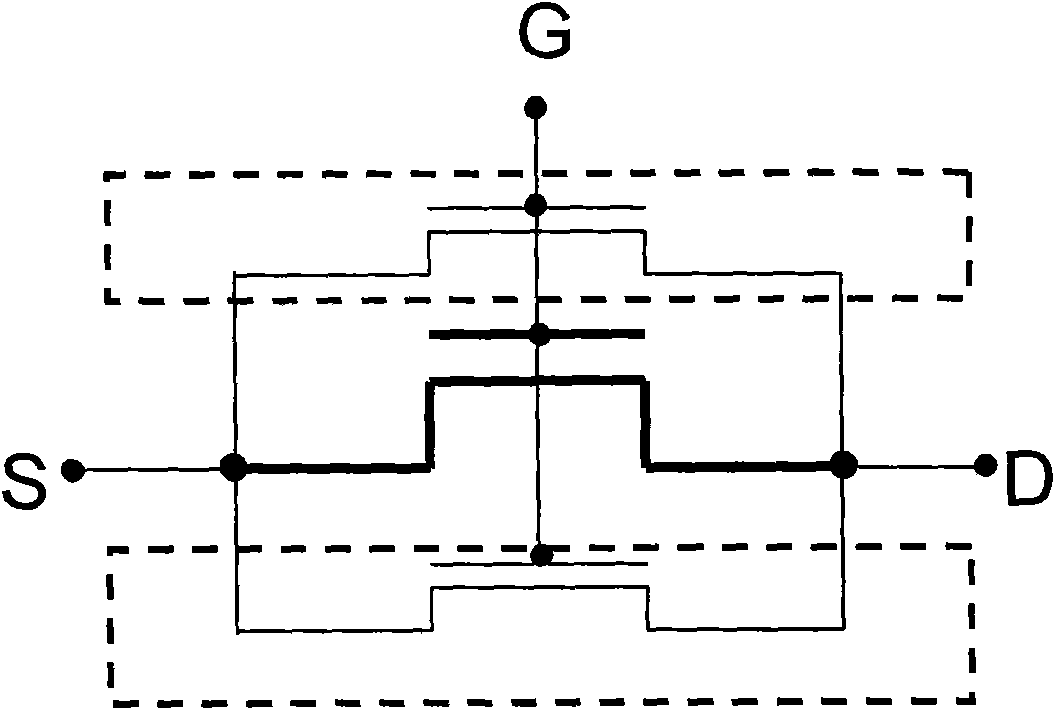

[0021] In the prior art, in the manufacturing process of MOS transistors, the size of the active region is larger than the predetermined size due to the recess phenomenon at the edge of the formed shallow trench isolation structure. As a result, two parasitic transistors with relatively low threshold voltages are connected in parallel on both sides of the subsequently formed transistor near the junction of the semiconductor substrate and the shallow trench isolation structure. During the operation of the transistor, a more serious anti-narrow channel effect will occur. The threshold voltage of the transistor decreases rapidly as the channel width decreases.

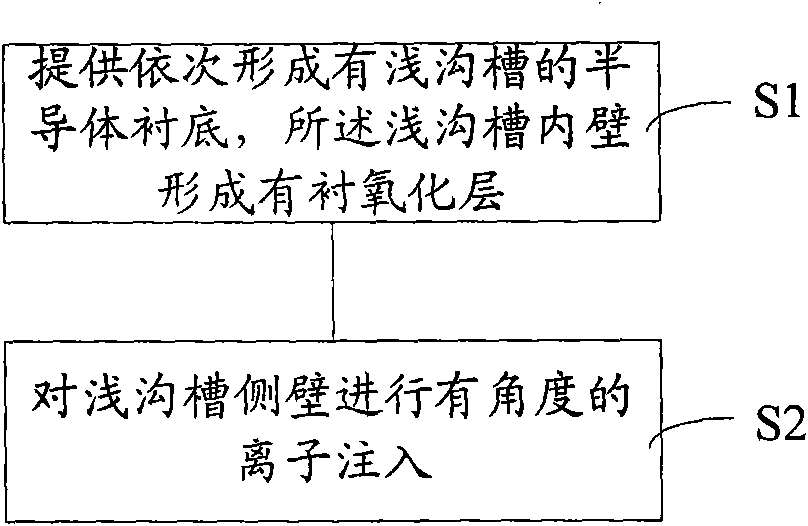

[0022] The present invention provides a method for improving the reverse narrow channel effect, such as image 3 As shown, step S1 is performed to provide a semiconductor substrate sequentially formed with shallow trenches, and a liner oxide layer is formed on the inner walls of the shallow trenches; step S2 is performed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More