MOS field effect pipe and its production

A technology of field effect transistors and silicon regions, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as transistor threshold voltage drop, achieve the effect of increasing threshold voltage and improving anti-narrow channel effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

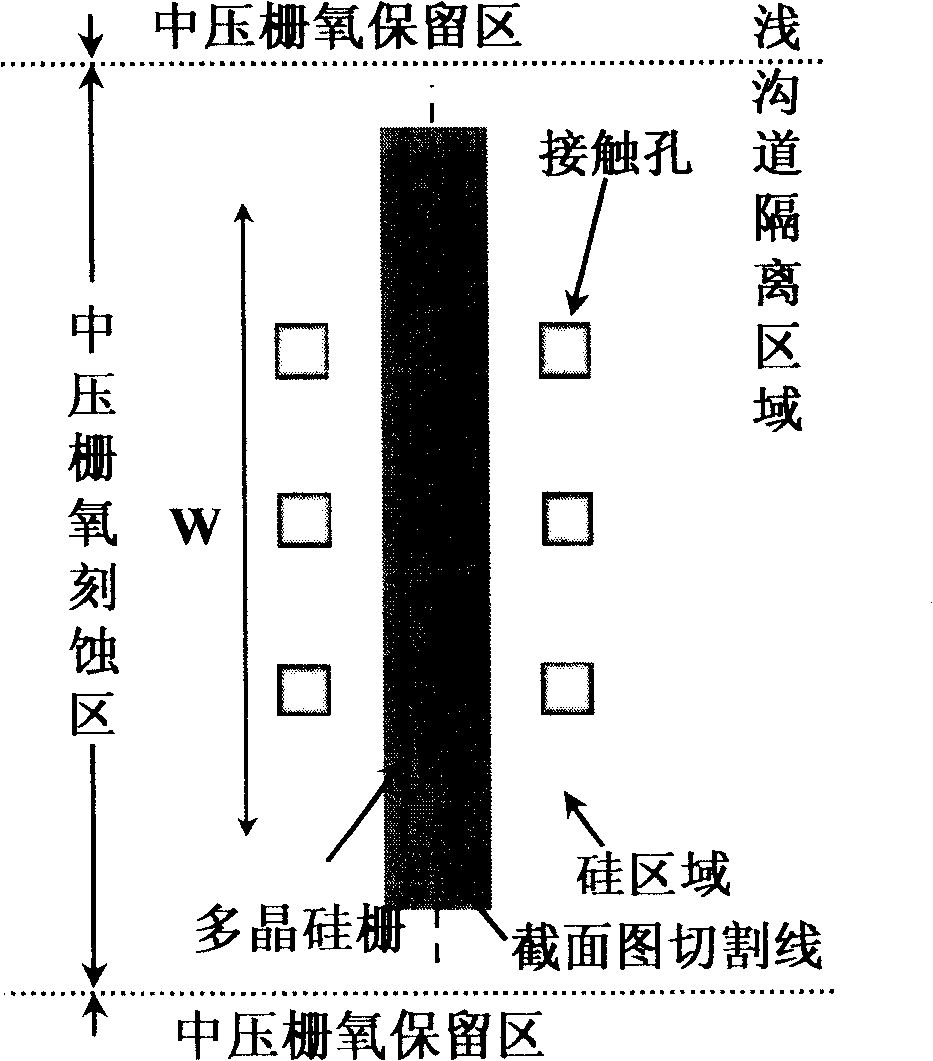

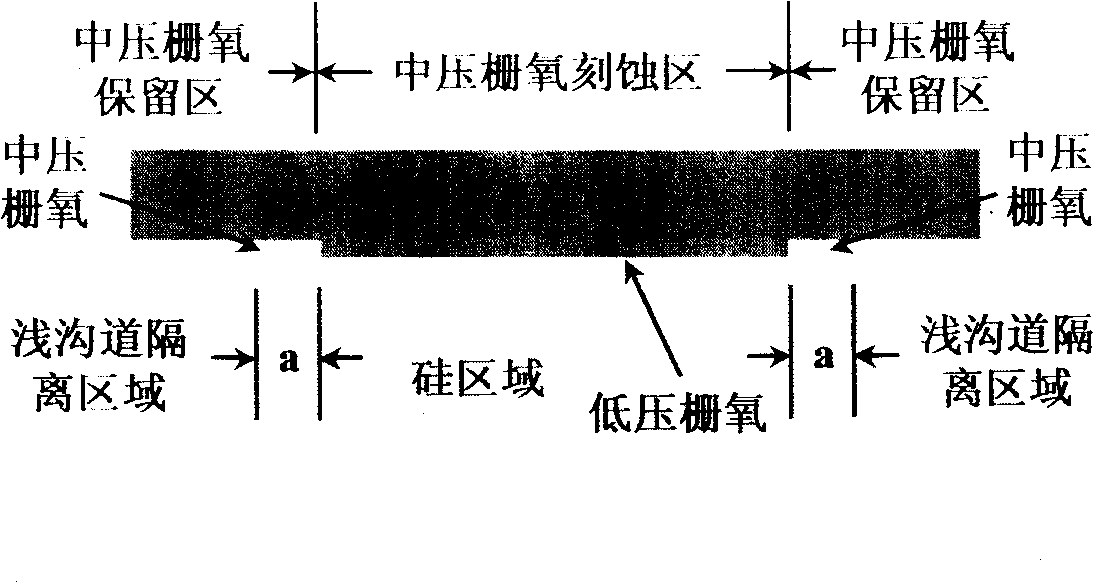

[0012] In a method for manufacturing a MOS field effect transistor of the present invention, the thick gate oxide of the medium voltage transistor must be grown after the thin gate oxide of the low voltage transistor is grown. Firstly, according to the severity of the anti-narrow channel effect of the low-voltage transistor, the thickness of the gate oxide of the medium-voltage transistor, the thickness of the gate oxide of the low-voltage transistor, the comprehensive device characteristics of the low-voltage transistor, and the relevant layout design rules are used to characterize the medium-voltage thick gate oxide. The geometry parameter "a" is optimized for the dimensions of the silicon edge region of the preserved low-voltage MOS transistor.

[0013] After the parameter "a" is determined, corresponding modifications are made to the layout of the double gate oxide etching photoresist. In the double gate oxide etching, only the medium-voltage thick gate oxide in the middle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More