Signal count delay method and circuit in chip electrifying process

A process signal and circuit technology, applied in electrical pulse generator circuits, logic circuits to generate pulses, electrical components, etc., can solve problems such as execution confusion, counters not full, chip destructive effects, etc., to improve safety, enhance Reliability and the effect of ensuring application security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The specific implementation manners of the present invention will be further described below in conjunction with the accompanying drawings.

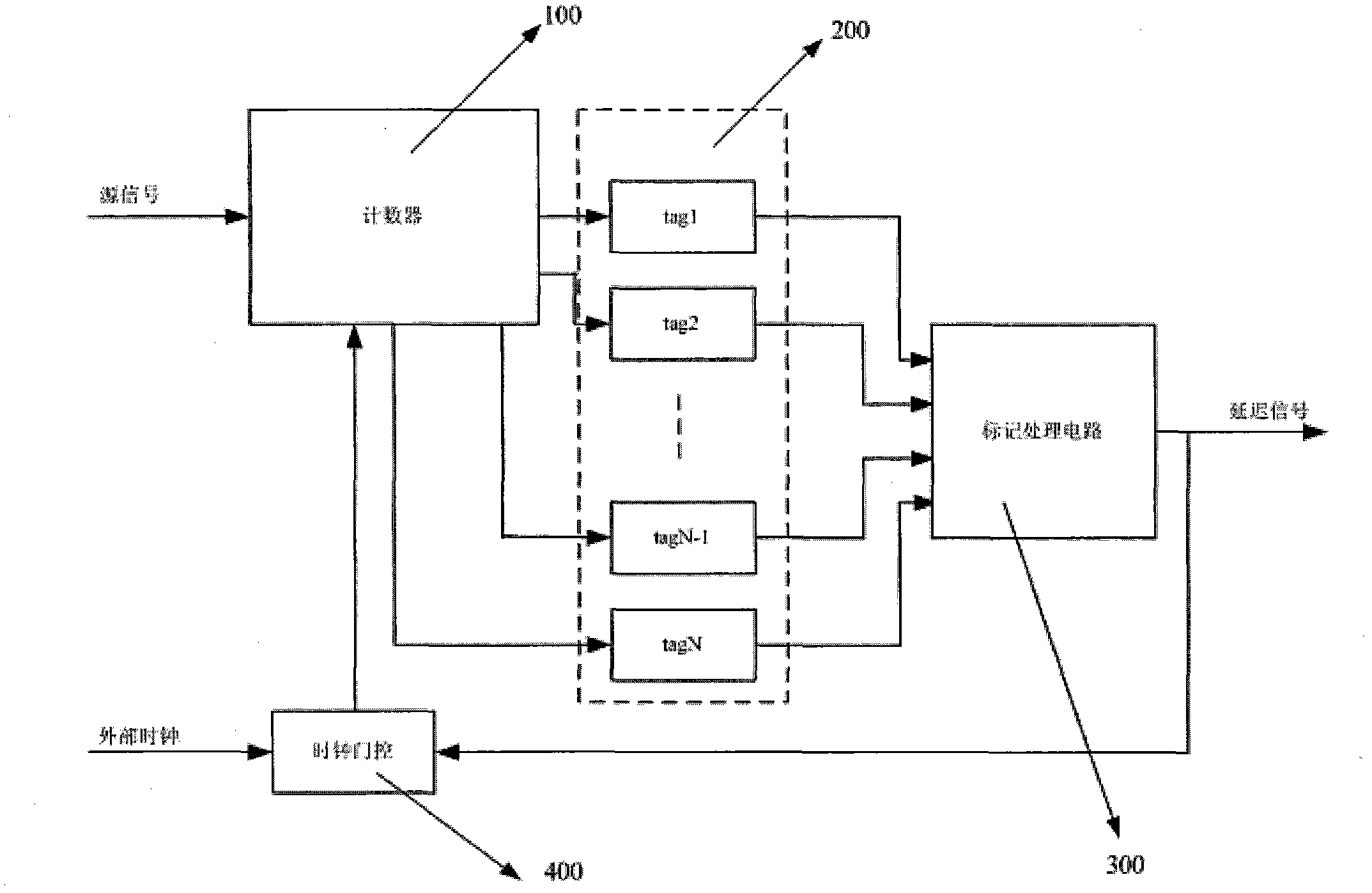

[0020] figure 1 It is an overall structure diagram of the present invention. The specific working process of the whole circuit is that the counter starts counting when the input signal is invalid. During the operation of the counter, if the counter value reaches one of the intermediate values of the set counting marks, the counting mark circuit automatically sets the corresponding mark bit. When After all the flag bits are set to valid, the flag processing circuit automatically generates the final delayed signal, and the delayed signal is sent to the subsequent control circuit in the card, and at the same time, the delayed signal is also sent to the clock gating circuit for shutting down Clock for the counter register and clock for the flag register.

[0021] The following takes the counting delay of the chip power-on reset si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More