Semi-precharging dynamic circuit

A dynamic circuit and pre-charging technology, applied in multiple input and output pulse circuits, etc., can solve the problems of voltage failure, increase DYN time, etc., and achieve the effect of eliminating DC power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

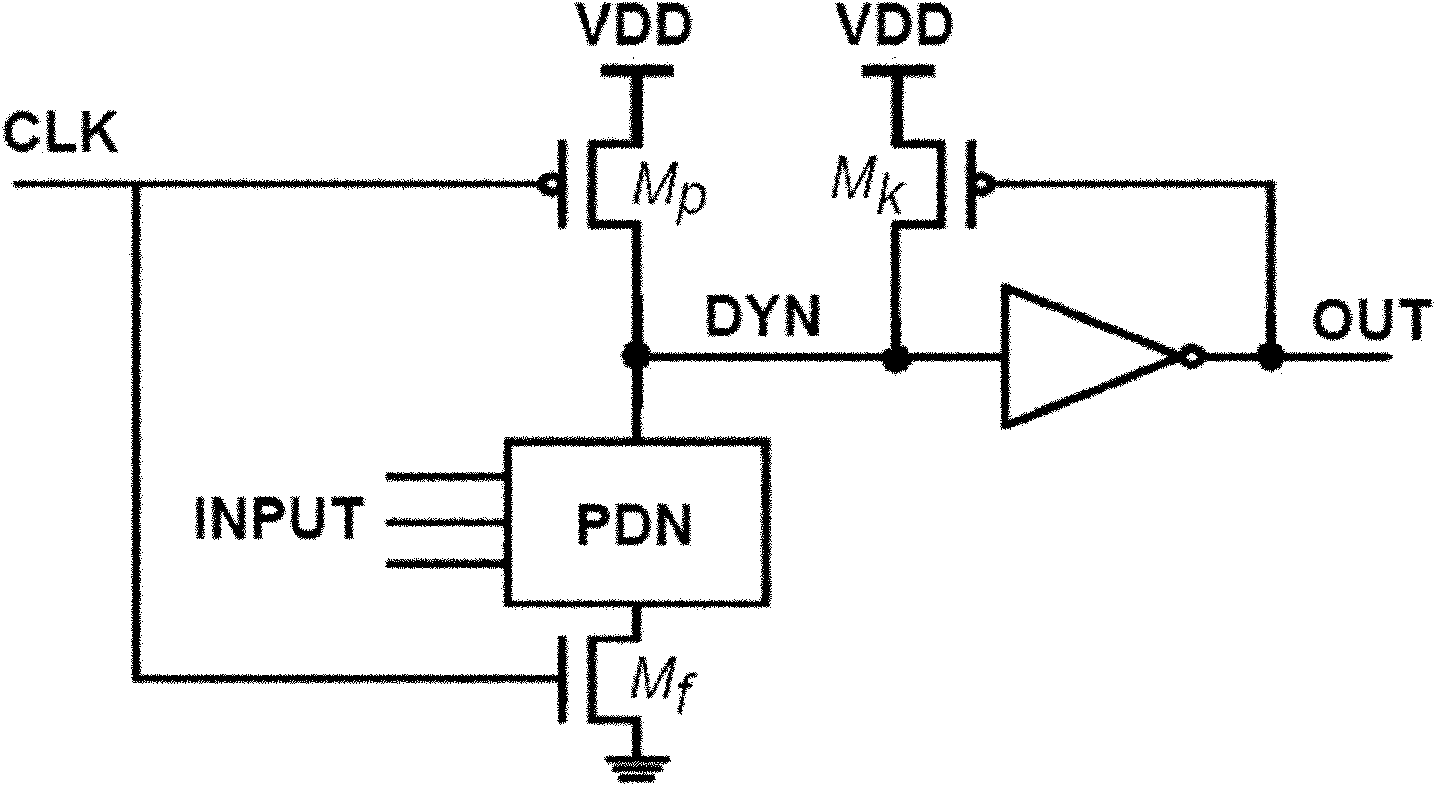

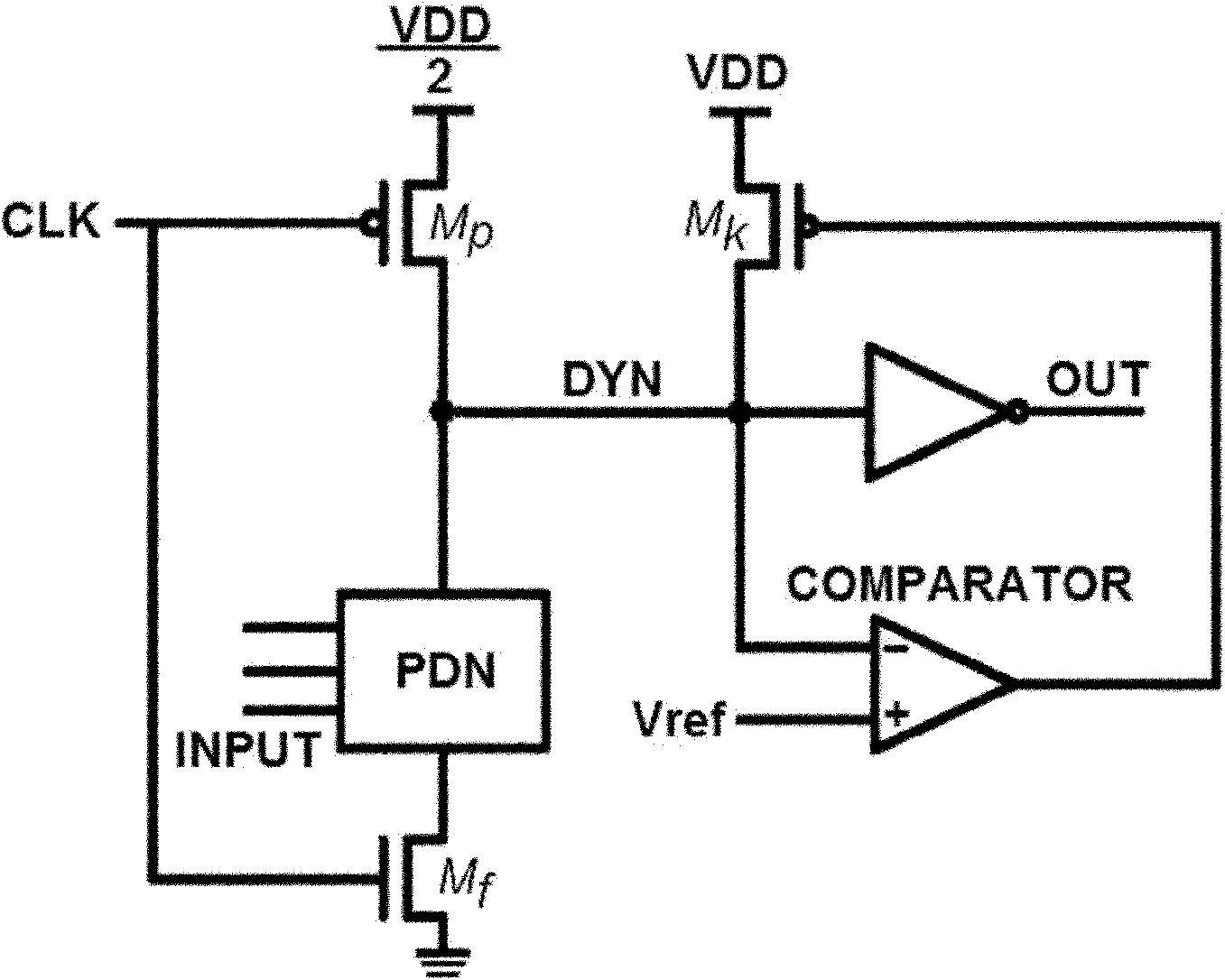

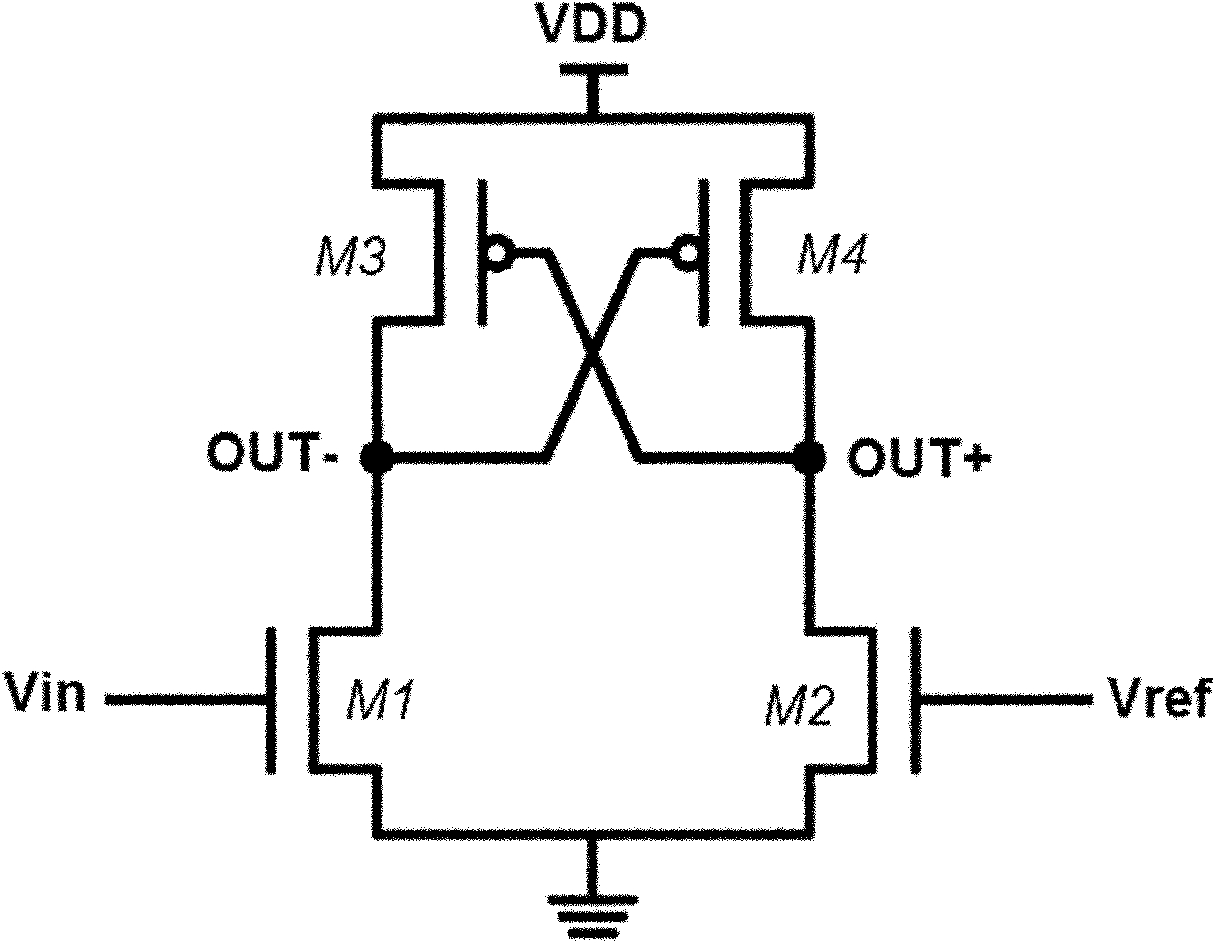

[0038] Such as Figure 4 As shown, it is a structural diagram of a semi-precharge dynamic circuit according to an embodiment of the present invention. The semi-precharge dynamic circuit includes: a first precharge tube Mp1, a pull-down logic network PDN, a hold tube Mk, an NMOS tube Mf, and an output inversion device and a comparator, the drain end of the first prefill pipe Mp1 is connected to the drain end of Mk to form a dynamic node DYN, one end of the PDN is connected to the DYN, and the other end is connected to the drain end of the Mf, and the comparator The negative input terminal of Mk is connected to DYN, the gate of Mk is connected to the output terminal of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More