Fully balanced dual-port memory cell

A memory unit and channel technology, applied in the field of memory, can solve problems such as inconvenience, and achieve the effect of reducing development investment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0078] In order to further explain the technical means and effects that the present invention adopts to achieve the intended purpose of the invention, the specific implementation, structure and characteristics of the fully balanced dual-channel memory unit proposed according to the present invention will be described below in conjunction with the accompanying drawings and preferred embodiments. And its effect, detailed description is as follows.

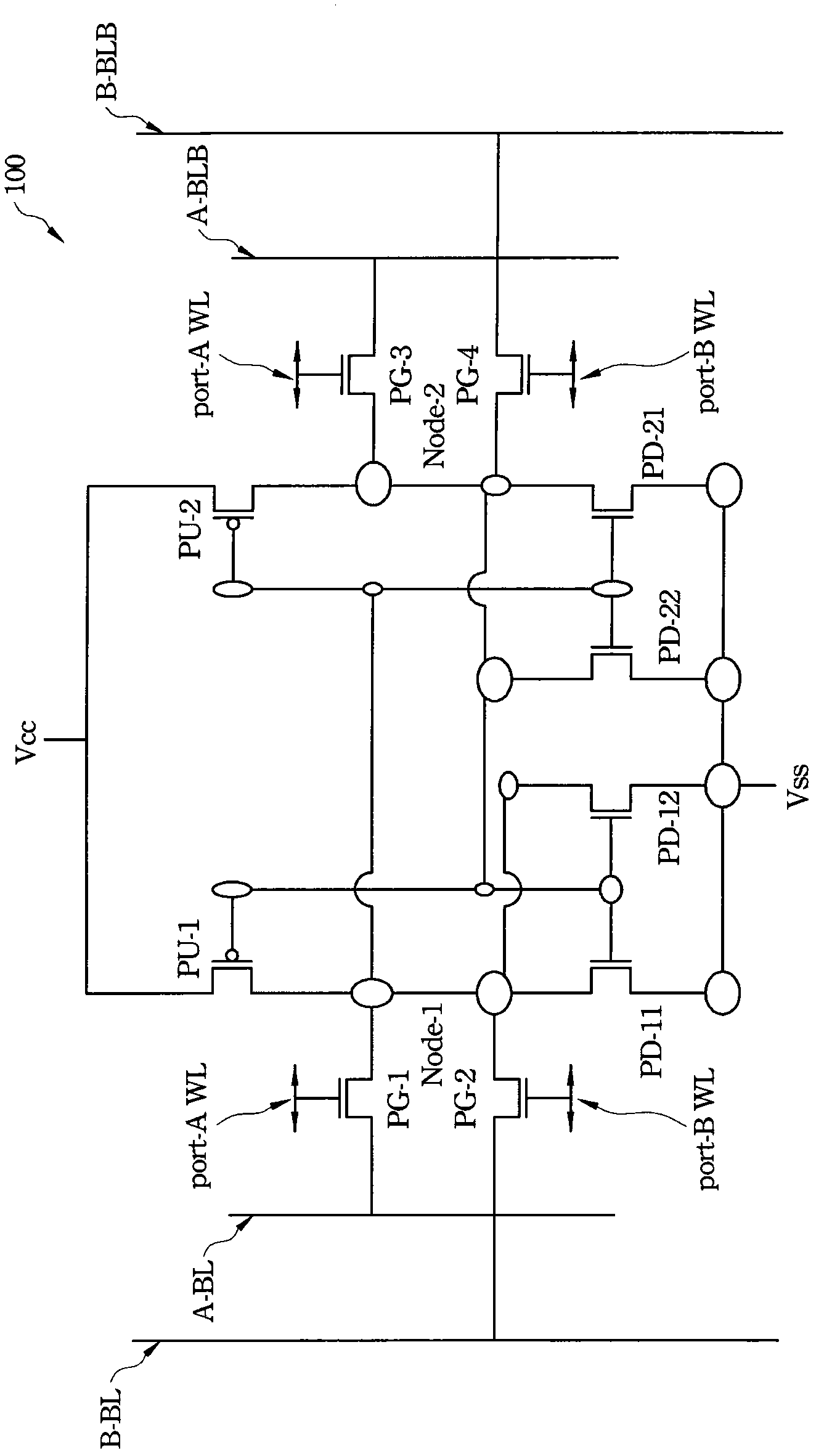

[0079] figure 1 It is a schematic diagram illustrating a dual-channel SRAM unit 100 according to an embodiment of the present invention. The dual-channel SRAM unit 100 includes a first inverter and a second inverter, and the first inverter and the second inverter are cross-coupled to each other. The first inverter includes a first pull-up device PU-1, a first pull-down device PD-11, and a second pull-down device PD-12. The first pull-up device PU-1 is formed by a P-type metal-oxide-semiconductor field-effect transistor (p-type met...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More