Integrated circuit device and packaging assembly

A technology of integrated circuits and conductive pillars, applied in the field of bump structures, can solve the problems of high manufacturing cost, interface peeling, and manufacturing cost attachment situation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

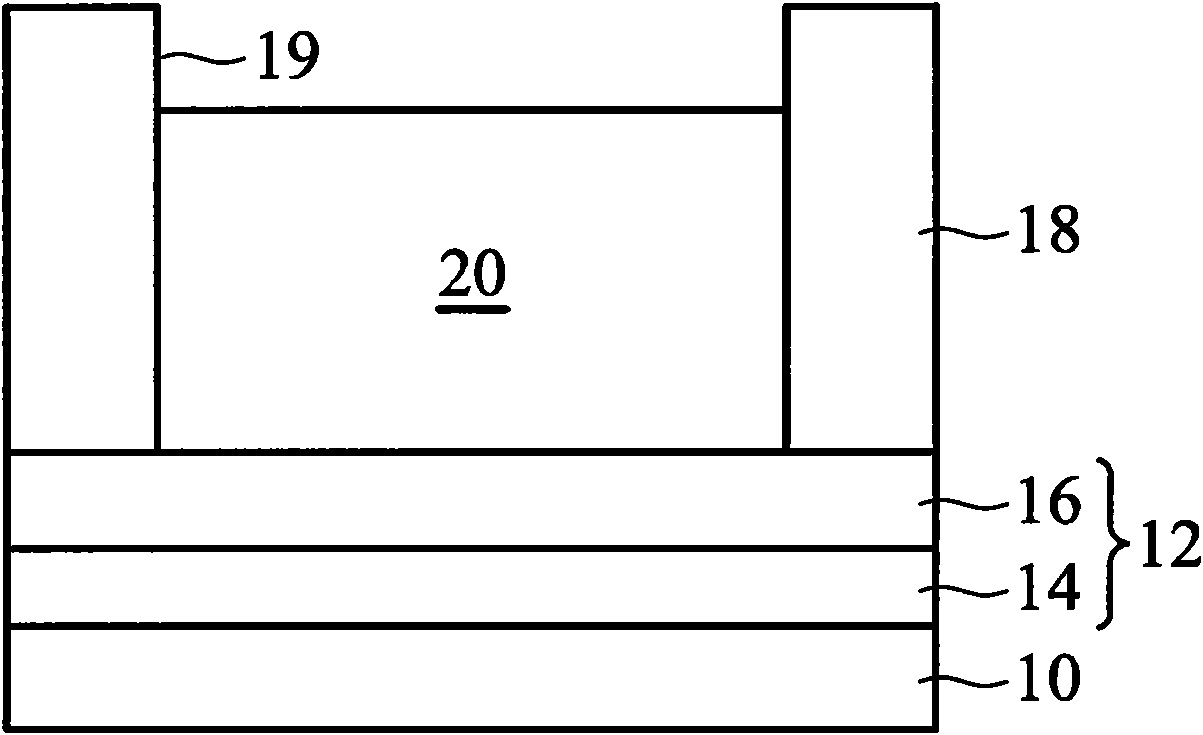

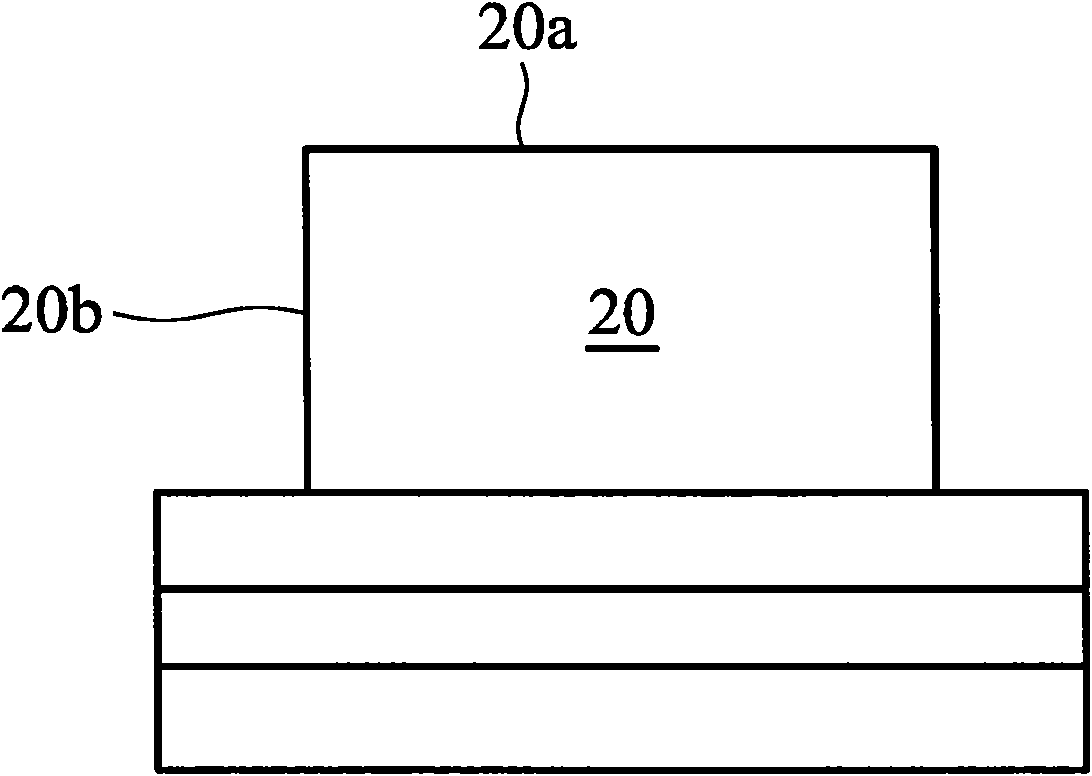

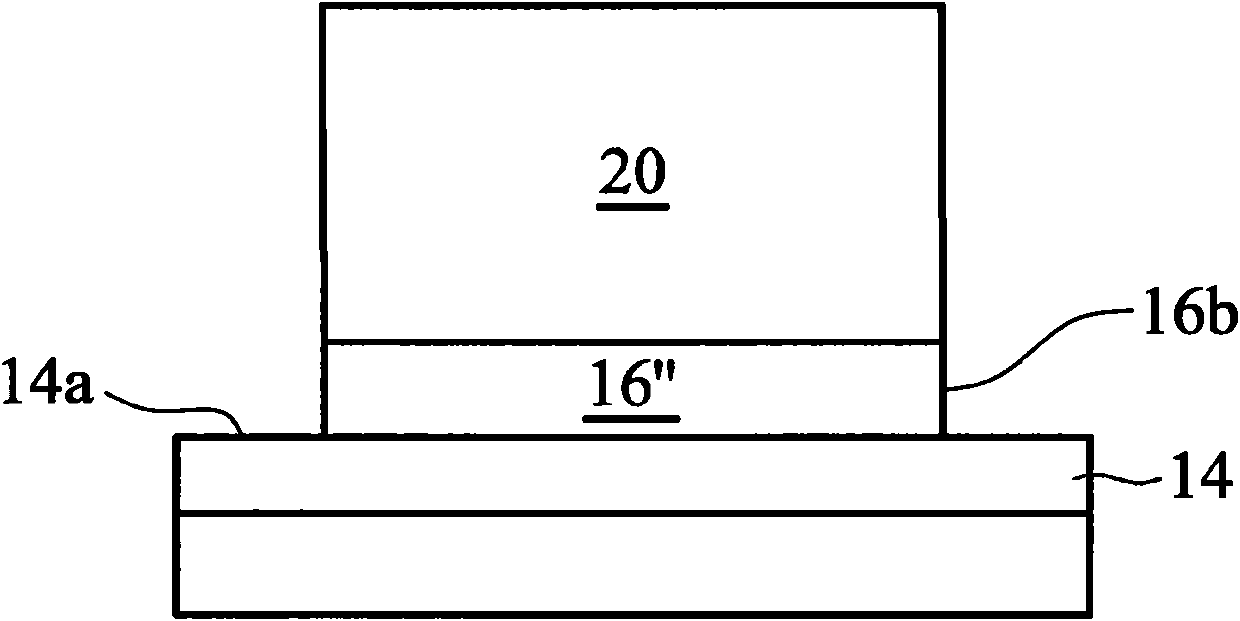

[0052] The present invention provides several embodiments of the sidewall protection process applicable to the copper pillar bump technology. Or the protective structure of one of the multiple non-metallic material film layers such as the combination of the above material film layers. The term "Cu pillar bump" used hereinafter refers to a bump structure including a conductive pillar (a pillar or a support base) formed of copper or copper alloy. The copper stud bumps can be directly applied on the conductive pads of a semiconductor chip or a redistribution layer of a flip-chip assembly or in other similar applications.

[0053] Examples and embodiments of the present invention are explained in detail below with reference to the corresponding drawings. Where possible, the same reference numbers have been used throughout the drawings and description to refer to the same or similar components. In the drawings, for the purpose of clarity and convenience, the shapes or thicknesses...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More