Instruction optimization method and processor for AES (Advanced Encryption Standard) symmetric encryption algorithm

A symmetric encryption algorithm and instruction optimization technology, applied in the direction of machine execution devices, etc., can solve the problems of not considering the AES algorithm instruction set expansion, the improvement effect of the AES algorithm execution efficiency is not very obvious, etc., to save memory space and code memory. space, and the effect of improving execution efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

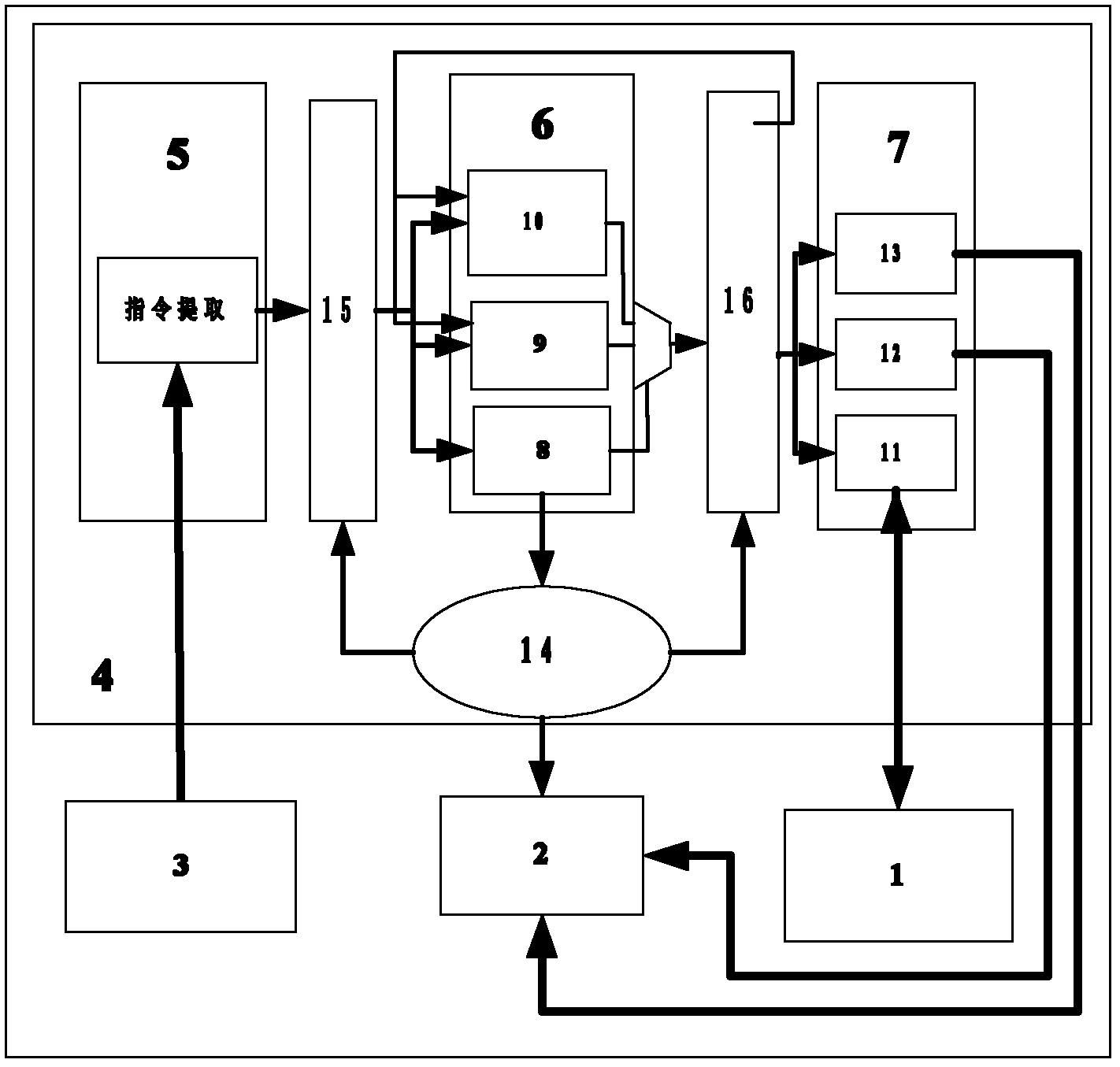

[0031] Below in conjunction with accompanying drawing and embodiment the present invention will be further described:

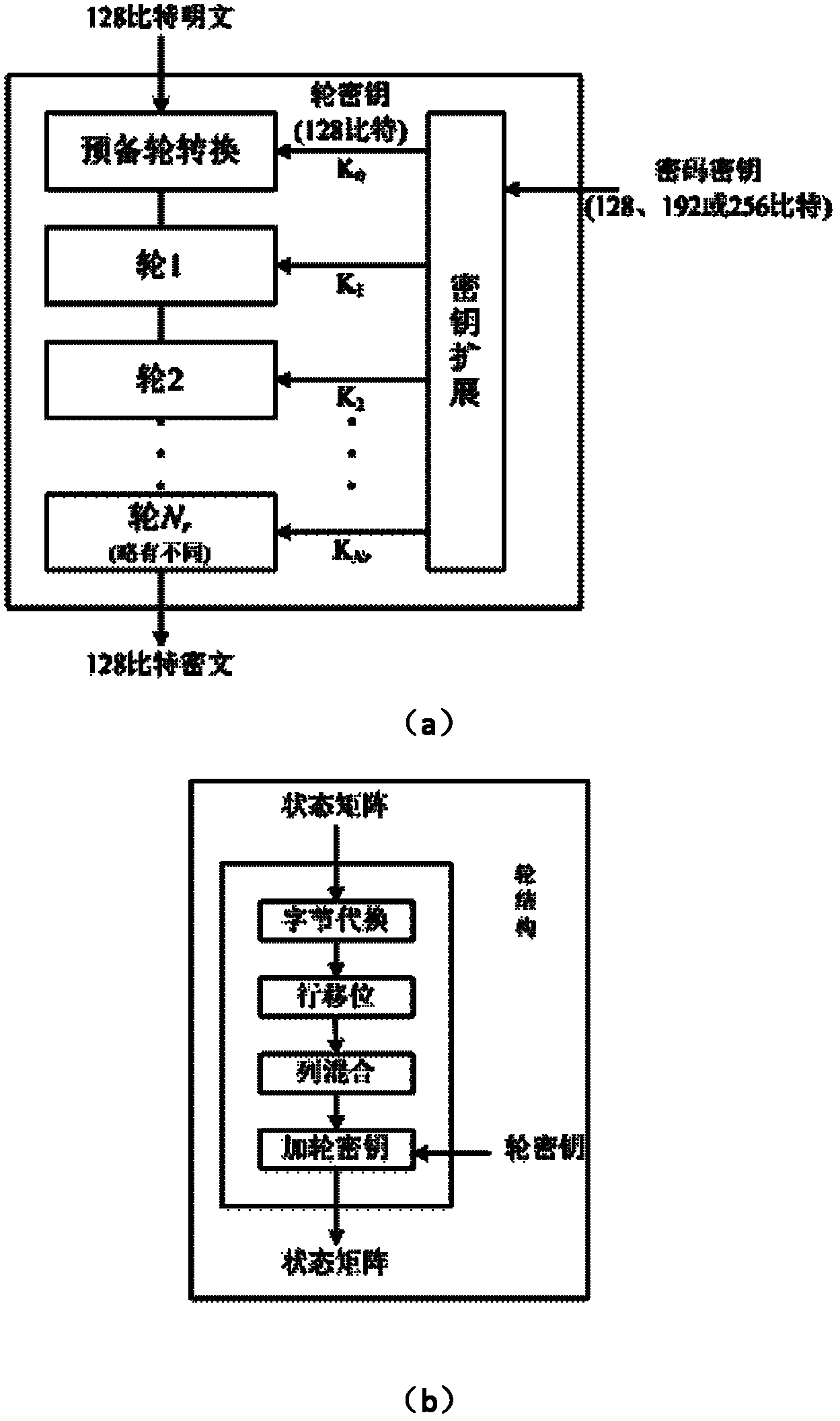

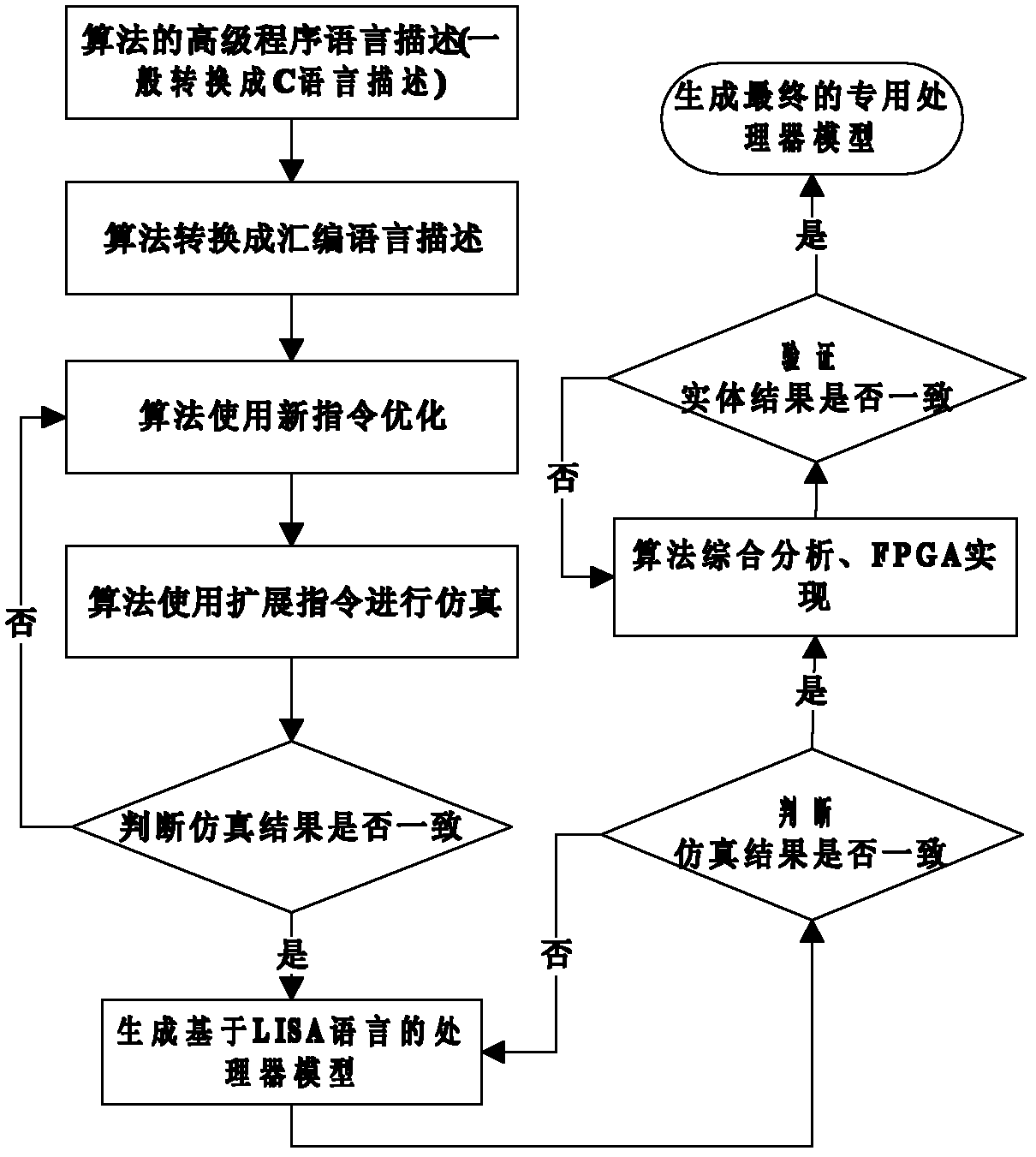

[0032] An AES symmetric encryption algorithm extended instruction set optimization method, under the premise of not changing the length of the original processor instruction opcode, the number of instruction bits and not affecting the operating speed of the processor, the optimization operation is:

[0033] 1) For the bit-fetching operation in the S-box byte replacement process, each bit of the eight-bit binary number needs to be taken out for each affine transformation. However, in the ARM processor and other commonly used embedded processors, there is no direct bit-fetching operation. The traditional method needs three assembly instructions to complete the bit-fetching operation, and needs to be executed for three clock cycles, so the execution process is very time-consuming. In order to speed up the process, the instruction getbit was designed and ad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More