Method and device for realizing instruction cache path selection in superscaler processor

A processor and superscalar technology, applied in machine execution devices, concurrent instruction execution, etc., can solve problems such as inability to read instructions, loss of useful way pointers, instruction fetch pause, etc., to avoid pipeline launch pause and shorten instruction fetch delay. , the effect of reducing the overall energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] The technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, and are not intended to limit the technical solution of the present invention.

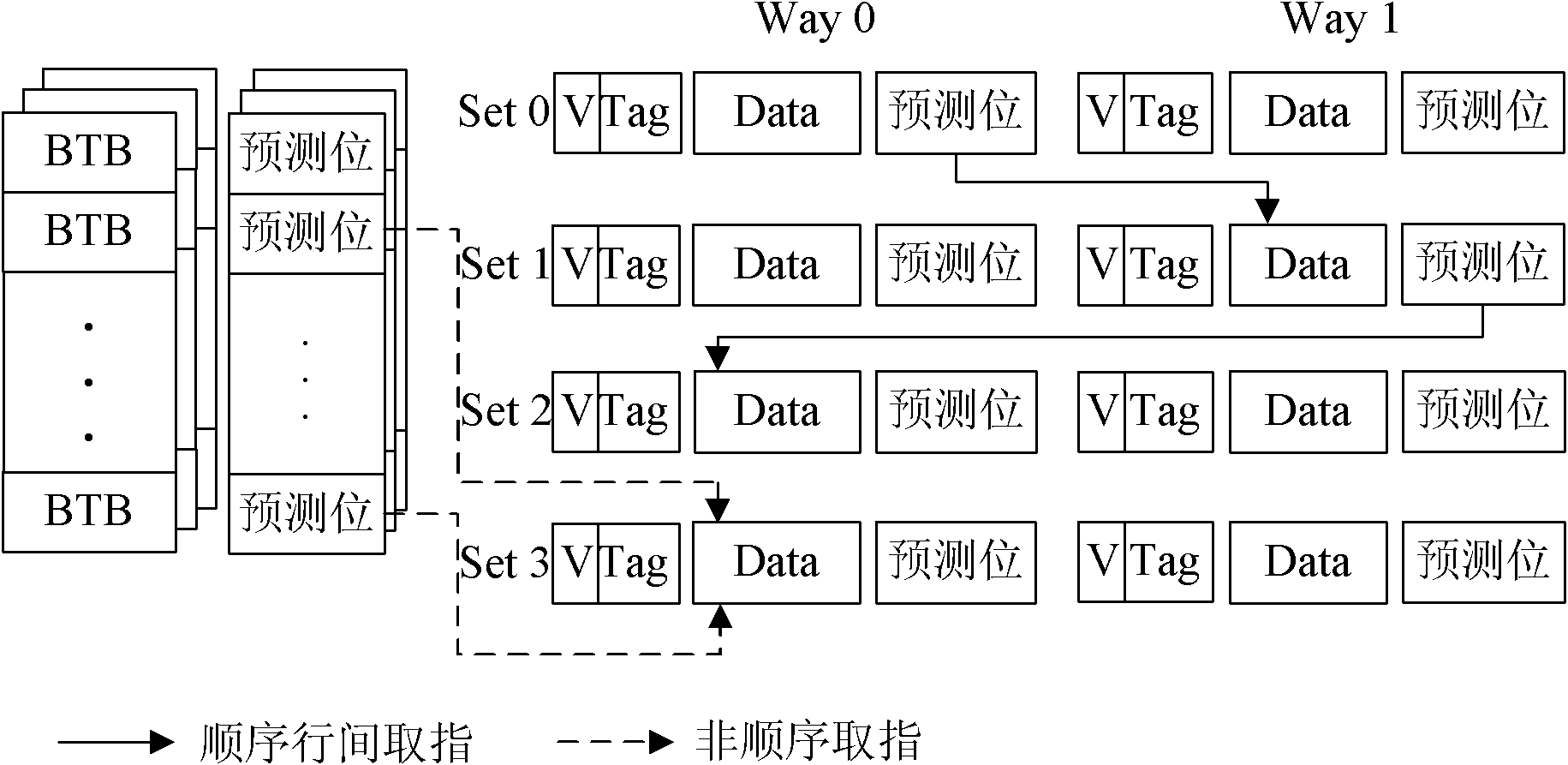

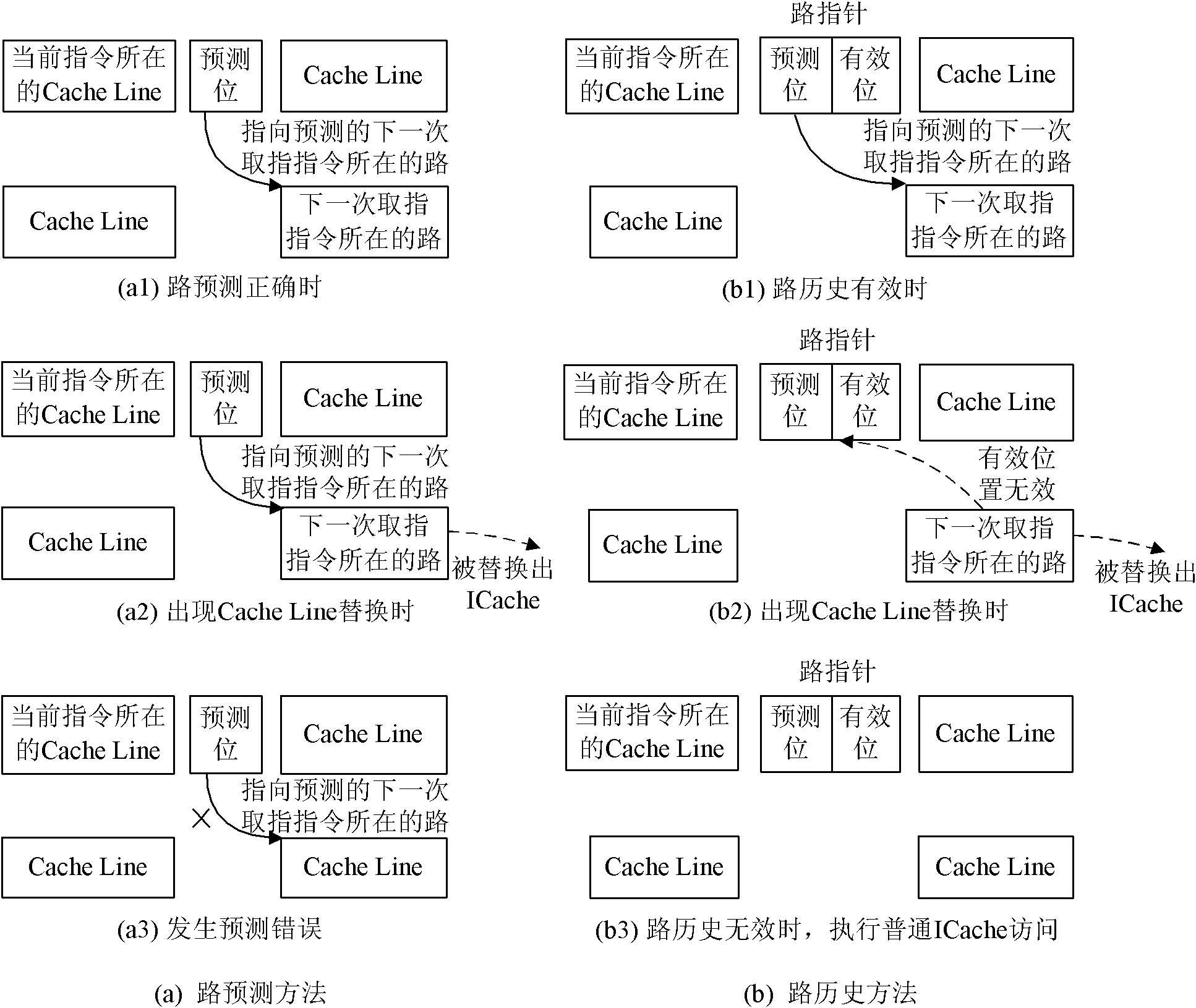

[0063] The present invention combines two way selection technologies of way prediction and way history on the traditional ICache structure, selects different way selection strategies according to different instruction fetching scenarios, and provides an embodiment of a method for realizing instruction cache way selection by a superscalar processor and The corresponding device embodiment.

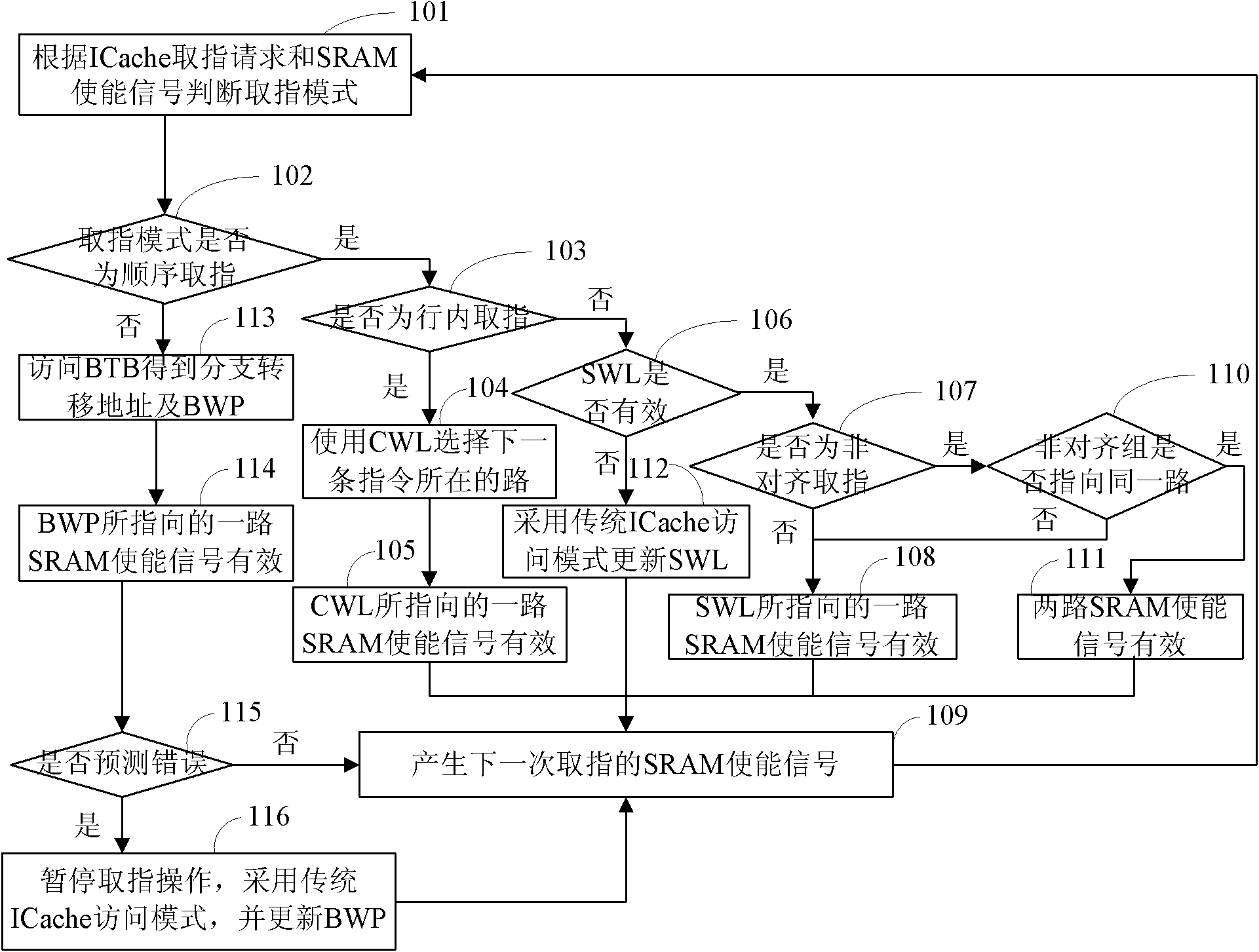

[0064] Wherein, the flow process of the method embodiment of the present invention is as follows image 3 shown, including the following steps:

[0065] 101: judge the instruction fetch mode according to the instruction fetch request and the SRA...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More